#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | -                                                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 17                                                                        |

| Program Memory Size        | 3.5KB (2K x 14)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 128 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                 |

| Data Converters            | A/D 14x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                            |

| Supplier Device Package    | 20-SSOP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16hv785-i-ss |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Міскоснір **РІС16F785/HV785**

### **20-Pin Flash-Based 8-Bit CMOS Microcontroller**

### High-Performance RISC CPU:

- Only 35 Instructions to Learn:

- All single-cycle instructions except branches

- · Operating Speed:

- DC 20 MHz oscillator/clock input

- DC 200 ns instruction cycle

- Interrupt Capability

- 8-Level Seep Hardware Stack

- Direct, Indirect and Relative Addressing modes

### **Special Microcontroller Features:**

- Precision Internal Oscillator:

- Factory calibrated to ±1%

- Software selectable frequency range of 8 MHz to 32 kHz

- Software tunable

- Two-Speed Start-up mode

- Crystal fail detect for critical applications

- Clock mode switching during operation for power savings

- Power-Saving Sleep mode

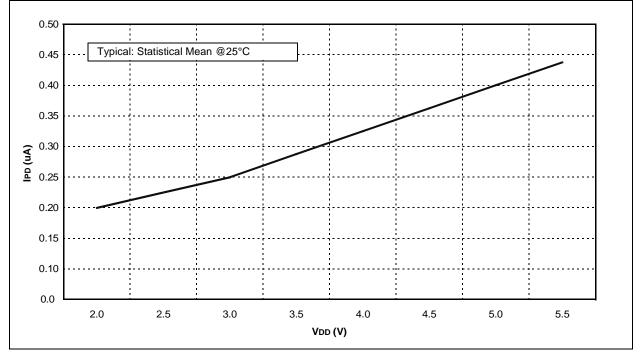

- Wide Operating Voltage Range (2.0V-5.5V)

- Industrial and Extended Temperature Range

- Power-on Reset (POR)

- Power-up Timer (PWRT) and Oscillator Start-up Timer (OST)

- Brown-out Reset (BOR) with Software Control

Option

- Enhanced Low-Current Watchdog Timer (WDT) with on-chip Oscillator (software selectable nominal 268 seconds with full prescaler) with Software Enable

- Multiplexed Master Clear with Pull-up/Input Pin

- Programmable Code Protection

- High-Endurance Flash/EEPROM cell:

- 100,000 write Flash endurance

- 1,000,000 write EEPROM endurance

- Flash/Data EEPROM retention: > 40 years

### Low-Power Features:

- Standby Current:

- 30 nA @ 2.0V, typical

- Operating Current:

- 8.5  $\mu A @$  32 kHz, 2.0V, typical

- 100 μA @ 1 MHz, 2.0V, typical

- Watchdog Timer Current:

- 1 μA @ 2.0V, typical

- Timer1 Oscillator Current:

- 2 μA @ 32 kHz, 2.0V, typical

### **Peripheral Features:**

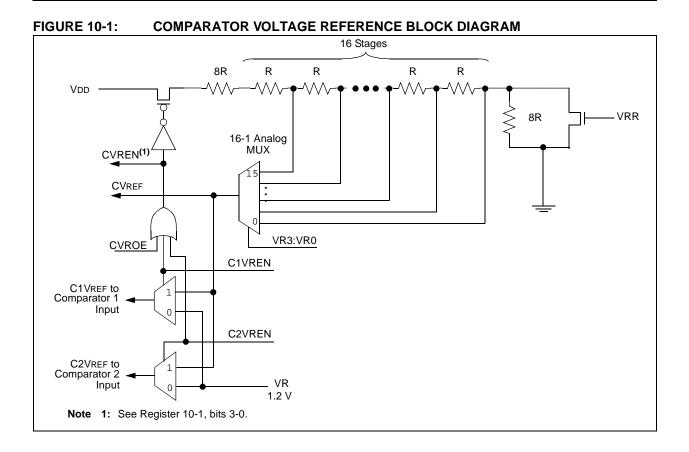

- High-Speed Comparator module with:

- Two independent analog comparators

Programmable on-chip voltage reference (CVREF) module (% of VDD)

- 1.2V band gap voltage reference

- Comparator inputs and outputs externally accessible

- < 40 ns propagation delay

- 2 mv offset, typical

- Operational Amplifier module with 2 independent Op Amps:

- 3 MHz GBWP, typical

- All I/O pins externally accessible

- Two-Phase Asynchronous Feedback PWM module:

- Complementary output with programmable dead band delay

- Infinite resolution analog duty cycle

- Sync Output/Input for multi-phase PWM

- FOSC/2 maximum PWM frequency

- A/D Converter:

- 10-bit resolution and 14 channels (2 internal)

- 17 I/O pins and 1 Input-only Pin:

- High-current source/sink for direct LED drive

- Interrupt-on-pin change

- Individually programmable weak pull-ups

- Timer0: 8-Bit Timer/Counter with 8-Bit Programmable Prescaler

- Enhanced Timer1:

- 16-bit timer/counter with prescaler

- External Gate Input mode

- Option to use OSC1 and OSC2 in LP mode as Timer1 oscillator, if INTOSC mode selected

- Timer2: 8-Bit Timer/Counter with 8-Bit Period Register, Prescaler and Postscaler

- Capture, Compare, PWM module:

- 16-bit Capture, max resolution 12.5 ns

Compare, max resolution 200 ns

- Compare, max resolution 200 hs

- 10-bit PWM with 1 output channel, max frequency 20 kHz

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) via two pins

- Shunt Voltage Regulator (PIC16HV785 only):

- 5 volt regulation

- 4 mA to 50 mA shunt range

### 2.2.2.6 PCON Register

The Power Control register contains flag bits to allow differentiation between a Power-on Reset (POR), a Brown-out Reset (BOR), a Watchdog Timer (WDT) Reset (WDT) and an external MCLR Reset.

### REGISTER 2-6: PCON: POWER CONTROL REGISTER

| U-0                                                                  | U-0          | U-0                                                 | R/W-1 | U-0                   | U-0              | R/W-0           | R/W-x |  |  |  |  |

|----------------------------------------------------------------------|--------------|-----------------------------------------------------|-------|-----------------------|------------------|-----------------|-------|--|--|--|--|

|                                                                      | —            | _                                                   | —     | SBOREN <sup>(1)</sup> | _                | —               | POR   |  |  |  |  |

| bit 7                                                                |              |                                                     |       |                       |                  |                 | bit 0 |  |  |  |  |

|                                                                      |              |                                                     |       |                       |                  |                 |       |  |  |  |  |

| Legend:                                                              |              |                                                     |       |                       |                  |                 |       |  |  |  |  |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |              |                                                     |       |                       |                  |                 |       |  |  |  |  |

| -n = Value at P                                                      | OR           | '1' = Bit is set                                    |       | '0' = Bit is cle      | ared             | x = Bit is unkn | iown  |  |  |  |  |

| bit 7-5<br>bit 4                                                     | (1)          |                                                     |       |                       |                  |                 |       |  |  |  |  |

| bit 3-2                                                              | Unimplement  | ted: Read as '                                      | )'    |                       |                  |                 |       |  |  |  |  |

| bit 1                                                                | 1 = No Power | on Reset Status<br>-on Reset occu<br>on Reset occur | urred | set in software       | after a Power-c  | on Reset occurs | 5)    |  |  |  |  |

| bit 0                                                                | 1 = No Brown | out Reset Statu<br>-out Reset occ<br>out Reset occu | urred | set in software       | e after a Brown- | out Reset occu  | rs)   |  |  |  |  |

**Note 1:** BOREN<1:0> = 01 in Configuration Word for this bit to control the  $\overline{\text{BOR}}$ .

### 3.7.1 FAIL-SAFE CONDITION CLEARING

The Fail-Safe condition is cleared after a Reset, the execution of a SLEEP instruction, or a modification of the SCS bit. While in Fail-Safe condition, the PIC16F785/HV785 uses the internal oscillator as the system clock source. The IRCF bits in the OSCCON Register can be modified to adjust the internal oscillator frequency without exiting the Fail-Safe condition.

The Fail-Safe condition must be cleared before the OSFIF flag can be cleared.

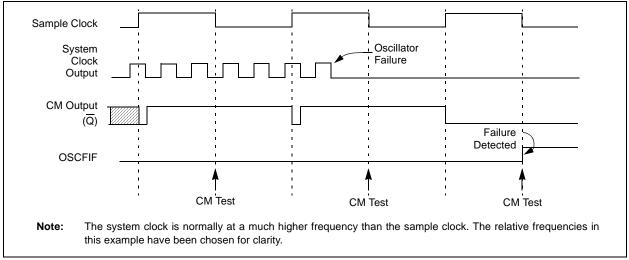

### FIGURE 3-9: FSCM TIMING DIAGRAM

### 3.7.2 RESET OR WAKE-UP FROM SLEEP

The FSCM is designed to detect oscillator failure at any point after the device has exited a Reset or Sleep condition and the Oscillator Start-up Timer (OST) has expired. If the external clock is EC or RC mode, monitoring will begin immediately following these events.

For LP, XT or HS mode, the external oscillator may require a start-up time considerably longer than the FSCM sample clock time; a false clock failure may be detected (see Figure 3-9). To prevent this, the internal oscillator is automatically configured as the system clock and functions until the external clock is stable (the OST has timed out). This is identical to Two-Speed Start-up mode. Once the external oscillator is stable, the LFINTOSC returns to its role as the FSCM source.

Note: Due to the wide range of oscillator start-up times, the Fail-Safe circuit is not active during oscillator start-up (i.e., after exiting Reset or Sleep). After an appropriate amount of time, the user should check the OSTS bit in the OSCCON Register to verify the oscillator start-up and system clock switchover has successfully completed.

### REGISTER 4-2: TRISA: PORTA TRI-STATE REGISTER

| U-0   | U-0 | R/W-1 |                       |        | R/W-1  | R/W-1  | R/W-1 |  |

|-------|-----|-------|-----------------------|--------|--------|--------|-------|--|

|       |     |       | TRISA3 <sup>(1)</sup> | TRISA2 | TRISA1 | TRISA0 |       |  |

| bit 7 |     |       |                       |        |        |        | bit 0 |  |

|       |     |       |                       |        |        |        |       |  |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7-6 | Unimplemented: Read as '0'                                                                        |

|---------|---------------------------------------------------------------------------------------------------|

| bit 5-0 | TRISA<5:0>: PORTA Tri-State Control bit <sup>(1), (2)</sup>                                       |

|         | 1 = PORTA pin configured as an input (tri-stated)                                                 |

|         | 0 = PORTA pin configured as an output                                                             |

| bit 0   | C: Carry/ $\overline{\text{Borrow}}$ bit (addwf, addlw, sublw, subwf instructions) <sup>(1)</sup> |

|         | 1 = A carry-out from the Most Significant bit of the result occurred                              |

|         | 0 = No carry-out from the Most Significant bit of the result occurred                             |

Note 1: TRISA<3> always reads '1'.

**2:** TRISA<5:4> always reads '1' in XT, HS and LP OSC modes.

### 4.2 Additional Pin Functions

Every PORTA pin on the PIC16F785/HV785 has an interrupt-on-change option and a weak pull-up option. The next three sections describe these functions.

### 4.2.1 WEAK PULL-UPS

Each of the PORTA pins has an individually configurable internal weak pull-up. Control bits WPUAx enable or disable each pull-up. Refer to Register 4-3. Each weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a Power-on Reset by the RAPU bit in the (OPTION Register. The weak pull-up on RA3 is automatically enabled when RA3 is configured as MCLR.

### REGISTER 4-3: WPUA: WEAK PULL-UP REGISTER

| U-0   | U-0                                           | R/W-1 | R/W-1                | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|-------|-----------------------------------------------|-------|----------------------|-------|-------|-------|-------|

| —     | — — WPUA5 <sup>(4)</sup> WPUA4 <sup>(4)</sup> |       | WPUA3 <sup>(3)</sup> | WPUA2 | WPUA1 | WPUA0 |       |

| bit 7 |                                               |       |                      |       |       |       | bit 0 |

|       |                                               |       |                      |       |       |       |       |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 7-6 Unimplemented: Read as '0'

bit 5-0 WPUA<5:0>: Weak Pull-up Register bits

- 1 = Pull-up enabled

- 0 = Pull-up disabled

**Note 1:** Global RAPU must be enabled for individual pull-ups to be enabled.

2: The weak pull-up device is automatically disabled if the pin is in Output mode (TRISA = 0).

3: The RA3 pull-up is automatically enabled when configured as MCLR in the Configuration Word.

**4:** WPUA<5:4> always reads '1' in XT, HS and LP OSC modes.

### 8.0 CAPTURE/COMPARE/PWM (CCP) MODULE

The Capture/Compare/PWM (CCP) module contains a 16-bit register which can operate as a:

- 16-bit Capture register

- 16-bit Compare register

- PWM Master/Slave Duty Cycle register

Capture/Compare/PWM Register 1 (CCPR1) is comprised of two 8-bit registers: CCPR1L (low byte) and CCPR1H (high byte). The CCP1CON register controls the operation of CCP. The special event trigger is generated by a compare match and will clear both TMR1H and TMR1L registers.

### TABLE 8-1: CCP MODE – TIMER RESOURCES REQUIRED

| CCP Mode | Timer Resource |

|----------|----------------|

| Capture  | Timer1         |

| Compare  | Timer1         |

| PWM      | Timer2         |

### **REGISTER 8-1: CCP1CON: CCP OPERATION REGISTER**

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0         | R/W-0 | R/W-0  | R/W-0  |

|-------|-----|-------|-------|---------------|-------|--------|--------|

| —     | —   | DC1B1 | DC1B0 | CCP1M3 CCP1M2 |       | CCP1M1 | CCP1M0 |

| bit 7 |     |       |       |               |       |        | bit 0  |

| Legend:      |                                                                                                          |                                                                                                                                                                                                         |                                                           |                                        |  |  |  |  |  |  |  |

|--------------|----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|----------------------------------------|--|--|--|--|--|--|--|

| R = Readat   | ole bit                                                                                                  | W = Writable bit                                                                                                                                                                                        | U = Unimplemented bit,                                    | , read as '0'                          |  |  |  |  |  |  |  |

| -n = Value a | at POR                                                                                                   | '1' = Bit is set                                                                                                                                                                                        | '0' = Bit is cleared                                      | x = Bit is unknown                     |  |  |  |  |  |  |  |

|              |                                                                                                          |                                                                                                                                                                                                         |                                                           |                                        |  |  |  |  |  |  |  |

| bit 7-6      | Unimplen                                                                                                 | Unimplemented: Read as '0'.                                                                                                                                                                             |                                                           |                                        |  |  |  |  |  |  |  |

| bit 5-4      | DC1B<1:0                                                                                                 | >: PWM Duty Cycle Least                                                                                                                                                                                 | Significant bits                                          |                                        |  |  |  |  |  |  |  |

|              | <u>Capture m</u><br>Unused                                                                               | node:                                                                                                                                                                                                   |                                                           |                                        |  |  |  |  |  |  |  |

|              | <u>Compare</u><br>Unused                                                                                 | mode:                                                                                                                                                                                                   |                                                           |                                        |  |  |  |  |  |  |  |

|              | <u>PWM moo</u><br>These bits                                                                             |                                                                                                                                                                                                         | NM duty cycle. The eight MSb                              | os are found in CCPR1L.                |  |  |  |  |  |  |  |

| bit 3-0      | CCP1M<3                                                                                                  | CCP1M<3:0>: CCP Mode Select bits                                                                                                                                                                        |                                                           |                                        |  |  |  |  |  |  |  |

|              | 0001 = U<br>0010 = C<br>0011 = U<br>0100 = C<br>0101 = C<br>0110 = C<br>1000 = C<br>1001 = C<br>1010 = C | nused (reserved)<br>apture mode, every falling e<br>apture mode, every rising e<br>apture mode, every 4th risi<br>apture mode, every 16th ris<br>ompare mode, set output o<br>ompare mode, clear output | ut on match (CCP1IF bit is set<br>edge<br>edge<br>ng edge | ,                                      |  |  |  |  |  |  |  |

|              | is<br>110x = P                                                                                           |                                                                                                                                                                                                         | s enabled. CCP1 pin is unaffe high true.                  | MR1 is reset, and A/D conversio cted.) |  |  |  |  |  |  |  |

- **Note 1:** For Borrow, the polarity is reversed. A subtraction is executed by adding the two's complement of the second operand. For rotate (RRF, RLF) instructions, this bit is loaded with either the high-order or low-order bit of the source register.

### 8.3.3 OPERATION IN SLEEP MODE

In Sleep mode, all clock sources are disabled. Timer2 will not increment and the state of the module will not change. If the RC5/CCP1 pin is driving a value, it will continue to drive that value. When the device wakes up, it will continue from this state.

### 8.3.3.1 OPERATION WITH FAIL-SAFE CLOCK MONITOR

If the Fail-Safe Clock Monitor is enabled, a clock failure will force the CCP to be clocked from the internal oscillator clock source, which may have a different clock frequency than the primary clock.

See **Section 3.0** "**Clock Sources**" for additional details.

### 8.3.4 EFFECTS OF RESET

Any Reset will force all ports to Input mode and the CCP registers to their Reset states.

### 8.3.5 SETUP FOR PWM OPERATION

The following steps should be taken when configuring the CCP module for PWM operation:

- 1. Configure the PWM pin (RC5/CCP1) as an input by setting the TRISC<5> bit.

- 2. Set the PWM period by loading the PR2 register.

- Configure the CCP module for the PWM mode by loading the CCP1CON register with the appropriate values.

- 4. Set the PWM duty cycle by loading the CCPR1L register and CCP1CON<5:4> bits.

- 5. Configure and start TMR2:

- Clear the TMR2 interrupt flag bit by clearing the TMR2IF bit of the PIR1 Register.

- Set the TMR2 prescale value by loading the T2CKPS bits of the T2CON Register.

- Enable Timer2 by setting the TMR2ON bit of the T2CON Register.

- 6. Enable PWM output after a new PWM cycle has started:

- Wait until TMR2 overflows (TMR2IF bit is set).

- Enable the RC5/CCP1 pin output by clearing the TRISC<5> bit.

| Name    | Bit 7                                   | Bit 6        | Bit 5        | Bit 4     | Bit 3   | Bit 2     | Bit 1     | Bit 0   | Value on<br>POR, BOR | Value on all other Resets |

|---------|-----------------------------------------|--------------|--------------|-----------|---------|-----------|-----------|---------|----------------------|---------------------------|

| CCP1CON | -                                       | —            | DC1B1        | DC1B0     | CCP1M3  | CCP1M2    | CCP1M1    | CCP1M0  | 0000 0000            | 0000 0000                 |

| CCPR1L  | Capture/Compare/PWM Register 1 Low Byte |              |              |           |         | XXXX XXXX | uuuu uuuu |         |                      |                           |

| CCPR1H  | Capture/C                               | ompare/PWI   | V Register 1 | High Byte |         |           |           |         | XXXX XXXX            | uuuu uuuu                 |

| INTCON  | GIE                                     | PEIE         | TOIE         | INTE      | RAIE    | T0IF      | INTF      | RAIF    | 0000 0000            | 0000 0000                 |

| PIE1    | EEIE                                    | ADIE         | CCP1IE       | C2IE      | C1IE    | OSFIE     | TMR2IE    | TMR1IE  | 0000 0000            | 0000 0000                 |

| PIR1    | EEIF                                    | ADIF         | CCP1IF       | C2IF      | C1IF    | OSFIF     | TMR2IF    | TMR1IF  | 0000 0000            | 0000 0000                 |

| PR2     | Timer2 Mo                               | dule Period  | Register     |           |         |           |           |         | 1111 1111            | 1111 1111                 |

| T2CON   | -                                       | TOUTPS3      | TOUTPS2      | TOUTPS1   | TOUTPS0 | TMR2ON    | T2CKPS1   | T2CKPS0 | -000 0000            | -000 0000                 |

| TMR2    | Timer2 Mo                               | dule Registe | er           |           |         |           |           |         | 0000 0000            | 0000 0000                 |

| TRISC   | TRISC7                                  | TRISC6       | TRISC5       | TRISC4    | TRISC3  | TRISC2    | TRISC1    | TRISC0  | 11 1111              | 11 1111                   |

### TABLE 8-4:REGISTERS ASSOCIATED WITH CCP AND TIMER2

Legend: -= Unimplemented locations, read as '0', u = unchanged, x = unknown. Shaded cells are not used by the CCP or Timer2 modules.

NOTES:

| Mnen   | nonic, | Description                  | Qualas       |       | 14-Bit | Opcode | •    | Status   | Natas |

|--------|--------|------------------------------|--------------|-------|--------|--------|------|----------|-------|

| Oper   | ands   | Description                  | Cycles       | MSb   |        |        | LSb  | Affected | Notes |

|        |        | BYTE-ORIENTED FILE REGI      | STER OPE     | RATIO | NS     |        |      |          |       |

| ADDWF  | f, d   | Add W and f                  | 1            | 00    | 0111   | dfff   | ffff | C,DC,Z   | 1,2   |

| ANDWF  | f, d   | AND W with f                 | 1            | 00    | 0101   | dfff   | ffff | Z        | 1,2   |

| CLRF   | f      | Clear f                      | 1            | 00    | 0001   | lfff   | ffff | Z        | 2     |

| CLRW   | -      | Clear W                      | 1            | 00    | 0001   | 0xxx   | xxxx | Z        |       |

| COMF   | f, d   | Complement f                 | 1            | 00    | 1001   | dfff   | ffff | Z        | 1,2   |

| DECF   | f, d   | Decrement f                  | 1            | 00    | 0011   | dfff   | ffff | Z        | 1,2   |

| DECFSZ | f, d   | Decrement f, Skip if 0       | 1 <b>(2)</b> | 00    | 1011   | dfff   | ffff |          | 1,2,3 |

| INCF   | f, d   | Increment f                  | 1            | 00    | 1010   | dfff   | ffff | Z        | 1,2   |

| INCFSZ | f, d   | Increment f, Skip if 0       | 1 <b>(2)</b> | 00    | 1111   | dfff   | ffff |          | 1,2,3 |

| IORWF  | f, d   | Inclusive OR W with f        | 1            | 00    | 0100   | dfff   | ffff | Z        | 1,2   |

| MOVF   | f, d   | Move f                       | 1            | 00    | 1000   | dfff   | ffff | Z        | 1,2   |

| MOVWF  | f      | Move W to f                  | 1            | 00    | 0000   | lfff   | ffff |          | -     |

| NOP    | -      | No Operation                 | 1            | 00    | 0000   | 0xx0   | 0000 |          |       |

| RLF    | f, d   | Rotate Left f through Carry  | 1            | 00    | 1101   | dfff   | ffff | С        | 1,2   |

| RRF    | f, d   | Rotate Right f through Carry | 1            | 00    | 1100   | dfff   | ffff | С        | 1,2   |

| SUBWF  | f, d   | Subtract W from f            | 1            | 00    | 0010   | dfff   | ffff | C,DC,Z   | 1,2   |

| SWAPF  | f, d   | Swap nibbles in f            | 1            | 00    | 1110   | dfff   | ffff |          | 1,2   |

| XORWF  | f, d   | Exclusive OR W with f        | 1            | 00    | 0110   | dfff   | ffff | Z        | 1,2   |

|        |        | BIT-ORIENTED FILE REGIS      |              | ATION | IS     |        |      |          |       |

| BCF    | f. b   | Bit Clear f                  | 1            | 01    | 00bb   | bfff   | ffff |          | 1,2   |

| BSF    | f, b   | Bit Set f                    | 1            | 01    | 01bb   | bfff   | ffff |          | 1,2   |

| BTFSC  | f, b   | Bit Test f, Skip if Clear    | 1 (2)        | 01    | 10bb   | bfff   | ffff |          | 3     |

| BTFSS  | f, b   | Bit Test f, Skip if Set      | 1 (2)        | 01    | 11bb   | bfff   | ffff |          | 3     |

|        | , -    | LITERAL AND CONTRO           |              | IONS  |        |        |      |          | -     |

| ADDLW  | k      | Add literal and W            | 1            | 11    | 111x   | kkkk   | kkkk | C,DC,Z   |       |

| ANDLW  | k      | AND literal with W           | 1            | 11    | 1001   | kkkk   | kkkk | Z        |       |

| CALL   | k      | Call subroutine              | 2            | 10    | 0kkk   | kkkk   | kkkk |          |       |

| CLRWDT | _      | Clear Watchdog Timer         | 1            | 00    | 0000   | 0110   | 0100 | TO,PD    |       |

| GOTO   | k      | Go to address                | 2            | 10    | 1kkk   | kkkk   | kkkk | -        |       |

| IORLW  | k      | Inclusive OR literal with W  | 1            | 11    | 1000   | kkkk   | kkkk | Z        |       |

| MOVLW  | k      | Move literal to W            | 1            | 11    | 00xx   | kkkk   | kkkk |          |       |

| RETFIE | _      | Return from interrupt        | 2            | 00    | 0000   | 0000   | 1001 |          |       |

| RETLW  | k      | Return with literal in W     | 2            | 11    | 01xx   | kkkk   | kkkk |          |       |

| RETURN | -      | Return from Subroutine       | 2            | 00    | 0000   | 0000   | 1000 |          |       |

| SLEEP  | _      | Go into Standby mode         | 1            | 00    | 0000   | 0110   | 0011 | TO,PD    |       |

| SUBLW  | k      | Subtract W from literal      | 1            | 11    | 110x   | kkkk   | kkkk | C,DC,Z   |       |

| XORLW  | k      | Exclusive OR literal with W  | 1            | 11    | 1010   |        | kkkk | Z        |       |

### TABLE 17-2: PIC16F785/HV785 INSTRUCTION SET

**Note 1:** When an I/O register is modified as a function of itself (e.g., MOVF PORTA, 1), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared if assigned to the Timer0 module.

3: If Program Counter (PC) is modified, or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

### 17.2 Instruction Descriptions

| ADDLW            | Add Literal and W                                                                                                          |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] ADDLW k                                                                                                   |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                        |  |  |  |  |

| Operation:       | $(W) + k \to (W)$                                                                                                          |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                   |  |  |  |  |

| Description:     | The contents of the W register<br>are added to the eight-bit literal 'k'<br>and the result is placed in the W<br>register. |  |  |  |  |

| ANDWF            | AND W with f                                                                                                                                                    |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] ANDWF f,d                                                                                                                                      |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                 |  |  |  |  |

| Operation:       | (W) .AND. (f) $\rightarrow$ (destination)                                                                                                                       |  |  |  |  |

| Status Affected: | Z                                                                                                                                                               |  |  |  |  |

| Description:     | AND the W register with register<br>'f'. If 'd' is '0', the result is stored in<br>the W register. If 'd' is '1', the<br>result is stored back in register 'f'. |  |  |  |  |

| ADDWF            | Add W and f                                                                                                                                                                        |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ <i>label</i> ] ADDWF f,d                                                                                                                                                         |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                    |  |  |  |

| Operation:       | (W) + (f) $\rightarrow$ (destination)                                                                                                                                              |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                                                                           |  |  |  |

| Description:     | Add the contents of the W register<br>with register 'f'. If 'd' is '0', the<br>result is stored in the W register. If<br>'d' is '1', the result is stored back<br>in register 'f'. |  |  |  |

| BCF              | Bit Clear f                                                         |  |  |  |

|------------------|---------------------------------------------------------------------|--|--|--|

| Syntax:          | [ <i>label</i> ] BCF f,b                                            |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |  |  |  |

| Operation:       | $0 \rightarrow (f < b >)$                                           |  |  |  |

| Status Affected: | None                                                                |  |  |  |

| Description:     | Bit 'b' in register 'f' is cleared.                                 |  |  |  |

| ANDLW            | AND Literal with W                                                                                                     |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ <i>label</i> ] ANDLW k                                                                                               |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                    |  |  |  |

| Operation:       | (W) .AND. (k) $\rightarrow$ (W)                                                                                        |  |  |  |

| Status Affected: | Z                                                                                                                      |  |  |  |

| Description:     | The contents of W register are<br>AND'ed with the eight-bit literal<br>'k'. The result is placed in the W<br>register. |  |  |  |

| BSF              | Bit Set f                                                           |  |  |  |

|------------------|---------------------------------------------------------------------|--|--|--|

| Syntax:          | [ <i>label</i> ] BSF f,b                                            |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |  |  |  |

| Operation:       | $1 \rightarrow (f < b >)$                                           |  |  |  |

| Status Affected: | None                                                                |  |  |  |

| Description:     | Bit 'b' in register 'f' is set.                                     |  |  |  |

| IORLW            | Inclusive OR Literal with W                                                                                               |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] IORLW k                                                                                                  |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                       |  |  |  |  |

| Operation:       | (W) .OR. $k \rightarrow$ (W)                                                                                              |  |  |  |  |

| Status Affected: | Z                                                                                                                         |  |  |  |  |

| Description:     | The contents of the W register<br>are OR'ed with the eight-bit literal<br>'k'. The result is placed in the W<br>register. |  |  |  |  |

| IORWF            | Inclusive OR W with f                                                                                                                                                       |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] IORWF f,d                                                                                                                                                  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                                 |  |  |  |  |

| Operation:       | (W) .OR. (f) $\rightarrow$ (destination)                                                                                                                                    |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                           |  |  |  |  |

| Description:     | Inclusive OR the W register with<br>register 'f'. If 'd' is '0', the result is<br>placed in the W register. If 'd' is<br>'1', the result is placed back in<br>register 'f'. |  |  |  |  |

| Syntax:                            | [ label ]                                                                                          | MOVLV        | V k           |      |  |

|------------------------------------|----------------------------------------------------------------------------------------------------|--------------|---------------|------|--|

| Operands:                          | $0 \le k \le 255$                                                                                  |              |               |      |  |

| Operation:                         | $k \rightarrow (W)$                                                                                |              |               |      |  |

| Status Affected:                   | None                                                                                               |              |               |      |  |

| Encoding:                          | 11                                                                                                 | 00xx         | kkkk          | kkkk |  |

|                                    | The eight-bit literal 'k' is loaded<br>into W register. The "don't cares"<br>will assemble as 0's. |              |               |      |  |

| MOVWF                              | will asse<br>Move W                                                                                |              | 0' <b>s</b> . |      |  |

| <b>MOVWF</b><br>Syntax:            |                                                                                                    | to f         |               |      |  |

|                                    | Move W                                                                                             | to f<br>MOVW |               |      |  |

| Syntax:                            | Move W                                                                                             | to f<br>MOVW |               |      |  |

| Syntax:<br>Operands:               | Move W<br>[ <i>label</i> ]<br>0 ≤ f ≤ 12                                                           | to f<br>MOVW |               |      |  |

| Syntax:<br>Operands:<br>Operation: | Move W<br>[ label ]<br>$0 \le f \le 12$<br>(W) $\rightarrow$ (f                                    | to f<br>MOVW |               | ffff |  |

Move Literal to W

MOVLW

Description:

Move data from W register to register 'f'.

| MOVF             | Move f                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [label] MOVF f,d                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                                                                                                               |  |  |  |  |  |  |

| Operation:       | $(f) \rightarrow (dest)$                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

| Encoding:        | 00 1000 dfff ffff                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

| Description:     | The contents of register 'f' is<br>moved to a destination depen-<br>dent upon the status of 'd'. If 'd' =<br>0, destination is W register. If 'd'<br>= 1, the destination is file register<br>'f' itself. 'd' = 1 is useful to test a<br>file register since status flag Z is |  |  |  |  |  |  |

affected.

| NOP              | No Operation  |      |      |      |  |  |

|------------------|---------------|------|------|------|--|--|

| Syntax:          | [ label ]     | NOP  |      |      |  |  |

| Operands:        | None          |      |      |      |  |  |

| Operation:       | No operation  |      |      |      |  |  |

| Status Affected: | None          |      |      |      |  |  |

| Encoding:        | 00            | 0000 | 0xx0 | 0000 |  |  |

| Description:     | No operation. |      |      |      |  |  |

### 18.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers are supported with a full range of hardware and software development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> IDE Software

- Assemblers/Compilers/Linkers

- MPASM<sup>™</sup> Assembler

- MPLAB C18 and MPLAB C30 C Compilers

- MPLINK<sup>™</sup> Object Linker/

- MPLIB™ Object Librarian

- MPLAB ASM30 Assembler/Linker/Library

- Simulators

- MPLAB SIM Software Simulator

- Emulators

- MPLAB ICE 2000 In-Circuit Emulator

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debugger

- MPLAB ICD 2

- Device Programmers

- PICSTART<sup>®</sup> Plus Development Programmer

- MPLAB PM3 Device Programmer

- PICkit<sup>™</sup> 2 Development Programmer

- Low-Cost Demonstration and Development Boards and Evaluation Kits

### 18.1 MPLAB Integrated Development Environment Software

The MPLAB IDE software brings an ease of software development previously unseen in the 8/16-bit microcontroller market. The MPLAB IDE is a Windows<sup>®</sup> operating system-based application that contains:

- A single graphical interface to all debugging tools

- Simulator

- Programmer (sold separately)

- Emulator (sold separately)

- In-Circuit Debugger (sold separately)

- · A full-featured editor with color-coded context

- A multiple project manager

- Customizable data windows with direct edit of contents

- High-level source code debugging

- Visual device initializer for easy register initialization

- Mouse over variable inspection

- Drag and drop variables from source to watch windows

- · Extensive on-line help

- Integration of select third party tools, such as HI-TECH Software C Compilers and IAR C Compilers

The MPLAB IDE allows you to:

- Edit your source files (either assembly or C)

- One touch assemble (or compile) and download to PIC MCU emulator and simulator tools (automatically updates all project information)

- Debug using:

- Source files (assembly or C)

- Mixed assembly and C

- Machine code

MPLAB IDE supports multiple debugging tools in a single development paradigm, from the cost-effective simulators, through low-cost in-circuit debuggers, to full-featured emulators. This eliminates the learning curve when upgrading to tools with increased flexibility and power.

### 19.3 DC Characteristics: PIC16F785/HV785-E (Extended)<sup>(1), (2)</sup>

| DC CHA | ARACTERISTICS          | <b>Standard Operating Conditions (unless otherwise stated)</b> Operating temperature $-40^{\circ}C \le Ta \le +125^{\circ}C$ for extended |      |      |            |     |                    |

|--------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|------|------|------------|-----|--------------------|

| Param  |                        | <b>_</b> .                                                                                                                                |      |      | Conditions |     |                    |

| No.    | Device Characteristics | Min                                                                                                                                       | Тур† | Мах  | Units      | Vdd |                    |

| D010E  | Supply Current (IDD)   | —                                                                                                                                         | 11   | 23   | μA         | 2.0 | Fosc = 32 kHz      |

|        |                        | —                                                                                                                                         | 18   | 38   | μA         | 3.0 | LP Oscillator mode |

|        |                        | _                                                                                                                                         | 35   | 75   | μA         | 5.0 |                    |

| D011E  |                        | —                                                                                                                                         | 140  | 240  | μA         | 2.0 | Fosc = 1 MHz       |

|        |                        | —                                                                                                                                         | 220  | 380  | μΑ         | 3.0 | XT Oscillator mode |

|        |                        | _                                                                                                                                         | 380  | 550  | μA         | 5.0 |                    |

| D012E  |                        | —                                                                                                                                         | 260  | 360  | μA         | 2.0 | Fosc = 4 MHz       |

|        |                        | —                                                                                                                                         | 420  | 650  | μΑ         | 3.0 | XT Oscillator mode |

|        |                        | —                                                                                                                                         | 0.8  | 1.1  | mA         | 5.0 |                    |

| D013E  |                        | —                                                                                                                                         | 130  | 220  | μA         | 2.0 | Fosc = 1 MHz       |

|        |                        | —                                                                                                                                         | 215  | 360  | μA         | 3.0 | EC Oscillator mode |

|        |                        | —                                                                                                                                         | 360  | 520  | μA         | 5.0 |                    |

| D014E  |                        | —                                                                                                                                         | 220  | 340  | μA         | 2.0 | Fosc = 4 MHz       |

|        |                        | —                                                                                                                                         | 375  | 550  | μA         | 3.0 | EC Oscillator mode |

|        |                        | —                                                                                                                                         | 0.65 | 1.0  | mA         | 5.0 |                    |

| D015E  |                        | —                                                                                                                                         | 8    | 20   | μA         | 2.0 | Fosc = 31 kHz      |

|        |                        | —                                                                                                                                         | 16   | 40   | μA         | 3.0 | INTRC mode         |

|        |                        | —                                                                                                                                         | 31   | 65   | μA         | 5.0 |                    |

| D016E  |                        | —                                                                                                                                         | 340  | 450  | μA         | 2.0 | Fosc = 4 MHz       |

|        |                        | _                                                                                                                                         | 500  | 700  | μA         | 3.0 | INTOSC mode        |

|        |                        | —                                                                                                                                         | 800  | 1200 | μΑ         | 5.0 |                    |

| D017E  |                        | —                                                                                                                                         | 230  | 400  | μA         | 2.0 | Fosc = 4 MHz       |

|        |                        | —                                                                                                                                         | 400  | 680  | μA         | 3.0 | EXTRC mode         |

|        |                        | _                                                                                                                                         | 0.63 | 1.1  | mA         | 5.0 | ]                  |

| D018E  |                        | _                                                                                                                                         | 2.6  | 3.25 | mA         | 4.5 | Fosc = 20 MHz      |

|        |                        | —                                                                                                                                         | 2.8  | 3.35 | mA         | 5.0 | HS Oscillator mode |

† Data in 'Typ' column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

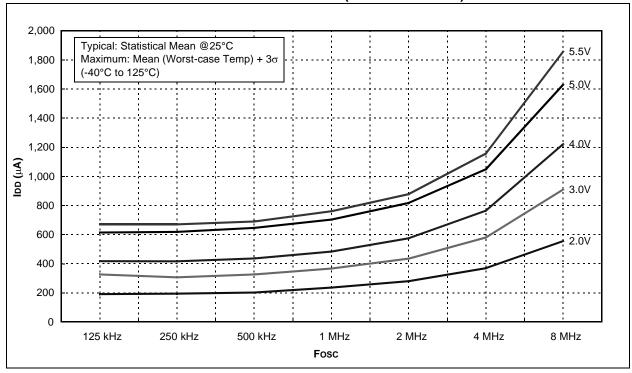

**Note 1:** The test conditions for all IDD measurements in Active Operation mode are: OSC1 = external square wave, from rail to rail; all I/O pins tri-stated, pulled to VDD; MCLR = VDD; WDT disabled.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature also have an impact on the current consumption.

3: The peripheral current is the sum of the base IDD or IPD and the additional current consumed when this peripheral is enabled. The peripheral ∆ current can be determined by subtracting the base IDD or IPD current from this limit. Max values should be used when calculating total current consumption.

4: The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD. When A/D is off, it will not consume any current other than leakage current. The power-down current spec includes any such leakage from the A/D module.

# 19.4 DC Characteristics: PIC16F785/HV785-I (Industrial), PIC16F785/HV785-E (Extended)

| DC CHARACTERISTICS |      |                                      | Standard Operating Conditions (unless otherwise stated)<br>Operating temperature-40°C $\leq$ TA $\leq$ +85°C for industrial<br>-40°C $\leq$ TA $\leq$ +125°C for extended |      |            |        |                                                                                                                               |

|--------------------|------|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------------|--------|-------------------------------------------------------------------------------------------------------------------------------|

| Param<br>No.       | Sym  | Characteristic                       | Min                                                                                                                                                                       | Тур† | Max        | Units  | Conditions                                                                                                                    |

|                    | VIL  | Input Low Voltage                    |                                                                                                                                                                           |      |            |        |                                                                                                                               |

|                    |      | I/O ports                            |                                                                                                                                                                           |      |            |        |                                                                                                                               |

| D030               |      | with TTL buffer                      | Vss                                                                                                                                                                       | —    | 0.8        | V      | $4.5V \leq V\text{DD} \leq 5.5V$                                                                                              |

| D030A              |      |                                      | Vss                                                                                                                                                                       | —    | 0.15 Vdd   | V      | Otherwise                                                                                                                     |

| D031               |      | with Schmitt Trigger buffer          | Vss                                                                                                                                                                       | —    | 0.2 Vdd    | V      | Entire range                                                                                                                  |

| D032               |      | MCLR, OSC1 (RC mode) <sup>(1)</sup>  | Vss                                                                                                                                                                       | —    | 0.2 Vdd    | V      |                                                                                                                               |

| D033               |      | OSC1 (XT and LP modes)               | Vss                                                                                                                                                                       | —    | 0.3        | V      |                                                                                                                               |

| D033A              |      | OSC1 (HS mode)                       | Vss                                                                                                                                                                       | —    | 0.3 Vdd    | V      |                                                                                                                               |

|                    | VIH  | Input High Voltage                   |                                                                                                                                                                           |      |            |        |                                                                                                                               |

|                    |      | I/O ports                            |                                                                                                                                                                           |      |            |        |                                                                                                                               |

| D040<br>D040A      |      | with TTL buffer                      | 2.0<br>(0.25 Vdd + 0.8)                                                                                                                                                   | _    | Vdd<br>Vdd | V<br>V | $4.5V \le VDD \le 5.5V$<br>Otherwise                                                                                          |

| D041               |      | with Schmitt Trigger buffer          | 0.8 Vdd                                                                                                                                                                   | —    | Vdd        | V      | Entire range                                                                                                                  |

| D042               |      | MCLR                                 | 0.8 Vdd                                                                                                                                                                   | _    | Vdd        | V      |                                                                                                                               |

| D043               |      | OSC1 (XT and LP modes)               | 1.6                                                                                                                                                                       | _    | Vdd        | V      |                                                                                                                               |

| D043A              |      | OSC1 (HS mode)                       | 0.7 Vdd                                                                                                                                                                   | _    | Vdd        | V      |                                                                                                                               |

| D043B              |      | OSC1 (RC mode)                       | 0.9 Vdd                                                                                                                                                                   | _    | Vdd        | V      | (Note 1)                                                                                                                      |

| D070               | IPUR | PORTA Weak Pull-up Current           | 50*                                                                                                                                                                       | 250  | 400*       | μA     | VDD = 5.0V, VPIN = VSS                                                                                                        |

|                    | lı∟  | Input Leakage Current <sup>(2)</sup> |                                                                                                                                                                           |      | J          |        | l                                                                                                                             |

| D060               |      | I/O ports                            | —                                                                                                                                                                         | ±0.1 | ±1         | μΑ     | $\label{eq:VSS} \begin{split} &V{\sf SS} \leq V{\sf PIN} \leq V{\sf DD}, \\ &P{\sf in} \mbox{ at high-impedance} \end{split}$ |

| D060A              |      | Analog inputs                        | _                                                                                                                                                                         | ±0.1 | ±1         | μA     | $VSS \le VPIN \le VDD$                                                                                                        |

| D060B              |      | VREF                                 | _                                                                                                                                                                         | ±0.1 | ±1         | μA     | $VSS \le VPIN \le VDD$                                                                                                        |

| D061               |      | MCLR <sup>(3)</sup>                  | _                                                                                                                                                                         | ±0.1 | ±5         | μA     | $VSS \le VPIN \le VDD$                                                                                                        |

| D063               |      | OSC1                                 | —                                                                                                                                                                         | ±0.1 | ±5         | μA     | Vss $\leq$ VPIN $\leq$ VDD, XT, HS and LP osc configuration                                                                   |

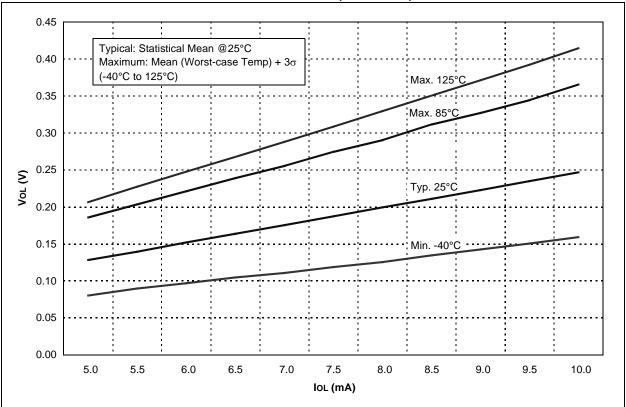

|                    | Vol  | Output Low Voltage                   |                                                                                                                                                                           |      |            |        |                                                                                                                               |

| D080               |      | I/O ports                            | _                                                                                                                                                                         | _    | 0.6        | V      | IOL = 8.5 mA, VDD = 4.5V                                                                                                      |

| D083               |      | OSC2/CLKOUT (RC mode)                | —                                                                                                                                                                         | _    | 0.6        | V      | IOL = 1.6 mA, VDD = 4.5V (Ind.)<br>IOL = 1.2 mA, VDD = 4.5V (Ext.)                                                            |

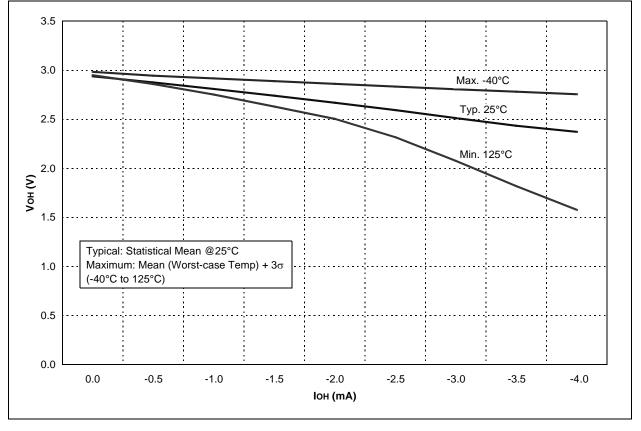

|                    | Vон  | Output High Voltage                  |                                                                                                                                                                           |      |            |        |                                                                                                                               |

| D090               |      | I/O ports                            | Vdd - 0.7                                                                                                                                                                 | _    | _          | V      | IOH = -3.0 mA, VDD = 4.5V                                                                                                     |

| D092               |      | OSC2/CLKOUT (RC mode)                | Vdd - 0.7                                                                                                                                                                 | —    | —          | V      | IOH = -1.3 mA, VDD = 4.5V (Ind.<br>IOH = -1.0 mA, VDD = 4.5V (Ext.                                                            |

| D193*              | Vod  | Open-Drain High Voltage              |                                                                                                                                                                           |      | 8.5        | V      | RB6 pin                                                                                                                       |

These parameters are characterized but not tested.

† Data in 'Typ' column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended to use an external clock in RC mode.

2: Negative current is defined as current sourced by the pin.

3: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

4: See Section 14.4.1 "Using the Data EEPROM" on page 105.

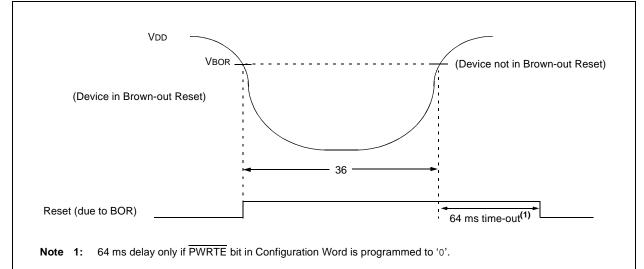

### FIGURE 19-6: BROWN-OUT RESET TIMING AND CHARACTERISTICS

## TABLE 19-4:RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER<br/>AND BROWN-OUT RESET REQUIREMENTS

| Param<br>No. | Sym   | Characteristic                                              | Min   | Тур†      | Max   | Units | Conditions                 |

|--------------|-------|-------------------------------------------------------------|-------|-----------|-------|-------|----------------------------|

| 30           | TMCL  | MCLR Pulse Width (low)                                      | 2     | _         | _     | μS    | VDD = 5.0V, -40°C to +85°C |

|              |       |                                                             | 11    | 18        | 24    | μS    | Extended temperature       |

| 31           | TWDT  | Watchdog Timer Time-out Period                              | 10    | 17        | 25    | ms    | VDD = 5.0V, -40°C to +85°C |

|              |       | (No Prescaler)                                              | 10    | 17        | 30    | ms    | Extended temperature       |

| 32           | Tost  | Oscillation Start-up Timer Period                           | _     | 1024 Tosc | _     | _     | Tosc = OSC1 period         |

| 33*          | TPWRT | Power-up Timer Period                                       | 28*   | 64        | 132*  | ms    | VDD = 5.0V, -40°C to +85°C |

| 34           | Tioz  | I/O High-impedance from MCLR<br>Low or Watchdog Timer Reset | —     | —         | 2.0   | μS    |                            |

| 35           | VBOR  | Brown-out Reset Voltage                                     | 2.025 | _         | 2.175 | V     |                            |

| 36           | TBOR  | Brown-out Reset Pulse Width                                 | 100*  | —         | _     | μS    | $VDD \le VBOR (D005)$      |

\* These parameters are characterized but not tested.

† Data in 'Typ' column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

FIGURE 20-12: MAXIMUM IDD vs. Fosc OVER VDD (HFINTOSC MODE)

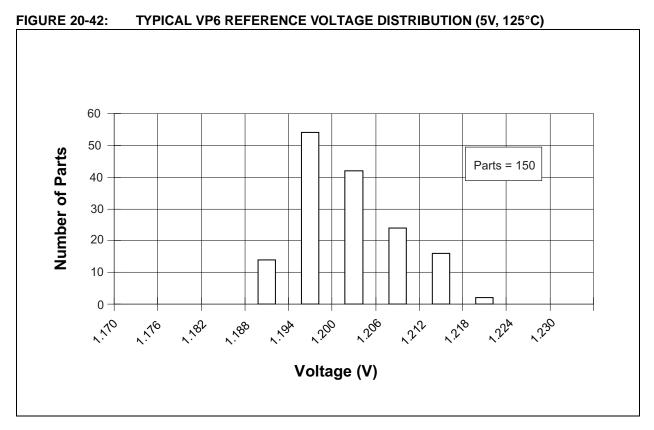

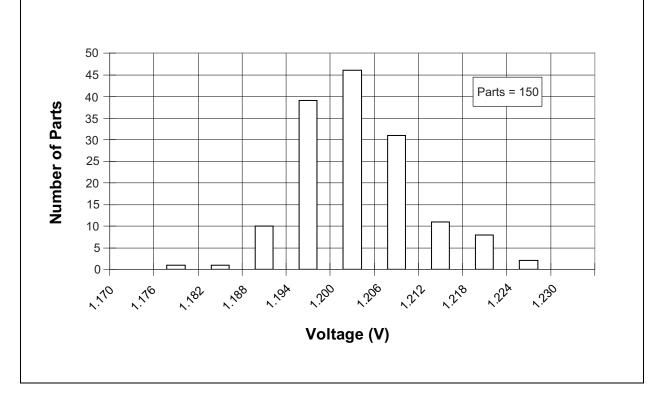

FIGURE 20-43: TYPICAL VP6 REFERENCE VOLTAGE DISTRIBUTION (5V, -40°C)

NOTES:

### Μ

| MCLR               |   |

|--------------------|---|

| Internal           |   |

|                    | 9 |

| Data               | 9 |

| Data EEPROM Memory |   |

| Program            | 9 |

|                    |   |

### 0

| OPA2CON Register                         |

|------------------------------------------|

| OPCODE Field Descriptions                |

| AC Specifications                        |

| Associated Registers                     |

| DC Specifications                        |

| OPTION_REG Register                      |

| OSCCON Register                          |

| Oscillator                               |

|                                          |

| Associated Registers                     |

| Oscillator Specifications151             |

| Oscillator Start-up Timer (OST)          |

| Specifications154                        |

| Oscillator Switching                     |

| Fail-Safe Clock Monitor                  |

| Two-Speed Clock Start-up                 |

| OSCTUNE                                  |

| Oscillator Tuning Register (Address 90h) |

### Ρ

| Packaging                            |        |

|--------------------------------------|--------|

| PCL and PCLATH                       | 21     |

| Stack                                |        |

| PCON                                 |        |

| Power Control Register (Address      |        |

| 8Eh)                                 |        |

| PCON Register                        |        |

| PICSTART Plus Development Programmer |        |

| PIE1 Register                        |        |

| Pin Diagram                          |        |

| Pinout Descriptions                  | , -    |

| PIC16F684                            | 6      |

| PIR1 Register                        |        |

| PORTA                                |        |

| Additional Pin Functions             |        |

| Interrupt-on-change                  |        |

| Weak Pull-up                         |        |

| Associated Registers                 |        |

| Pin Descriptions and Diagrams        |        |

| RA0                                  |        |

| RA1                                  |        |

| RA2                                  |        |

| RA3                                  |        |

| RA4                                  |        |

| RA5                                  |        |

| Specifications                       | -      |

| PORTB                                |        |

| Associated Registers                 |        |

| Pin Descriptions and Diagrams        |        |

| RB4                                  |        |

| RB5                                  |        |

| RB6                                  |        |

| RB7                                  |        |

| PORTC                                |        |

| Associated Registers                 |        |

| Associated Neglsters                 | 54, 40 |

| Pin Descriptions and Diagrams            | 46  |

|------------------------------------------|-----|

| RC0                                      | 46  |

| RC1                                      | 46  |

| RC2                                      | 47  |

| RC3                                      | 47  |

| RC4                                      | 47  |

| RC5                                      | 48  |

| RC6                                      | 46  |

| RC7                                      | 46  |

| Specifications                           | 152 |

| Power-Down Mode (Sleep)                  | 123 |

| Power-up Timer (PWRT)                    | 110 |

| Specifications                           | 154 |

| Power-up Timing Delays                   | 112 |

| Precision Internal Oscillator Parameters | 153 |

| Prescaler                                |     |

| Shared WDT/Timer0                        | 50  |

| Switching Prescaler Assignment           | 50  |