Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

## **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                                             |

|--------------------------------|-----------------------------------------------------------------------------|

| Product Status                 | Obsolete                                                                    |

| Number of LABs/CLBs            | 160                                                                         |

| Number of Logic Elements/Cells | 1280                                                                        |

| Total RAM Bits                 | 65536                                                                       |

| Number of I/O                  | 67                                                                          |

| Number of Gates                | -                                                                           |

| Voltage - Supply               | 1.14V ~ 1.26V                                                               |

| Mounting Type                  | Surface Mount                                                               |

| Operating Temperature          | 0°C ~ 70°C (TA)                                                             |

| Package / Case                 | 84-VFQFN Dual Rows, Exposed Pad                                             |

| Supplier Device Package        | 84-QFN (7x7)                                                                |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/ice65l01f-lqn84c |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Packaging Options**

iCE65 components are available in a variety of package options to support specific application requirements. The available options, including the number of available user-programmable I/O pins (PIOs), are listed in Table 2. Fully-tested Known-Good Die (KGD) DiePlus <sup>™</sup> are available for die stacking and highly space-conscious applications. All iCE65 devices are provided exclusively in Pb-free, RoHS-compliant packages.

Table 2: iCE65 Family Packaging Options, Maximum I/O per Package

| Package                             | Package<br>Body<br>(mm)   | Package<br>Code | Ball/Lead<br>Pitch<br>(mm) | 65L01           | 65L04                        | 65L08                  |

|-------------------------------------|---------------------------|-----------------|----------------------------|-----------------|------------------------------|------------------------|

| 81-ball chip-scale BGA              | 5 x 5                     | CB81            | 0.5                        | 63 <i>(0)</i>   | _                            | _                      |

| 84-pin quad flat no-lead package    | 7 x 7                     | QN84            | 0.5                        | 67 <i>(0)</i>   | _                            | _                      |

| 100-pin very thin quad flat package | 14 x 14                   | VQ100           | 0.5                        | 72 <i>(0)</i> 😓 | <del>_</del> > 72 <i>(9)</i> | _                      |

| 121-ball chip-scale BGA             | 6 x 6                     | CB121           |                            | 92 <i>(0)</i>   |                              | _                      |

| 132-ball chip-scale BGA             | 8 x 8                     | CB132           | 0.5                        | U 2 ///) :      | 95 (11)                      | > 95 <i>(12)</i>       |

| 196-ball chip-scale BGA             | 8 x 8                     | CB196           | 0.5                        | _ `             | 150 (18)                     | 1 FO (10)              |

| 284-ball chip-scale BGA             | 12 x 12                   | CB284           |                            | _               | 176 <i>(20)</i> 📛            | <b>222</b> <i>(25)</i> |

| Known Good Die                      | See DiePlus<br>data sheet | DI              | _                          | 95 <i>(0)</i>   | 176 <i>(20)</i>              | 222 <i>(25)</i>        |

= Common footprint allows each density migration on the same printed circuit board. (Differential input count).

The iCE65L04 and the iCE65L08 are both available in the CB196 package and have similar footprints but are not completely pin compatible. See "Pinout Differences between iCE65L04 and iCE65L08 in CB196 Package" on page 73 for more information.

When iCE65 components are supplied in the same package style, devices of different gate densities share a common footprint. The common footprint improves manufacturing flexibility. Different models of the same product can share a common circuit board. Feature-rich versions of the end application mount a larger iCE65 device on the circuit board. Low-end versions mount a smaller iCE65 device.

## **Look-Up Table (LUT4)**

The four-input Look-Up Table (LUT4) function implements any and all combinational logic functions, regardless of complexity, of between zero and four inputs. Zero-input functions include "High" (1) and "Low" (0). The LUT4 function has four inputs, labeled IO, II, I2, and I3. Three of the four inputs are shared with the Carry Logic function, as shown in Figure 4. The bottom-most LUT4 input connects either to the I3 input or to the Carry Logic output from the previous Logic Cell.

The output from the LUT4 function connects to the flip-flop within the same Logic Cell. The LUT4 output or the flip-flop output then connects to the programmable interconnect.

For detailed LUT4 internal timing, see Table 54.

## **'D'-style Flip-Flop (DFF)**

The 'D'-style flip-flop (DFF) optionally stores state information for the application.

The flip-flop has a data input, 'D', and a data output, 'Q'. Additionally, each flip-flop has up to three control signals that are shared among all flip-flops in all Logic Cells within the PLB, as shown in Figure 4. Table 3 describes the behavior of the flip-flop based on inputs and upon the specific DFF design primitive used or synthesized.

Table 3: 'D'-Style Flip-Flop Behavior

| DFF       |                                         | Flip-Flop             | Flip-Flop Inputs |    |    |          |   |

|-----------|-----------------------------------------|-----------------------|------------------|----|----|----------|---|

| Primitive | Operation                               | Mode                  | D                | EN | SR | CLK      | Q |

| All       | Cleared Immediately after Configuration | X                     | Χ                | Χ  | Χ  | X        | 0 |

|           | Hold Present Value<br>(Disabled)        |                       | Χ                | 0  | Χ  | Χ        | Q |

|           | Hold Present Value (Static Clock)       |                       | Χ                | Χ  | Χ  | 1 or 0   | Q |

|           | Load with Input Data                    |                       | D                | 1* | 0* | <b>↑</b> | D |

| SB_DFFR   | Asynchronous Reset                      | Asynchronous<br>Reset | Χ                | Χ  | 1  | Χ        | 0 |

| SB_DFFS   | Asynchronous Set                        | Asynchronous<br>Set   | Χ                | Χ  | 1  | X        | 1 |

| SB_DFFSR  | Synchronous Reset                       | Synchronous<br>Reset  | Χ                | 1* | 1  | 1        | 0 |

| SB_DFFSS  | Synchronous Set                         | Synchronous<br>Set    | Χ                | 1* | 1  | <b>†</b> | 1 |

X = don't care,  $\uparrow = rising$  clock edge (default polarity),  $1^* = High$  or unused,  $0^* = Low$  or unused

The CLK clock signal is not optional and is shared among all flip-flops in a Programmable Logic Block. By default, flip-flops are clocked by the rising edge of the PLB clock input, although the clock polarity can be inverted for all the flip-flops in the PLB.

The CLK input optionally connects to one of the following clock sources.

- The output from any one of the eight Global Buffers, or

- A connection from the general-purpose interconnect fabric

The EN clock-enable signal is common to all Logic Cells in a Programmable Logic Block. If the enable signal is not used, then the flip-flop is always enabled. This condition is indicated as "1\*" in Table 3. The asterisk indicates that this is the default state if the control signal is not connected in the application.

Similarly, the SR set/reset signal is common to all Logic Cells in a Programmable Logic Block. If not used, then the flip-flop is never set/reset, except when cleared immediately after configuration or by the Global Reset signal. This condition is indicated as "0\*" in Table 3. The asterisk indicates that this is the default state if the control signal is not connected in the application.

## Programmable Input/Output Block (PIO)

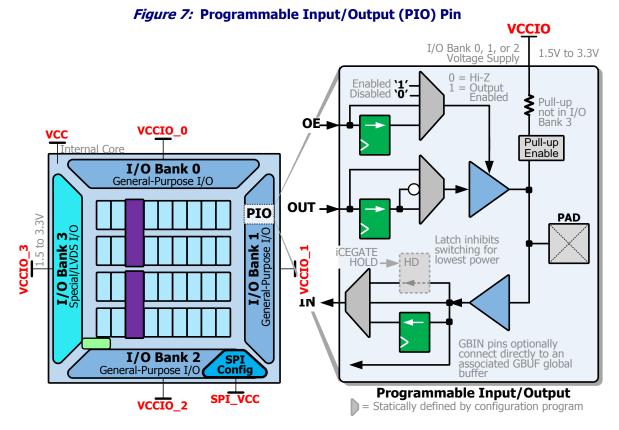

Programmable Input/Output (PIO) blocks surround the periphery of the device and connect external components to the Programmable Logic Blocks (PLBs) and RAM4K blocks via programmable interconnect. Individual PIO pins are grouped into one of four I/O banks, as shown in Figure 7. I/O Bank 3 has additional capabilities, including LVDS differential I/O and the ability to interface to Mobile DDR memories.

Figure 7 also shows the logic within a PIO pin. When used in an application, a PIO pin becomes a signal input, an output, or a bidirectional I/O pin with a separate direction control input.

#### I/O Banks

PIO blocks are organized into four separate I/O banks, each with its own voltage supply input, as shown in Table 5. The voltage applied to the VCCIO pin on a bank defines the I/O standard used within the bank. Table 50 and Table 51 describe the I/O drive capabilities and switching thresholds by I/O standard. On iCE65L04 and iCE65L08 devices, I/O Bank 3, along the left edge of the die, is different than the others and supports specialized I/O standards.

#### I/O Bank Voltage Supply Inputs Support Different I/O Standards

Because each I/O bank has its own voltage supply, iCE65 components become the ideal bridging device between different interface standards. For example, the iCE65 device allows a 1.8V-only processor to interface cleanly with a 3.3V bus interface. The iCE65 device replaces external voltage translators.

Table 5: Supported Voltages by I/O Bank

| Bank | Device Edge  | Supply Input | 3.3V | 2.5V | 1.8V | 1.5V                   |

|------|--------------|--------------|------|------|------|------------------------|

| 0    | Тор          | VCCIO_0      | Yes  | Yes  | Yes  | Outputs only           |

| 1    | Right        | VCCIO_1      | Yes  | Yes  | Yes  | Outputs only           |

| 2    | Bottom       | VCCIO_2      | Yes  | Yes  | Yes  | Outputs only           |

| 3    | Left         | VCCIO_3      | Yes  | Yes  | Yes  | iCE65L01: Outputs only |

|      |              |              |      |      |      | iCE65L04/08: Yes       |

| SPI  | Bottom Right | SPI_VCC      | Yes  | Yes  | Yes  | No                     |

If not connected to an external SPI PROM, the four pins associated with the SPI Master Configuration Interface can be used as PIO pins, supplied by the SPI\_VCC input, essentially forming a fifth "mini" I/O bank. If using an SPI Flash PROM, then connect SPI VCC to 3.3V.

### I/O Banks 0, 1, 2, SPI and Bank 3 of iCE65L01

Table 6 highlights the available I/O standards when using an iCE65 device, indicating the drive current options, and in which bank(s) the standard is supported. I/O Banks 0, 1, 2 and SPI interface support the same standards. I/O Bank 3 has additional capabilities in iCE65L04 and iCE65L08, including support for MDDR memory standards and LVDS differential I/O.

Table 6: I/O Standards for I/O Banks 0, 1, 2, SPI Interface Bank, and Bank 3 of iCE65L01

| I/O Standard       | Supply Voltage | Drive Current (mA) | Attribute Name |

|--------------------|----------------|--------------------|----------------|

| 5V Input Tolerance | 3.3V           | N/A                | N/A            |

| LVCMOS33           | 3.3V           | ±11                |                |

| LVCMOS25           | 2.5V           | ±8                 | SB LVCMOS      |

| LVCMOS18           | 1.8V           | ±5                 | 3B_LVCMO3      |

| LVCMOS15 outputs   | 1.5V           | ±4                 |                |

### IBIS Models for I/O Banks 0, 1, 2 and the SPI Bank

The IBIS (I/O Buffer Information Specification) file that describes the output buffers used in I/O Banks 0, 1, 2, SPI Bank and Bank 3 of iCE65L01 is available from the following link.

■ IBIS Models for I/O Banks 0, 1, 2, SPI Bank and Bank 3 of iCE65L01

#### I/O Bank 3 of iCE65L04 and iCE65L08

I/O Bank 3, located along the left edge of the die, has additional special I/O capabilities to support memory components and differential I/O signaling (LVDS). Table 7 lists the various I/O standards supported by I/O Bank 3. The SSTL2 and SSTL18 I/O standards require the VREF voltage reference input pin which is only available on the CB284 package. Also see Table 51 for electrical characteristics.

Table 7: I/O Standards for I/O Bank 3 Only of iCE65L04 and iCE65L08

|              | Supply  | VREF Pin (CB284 or | Target             |                  |

|--------------|---------|--------------------|--------------------|------------------|

| I/O Standard | Voltage | DiePlus) Required? | Drive Current (mA) | Attribute Name   |

| LVCMOS33     | 3.3V    | No                 | ±8                 | SB_LVCMOS33_8    |

|              |         | No                 | ±16                | SB_LVCMOS25_16   |

| LVCMOS25     | 2.5V    |                    | ±12                | SB_LVCMOS25_12   |

| LVCMOSZS     | 2.50    |                    | ±8                 | SB_LVCMOS25_8    |

|              |         |                    | ±4                 | SB_LVCMOS25_4    |

|              |         | No                 | ±10                | SB_LVCMOS18_10   |

| LVCMOS18     | 1.8V    |                    | ±8                 | SB_LVCMOS18_8    |

| LVCI40210    | 1.00    |                    | ±4                 | SB_LVCMOS18_4    |

|              |         |                    | ±2                 | SB_LVCMOS18_2    |

| LVCMOS15     | 1.5V    | No                 | ±4                 | SB_LVCMOS15_4    |

| LVCMOSTS     | 1.50    |                    | ±2                 | SB_LVCMOS15_2    |

| SSTL2_II     | 2.5V    | Yes                | ±16.2              | SB_SSTL2_CLASS_2 |

| SSTL2_I      | 2.50    |                    | ±8.1               | SB_SSTL2_CLASS_1 |

| SSTL18_II    | 1.8V    | Yes                | ±13.4              | SB_SSTL18_FULL   |

| SSTL18_I     | 1.00    |                    | ±6.7               | SB_SSTL18_HALF   |

|              |         | No                 | ±10                | SB_MDDR10        |

| MDDR         | 1 0\/   |                    | ±8                 | SB_MDDR8         |

| אטטויו       | 1.8V    |                    | ±4                 | SB_MDDR4         |

|              |         |                    | ±2                 | SB_MDDR2         |

| LVDS         | 2.5V    | No                 | N/A                | SB_LVDS_INPUT    |

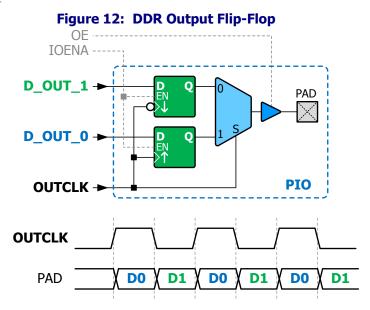

## **Double Data Rate (DDR) Flip-Flops**

Each individual PIO pin optionally has two sets of double data rate (DDR) flip-flops; one input pair and one output pair. Figure 12 demonstrates the functionality of the output DDR flip-flop. Two signals from within the iCE65 device drive the DDR output flip-flop. The D\_OUT\_0 signal is clocked by the rising edge of the OUTCLK signal while the D\_OUT\_1 signal is clocked by the falling edge of the OUTCLK signal, assuming no optional clock polarity inversion. Internally, the two individual flip-flops are multiplexed together before the data appears at the pad, effectively doubling the output data rate.

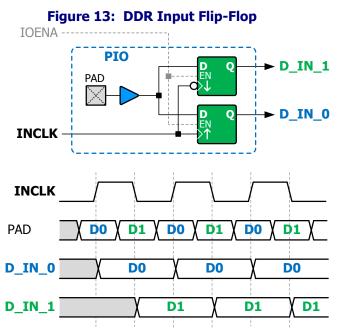

Similarly, Figure 13 demonstrates the DDR input flip-flop functionality. A double data rate (DDR) signal arrives at the pad. Internally, one value is clocked by the rising edge of the INCLK signal and another value is clocked by the falling edge of the INCLK signal. The DDR data stream is effectively de-multiplexed within the PIO pin and presented to the programmable interconnect on D\_IN\_0 and D\_IN\_1.

The DDR flip-flops provide several design advantages. Internally within the iCE65 device, the clock frequency is half the effective external data rate. The lower clock frequency eases internal timing, doubling the clock period, and slashes the clock-related power in half.

## Automatic Global Buffer Insertion, Manual Insertion

The iCEcube development software automatically assigns high-fanout signals to a global buffer. However, to manual insert a global buffer input/global buffer (GBIN/GBUF) combination, use the **SB\_IO\_GB** primitive. To insert just a global buffer (GBUF), use the **SB\_GB** primitive.

#### Global Hi-Z Control

The global high-impedance control signal, GHIZ, connects to all I/O pins on the iCE65 device. This GHIZ signal is automatically asserted throughout the configuration process, forcing all user-I/O pins into their high-impedance state. Similarly, the PIO pins can be forced into their high-impedance state via the JTAG controller.

#### **Global Reset Control**

The global reset control signal connects to all PLB and PIO flip-flops on the iCE65 device. The global reset signal is automatically asserted throughout the configuration process, forcing all flip-flops to their defined wake-up state. For PLB flip-flops, the wake-up state is always reset, regardless of the PLB flip-flop primitive used in the application. See Table 3 for more information.

The PIO flip-flops are always reset during configuration, although the output flip-flop can be inverted before leaving the iCE65 device, as shown in Figure 11.

#### **RAM**

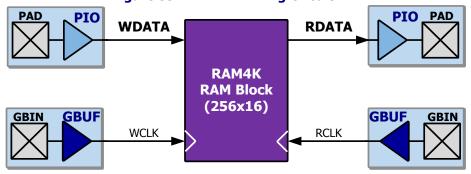

Each iCE65 device includes multiple high-speed synchronous RAM blocks (RAM4K), each 4Kbit in size. As shown in Table 16 a single iCE65 integrates between 16 to 96 such blocks. Each RAM4K block is generically a 256-word deep by 16-bit wide, two-port register file, as illustrated in Figure 17. The input and output connections, to and from a RAM4K block, feed into the programmable interconnect resources.

Figure 17: RAM4K Memory Block **Write Port Read Port RDATA[15:0]** WDATA[15:0] MASK[15:0] **WADDR[7:0] RADDR[7:0]** RAM4K **RAM Block** WE (256x16) WCLKE **RCLKE** WCLK\_\_ RCLK

Table 16: RAM4K Blocks per Device

| Device   | RAM4K Blocks | Default<br>Configuration | RAM Bits per Block | Block RAM Bits |

|----------|--------------|--------------------------|--------------------|----------------|

| iCE65L01 | 16           |                          |                    | 64K            |

| iCE65L04 | 20           | 256 x 16                 | 4K<br>(4,096)      | 80K            |

| iCE65L08 | 32           |                          | (,,,,,             | 128K           |

Using programmable logic resources, a RAM4K block implements a variety of logic functions, each with configurable input and output data width.

- Random-access memory (RAM)

- ♦ Single-port RAM with a common address, enable, and clock control lines

- ♦ Two-port RAM with separate read and write control lines, address inputs, and enable

Table 31 describes how to maintain voltage compatibility for two interface scenarios. The easiest interface is when the Application Processor's (AP) I/O supply rail and the iCE65's SPI and VCCIO\_2 bank supply rails all connect to the same voltage. The second scenario is when the AP's I/O supply voltage is greater than the iCE65's VCCIO\_2 supply voltage.

**Table 31:** CRESET\_B and CDONE Voltage Compatibility

|                                                | CRESET_B |                                  |                                              |             |                                                                                                                                                                                                                                                                                                                |

|------------------------------------------------|----------|----------------------------------|----------------------------------------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                |          | Open-                            |                                              | CDONE Pull- |                                                                                                                                                                                                                                                                                                                |

| Condition                                      | Direct   | Drain                            | Pull-up                                      | up          | Requirement                                                                                                                                                                                                                                                                                                    |

| VCCIO_AP<br>= VCC_SPI<br>VCCIO_AP<br>= VCCIO_2 | OK       | OK with<br>pull-up               | Required if<br>using<br>open-drain<br>output | Recommended | AP can directly drive CRESET_B High and Low although an open-drain output recommended is if multiple devices control CRESET_B. If using an open-drain driver, the CRESET_B input must include a 10 k $\Omega$ pull-up resistor to VCCIO_2. The 10 k $\Omega$ pull-up resistor to AP_VCCIO is also recommended. |

| AP_VCCIO<br>> VCCIO_2                          | N/A      | Required,<br>requires<br>pull-up | Required                                     | Required    | The AP must control CRESET_B with an open-drain output, which requires a $10~\text{k}\Omega$ pull-up resistor to VCCIO_2. The $10~\text{k}\Omega$ pull-up resistor to AP_VCCIO is required.                                                                                                                    |

## **JTAG Boundary Scan Port**

#### **Overview**

Each iCE65 device includes an IEEE 1149.1-compatible JTAG boundary-scan port. The port supports printed-circuit board (PCB) testing and debugging. It also provides an alternate means to configure the iCE65 device.

## **Signal Connections**

The JTAG port connections are listed in Table 32.

Table 32: iCE65 JTAG Boundary Scan Signals

| Signal | D: 11     |                                                                                                              |

|--------|-----------|--------------------------------------------------------------------------------------------------------------|

| Name   | Direction | Description                                                                                                  |

| TDI    | Input     | Test Data Input. Must be tied off to GND when unused. (no pull-up resistor)*                                 |

| TMS    | Input     | Test Mode Select. Must be tied off to GND when unused. (no pull-up resistor)*                                |

| TCK    | Input     | Test Clock. Must be tied off to GND when unused. (no pull-up resistor)*                                      |

| TDO    | Output    | Test Data Output.                                                                                            |

| TRST_B | Input     | Test Reset, active Low. Must be Low during normal device operation. Must be High to enable JTAG operations.* |

<sup>\*</sup> Must be tied off to GND or VCCIO 1, else VCCIO 1 draws current.

Table 33 lists the ball/pin numbers for the JTAG interface by package code. The JTAG interface is available in select package types. The JTAG port is located in I/O Bank 1 along the right edge of the iCE65 device and powered by the VCCIO\_1 supply inputs. Consequently, the JTAG interface uses the associated I/O standards for I/O Bank 1.

Table 33: JTAG Interface Ball/Pin Numbers by Package

| JTAG Interface | VQ100 | CB132 | CB196 | CB284 |

|----------------|-------|-------|-------|-------|

| TDI            |       | M12   | M12   | T16   |

| TMS            |       | P14   | P14   | V18   |

| TCK            | N/A   | L12   | L12   | R16   |

| TDO            |       | N14   | N14   | U18   |

| TRST_B         |       | M14   | M14   | T18   |

## **Supported JTAG Commands**

The JTAG interface supports the IEEE 1149.1 mandatory instructions, including EXTEST, SAMPLE/PRELOAD, and BYPASS.

## **Package and Pinout Information**

## Maximum User I/O Pins by Package and by I/O Bank

Table 34 lists the maximum number of user-programmable I/O pins by package, with additional detail showing user I/O pins by I/O bank. In some cases, a smaller iCE65 device is packaged in a larger package with unconnected (N.C.) pins or balls, resulting in fewer overall I/O pins. See Table 35 for device-specific I/O counts by package.

| <i>Table 34:</i> | User I/ | O by | Package, | by I | /C | ) Bank |

|------------------|---------|------|----------|------|----|--------|

|------------------|---------|------|----------|------|----|--------|

|                                 | CB81  | QN84  | VQ100   | CB132   | CB196   | CB284   |

|---------------------------------|-------|-------|---------|---------|---------|---------|

| Package Leads                   | 81    | 84    | 100     | 132     | 196     | 284     |

| Package Body (mm)               | 5 x 5 | 7 x 7 | 14 x 14 | 8 x 8   | 8 x 8   | 12 x 12 |

| Ball Array (balls)              | 9 x 9 | N/A   | N/A     | 14 x 14 | 14 x 14 | 22 x 22 |

| Ball/Lead Pitch (mm)            | 0.5   | 0.5   | 0.5     | 0.5     | 0.5     | 0.5     |

| Maximum user I/O, all I/O banks | 63    | 67    | 72      | 95      | 150     | 222     |

| PIO Pins in Bank 0              | 17    | 17    | 19      | 26      | 37      | 60      |

| PIO Pins in Bank 1              | 16    | 17    | 19      | 21      | 38      | 55      |

| PIO Pins in Bank 2              | 12    | 11    | 12      | 20      | 35      | 53      |

| PIO Pins in Bank 3              | 18    | 18    | 18      | 24      | 36      | 50      |

| PIO Pins in SPI<br>Interface    | 4     | 4     | 4       | 4       | 4       | 4       |

## **Printed Circuit Board Layout Information**

For information on how to use the iCE65 packages on a printed circuit board (PCB) design, consult the following application note.

■ AN010: iCE65 Printed Circuit Board (PCB Layout) Guidelines

### Maximum User I/O by Device and Package

Table 35 lists the maximum available user I/O by device and by and package type. Not all devices are available in all packages. Similarly, smaller iCE65 devices may have unconnected balls in some packages. Devices sharing a common package have similar footprints.

Table 35: Maximum User I/O by Device and Package

|         | Device   |          |          |  |  |  |  |

|---------|----------|----------|----------|--|--|--|--|

| Package | iCE65L01 | iCE65L04 | iCE65L08 |  |  |  |  |

| CB81    | 63       | _        | _        |  |  |  |  |

| QN84    | 67       | _        | _        |  |  |  |  |

| VQ100   | 72       | 72       |          |  |  |  |  |

| CB132   | 93       | 95       | _        |  |  |  |  |

| CB196   | _        | 150      | 150      |  |  |  |  |

| CB284   | _        | 176      | 222      |  |  |  |  |

## **iCE65 Pin Descriptions**

Table 36 lists the various iCE65 pins, alphabetically by name. The table indicates the directionality of the signal and the associated I/O bank. The table also indicates if the signal has an internal pull-up resistor enabled during configuration. Finally, the table describes the function of the pin.

| Table 36: iCE65 Pin Description |           |             |                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|---------------------------------|-----------|-------------|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Signal Name                     | Direction | I/O<br>Bank | Pull-up<br>during<br>Config | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| CDONE                           | Output    | 2           | Yes                         | Configuration Done. Dedicated output. Includes a permanent weak pull-up resistor to VCCIO_2 If driving external devices with CDONE output, connect a 10 k $\Omega$ pull-up resistor to VCCIO_2.                                                                                                                                                                                                                                                                               |  |  |

| CRESET_B                        | Input     | 2           | No                          | Configuration Reset, active Low. Dedicated input. No internal pull-up resistor. Either actively drive externally or connect a $10~\mathrm{k}\Omega$ pull-up resistor to VCCIO_2.                                                                                                                                                                                                                                                                                              |  |  |

| GBINO/PIOO<br>GBIN1/PIOO        | Input/IO  | 0           | Yes                         | Global buffer input from I/O Bank 0. Optionally, a full-featured PIO pin.                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| GBIN2/PIO1<br>GBIN3/PIO1        | Input/IO  | 1           | Yes                         | Global buffer input from I/O Bank 1. Optionally, a full-featured PIO pin.                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| GBIN4/PIO2<br>GBIN5/PIO2        | Input/IO  | 2           | Yes                         | Global buffer input from I/O Bank 2. Optionally, a full-featured PIO pin.                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| GBIN6/PIO3                      | Input/IO  | 3           | No                          | Global buffer input from I/O Bank 3. Optionally, a full-featured PIO pin.                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| GBIN7/PIO3                      | Input/IO  | 3           | No                          | Global buffer input from I/O Bank 3. Optionally, a full-featured PIO pin. Optionally, a differential clock input using the associated differential input pin.                                                                                                                                                                                                                                                                                                                 |  |  |

| GND                             | Supply    | All         | N/A                         | Ground. All must be connected.                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| PIOx_yy                         | I/O       | 0,1,2       | Yes                         | Programmable I/O pin defined by the iCE65 configuration bitstream. The 'x' number specifies the I/O bank number in which the I/O pin resides. The "yy' number specifies the I/O number in that bank.                                                                                                                                                                                                                                                                          |  |  |

| PIO2/CBSEL0                     | Input/IO  | 2           | Yes                         | Optional ColdBoot configuration SELect input, if ColdBoot mode is enabled. A full-featured PIO pin after configuration.                                                                                                                                                                                                                                                                                                                                                       |  |  |

| PIO2/CBSEL1                     | Input/IO  | 2           | Yes                         | Optional ColdBoot configuration SELect input, if ColdBoot mode is enabled. A full-featured PIO pin after configuration.                                                                                                                                                                                                                                                                                                                                                       |  |  |

| PIO3_yy/<br>DPwwz               | I/O       | 3           | No                          | Programmable I/O pin that is also half of a differential I/O pair. Only available in I/O Bank 3. The "yy" number specifies the I/O number in that bank. The "ww" number indicates the differential I/O pair. The 'z' indicates the polarity of the pin in the differential pair. 'A'=negative input. 'B'=positive input.                                                                                                                                                      |  |  |

| PIOS/SPI_SO                     | I/O       | SPI         | Yes                         | SPI Serial Output. A full-featured PIO pin after configuration.                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| PIOS /SPI_SI                    | I/O       | SPI         | Yes                         | SPI Serial Input. A full-featured PIO pin after configuration.                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| PIOS /<br>SPI_SS_B              | I/O       | SPI         | Yes                         | SPI Slave Select. Active Low. Includes an internal weak pull-up resistor to SPI_VCC during configuration. During configuration, the logic level sampled on this pin determines the configuration mode used by the iCE65 device, as shown in Figure 20. An input when sampled at the start of configuration. An input when in SPI Peripheral configuration mode (SPI_SS_B = Low). An output when in SPI Flash configuration mode. A full-featured PIO pin after configuration. |  |  |

| PIOS/<br>SPI_SCK                | I/O       | SPI         | Yes                         | SPI Slave Clock. An input when in SPI Peripheral configuration mode (SPI_SS_B = Low). An output when in SPI Flash configuration mode. A full-featured PIO pin after configuration.                                                                                                                                                                                                                                                                                            |  |  |

| TDI                             | Input     | 1           | No                          | JTAG Test Data Input. If using the JTAG interface, use a $10k\Omega$ pull-up resistor to VCCIO_1. Tie off to GND when unused.                                                                                                                                                                                                                                                                                                                                                 |  |  |

| Signal Name | Direction            | I/O<br>Bank | Pull-up<br>during<br>Config | Description                                                                                                                                                                                                   |

|-------------|----------------------|-------------|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TMS         | Input                | 1           | No                          | JTAG Test Mode Select. If using the JTAG interface, use a $10k\Omega$ pull-up resistor to VCCIO_1. Tie off to GND when unused.                                                                                |

| тск         | Input                | 1           | No                          | JTAG Test Clock. If using the JTAG interface, use a $10k\Omega$ pull-up resistor to VCCIO_1. Tie off to GND when unused.                                                                                      |

| TDO         | Output               | 1           | No                          | JTAG Test Data Output.                                                                                                                                                                                        |

| TRST_B      | Input                | 1           | No                          | JTAG Test Reset, active Low. Keep Low during normal operation; High for JTAG operation.                                                                                                                       |

| VCC         | Supply               | All         | N/A                         | Internal core voltage supply. All must be connected.                                                                                                                                                          |

| VCCIO_0     | Supply               | 0           | N/A                         | Voltage supply to I/O Bank 0. All such pins or balls on the package must be connected. Can be disconnected or turned off without affecting the Power-On Reset (POR) circuit.                                  |

| VCCIO_1     | Supply               | 1           | N/A                         | Voltage supply to I/O Bank 1. All such pins or balls on the package must be connected. Required to guarantee a valid input voltage on TRST_B JTAG pin.                                                        |

| VCCIO_2     | Supply               | 2           | N/A                         | Voltage supply to I/O Bank 2. All such pins or balls on the package must be connected. Required input to the Power-On Reset (POR) circuit.                                                                    |

| VCCIO_3     | Supply               | 3           | N/A                         | Voltage supply to I/O Bank 3. All such pins or balls on the package must be connected. Can be disconnected or turned off without affecting the Power-On Reset (POR) circuit.                                  |

| SPI_VCC     | Supply               | SPI         | N/A                         | SPI interface voltage supply input. Must have a valid voltage even if configuring from NVCM. Required input to the Power-On Reset (POR) circuit.                                                              |

| VPP_FAST    | Supply               | All         | N/A                         | Direct programming voltage supply. If unused, leave floating or unconnected during normal operation.                                                                                                          |

| VPP_2V5     | Supply               | All         | N/A                         | Programming supply voltage. When the iCE65 device is active, VPP_2V5 must be in the valid range between 2.3 V to 3.47 V to release the Power-On Reset circuit, even if the application is not using the NVCM. |

| VREF        | Voltage<br>Reference | 3           | N/A                         | Input reference voltage in I/O Bank 3 for the SSTL I/O standard. This pin only appears on the CB284 package and for die-based products.                                                                       |

N/A = Not Applicable

## **iCE65 Package Footprint Diagram Conventions**

Figure 31 illustrates the naming conventions used in the following footprint diagrams. Each PIO pin is associated with an I/O Bank. PIO pins in I/O Bank 3 that support differential inputs are also numbered by differential input pair.

Ball column number Ball row number Single-ended PIO Numbering PIO0 PIO0 Ball number A1 -I/O bank number PIO3/ Differential Input Pair Indicators **Differential Input Pair Numbering** DP07A DP07A -Pair pin polarity PIO3/ Pair number DP07B Differential Pair Dot indicates unconnected pin for iCE65L04 in CB284 package

Figure 31: CB Package Footprint Diagram Conventions

| Ball Function | Ball Number | Pin Type | Bank |

|---------------|-------------|----------|------|

| PIO2          | B14         | PIO      | 2    |

| PIO2/CBSEL0   | B15         | PIO      | 2    |

| PIO2/CBSEL1   | A20         | PIO      | 2    |

| VCCIO_2       | A17         | PIO      | 2    |

| GBIN6/PIO3    | А9          | GBIN     | 3    |

| GBIN7/PIO3    | A8          | GBIN     | 3    |

| PIO3          | A1          | PIO      | 3    |

| PIO3          | A2          | PIO      | 3    |

| PIO3          | A3          | PIO      | 3    |

| PIO3          | A4          | PIO      | 3    |

| PIO3          | A5          | PIO      | 3    |

| PIO3          | A10         | PIO      | 3    |

| PIO3          | A11         | PIO      | 3    |

| PIO3          | A12         | PIO      | 3    |

| PIO3          | B1          | PIO      | 3    |

| PIO3          | B2          | PIO      | 3    |

| PIO3          | В3          | PIO      | 3    |

| PIO3          | B4          | PIO      | 3    |

| PIO3          | B5          | PIO      | 3    |

| PIO3          | B7          | PIO      | 3    |

| PIO3          | B8          | PIO      | 3    |

| PIO3          | B9          | PIO      | 3    |

| VCCIO_3       | B6          | VCCIO    | 3    |

| PIOS/SPI_SO   | B17         | SPI      | SPI  |

| PIOS/SPI_SI   | A22         | SPI      | SPI  |

| PIOS/SPI_SCK  | A23         | SPI      | SPI  |

| PIOS/SPI_SS_B | B18         | SPI      | SPI  |

| SPI_VCC       | A24         | SPI      | SPI  |

| GND           | A6          | GND      | GND  |

| GND           | A18         | GND      | GND  |

| GND           | A30         | GND      | GND  |

| GND           | B33         | GND      | GND  |

| VCC           | A7          | VCC      | VCC  |

| VCC           | A15         | VCC      | VCC  |

| VCC           | A28         | VCC      | VCC  |

| VCC           | B28         | VCC      | VCC  |

| VPP_2V5       | A36         | VPP      | VPP  |

| VPP_FAST      | A37         | VPP      | VPP  |

## **VQ100 Very-thin Quad Flat Package**

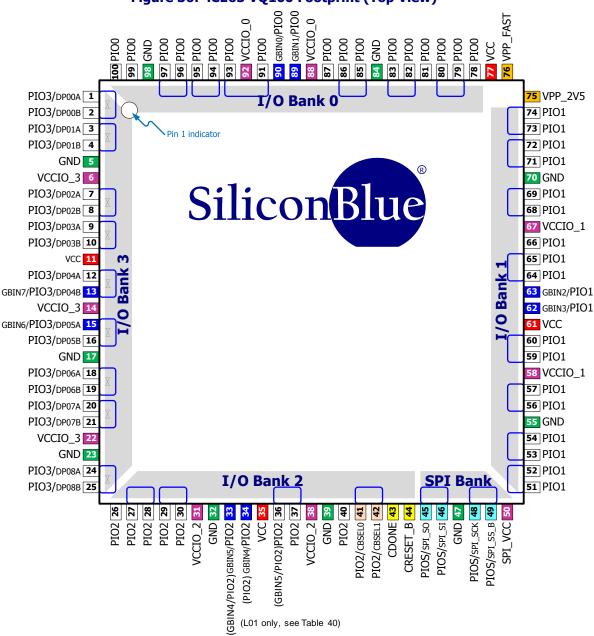

The VQ100 package is a very-thin quad-flat package with 0.5 mm lead pitch. The iCE65L01 and iCE65L04 devices are available in this package.

## **Footprint Diagram**

Figure 36 shows the footprint diagram for the 100-lead very-thin quad-flat package (VQ100). See Table 40 for a complete, detailed pinout for the 100-lead very-thin quad-flat package. The signal pins are also grouped into the four I/O Banks and the SPI interface.

Figure 36: iCE65 VQ100 Footprint (Top View)

#### **Pinout Table**

Table 39 provides a detailed pinout table for the VQ100 package. Pins are generally arranged by I/O bank, then by pin function. The table also highlights the differential I/O pairs in I/O Bank 3. The VQ100 package has no JTAG pins.

## **CB196 Chip-Scale Ball-Grid Array**

The CB196 package is a chip-scale, fully-populated, ball-grid array with 0.5 mm ball pitch.

## Footprint Diagram

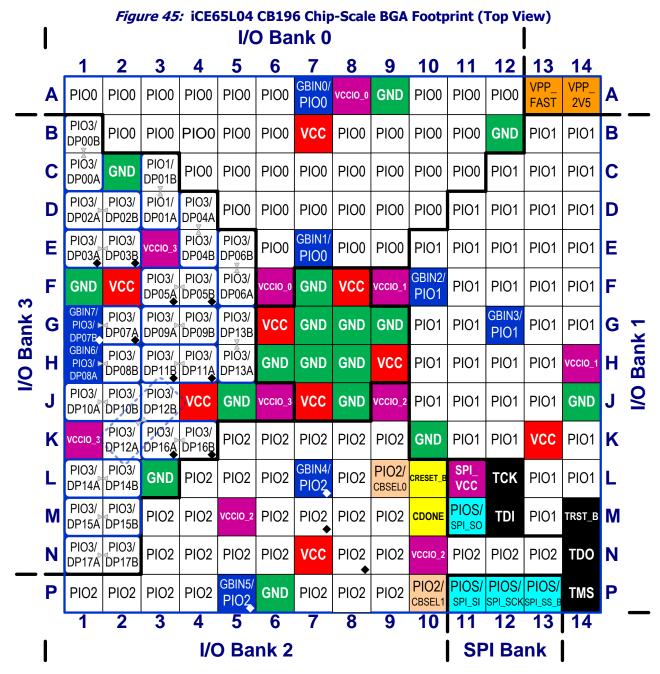

Figure 45 shows the iCE65L04 chip-scale BGA footprint for the 8 x 8 mm CB196 package. The footprint for the iCE65L08 is different than the iCE64L04 footprint, as shown in Figure 46. The pinout differences are highlighted by warning diamonds (♠) in the footprint diagrams and summarized in Table 43.

Although both the iCE65L04 and iCE65L08 are both available in the CB196 package and *almost* completely pin compatible, there are differences as shown in Table 43.

Figure 31 shows the conventions used in the diagram. Also see Table 42 for a complete, detailed pinout for the 196-ball chip-scale BGA packages. The signal pins are also grouped into the four I/O Banks and the SPI interface.

|               | D. II NI. I |           |             |      |            |  |

|---------------|-------------|-----------|-------------|------|------------|--|

|               | Ball Number | Pin Type  | e by Device |      | CD422 D    |  |

| 5.115.11      | iCE65L04    | :05051.04 | :05051.00   | 5 .  | CB132 Ball |  |

| Ball Function | iCE65L08    | iCE65L04  | iCE65L08    | Bank | Equivalent |  |

| PIO2          | T13         | PIO       | PIO         | 2    | M9         |  |

| PIO2          | V6          | PIO       | PIO         | 2    | P2         |  |

| PIO2          | V7          | PIO       | PIO         | 2    | P3         |  |

| PIO2          | V8          | PIO       | PIO         | 2    | P4         |  |

| PIO2          | V9          | PIO       | PIO         | 2    | P5         |  |

| PIO2          | V13         | PIO       | PIO         | 2    | P9         |  |

| PIO2          | Y4          | PIO       | PIO         | 2    | _          |  |

| PIO2          | Y5          | PIO       | PIO         | 2    | _          |  |

| PIO2          | Y6          | PIO       | PIO         | 2    | _          |  |

| PIO2          | Y7          | PIO       | PIO         | 2    | _          |  |

| PIO2          | Y9          | PIO       | PIO         | 2    | _          |  |

| PIO2          | Y10         | PIO       | PIO         | 2    | _          |  |

| PIO2          | Y13         | PIO       | PIO         | 2    | _          |  |

| PIO2          | Y14         | PIO       | PIO         | 2    | _          |  |

| PIO2          | Y15         | PIO       | PIO         | 2    | _          |  |

| PIO2          | Y17         | PIO       | PIO         | 2    | _          |  |

| PIO2          | Y18         | PIO       | PIO         | 2    | _          |  |

| PIO2          | Y19         | PIO       | PIO         | 2    | _          |  |

| PIO2          | Y20         | PIO       | PIO         | 2    | _          |  |

| PIO2          | AB2         | PIO       | PIO         | 2    | _          |  |

| PIO2 (●)      | AB3         | N.C.      | PIO         | 2    | _          |  |

| PIO2 (●)      | AB4         | N.C.      | PIO         | 2    | _          |  |

| PIO2          | AB6         | PIO       | PIO         | 2    | _          |  |

| PIO2          | AB7         | PIO       | PIO         | 2    | _          |  |

| PIO2          | AB8         | PIO       | PIO         | 2    | _          |  |

| PIO2          | AB9         | PIO       | PIO         | 2    | _          |  |

| PIO2          | AB10        | PIO       | PIO         | 2    | _          |  |

| PIO2          | AB11        | PIO       | PIO         | 2    | _          |  |

| PIO2          | AB12        | PIO       | PIO         | 2    | _          |  |

| PIO2          | AB13        | PIO       | PIO         | 2    | _          |  |

| PIO2          | AB14        | PIO       | PIO         | 2    | _          |  |

| PIO2          | AB15        | PIO       | PIO         | 2    | _          |  |

| PIO2 (●)      | AB16        | N.C.      | PIO         | 2    | _          |  |

| PIO2 (●)      | AB17        | N.C.      | PIO         | 2    | _          |  |

| PIO2 (●)      | AB18        | N.C.      | PIO         | 2    | _          |  |

| PIO2 (●)      | AB19        | N.C.      | PIO         | 2    | _          |  |

| PIO2 (●)      | AB20        | N.C.      | PIO         | 2    | _          |  |

| PIO2 (●)      | AB21        | N.C.      | PIO         | 2    | _          |  |

| PIO2 (●)      | AB22        | N.C.      | PIO         | 2    | _          |  |

| PIO2/CBSEL0   | R13         | PIO       | PIO         | 2    | L9         |  |

| PIO2/CBSEL1   | V14         | PIO       | PIO         | 2    | P10        |  |

| VCCIO_2       | N13         | VCCIO     | VCCIO       | 2    | J9         |  |

| VCCIO_2       | T9          | VCCIO     | VCCIO       | 2    | M5         |  |

| VCCIO_2       | Y11         | VCCIO     | VCCIO       | 2    | U13        |  |

|               |             |           |             |      |            |  |

| PIO3/DP00A    | F5          | DPIO      | DPIO        | 3    | B1         |  |

| PIO3/DP00B    | G5          | DPIO      | DPIO        | 3    | C1         |  |

| PIO3/DP01A    | G7          | DPIO      | DPIO        | 3    | C3         |  |

| PIO3/DP01B    | H7          | DPIO      | DPIO        | 3    | D3         |  |

| PIO3/DP02A    | H8          | DPIO      | DPIO        | 3    | D4         |  |

| PIO3/DP02B    | J8          | DPIO      | DPIO        | 3    | E4         |  |

| 1 100/ 01 020 | 30          | טו וט     | טו זט       | J    | L 1        |  |

#### **Die Cross Reference**

The tables in this section list all the pads on a specific die type and provide a cross reference on how a specific pad connects to a ball or pin in each of the available package offerings. Similarly, the tables provide the pad coordinates for the die-based version of the product (DiePlus). These tables also provide a way to prototype with one package option and then later move to a different package or die.

As described in "Input and Output Register Control per PIO Pair" on page 16, PIO pairs share register control inputs. Similarly, as described in "Differential Inputs and Outputs" on page 12, a PIO pair can form a differential input or output. PIO pairs in I/O Bank 3 are optionally differential inputs or differential outputs. PIO pairs in all other I/O Banks are optionally differential outputs. In the tables, differential pairs are surrounded by a heavy blue box.

#### iCE65L04

Table 45 lists all the pads on the iCE65L04 die and how these pads connect to the balls or pins in the supported package styles. Most VCC, VCCIO, and GND pads are double-bonded inside the package although the table shows only a single connection.

For additional information on the iCE65L04 DiePlus product, please refer to the following data sheet.

DiePlus Advantage FPGA Known Good Die

Table 45: iCE65L04 Die Cross Reference

| Table 45. Ice of the cross Reference |       |         |       |       |     |        |          |

|--------------------------------------|-------|---------|-------|-------|-----|--------|----------|

| iCE65L04                             |       | DiePlus |       |       |     |        |          |

| Pad Name                             | VQ100 | CB132   | CB196 | CB284 | Pad | Χ (μm) | Υ (μm)   |

| PIO3_00/DP00A                        | 1     | B1      | C1    | F5    | 1   | 129.40 | 2,687.75 |

| PIO3_01/DP00B                        | 2     | C1      | B1    | G5    | 2   | 231.40 | 2,642.74 |

| PIO3_02/DP01A                        | 3     | C3      | D3    | G7    | 3   | 129.40 | 2,597.75 |

| PIO3_03/DP01B                        | 4     | D3      | C3    | H7    | 4   | 231.40 | 2,552.74 |

| GND                                  | 5     | F1      | F1    | K5    | 5   | 129.40 | 2,507.75 |

| GND                                  | _     | _       | _     | _     | 6   | 231.40 | 2,462.74 |

| VCCIO_3                              | 6     | E3      | E3    | J7    | 7   | 129.40 | 2,417.75 |

| VCCIO_3                              | _     | _       | _     | _     | 8   | 231.40 | 2,372.74 |

| PIO3_04/DP02A                        | 7     | D4      | D1    | H8    | 9   | 129.40 | 2,327.75 |

| PIO3_05/DP02B                        | 8     | E4      | D2    | J8    | 10  | 231.40 | 2,292.74 |

| PIO3_06/DP03A                        | _     | D1      | E1    | H5    | 11  | 129.40 | 2,257.75 |

| PIO3_07/DP03B                        | _     | E1      | E2    | J5    | 12  | 231.40 | 2,222.74 |

| VCC                                  | _     | _       | H9    | D3    | 13  | 129.40 | 2,187.75 |

| PIO3_08/DP04A                        | 9     | F4      | D4    | K8    | 14  | 231.40 | 2,152.74 |

| PIO3_09/DP04B                        | 10    | F3      | E4    | K7    | 15  | 129.40 | 2,117.75 |

| PIO3_10/DP05A                        | _     | _       | F3    | E3    | 16  | 231.40 | 2,082.74 |

| PIO3_11/DP05B                        | _     | _       | F4    | F3    | 17  | 129.40 | 2,047.75 |

| GND                                  | _     | H6      | A9    | M10   | 18  | 231.40 | 2,012.74 |

| PIO3_12/DP06A                        | _     | _       | F5    | G3    | 19  | 129.40 | 1,977.75 |

| PIO3_13/DP06B                        | _     | _       | E5    | Н3    | 20  | 231.40 | 1,942.74 |

| GND                                  | _     | _       | A9    | J3    | 21  | 129.40 | 1,907.75 |

| GND                                  | _     | _       | _     | _     | 22  | 231.40 | 1,872.74 |

| PIO3_14/DP07A                        | _     | _       | _     | H1    | 23  | 129.40 | 1,837.75 |

| PIO3_15/DP07B                        | _     | _       | _     | J1    | 24  | 231.40 | 1,802.74 |

| VCCIO_3                              | _     | _       | K1    | К3    | 25  | 129.40 | 1,767.75 |

| VCC                                  | 11    | G6      | G6    | L10   | 26  | 231.40 | 1,732.74 |

| PIO3_16/DP08A                        | _     | _       | _     | K1    | 27  | 129.40 | 1,697.75 |

| PIO3_17/DP08B                        | _     | _       | _     | L1    | 28  | 231.40 | 1,662.74 |

## *iCE65L08*

Table 46 lists all the pads on the iCE65L08 die and how these pads connect to the balls or pins in the supported package styles. Most VCC, VCCIO, and GND pads are double-bonded inside the package although the table shows only a single connection.

For additional information on the iCE65L08 DiePlus product, please refer to the following data sheet.

■ DiePlusAdvantage FPGA Known Good Die

| Table 46: iCE65L08 Die Cross Reference |           |          |     |         |           |  |  |  |

|----------------------------------------|-----------|----------|-----|---------|-----------|--|--|--|

| iCE65L08                               | Available | Packages |     | DiePlus |           |  |  |  |

| Pad Name                               | CB196     | CB284    | Pad | Χ (μm)  | Υ (μm)    |  |  |  |

| PIO3_00/DP00A                          | _         | B1       | 1   | 129.735 | 3,882.665 |  |  |  |

| PIO3_01/DP00B                          | _         | C1       | 2   | 231.735 | 3,837.665 |  |  |  |

| PIO3_02/DP01A                          | C1        | F5       | 3   | 129.735 | 3,792.665 |  |  |  |

| PIO3_03/DP01B                          | B1        | G5       | 4   | 231.735 | 3,747.665 |  |  |  |

| GND                                    | C2        | K5       | 5   | 129.735 | 3,702.665 |  |  |  |

| GND                                    | _         | _        | 6   | 231.735 | 3,657.665 |  |  |  |

| VCCIO_3                                | E3        | J7       | 7   | 129.735 | 3,612.665 |  |  |  |

| VCCIO_3                                | _         | _        | 8   | 231.735 | 3,567.665 |  |  |  |

| PIO3_04/DP02A                          | D3        | E3       | 9   | 129.735 | 3,512.665 |  |  |  |

| PIO3_05/DP02B                          | C3        | F3       | 10  | 231.735 | 3,477.665 |  |  |  |

| PIO3_06/DP03A                          | D1        | G3       | 11  | 129.735 | 3,442.665 |  |  |  |

| PIO3_07/DP03B                          | D2        | H3       | 12  | 231.735 | 3,407.665 |  |  |  |

| VCC                                    | F2        | D3       | 13  | 129.735 | 3,372.665 |  |  |  |

| VCC                                    | _         | _        | 14  | 231.735 | 3,337.665 |  |  |  |

| PIO3_08/DP04A                          | D4        | D1       | 15  | 129.735 | 3,302.665 |  |  |  |

| PIO3_09/DP04B                          | E4        | E1       | 16  | 231.735 | 3,267.665 |  |  |  |

| PIO3_10/DP05A                          | _         | H1       | 17  | 129.735 | 3,232.665 |  |  |  |

| PIO3_11/DP05B                          | _         | J1       | 18  | 231.735 | 3,197.665 |  |  |  |

| GND                                    | F1        | M10      | 19  | 129.735 | 3,162.665 |  |  |  |

| GND                                    | _         | _        | 20  | 231.735 | 3,127.665 |  |  |  |

| PIO3_12/DP06A                          | E2        | H5       | 21  | 129.735 | 3,092.665 |  |  |  |

| PIO3_13/DP06B                          | E1        | J5       | 22  | 231.735 | 3,057.665 |  |  |  |

| GND                                    | L3        | J3       | 23  | 129.735 | 3,022.665 |  |  |  |

| GND                                    | _         | _        | 24  | 231.735 | 2,987.665 |  |  |  |

| PIO3_14/DP07A                          | F5        | K1       | 25  | 129.735 | 2,952.665 |  |  |  |

| PIO3_15/DP07B                          | E5        | L1       | 26  | 231.735 | 2,917.665 |  |  |  |

| VCCIO_3                                | E3        | K3       | 27  | 129.735 | 2,882.665 |  |  |  |

| VCCIO_3                                | _         | _        | 28  | 231.735 | 2,847.665 |  |  |  |

| VCC                                    | G6        | L10      | 29  | 129.735 | 2,812.665 |  |  |  |

| VCC                                    | _         | _        | 30  | 231.735 | 2,777.665 |  |  |  |

| PIO3_16/DP08A                          | F4        | G7       | 31  | 129.735 | 2,742.665 |  |  |  |

| PIO3_17/DP08B                          | F3        | H7       | 32  | 231.735 | 2,707.665 |  |  |  |

| VCCIO_3                                | K1        | F1       | 33  | 129.735 | 2,672.665 |  |  |  |

| VCCIO_3                                | _         | _        | 34  | 231.735 | 2,637.665 |  |  |  |

| GND                                    | _         | G1       | 35  | 129.735 | 2,602.665 |  |  |  |

| GND                                    | _         | _        | 36  | 231.735 | 2,567.665 |  |  |  |

| PIO3_18/DP09A                          | G3        | K8       | 37  | 129.735 | 2,532.665 |  |  |  |

| PIO3_19/DP09B                          | G4        | K7       | 38  | 231.735 | 2,497.665 |  |  |  |

## **I/O Characteristics**

**Table 49: PIO Pin Electrical Characteristics**

| Symbol             | Descr                                      | iption           | Conditions                    | Minimum | Nominal | Maximum | Units |

|--------------------|--------------------------------------------|------------------|-------------------------------|---------|---------|---------|-------|

| $\mathbf{I}_{l}$   | Input pin                                  | I/O Bank 0, 1, 2 | $V_{IN} = VCCIO_{max}$ to 0 V |         |         | ±10     | μΑ    |

|                    | leakage current                            | I/O Bank 3       | $V_{IN} = VCCIO_{max}$        |         |         |         |       |

| I <sub>oz</sub>    | Three-state I/O pin (Hi-Z) leakage current |                  | $V_{O} = VCCIO_{max}$ to 0 V  |         |         | ±10     | μΑ    |

| C <sub>PIO</sub>   | PIO pin input capa                         | icitance         |                               |         | 6       |         | pF    |

| C <sub>GBIN</sub>  | GBIN global buffer pin input               |                  |                               |         | 6       |         | pF    |

|                    | capacitance                                |                  |                               |         |         |         |       |

| R <sub>PULLU</sub> | Internal PIO pull-เ                        | ıp resistance    | VCCIO = 3.3V                  |         | 40      |         | kΩ    |

| P                  | during configuration                       | on               | VCCIO = 2.5V                  |         | 50      |         | kΩ    |

|                    |                                            |                  | VCCIO = 1.8V                  |         | 90      |         | kΩ    |

|                    |                                            |                  | VCCIO = 1.5V                  |         |         |         | kΩ    |

|                    |                                            |                  | VCCIO = 1.2V                  |         |         |         | kΩ    |

| V <sub>HYST</sub>  | Input hysteresis                           |                  | VCCIO = 1.5V  to  3.3V        |         | 50      |         | mV    |

**NOTE:** All characteristics are characterized and may or may not be tested on each pin on each device.

## Single-ended I/O Characteristics

Table 50: I/O Characteristics (I/O Banks 0, 1, 2 and SPI only) (I/O Bank 3 iCE65L01 only)

|              | Nominal I/O<br>Bank Supply | Input Voltage (V) |                   | Output Vo       | oltage (V)      | Output Current at<br>Voltage (mA) |                 |  |

|--------------|----------------------------|-------------------|-------------------|-----------------|-----------------|-----------------------------------|-----------------|--|

| I/O Standard | Voltage                    | V <sub>IL</sub>   | V <sub>IH</sub>   | V <sub>oL</sub> | V <sub>OH</sub> | I <sub>OL</sub>                   | I <sub>OH</sub> |  |

| LVCMOS33     | 3.3V                       | 0.80              | 2.00              | 0.4             | 2.40            | 8                                 | 8               |  |

| LVCMOS25     | 2.5V                       | 0.70              | 1.70              | 0.4             | 2.00            | 6                                 | 6               |  |

| LVCMOS18     | 1.8V                       | 35% VCCIO         | 65% VCCIO         | 0.4             | 1.40            | 4                                 | 4               |  |

| LVCMOS15     | 1.5V                       |                   | oported<br>Bank 3 | 0.4             | 1.20            | 2                                 | 2               |  |

Table 51: I/O Characteristics (I/O Bank 3 and iCE65L04/08 only)

|                 | Supply  | Input Voltage (V)    |                      | Output Voltage (V)   |                      | I/O Attribute    | mA at<br>Voltage                 |    |

|-----------------|---------|----------------------|----------------------|----------------------|----------------------|------------------|----------------------------------|----|

| I/O Standard    | Voltage | Max. V <sub>IL</sub> | Min. V <sub>IH</sub> | Max. V <sub>oL</sub> | Min. V <sub>OH</sub> | Name             | I <sub>OL.</sub> I <sub>OH</sub> |    |

| LVCMOS33        | 3.3V    | 0.80                 | 2.20                 | 0.4                  | 2.40                 | SL_LVCMOS33_8    | ±8                               |    |

|                 |         |                      |                      |                      |                      | SB_LVCMOS25_16   | ±16                              |    |

| LVCMOC2E        | 2 51/   | 0.70                 | 1 70                 | 0.4                  | 2.00                 | SB_LVCMOS25_12   | ±12                              |    |

| LVCMOS25        | 2.5V    | 0.70                 | 1.70                 | 0.4                  | 2.00                 | SB_LVCMOS25_8 *  | ±8                               |    |

|                 |         |                      |                      |                      |                      | SB_LVCMOS25_4    | ±4                               |    |

|                 |         |                      |                      |                      |                      | SB_LVCMOS18_10   | ±10                              |    |

| LVCMOC10        | 1.0\/   | 250/ 1/6610          | CENT VICETO          | CEN/ N/CCIO          | 0.4                  | VCCIO 0 45       | SB_LVCMOS18_8                    | ±8 |

| LVCMOS18        | 1.8V    | 35% VCCIO            | 65% VCCIO            | 0.4                  | VCCIO-0.45           | SB_LVCMOS18_4 *  | ±4                               |    |

|                 |         |                      |                      |                      |                      | SB_LVCMOS18_2    | ±2                               |    |

| LVCMOC1E        | 1 5\/   | 250/ 1/6610          | CENT VICCIO          | 250/ 1/0010          | 750/ 1/6610          | SB_LVCMOS15_4    | ±4                               |    |

| LVCMOS15        | 1.5V    | 35% VCCIO            | 65% VCCIO            | 25% VCCIO            | 75% VCCIO            | SB_LVCMOS15_2 *  | ±2                               |    |

|                 |         |                      |                      |                      |                      | SB_MDDR10        | ±10                              |    |

| MDDD            | 1.0\/   | 250/ 1/6610          | CENT VICCIO          | 0.4                  | VCCIO 0 45           | SB_MDDR8         | ±8                               |    |

| MDDR            | 1.8V    | 35% VCCIO            | 65% VCCIO            | 0.4                  | VCCIO-0.45           | SB_MDDR4 *       | ±4                               |    |

|                 |         |                      |                      |                      |                      | SB_MDDR2         | ±2                               |    |

| SSTL2 (Class 2) | 2 51/   | VDEE 0 100           | VDEE : 0 100         | 0.35                 | VTT - 0 420          | SB_SSTL2_CLASS_2 | ±16.2                            |    |

| SSTL2 (Class 1) | 2.5V    | VREF-0.180           | VREF+0.180           | 0.54                 | VTT+0.430            | SB_SSTL2_CLASS_1 | ±8.1                             |    |

| SSTL18 (Full)   | 1.0\/   | VDEE 0 125           | VDEE : 0 125         | 0.28                 | VTT+0.280            | SB_SSTL18_FULL   | ±13.4                            |    |

| SSTL18 (Half)   | 1.8V    | VREF-0.125           | VREF+0.125           | VTT-0.475            | VTT+0.475            | SB_SSTL18_HALF   | ±6.7                             |    |

| NOTEC:          | •       | •                    |                      | •                    | •                    | •                |                                  |    |

#### NOTES

SSTL2 and SSTL18 I/O standards require the VREF input pin, which is only available on the CB284 package and die-based products.

#### **RAM4K Block**

Table 56 provides timing information for the logic in a RAM4K block, which includes the paths shown in Figure 59.

Figure 59: RAM4K Timing Circuit

**Table 56: Typical RAM4K Block Timing**

|                     |                        |                        | Table 50: Typical Ital-141t bi                                                                                                   | ••••       | 9     |          |       |       |

|---------------------|------------------------|------------------------|----------------------------------------------------------------------------------------------------------------------------------|------------|-------|----------|-------|-------|

|                     |                        |                        | Device: iCE65                                                                                                                    | L01        |       | L04, L08 |       |       |

|                     |                        |                        | Power/Speed Grade                                                                                                                | <b>-</b> T | -L    | -L       | -Т    |       |

|                     |                        |                        | Nominal VCC                                                                                                                      | 1.2 V      | 1.0 V | 1.2 V    | 1.2 V |       |

| Symbol              | From                   | То                     | Description                                                                                                                      | Тур.       | Тур.  | Тур.     | Тур.  | Units |

|                     | Write 9                | Setup/Ho               | old Time                                                                                                                         |            |       |          |       |       |

| t <sub>suwd</sub>   | PIO<br>input           | GBIN<br>input          | Minimum write data setup time on PIO inputs before active clock edge on GBIN                                                     | 0.6        | 3.1   | 1.7      | 0.8   | ns    |

|                     |                        | · ·                    | input, include interconnect delay.                                                                                               |            |       |          |       |       |

| t <sub>HDWD</sub>   | GBIN<br>input          | PIO<br>input           | Minimum write data hold time on PIO inputs after active clock edge on GBIN input, including interconnect delay.                  | 0          | 0     | 0        | 0     | ns    |

|                     | Read C                 | lock-Out               | put-Time                                                                                                                         |            |       |          |       |       |

| t <sub>CKORD</sub>  | RCLK<br>clock<br>input | PIO<br>output          | Clock-to-output delay from RCLK input pin, through RAM4K RDATA output flip-flop to PIO output pad, including interconnect delay. | 5.6        | 17.1  | 9.1      | 7.3   | ns    |

| t <sub>GBCKRM</sub> | GBIN<br>input          | RCLK<br>clock<br>input | Global Buffer Input (GBIN) delay, though<br>Global Buffer (GBUF) clock network to<br>the RCLK clock input.                       | 2.1        | 7.3   | 3.8      | 2.6   | ns    |

|                     | Write a                | and Read               | Clock Characteristics                                                                                                            |            |       |          |       |       |

| t <sub>RMWCKH</sub> | WCLK                   | WCLK                   | Write clock High time                                                                                                            | 0.54       | 1.14  | 0.54     | 0.54  | ns    |

| t <sub>RMWCKL</sub> | RCLK                   | RCLK                   | Write clock Low time                                                                                                             | 0.63       | 1.32  | 0.63     | 0.63  | ns    |

| t <sub>RMWCYC</sub> |                        |                        | Write clock cycle time                                                                                                           | 1.27       | 2.64  | 1.27     | 1.27  | ns    |

| F <sub>WMAX</sub>   |                        |                        | Sustained write clock frequency                                                                                                  | 256        | 256   | 256      | 256   | MHz   |

## **Revision History**

| Version | Date         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |