Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

## **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                                              |

|--------------------------------|------------------------------------------------------------------------------|

| Product Status                 | Obsolete                                                                     |

| Number of LABs/CLBs            | 440                                                                          |

| Number of Logic Elements/Cells | 3520                                                                         |

| Total RAM Bits                 | 81920                                                                        |

| Number of I/O                  | 176                                                                          |

| Number of Gates                | -                                                                            |

| Voltage - Supply               | 1.14V ~ 1.26V                                                                |

| Mounting Type                  | Surface Mount                                                                |

| Operating Temperature          | -40°C ~ 85°C (TA)                                                            |

| Package / Case                 | 284-VFBGA, CSPBGA                                                            |

| Supplier Device Package        | 284-CSPBGA (12x12)                                                           |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/ice65l04f-lcb284i |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Overview**

The Lattice Semiconductor iCE65 programmable logic family is specifically designed to deliver the lowest static and dynamic power consumption of any comparable CPLD or FPGA device. iCE65 devices are designed for cost-sensitive, high-volume applications and provide on-chip, nonvolatile configuration memory (NVCM) to customize for a specific application. iCE65 devices can self-configure from a configuration image stored in an external commodity SPI serial Flash PROM or be downloaded from an external processor over an SPI-like serial port.

The three iCE65 components, highlighted in Table 1, deliver from approximately 1K to nearly 8K logic cells and flip-flops while consuming a fraction of the power of comparable programmable logic devices. Each iCE65 device includes between 16 to 32 RAM blocks, each with 4Kbits of storage, for on-chip data storage and data buffering.

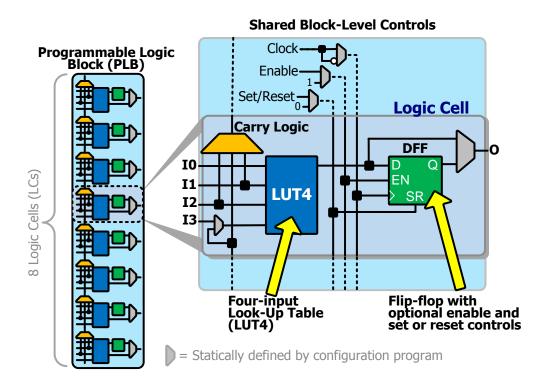

As pictured in Figure 1, each iCE65 device consists of four primary architectural elements.

- An array of Programmable Logic Blocks (PLBs)

- ◆ Each PLB contains eight Logic Cells (LCs); each Logic Cell consists of ...

- A fast, four-input look-up table (LUT4) capable of implementing any combinational logic function of up to four inputs, regardless of complexity

- A 'D'-type flip-flop with an optional clock-enable and set/reset control

- Fast carry logic to accelerate arithmetic functions such as adders, subtracters, comparators, and counters.

- ◆ Common clock input with polarity control, clock-enable input, and optional set/reset control input to the PLB is shared among all eight Logic Cells

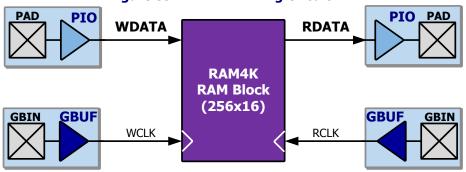

- Two-port, 4Kbit RAM blocks (RAM4K)

- ◆ 256x16 default configuration; selectable data width using programmable logic resources

- ♦ Simultaneous read and write access; ideal for FIFO memory and data buffering applications

- ◆ RAM contents pre-loadable during configuration

- Four I/O banks with independent supply voltage, each with multiple Programmable Input/Output (PIO) blocks

- ◆ LVCMOS I/O standards and LVDS outputs supported in all banks

- ◆ I/O Bank 3 supports additional SSTL, MDDR, LVDS, and SubLVDS I/O standards

- Programmable interconnections between the blocks

- Flexible connections between all programmable logic functions

- Eight dedicated low-skew, high-fanout clock distribution networks

# **Packaging Options**

iCE65 components are available in a variety of package options to support specific application requirements. The available options, including the number of available user-programmable I/O pins (PIOs), are listed in Table 2. Fully-tested Known-Good Die (KGD) DiePlus <sup>™</sup> are available for die stacking and highly space-conscious applications. All iCE65 devices are provided exclusively in Pb-free, RoHS-compliant packages.

Table 2: iCE65 Family Packaging Options, Maximum I/O per Package

| Package                             | Package<br>Body<br>(mm)   | Package<br>Code | Ball/Lead<br>Pitch<br>(mm) | 65L01           | 65L04                        | 65L08                  |

|-------------------------------------|---------------------------|-----------------|----------------------------|-----------------|------------------------------|------------------------|

| 81-ball chip-scale BGA              | 5 x 5                     | CB81            | 0.5                        | 63 <i>(0)</i>   | _                            | _                      |

| 84-pin quad flat no-lead package    | 7 x 7                     | QN84            | 0.5                        | 67 <i>(0)</i>   | _                            | _                      |

| 100-pin very thin quad flat package | 14 x 14                   | VQ100           | 0.5                        | 72 <i>(0)</i> 😓 | <del>_</del> > 72 <i>(9)</i> | _                      |

| 121-ball chip-scale BGA             | 6 x 6                     | CB121           |                            | 92 <i>(0)</i>   |                              | _                      |

| 132-ball chip-scale BGA             | 8 x 8                     | CB132           | 0.5                        | U 2 ///) :      | 95 (11)                      | > 95 <i>(12)</i>       |

| 196-ball chip-scale BGA             | 8 x 8                     | CB196           | 0.5                        | _ `             | 150 (18)                     | 1 FO (10)              |

| 284-ball chip-scale BGA             | 12 x 12                   | CB284           |                            | _               | 176 <i>(20)</i> 📛            | <b>222</b> <i>(25)</i> |

| Known Good Die                      | See DiePlus<br>data sheet | DI              | _                          | 95 <i>(0)</i>   | 176 <i>(20)</i>              | 222 <i>(25)</i>        |

= Common footprint allows each density migration on the same printed circuit board. (Differential input count).

The iCE65L04 and the iCE65L08 are both available in the CB196 package and have similar footprints but are not completely pin compatible. See "Pinout Differences between iCE65L04 and iCE65L08 in CB196 Package" on page 73 for more information.

When iCE65 components are supplied in the same package style, devices of different gate densities share a common footprint. The common footprint improves manufacturing flexibility. Different models of the same product can share a common circuit board. Feature-rich versions of the end application mount a larger iCE65 device on the circuit board. Low-end versions mount a smaller iCE65 device.

## **Programmable Logic Block (PLB)**

Generally, a logic design for an iCE65 component is created using a high-level hardware description language such as Verilog or VHDL. The Lattice Semiconductor development software then synthesizes the high-level description into equivalent functions built using the programmable logic resources within each iCE65 device. Both sequential and combinational functions are constructed from an array of Programmable Logic Blocks (PLBs). Each PLB contains eight Logic Cells (LCs), as pictured in Figure 4, and share common control inputs, such as clocks, reset, and enable controls.

PLBs are connected to one another and other logic functions using the rich Programmable Interconnect resources.

# Logic Cell (LC)

Each iCE65 device contains thousands of Logic Cells (LCs), as listed in Table 1. Each Logic Cell includes three primary logic elements, shown in Figure 4.

■ A four-input Look-Up Table (LUT4) builds any combinational logic function, of any complexity, of up to four inputs. Similarly, the LUT4 element behaves as a 16xl Read-Only Memory (ROM). Combine and cascade multiple LUT4s to create wider logic functions.

# Figure 4: Programmable Logic Block and Logic Cell

- A 'D'-style Flip-Flop (DFF), with an optional clock-enable and reset control input, builds sequential logic functions. Each DFF also connects to a global reset signal that is automatically asserted immediately following device configuration.

- Carry Logic boosts the logic efficiency and performance of arithmetic functions, including adders, subtracters, comparators, binary counters and some wide, cascaded logic functions.

The output from a Logic Cell is available to all inputs to all eight Logic Cells within the Programmable Logic Block. Similarly, the Logic Cell output feeds into fabric to connect to other features on the iCE65 device.

## **Look-Up Table (LUT4)**

The four-input Look-Up Table (LUT4) function implements any and all combinational logic functions, regardless of complexity, of between zero and four inputs. Zero-input functions include "High" (1) and "Low" (0). The LUT4 function has four inputs, labeled IO, II, I2, and I3. Three of the four inputs are shared with the Carry Logic function, as shown in Figure 4. The bottom-most LUT4 input connects either to the I3 input or to the Carry Logic output from the previous Logic Cell.

The output from the LUT4 function connects to the flip-flop within the same Logic Cell. The LUT4 output or the flip-flop output then connects to the programmable interconnect.

For detailed LUT4 internal timing, see Table 54.

## **'D'-style Flip-Flop (DFF)**

The 'D'-style flip-flop (DFF) optionally stores state information for the application.

The flip-flop has a data input, 'D', and a data output, 'Q'. Additionally, each flip-flop has up to three control signals that are shared among all flip-flops in all Logic Cells within the PLB, as shown in Figure 4. Table 3 describes the behavior of the flip-flop based on inputs and upon the specific DFF design primitive used or synthesized.

Table 3: 'D'-Style Flip-Flop Behavior

| DFF       |                                         | Flip-Flop             |   | Inp | uts |          | Output |

|-----------|-----------------------------------------|-----------------------|---|-----|-----|----------|--------|

| Primitive | Operation                               | Mode                  | D | EN  | SR  | CLK      | Q      |

| All       | Cleared Immediately after Configuration | X                     | Χ | Χ   | Χ   | X        | 0      |

|           | Hold Present Value<br>(Disabled)        |                       | Χ | 0   | Χ   | Χ        | Q      |

|           | Hold Present Value (Static Clock)       |                       | Χ | Χ   | Χ   | 1 or 0   | Q      |

|           | Load with Input Data                    |                       | D | 1*  | 0*  | <b>↑</b> | D      |

| SB_DFFR   | Asynchronous Reset                      | Asynchronous<br>Reset | Χ | Χ   | 1   | Χ        | 0      |

| SB_DFFS   | Asynchronous Set                        | Asynchronous<br>Set   | Χ | Χ   | 1   | X        | 1      |

| SB_DFFSR  | Synchronous Reset                       | Synchronous<br>Reset  | Χ | 1*  | 1   | 1        | 0      |

| SB_DFFSS  | Synchronous Set                         | Synchronous<br>Set    | Χ | 1*  | 1   | <b>†</b> | 1      |

X = don't care,  $\uparrow = rising$  clock edge (default polarity),  $1^* = High$  or unused,  $0^* = Low$  or unused

The CLK clock signal is not optional and is shared among all flip-flops in a Programmable Logic Block. By default, flip-flops are clocked by the rising edge of the PLB clock input, although the clock polarity can be inverted for all the flip-flops in the PLB.

The CLK input optionally connects to one of the following clock sources.

- The output from any one of the eight Global Buffers, or

- A connection from the general-purpose interconnect fabric

The EN clock-enable signal is common to all Logic Cells in a Programmable Logic Block. If the enable signal is not used, then the flip-flop is always enabled. This condition is indicated as "1\*" in Table 3. The asterisk indicates that this is the default state if the control signal is not connected in the application.

Similarly, the SR set/reset signal is common to all Logic Cells in a Programmable Logic Block. If not used, then the flip-flop is never set/reset, except when cleared immediately after configuration or by the Global Reset signal. This condition is indicated as "0\*" in Table 3. The asterisk indicates that this is the default state if the control signal is not connected in the application.

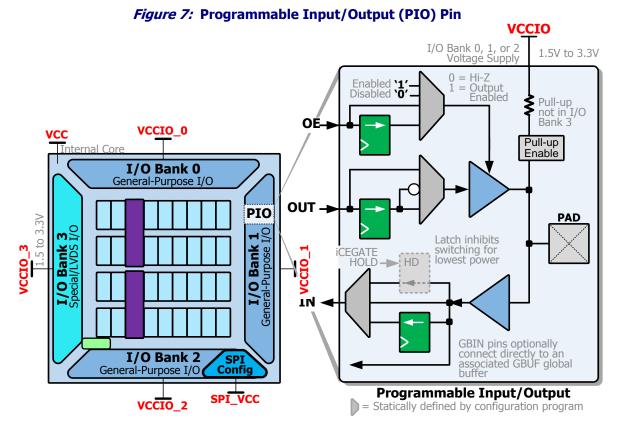

## Programmable Input/Output Block (PIO)

Programmable Input/Output (PIO) blocks surround the periphery of the device and connect external components to the Programmable Logic Blocks (PLBs) and RAM4K blocks via programmable interconnect. Individual PIO pins are grouped into one of four I/O banks, as shown in Figure 7. I/O Bank 3 has additional capabilities, including LVDS differential I/O and the ability to interface to Mobile DDR memories.

Figure 7 also shows the logic within a PIO pin. When used in an application, a PIO pin becomes a signal input, an output, or a bidirectional I/O pin with a separate direction control input.

#### I/O Banks

PIO blocks are organized into four separate I/O banks, each with its own voltage supply input, as shown in Table 5. The voltage applied to the VCCIO pin on a bank defines the I/O standard used within the bank. Table 50 and Table 51 describe the I/O drive capabilities and switching thresholds by I/O standard. On iCE65L04 and iCE65L08 devices, I/O Bank 3, along the left edge of the die, is different than the others and supports specialized I/O standards.

#### I/O Bank Voltage Supply Inputs Support Different I/O Standards

Because each I/O bank has its own voltage supply, iCE65 components become the ideal bridging device between different interface standards. For example, the iCE65 device allows a 1.8V-only processor to interface cleanly with a 3.3V bus interface. The iCE65 device replaces external voltage translators.

Table 5: Supported Voltages by I/O Bank

| Bank | Device Edge  | Supply Input | 3.3V | 2.5V | 1.8V | 1.5V                   |

|------|--------------|--------------|------|------|------|------------------------|

| 0    | Тор          | VCCIO_0      | Yes  | Yes  | Yes  | Outputs only           |

| 1    | Right        | VCCIO_1      | Yes  | Yes  | Yes  | Outputs only           |

| 2    | Bottom       | VCCIO_2      | Yes  | Yes  | Yes  | Outputs only           |

| 3    | Left         | VCCIO_3      | Yes  | Yes  | Yes  | iCE65L01: Outputs only |

|      |              |              |      |      |      | iCE65L04/08: Yes       |

| SPI  | Bottom Right | SPI_VCC      | Yes  | Yes  | Yes  | No                     |

If not connected to an external SPI PROM, the four pins associated with the SPI Master Configuration Interface can be used as PIO pins, supplied by the SPI\_VCC input, essentially forming a fifth "mini" I/O bank. If using an SPI Flash PROM, then connect SPI VCC to 3.3V.

#### I/O Banks 0, 1, 2, SPI and Bank 3 of iCE65L01

Table 6 highlights the available I/O standards when using an iCE65 device, indicating the drive current options, and in which bank(s) the standard is supported. I/O Banks 0, 1, 2 and SPI interface support the same standards. I/O Bank 3 has additional capabilities in iCE65L04 and iCE65L08, including support for MDDR memory standards and LVDS differential I/O.

Table 6: I/O Standards for I/O Banks 0, 1, 2, SPI Interface Bank, and Bank 3 of iCE65L01

| I/O Standard       | Supply Voltage | Drive Current (mA) | Attribute Name |

|--------------------|----------------|--------------------|----------------|

| 5V Input Tolerance | 3.3V           | N/A                | N/A            |

| LVCMOS33           | 3.3V           | ±11                |                |

| LVCMOS25           | 2.5V           | ±8                 | SB LVCMOS      |

| LVCMOS18           | 1.8V           | ±5                 | 3B_LVCMO3      |

| LVCMOS15 outputs   | 1.5V           | ±4                 |                |

#### IBIS Models for I/O Banks 0, 1, 2 and the SPI Bank

The IBIS (I/O Buffer Information Specification) file that describes the output buffers used in I/O Banks 0, 1, 2, SPI Bank and Bank 3 of iCE65L01 is available from the following link.

■ IBIS Models for I/O Banks 0, 1, 2, SPI Bank and Bank 3 of iCE65L01

#### I/O Bank 3 of iCE65L04 and iCE65L08

I/O Bank 3, located along the left edge of the die, has additional special I/O capabilities to support memory components and differential I/O signaling (LVDS). Table 7 lists the various I/O standards supported by I/O Bank 3. The SSTL2 and SSTL18 I/O standards require the VREF voltage reference input pin which is only available on the CB284 package. Also see Table 51 for electrical characteristics.

Table 7: I/O Standards for I/O Bank 3 Only of iCE65L04 and iCE65L08

|              | Supply  | VREF Pin (CB284 or | Target             |                  |

|--------------|---------|--------------------|--------------------|------------------|

| I/O Standard | Voltage | DiePlus) Required? | Drive Current (mA) | Attribute Name   |

| LVCMOS33     | 3.3V    | No                 | ±8                 | SB_LVCMOS33_8    |

|              |         | No                 | ±16                | SB_LVCMOS25_16   |

| LVCMOS25     | 2.5V    |                    | ±12                | SB_LVCMOS25_12   |

| LVCMOS25     | 2.50    |                    | ±8                 | SB_LVCMOS25_8    |

|              |         |                    | ±4                 | SB_LVCMOS25_4    |

|              |         | No                 | ±10                | SB_LVCMOS18_10   |

| LVCMOS18     | 1.8V    |                    | ±8                 | SB_LVCMOS18_8    |

| LVCI40210    | 1.00    |                    | ±4                 | SB_LVCMOS18_4    |

|              |         |                    | ±2                 | SB_LVCMOS18_2    |

| LVCMOS15     | 1.5V    | No                 | ±4                 | SB_LVCMOS15_4    |

| LVCMOSTS     | 1.50    |                    | ±2                 | SB_LVCMOS15_2    |

| SSTL2_II     | 2.5V    | Yes                | ±16.2              | SB_SSTL2_CLASS_2 |

| SSTL2_I      | 2.50    |                    | ±8.1               | SB_SSTL2_CLASS_1 |

| SSTL18_II    | 1.8V    | Yes                | ±13.4              | SB_SSTL18_FULL   |

| SSTL18_I     | 1.00    |                    | ±6.7               | SB_SSTL18_HALF   |

|              |         | No                 | ±10                | SB_MDDR10        |

| MDDR         | 1 0\/   |                    | ±8                 | SB_MDDR8         |

| אטטויו       | 1.8V    |                    | ±4                 | SB_MDDR4         |

|              |         |                    | ±2                 | SB_MDDR2         |

| LVDS         | 2.5V    | No                 | N/A                | SB_LVDS_INPUT    |

- Register file and scratchpad RAM

- First-In, First-Out (FIFO) memory for data buffering applications

- Circuit buffer

- A 256-deep by 16-wide ROM with registered outputs, contents loaded during configuration

- ♦ Sixteen different 8-input look-up tables

- ◆ Function or waveform tables such as sine, cosine, etc.

- ◆ Correlators or pattern matching operations

- Counters, sequencers

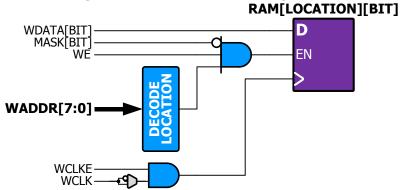

As pictured in Figure 17, a RAM4K block has separate write and read ports, each with independent control signals. Table 17 lists the signals for both ports. Additionally, the write port has an active-Low bit-line write-enable control; optionally mask write operations on individual bits. By default, input and output data is 16 bits wide, although the data width is configurable using programmable logic and, if needed, multiple RAM4K blocks.

The WCLK and RCLK inputs optionally connect to one of the following clock sources.

- ◆ The output from any one of the eight Global Buffers, or

- ◆ A connection from the general-purpose interconnect fabric

The data contents of the RAM4K block are optionally pre-loaded during iCE65 device configuration. If the RAM4K blocks are not pre-loaded during configuration, then the resulting configuration bitstream image is smaller. However, if an uninitialized RAM4K block is used in the application, then the application must initialize the RAM contents to guarantee the data value.

See Table 56 for detailed timing information.

## **Signals**

Table 17 lists the signal names, direction, and function of each connection to the RAM4K block. See also Figure 17.

Table 17: RAM4K Block RAM Signals

| Signal Name | Direction | Description                                                                               |

|-------------|-----------|-------------------------------------------------------------------------------------------|

| WDATA[15:0] | Input     | Write Data input.                                                                         |

| MASK[15:0]  | Input     | Masks write operations for individual data bit-lines.  0 = Write bit; 1 = Don't write bit |

| WADDR[7:0]  | Input     | Write Address input. Selects one of 256 possible RAM locations.                           |

| WE          | Input     | Write Enable input.                                                                       |

| WCLKE       | Input     | Write Clock Enable input.                                                                 |

| WCLK        | Input     | Write Clock input. Default rising-edge, but with falling-edge option.                     |

| RDATA[15:0] | Output    | Read Data output.                                                                         |

| RADDR[7:0]  | Input     | Read Address input. Selects one of 256 possible RAM locations.                            |

| RE          | Input     | Read Enable input.                                                                        |

| RCLKE       | Input     | Read Clock Enable input.                                                                  |

| RCLK        | Input     | Read Clock input. Default rising-edge, but with falling-edge option.                      |

#### **Write Operations**

Figure 18 shows the logic involved in writing a data bit to a RAM location. Table 18 describes various write operations for a RAM4K block. By default, all RAM4K write operations are synchronized to the rising edge of WCLK although the clock is invertible as shown in Figure 18.

Figure 18: RAM4K Bit Write Logic

When the WCLKE signal is Low, the clock to the RAM4K block is disabled, keeping the RAM in its lowest power mode.

**Table 18: RAM4K Write Operations**

|           | WDATA[15:0] | MASK[15:0]  | WADDR[7:0] | WE     | WCLKE  | WCLK     |               |

|-----------|-------------|-------------|------------|--------|--------|----------|---------------|

|           |             |             |            | Write  | Clock  |          |               |

| Operation | Data        | Mask Bit    | Address    | Enable | Enable | Clock    | RAM Location  |

| Disabled  | X           | X           | X          | Χ      | Χ      | 0        | No change     |

| Disabled  |             |             |            |        | 0      | Χ        | No change     |

| Disabled  | X           | Χ           | X          | 0      | Χ      | Χ        | No change     |

| Write     | WDATA[i]    | MASK[i] = 0 | WADDR      | 1      | 1      | <b>↑</b> | RAM[WADDR][i] |

| Data      |             |             |            |        |        |          | = WDATA[i]    |

| Masked    | X           | MASK[i] = 1 | WADDR      | 1      | 1      | <b>↑</b> | RAM[WADDR][i] |

| Write     |             |             |            |        |        |          | = No change   |

To write data into the RAM4K block, perform the following operations.

- ◆ Supply a valid address on the WADDR[7:0] address input port

- ◆ Supply valid data on the WDATA[15:0] data input port

- ◆ To write or mask selected data bits, set the associated MASK input port accordingly. For example, write operations on data bit D[i] are controlled by the associated MASK[i] input.

- MASK[i] = 0: Write operations are enabled for data line WDATA[i]

- MASK[i] = 1: Mask write operations are disabled for data line WDATA[i]

- ◆ Enable the RAM4K write port (WE = 1)

- ◆ Enable the RAM4K write clock (WCLKE = 1)

- ◆ Apply a rising clock edge on WCLK (assuming that the clock is not inverted)

#### **Read Operations**

Figure 19 shows the logic involved in reading a location from RAM. Table 19 describes various read operations for a RAM4K block. By default, all RAM4K read operations are synchronized to the rising edge of RCLK although the clock is invertible as shown in Figure 19.

23

Table 28: ColdBoot Select Ball/Pin Numbers by Package

| ColdBoot Select | CB81 | QN84 | VQ100 | CB132 | CB196 | CB284 |

|-----------------|------|------|-------|-------|-------|-------|

| PIO2/CBSEL0     | G5   | B15  | 41    | L9    | L9    | R13   |

| PIO2/CBSEL1     | H5   | A20  | 42    | P10   | P10   | V14   |

When creating the initial configuration image, the Lattice development software loads the start address for up to four configuration images in the bitstream. The value on the CBSEL[1:0] pins tell the configuration controller to read a specific start address, then to load the configuration image stored at the selected address. The multiple bitstreams are stored either in the SPI Flash or in the internal NVCM.

After configuration, the CBSEL[1:0] pins become normal PIO pins available to the application.

The Cold Boot feature allows the iCE65 to be reprogrammed for special application requirements such as the following.

- A normal operating mode and a self-test or diagnostics mode.

- Different applications based on switch settings.

- Different applications based on a card-slot ID number.

#### **Warm Boot Configuration Option**

The Warm Boot configuration is similar to the Cold Boot feature, but is completely under the control of the FPGA application.

A special design primitive, SB\_WARMBOOT, allows an FPGA application to choose between four configuration images using two internal signal ports, Sl and S0, as shown in Figure 27. These internal signal ports connect to programmable interconnect, which in turn can connect to PLB logic and/or PIO pins.

After selecting the desired configuration image, the application then asserts the internal signal BOOT port High to force the FPGA to restart the configuration process from the specified vector address stored in PROM.

A Warm Boot application can only jump to another configuration image that DOES NOT have Warm Boot enabled. There is no such restriction for Cold Boot applications.

## **Time-Out and Retry**

When configuring from external SPI Flash, the iCE65 device looks for a synchronization word. If the device does not find a synchronization word within its timeout period, the device automatically attempts to restart the configuration process from the very beginning. This feature is designed to address any potential power-sequencing issues that may occur between the iCE65 device and the external PROM.

The iCE65 device attempts to reconfigure six times. If not successful after six attempts, the iCE65 FPGA automatically goes into low-power mode.

#### **SPI Peripheral Configuration Interface**

Using the SPI peripheral configuration interface, an application processor (AP) serially writes a configuration image to an iCE65 FPGA using the iCE65's SPI interface, as shown in Figure 23. The iCE65's SPI configuration interface is a separate, independent I/O bank, powered by the VCC\_SPI supply input. Typically, VCC\_SPI is the same voltage as the application processor's I/O. The configuration control signals, CDONE and CRESET\_B, are supplied by the separate I/O Bank 2 voltage input, VCCIO\_2.

This same SPI peripheral interface supports programming for the iCE65's Nonvolatile Configuration Memory (NVCM).

| Ball Function | Ball Number | Pin Type | Bank |

|---------------|-------------|----------|------|

| PIO3          | B1          | PIO      | 3    |

| PIO3          | B2          | PIO      | 3    |

| PIO3          | В3          | PIO      | 3    |

| PIO3          | C1          | PIO      | 3    |

| PIO3          | C2          | PIO      | 3    |

| PIO3          | C3          | PIO      | 3    |

| GBIN7/PIO3    | D1          | GBIN     | 3    |

| PIO3          | D2          | PIO      | 3    |

| PIO3          | D3          | PIO      | 3    |

| GBIN6/PIO3    | E1          | GBIN     | 3    |

| PIO3          | E2          | PIO      | 3    |

| PIO3          | E3          | PIO      | 3    |

| PIO3          | F2          | PIO      | 3    |

| PIO3          | F3          | PIO      | 3    |

| PIO3          | G1          | PIO      | 3    |

| PIO3          | G2          | PIO      | 3    |

| PIO3          | H1          | PIO      | 3    |

| PIO3          | H2          | PIO      | 3    |

| VCCIO_3       | F1          | VCCIO    | 3    |

| PIOS/SPI_SO   | H7          | SPI      | SPI  |

| PIOS/SPI_SI   | J7          | SPI      | SPI  |

| PIOS/SPI_SCK  | Ј8          | SPI      | SPI  |

| PIOS/SPI_SS_B | H8          | SPI      | SPI  |

| SPI_VCC       | H9          | SPI      | SPI  |

| GND           | A1          | GND      | GND  |

| GND           | A9          | GND      | GND  |

| GND           | J9          | GND      | GND  |

| GND           | J1          | GND      | GND  |

| GND           | E4          | GND      | GND  |

| GND           | E5          | GND      | GND  |

| GND           | F4          | GND      | GND  |

| GND           | F5          | GND      | GND  |

| VCC           | A5          | VCC      | VCC  |

| VCC           | J5          | VCC      | VCC  |

| VPP_2V5       | B9          | VPP      | VPP  |

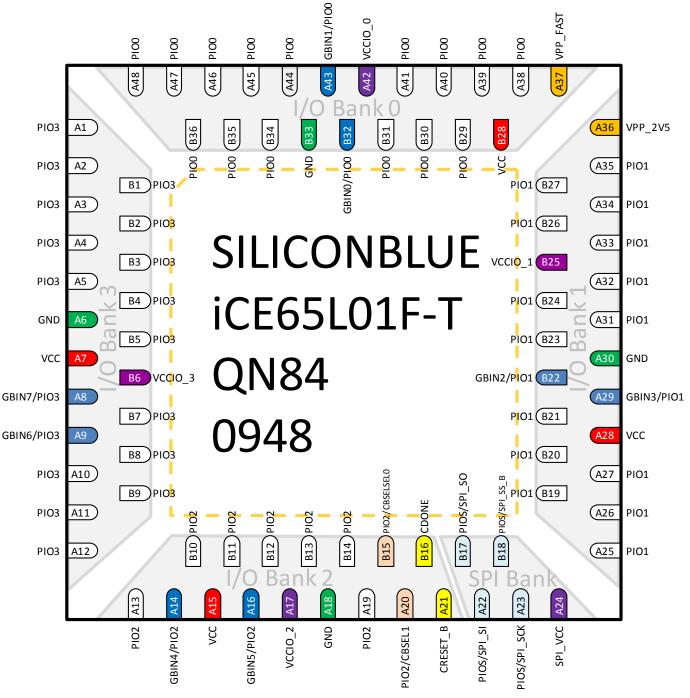

## **QN84 Quad Flat Pack No-Lead**

The QN84 is a Quad Flat Pack No-Lead package with a 0.5 mm pad pitch.

# Footprint Diagram

Figure 34 shows the iCE65 footprint diagram for the QN84 package.

Also see Table 38 for a complete, detailed pinout for the QN84 package.

The signal pins are also grouped into the four I/O Banks and the SPI interface.

Figure 34: iCE65 QN84 Quad Flat Pack No-Lead Footprint (Top View)

# **Pinout Table**

*Table 38* provides a detailed pinout table for the QN84 package. Pins are generally arranged by I/O bank, then by ball function. The QN84 package has no JTAG pins.

Table 38: iCE65 QN84 Chip-scale BGA Pinout Table

|               | lable 38: ICE65 QN84 Chip-scale BGA Pinout Table |          |      |  |  |  |  |

|---------------|--------------------------------------------------|----------|------|--|--|--|--|

| Ball Function | Ball Number                                      | Pin Type | Bank |  |  |  |  |

| GBINO/PIOO    | B32                                              | GBIN     | 0    |  |  |  |  |

| GBIN1/PIO0    | A43                                              | GBIN     | 0    |  |  |  |  |

| PIO0          | A38                                              | PIO      | 0    |  |  |  |  |

| PIO0          | A39                                              | PIO      | 0    |  |  |  |  |

| PIO0          | A40                                              | PIO      | 0    |  |  |  |  |

| PIO0          | A41                                              | PIO      | 0    |  |  |  |  |

| PIO0          | A44                                              | PIO      | 0    |  |  |  |  |

| PIO0          | A45                                              | PIO      | 0    |  |  |  |  |

| PIO0          | A46                                              | PIO      | 0    |  |  |  |  |

| PIO0          | A47                                              | PIO      | 0    |  |  |  |  |

| PIO0          | A48                                              | PIO      | 0    |  |  |  |  |

| PIO0          | B29                                              | PIO      | 0    |  |  |  |  |

| PIO0          | B30                                              | PIO      | 0    |  |  |  |  |

| PIO0          | B31                                              | PIO      | 0    |  |  |  |  |

| PIO0          | B34                                              | PIO      | 0    |  |  |  |  |

| PIOO          | B35                                              | PIO      | 0    |  |  |  |  |

| PIO0          | B36                                              | PIO      | 0    |  |  |  |  |

| VCCIO_0       | A42                                              | VCCIO    | 0    |  |  |  |  |

|               |                                                  |          | 0    |  |  |  |  |

| GBIN2/PIO1    | B22                                              | GBIN     | 1    |  |  |  |  |

| GBIN3/PIO1    | A29                                              | GBIN     | 1    |  |  |  |  |

| PIO1          | A25                                              | PIO      | 1    |  |  |  |  |

| PIO1          | A26                                              | PIO      | 1    |  |  |  |  |

| PIO1          | A27                                              | PIO      | 1    |  |  |  |  |

| PIO1          | A31                                              | PIO      | 1    |  |  |  |  |

| PIO1          | A32                                              | PIO      | 1    |  |  |  |  |

| PIO1          | A33                                              | PIO      | 1    |  |  |  |  |

| PIO1          | A34                                              | PIO      | 1    |  |  |  |  |

| PIO1          | A35                                              | PIO      | 1    |  |  |  |  |

| PIO1          | B19                                              | PIO      | 1    |  |  |  |  |

| PIO1          | B20                                              | PIO      | 1    |  |  |  |  |

| PIO1          | B21                                              | PIO      | 1    |  |  |  |  |

| PIO1          | B23                                              | PIO      | 1    |  |  |  |  |

| PIO1          | B24                                              | PIO      | 1    |  |  |  |  |

| PIO1          | B26                                              | PIO      | 1    |  |  |  |  |

| PIO1          | B27                                              | PIO      | 1    |  |  |  |  |

| VCCIO_1       | B25                                              | VCCIO    | 1    |  |  |  |  |

| CDONE         | B16                                              | CONFIG   | 2    |  |  |  |  |

| CRESET_B      | A21                                              | CONFIG   | 2    |  |  |  |  |

| GBIN4/PIO2    | A14                                              | GBIN     | 2    |  |  |  |  |

| GBIN5/PIO2    | A16                                              | GBIN     | 2    |  |  |  |  |

| PIO2          | A13                                              | PIO      | 2    |  |  |  |  |

| PIO2          | B12                                              | PIO      | 2    |  |  |  |  |

| PIO2          | A19                                              | PIO      | 2    |  |  |  |  |

| PIO2          | B10                                              | PIO      | 2    |  |  |  |  |

| PIO2          | B11                                              | PIO      | 2    |  |  |  |  |

| PIO2          | B13                                              | PIO      | 2    |  |  |  |  |

| FIUZ          | DIO                                              | LIO      | ۷    |  |  |  |  |

| Ball Function | Ball Number | Pin Type | Bank |

|---------------|-------------|----------|------|

| PIO0          | A5          | PIO      | 0    |

| PIO0          | A6          | PIO      | 0    |

| PIOO          | A8          | PIO      | 0    |

| PIO0          | A10         | PIO      | 0    |

| PIO0          | B3          | PIO      | 0    |

| PIO0          | B4          | PIO      | 0    |

| PIO0          | B5          | PIO      | 0    |

| PIO0          | B8          | PIO      | 0    |

| PIOO          | B9          | PIO      | 0    |

| PIO0          | C5          | PIO      | 0    |

| PIOO          | C7          | PIO      | 0    |

| PIO0          | C8          | PIO      | 0    |

| PIOO          | C9          | PIO      | 0    |

| PIO0          | D5          | PIO      | 0    |

| PIO0          | D7          | PIO      | 0    |

| PIO0          | E5          | PIO      | 0    |

| PIO0          | E6          | PIO      | 0    |

| PIO0          | E7          | PIO      | 0    |

| PIO0          | F7          | PIO      | 0    |

| VCCIO 0       | В7          | VCCIO    | 0    |

|               |             |          |      |

| GBIN2/PIO1    | F9          | GBIN     | 1    |

| GBIN3/PIO1    | F8          | GBIN     | 1    |

| PIO1          | A11         | PIO      | 1    |

| PIO1          | B11         | PIO      | 1    |

| PIO1          | C11         | PIO      | 1    |

| PIO1          | D8          | PIO      | 1    |

| PIO1          | D9          | PIO      | 1    |

| PIO1          | D10         | PIO      | 1    |

| PIO1          | D11         | PIO      | 1    |

| PIO1          | E8          | PIO      | 1    |

| PIO1          | E9          | PIO      | 1    |

| PIO1          | E11         | PIO      | 1    |

| PIO1          | F10         | PIO      | 1    |

| PIO1          | G7          | PIO      | 1    |

| PIO1          | G8          | PIO      | 1    |

| PIO1          | G9          | PIO      | 1    |

| PIO1          | G10         | PIO      | 1    |

| PIO1          | H7          | PIO      | 1    |

| PIO1          | H8          | PIO      | 1    |

| PIO1          | H9          | PIO      | 1    |

| PIO1          | H10         | PIO      | 1    |

| VCCIO_1       | E10         | VCCIO    | 1    |

| CDONE         | J7          | CONFIG   | 2    |

| CRESET_B      | K7          | CONFIG   | 2    |

| GBIN4/PIO2    | L8          | GBIN     | 2    |

| GBIN5/PIO2    | L9          | GBIN     | 2    |

| PIO2          | H4          | PIO      | 2    |

| PIO2          | H5          | PIO      | 2    |

| PIO2          | H11         | PIO      | 2    |

| PIO2          | J4          | PIO      | 2    |

| PIO2          | J5          | PIO      | 2    |

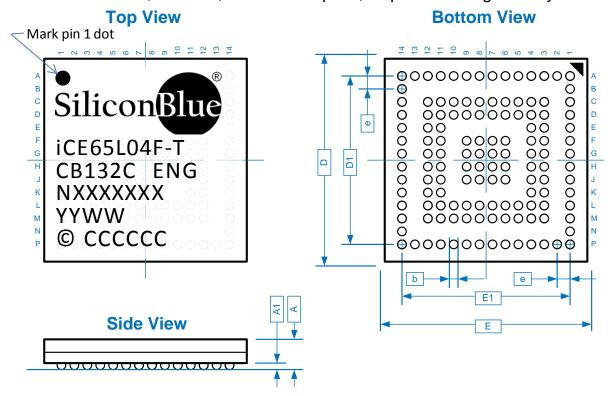

#### Package Mechanical Drawing

# Figure 44: CB132 Package Mechanical Drawing

CB132: 8 x 8 mm, 132-ball, 0.5 mm ball-pitch, chip-scale ball grid array

| Description              | Symbol        | Min. | Nominal | Max. | Units |         |  |

|--------------------------|---------------|------|---------|------|-------|---------|--|

| Number of Ball Columns X |               |      |         | 14   |       | Columns |  |

| Number of Ball Rows      | Υ             |      |         | 14   |       | Rows    |  |

| Number of Signal Balls   |               | n    |         | 132  |       | Balls   |  |

| Body Size                | Х             | Е    | 7.90    | 8.00 | 8.10  |         |  |

| body Size                | Υ             | D    | 7.90    | 8.00 | 8.10  |         |  |

| Ball Pitch               |               | е    | _       | 0.50 | _     |         |  |

| Ball Diameter            | Ball Diameter |      | 0.27    | _    | 0.37  | mm      |  |

| Edge Ball Center to      | Х             | E1   | _       | 6.50 | _     | mm      |  |

| Center                   | Υ             | D1   | _       | 6.50 | _     |         |  |

| Package Height           |               | Α    | _       | _    | 1.00  |         |  |

| Stand Off                |               | A1   | 0.16    | _    | 0.26  |         |  |

# **Top Marking Format**

| Line | Content   | Description  |  |  |

|------|-----------|--------------|--|--|

| 1    | Logo      | Logo         |  |  |

| 2    | iCE65L04F | Part number  |  |  |

| 2    | -T        | Power/Speed  |  |  |

| _    | CB132C    | Package type |  |  |

| 3    | ENG       | Engineering  |  |  |

| 4    | NXXXXXX   | Lot Number   |  |  |

| 5    | YYWW      | Date Code    |  |  |

| 6    | © CCCCCC  | Country      |  |  |

# Thermal Resistance

| Junction-to-Ambient |    |  |  |  |  |  |  |

|---------------------|----|--|--|--|--|--|--|

| OJA (°C/W)          |    |  |  |  |  |  |  |

| 0 LFM 200 LFM       |    |  |  |  |  |  |  |

| 42                  | 34 |  |  |  |  |  |  |

#### **CB196 Chip-Scale Ball-Grid Array**

The CB196 package is a chip-scale, fully-populated, ball-grid array with 0.5 mm ball pitch.

#### Footprint Diagram

Figure 45 shows the iCE65L04 chip-scale BGA footprint for the 8 x 8 mm CB196 package. The footprint for the iCE65L08 is different than the iCE64L04 footprint, as shown in Figure 46. The pinout differences are highlighted by warning diamonds (♠) in the footprint diagrams and summarized in Table 43.

Although both the iCE65L04 and iCE65L08 are both available in the CB196 package and *almost* completely pin compatible, there are differences as shown in Table 43.

Figure 31 shows the conventions used in the diagram. Also see Table 42 for a complete, detailed pinout for the 196-ball chip-scale BGA packages. The signal pins are also grouped into the four I/O Banks and the SPI interface.

| Ball Function | Ball Number | Pin Type | Bank |

|---------------|-------------|----------|------|

| PIO0          | A5          | PIO      | 0    |

| PIO0          | A6          | PIO      | 0    |

| PIO0          | A10         | PIO      | 0    |

| PIOO          | A11         | PIO      | 0    |

| PIOO          | A12         | PIO      | 0    |

|               |             |          |      |

| PIO0          | B2          | PIO      | 0    |

| PIO0          | B3          | PIO      | 0    |

| PIO0          | B4          | PIO      | 0    |

| PIO0          | B5          | PIO      | 0    |

| PIO0          | B6          | PIO      | 0    |

| PIO0          | B8          | PIO      | 0    |

| PIO0          | B9          | PIO      | 0    |

| PIO0          | B10         | PIO      | 0    |

| PIO0          | B11         | PIO      | 0    |

| PIOO          | C4          | PIO      | 0    |

| PIOO          | C5          | PIO      | 0    |

| PIO0          | C6          | PIO      | 0    |

|               |             |          |      |

| PIO0          | C7          | PIO      | 0    |

| PIO0          | C8          | PIO      | 0    |

| PIO0          | C9          | PIO      | 0    |

| PIO0          | C10         | PIO      | 0    |

| PIO0          | C11         | PIO      | 0    |

| PIO0          | D5          | PIO      | 0    |

| PIO0          | D6          | PIO      | 0    |

| PIO0          | D7          | PIO      | 0    |

| PIO0          | D8          | PIO      | 0    |

| PIO0          | D9          | PIO      | 0    |

| PIO0          | D10         | PIO      | 0    |

| PIOO          | E6          | PIO      | 0    |

| PIOO          | E8          | PIO      | 0    |

| PIO0          | E9          |          | 0    |

|               |             | PIO      |      |

| VCCIO_0       | A8          | VCCIO    | 0    |

| VCCIO_0       | F6          | VCCIO    | 0    |

| GBIN2/PIO1    | F10         | GBIN     | 1    |

| GBIN3/PIO1    | G12         | GBIN     | 1    |

| PIO1          | B13         | PIO      | 1    |

| PIO1          | B14         | PIO      | 1    |

| PIO1          | C12         | PIO      | 1    |

| PIO1          | C13         | PIO      | 1    |

| PIO1          | C13         | PIO      | 1    |

| PIO1          | D11         | PIO      | 1    |

|               |             |          |      |

| PIO1          | D12         | PIO      | 1    |

| PIO1          | D13         | PIO      | 1    |

| PIO1          | D14         | PIO      | 1    |

| PIO1          | E10         | PIO      | 1    |

| PIO1          | E11         | PIO      | 1    |

| PIO1          | E12         | PIO      | 1    |

| PIO1          | E13         | PIO      | 1    |

| PIO1          | E14         | PIO      | 1    |

| PIO1          | F11         | PIO      | 1    |

| PIO1          | F12         | PIO      | 1    |

| PIO1          | F13         | PIO      | 1    |

| LIOI          | LTO         | LIO      | 1    |

| Ball Function         | Ball Number                                | Pin Type   | Bank |

|-----------------------|--------------------------------------------|------------|------|

| PIO1                  | F14                                        | PIO        | 1    |

| PIO1                  | G10                                        | PIO        | 1    |

| PIO1                  | G11                                        | PIO        | 1    |

| PIO1                  | G13                                        | PIO        | 1    |

| PIO1                  | G14                                        | PIO        | 1    |

| PIO1                  | H10                                        | PIO        | 1    |

| PIO1                  | H11                                        | PIO        | 1    |

| PIO1                  | H12                                        | PIO        | 1    |

| PIO1                  | H13                                        | PIO        | 1    |

| PIO1                  | J10                                        | PIO        | 1    |

| PIO1                  | J11                                        | PIO        | 1    |

| PIO1                  | J12                                        | PIO        | 1    |

| PIO1                  | J13                                        | PIO        | 1    |

| PIO1                  | K11                                        | PIO        | 1    |

| PIO1                  | K12                                        | PIO        | 1    |

| PIO1                  | K14                                        | PIO        | 1    |

| PIO1                  | L13                                        | PIO        | 1    |

| PIO1                  | L14                                        | PIO        | 1    |

| PIO1                  | M13                                        | PIO        | 1    |

| TCK                   | L12                                        | JTAG       | 1    |

| TDI                   | M12                                        | JTAG       | 1    |

| TDO                   | N14                                        | JTAG       | 1    |

| TMS                   | P14                                        | JTAG       | 1    |

| TRST_B                | M14                                        | JTAG       | 1    |

| VCCIO_1               | F9                                         | VCCIO      | 1    |

| VCCIO_1               | H14                                        | VCCIO      | 1    |

|                       |                                            |            |      |

| CDONE                 | M10                                        | CONFIG     | 2    |

| CRESET_B              | L10                                        | CONFIG     | 2    |

| <b>GBIN4/PIO2 (♦)</b> | <i>iCE65L04:</i> L7                        | GBIN       | 2    |

|                       | <i>iCE65L08:</i> N8                        |            |      |

| GBIN5/PIO2 (♦)        | <i>iCE65L04:</i> P5<br><i>iCE65L08:</i> M7 | GBIN       | 2    |

| PIO2                  | K5                                         | PIO        | 2    |

| PIO2                  | K6                                         | PIO        | 2    |

| PIO2                  | K7                                         | PIO        | 2    |

| PIO2                  | K8                                         | PIO        | 2    |

| PIO2                  | K9                                         | PIO        | 2    |

| PIO2                  | L4                                         | PIO        | 2    |

| PIO2                  | L5                                         | PIO        | 2    |

| PIO2                  | L6                                         | PIO        | 2    |

| PIO2                  | L8                                         | PIO        | 2    |

| PIO2                  | M3                                         | PIO        | 2    |

| PIO2                  | M4                                         | PIO        | 2    |

| PIO2                  | M6                                         | PIO        | 2    |

| PIO2 ( <b>♦</b> )     | <i>iCE65L04:</i> M7                        | PIO        | 2    |

| DIO2                  | <i>iCE65L08:</i> P5                        | DIO        | 2    |

| PIO2<br>PIO2          | M8<br>M9                                   | PIO<br>PIO | 2 2  |

| PIO2                  | N3                                         | PIO        | 2    |

| PIO2                  | N4                                         | PIO        | 2    |

| PIO2                  | N5                                         | PIO        | 2    |

| PIO2                  | N6                                         | PIO        | 2    |

| FIUZ                  | INU                                        | LIO        |      |

#### Package Mechanical Drawing

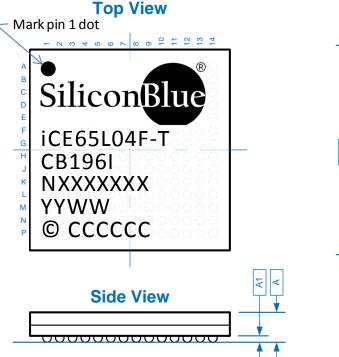

# Figure 47: (a) iCE65L04 CB196 Package Mechanical Drawing

CB196: 8 x8 mm, 196-ball, 0.5 mm ball-pitch, fully-populated, chip-scale ball grid array

Symbol

Ε

D

е

b E1

D1

Α

Α1

Χ

Χ

Description

Number of Ball Columns

Number of Ball Rows

Number of Signal Balls

Body Size

Edge Ball Center to Center

Ball Pitch

**Ball Diameter**

Package Height

Stand Off

**Bottom View**

# **Top Marking Format**

| Min. | Nominal | Max. | Units   |  |  |

|------|---------|------|---------|--|--|

|      | 14      |      | Columns |  |  |

|      | 14      |      | Rows    |  |  |

|      | 196     |      | Balls   |  |  |

| 7.90 | 8.00    | 8.10 |         |  |  |

| 7.90 | 8.00    | 8.10 |         |  |  |

| _    | 0.50    | _    |         |  |  |

| 0.27 | _       | 0.37 |         |  |  |

| _    | 6.50    |      | mm      |  |  |

| _    | 6.50    | _    |         |  |  |

| _    | _       | 1.00 |         |  |  |

| 0.16 | _       | 0.26 |         |  |  |

| Content   | Description                                                  |  |

|-----------|--------------------------------------------------------------|--|

| Logo      | Logo                                                         |  |

| iCE65L04F | Part number                                                  |  |

| -T        | Power/Speed                                                  |  |

| CB196I    | Package type                                                 |  |

| ENG       | Engineering                                                  |  |

| NXXXXXX   | Lot Number                                                   |  |

| YYWW      | Date Code                                                    |  |

| © CCCCCC  | Country                                                      |  |

|           | Logo<br>iCE65L04F<br>-T<br>CB196I<br>ENG<br>NXXXXXXX<br>YYWW |  |

# Thermal Resistance

| Junction-to-Ambient |  |  |  |  |  |

|---------------------|--|--|--|--|--|

| OJA (°C/W)          |  |  |  |  |  |

| 0 LFM 200 LFM       |  |  |  |  |  |

| 42 34               |  |  |  |  |  |

#### Package Mechanical Drawing

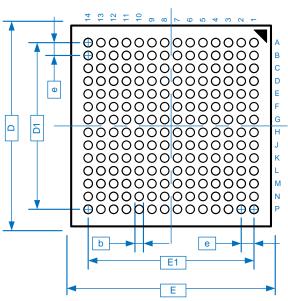

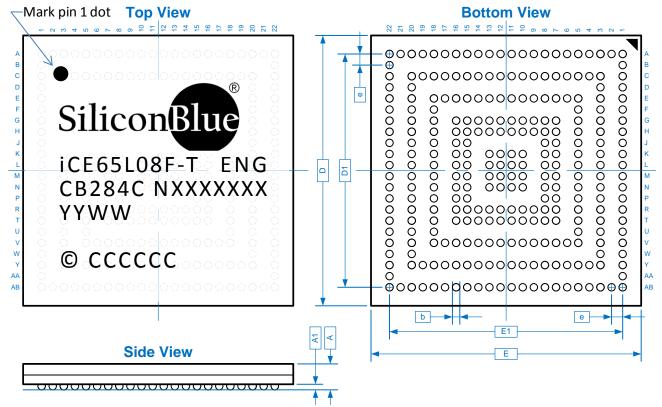

# Figure 49: CB284 Package Mechanical Drawing

| Description            | Symbol        | Min. | Nominal | Max.  | Units |         |  |

|------------------------|---------------|------|---------|-------|-------|---------|--|

| Number of Ball Columns | Х             |      |         | 22    |       | Columns |  |

| Number of Ball Rows    | Υ             |      |         | 22    |       | Rows    |  |

| Number of Signal Balls |               | n    |         | 284   |       | Balls   |  |

| Body Size              |               | Е    | 11.90   | 12.00 | 12.10 |         |  |

|                        |               | D    | 11.90   | 12.00 | 12.10 |         |  |

| Ball Pitch             |               | е    | _       | 0.50  | _     |         |  |

| Ball Diameter          | Ball Diameter |      | 0.27    | _     | 0.37  | mm      |  |

| Edge Ball Center to    | Х             | E1   | _       | 10.50 | _     | '''''   |  |

| Center                 | Υ             | D1   | _       | 10.50 | _     |         |  |

| Package Height         |               | Α    | _       | _     | 1.00  |         |  |

| Stand Off              |               | A1   | 0.16    | _     | 0.26  |         |  |

# **Top Marking Format**

| Top Warking Format |           |                  |  |  |  |

|--------------------|-----------|------------------|--|--|--|

| Line               | Content   | Description      |  |  |  |

| 1                  | Logo      | Logo             |  |  |  |

|                    | iCE65L08F | Part number      |  |  |  |

| 2                  | -T        | Power/Speed      |  |  |  |

|                    | ENG       | Engineering      |  |  |  |

| 3                  | CB284C    | Package type and |  |  |  |

|                    | NXXXXXX   | Lot number       |  |  |  |

| 4                  | YYWW      | Date Code        |  |  |  |

| 5                  | N/A       | Blank            |  |  |  |

| 6                  | © CCCCCC  | Country          |  |  |  |

#### Thermal Resistance

| THE THAT            | (CSIStario |  |  |  |  |  |  |

|---------------------|------------|--|--|--|--|--|--|

| Junction-to-Ambient |            |  |  |  |  |  |  |

| OJA (°C/W)          |            |  |  |  |  |  |  |

| 0 LFM               | 200 LFM    |  |  |  |  |  |  |

| 35                  | 28         |  |  |  |  |  |  |

#### **RAM4K Block**

Table 56 provides timing information for the logic in a RAM4K block, which includes the paths shown in Figure 59.

Figure 59: RAM4K Timing Circuit

**Table 56: Typical RAM4K Block Timing**

|                     |         |            | rubic bor Typical Idai In Bi                                               | • • • • • • • • • • • • • • • • • • • • | 9     |          |       |       |

|---------------------|---------|------------|----------------------------------------------------------------------------|-----------------------------------------|-------|----------|-------|-------|

|                     |         |            | Device: iCE65                                                              | L01                                     |       | L04, L08 |       |       |

|                     |         |            | Power/Speed Grade                                                          | <b>-</b> T                              | -L    | -L       | -Т    |       |

|                     |         |            | Nominal VCC                                                                | 1.2 V                                   | 1.0 V | 1.2 V    | 1.2 V |       |

| Symbol              | From    | То         | Description                                                                | Тур.                                    | Тур.  | Тур.     | Тур.  | Units |

|                     | Write 9 | Setup/Ho   | old Time                                                                   |                                         |       |          |       |       |

| t <sub>SUWD</sub>   | PIO     | GBIN       | Minimum write data setup time on PIO                                       | 0.6                                     | 3.1   | 1.7      | 0.8   | ns    |

|                     | input   | input      | inputs before active clock edge on GBIN input, include interconnect delay. |                                         |       |          |       |       |

| t <sub>HDWD</sub>   | GBIN    | PIO        | Minimum write data hold time on PIO                                        | 0                                       | 0     | 0        | 0     | ns    |

|                     | input   | input      | inputs after active clock edge on GBIN                                     |                                         |       |          |       |       |

|                     | Dood    | No als Oud | input, including interconnect delay.                                       |                                         |       |          |       |       |

|                     |         |            | put-Time                                                                   |                                         |       |          |       |       |

| t <sub>CKORD</sub>  | RCLK    | PIO        | Clock-to-output delay from RCLK input                                      | 5.6                                     | 17.1  | 9.1      | 7.3   | ns    |

|                     | clock   | output     | pin, through RAM4K RDATA output flip-<br>flop to PIO output pad, including |                                         |       |          |       |       |

|                     | input   |            | interconnect delay.                                                        |                                         |       |          |       |       |

| t <sub>GBCKRM</sub> | GBIN    | RCLK       | Global Buffer Input (GBIN) delay, though                                   | 2.1                                     | 7.3   | 3.8      | 2.6   | ns    |

|                     | input   | clock      | Global Buffer (GBUF) clock network to                                      |                                         |       |          |       |       |

|                     |         | input      | the RCLK clock input.                                                      |                                         |       |          |       |       |

|                     | Write a | and Read   | Clock Characteristics                                                      |                                         |       |          |       |       |

| t <sub>RMWCKH</sub> | WCLK    | WCLK       | Write clock High time                                                      | 0.54                                    | 1.14  | 0.54     | 0.54  | ns    |

| t <sub>RMWCKL</sub> | RCLK    | RCLK       | Write clock Low time                                                       | 0.63                                    | 1.32  | 0.63     | 0.63  | ns    |

| t <sub>RMWCYC</sub> |         |            | Write clock cycle time                                                     | 1.27                                    | 2.64  | 1.27     | 1.27  | ns    |

| F <sub>WMAX</sub>   |         |            | Sustained write clock frequency                                            | 256                                     | 256   | 256      | 256   | MHz   |