Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                                              |

|--------------------------------|------------------------------------------------------------------------------|

| Product Status                 | Obsolete                                                                     |

| Number of LABs/CLBs            | 440                                                                          |

| Number of Logic Elements/Cells | 3520                                                                         |

| Total RAM Bits                 | 81920                                                                        |

| Number of I/O                  | 150                                                                          |

| Number of Gates                | -                                                                            |

| Voltage - Supply               | 1.14V ~ 1.26V                                                                |

| Mounting Type                  | Surface Mount                                                                |

| Operating Temperature          | 0°C ~ 70°C (TA)                                                              |

| Package / Case                 | 196-VFBGA, CSPBGA                                                            |

| Supplier Device Package        | 196-CSPBGA (8x8)                                                             |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/ice65l04f-tcb196c |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Note the clock differences between the iCE65L04 and iCE65L08 in the CB196 package.

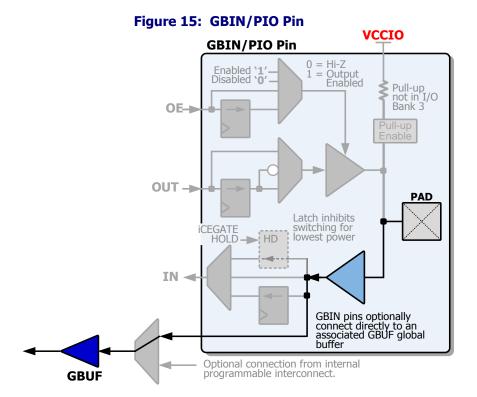

# Differential Global Buffer Input

All eight global buffer inputs support single-ended I/O standards such as LVCMOS. Global buffer GBUF7 in I/O Bank 3 also provides an optional direct SubLVDS, LVDS, or LVPECL differential clock input, as shown in Figure 16. The GBIN7 and its associated differential I/O pad accept a differential clock signal. A 100  $\Omega$  termination resistor is required across the two pads. Optionally, swap the outputs from the LVDS or LVPECL clock driver to invert the clock as it enters the iCE65 device.

Figure 16: LVDS or LVPECL Clock Input

Table 15 lists the pin or ball numbers for the differential global buffer input by package style. Although this differential input is the only one that connects directly to a global buffer, other differential inputs can connect to a global buffer using general-purpose interconnect, with slightly more signal delay.

Table 15: Differential Global Buffer Input Ball/Pin Number by Package

| Differential Global |      |       |       |       |             |       |

|---------------------|------|-------|-------|-------|-------------|-------|

| Buffer Input        | I/O  |       |       | `L04  | <b>`L08</b> |       |

| (GBIN)              | Bank | VQ100 | CB132 | CB196 | CB196       | CB284 |

| GBIN7/DPxxB         | 2    | 13    | N/A   | G1    | H3          | L5    |

| DPxxA               | 3    | 12    | N/A   | G2    | H4          | L3    |

The differential global buffer input is not available for iCE65 devices in the CB132 package. This restriction is an artifact of the pin compatibility between the CB132 and CB284 package.

Note the clock differences between the iCE65L04 and iCE65L08 in the CB196 package.

## Automatic Global Buffer Insertion, Manual Insertion

The iCEcube development software automatically assigns high-fanout signals to a global buffer. However, to manual insert a global buffer input/global buffer (GBIN/GBUF) combination, use the **SB\_IO\_GB** primitive. To insert just a global buffer (GBUF), use the **SB\_GB** primitive.

#### Global Hi-Z Control

The global high-impedance control signal, GHIZ, connects to all I/O pins on the iCE65 device. This GHIZ signal is automatically asserted throughout the configuration process, forcing all user-I/O pins into their high-impedance state. Similarly, the PIO pins can be forced into their high-impedance state via the JTAG controller.

#### **Global Reset Control**

The global reset control signal connects to all PLB and PIO flip-flops on the iCE65 device. The global reset signal is automatically asserted throughout the configuration process, forcing all flip-flops to their defined wake-up state. For PLB flip-flops, the wake-up state is always reset, regardless of the PLB flip-flop primitive used in the application. See Table 3 for more information.

The PIO flip-flops are always reset during configuration, although the output flip-flop can be inverted before leaving the iCE65 device, as shown in Figure 11.

#### **RAM**

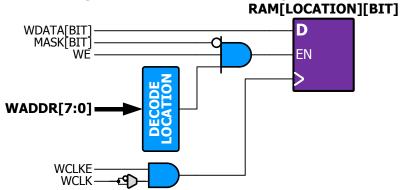

Each iCE65 device includes multiple high-speed synchronous RAM blocks (RAM4K), each 4Kbit in size. As shown in Table 16 a single iCE65 integrates between 16 to 96 such blocks. Each RAM4K block is generically a 256-word deep by 16-bit wide, two-port register file, as illustrated in Figure 17. The input and output connections, to and from a RAM4K block, feed into the programmable interconnect resources.

Figure 17: RAM4K Memory Block **Write Port Read Port RDATA[15:0]** WDATA[15:0] MASK[15:0] **WADDR[7:0] RADDR[7:0]** RAM4K **RAM Block** WE (256x16) WCLKE **RCLKE** WCLK\_\_ RCLK

Table 16: RAM4K Blocks per Device

| Device   | RAM4K Blocks | Default<br>Configuration | RAM Bits per Block | Block RAM Bits |

|----------|--------------|--------------------------|--------------------|----------------|

| iCE65L01 | 16           |                          |                    | 64K            |

| iCE65L04 | 20           | 256 x 16                 | 4K<br>(4,096)      | 80K            |

| iCE65L08 | 32           |                          | (,,,,,             | 128K           |

Using programmable logic resources, a RAM4K block implements a variety of logic functions, each with configurable input and output data width.

- Random-access memory (RAM)

- ♦ Single-port RAM with a common address, enable, and clock control lines

- ♦ Two-port RAM with separate read and write control lines, address inputs, and enable

Figure 18: RAM4K Bit Write Logic

When the WCLKE signal is Low, the clock to the RAM4K block is disabled, keeping the RAM in its lowest power mode.

**Table 18: RAM4K Write Operations**

|           | WDATA[15:0] | MASK[15:0]  | WADDR[7:0] | WE     | WCLKE  | WCLK     |               |

|-----------|-------------|-------------|------------|--------|--------|----------|---------------|

|           |             |             |            | Write  | Clock  |          |               |

| Operation | Data        | Mask Bit    | Address    | Enable | Enable | Clock    | RAM Location  |

| Disabled  | X           | X           | X          | Χ      | Χ      | 0        | No change     |

| Disabled  |             |             |            |        | 0      | Χ        | No change     |

| Disabled  | X           | X           | X          | 0      | Χ      | Χ        | No change     |

| Write     | WDATA[i]    | MASK[i] = 0 | WADDR      | 1      | 1      | <b>↑</b> | RAM[WADDR][i] |

| Data      |             |             |            |        |        |          | = WDATA[i]    |

| Masked    | X           | MASK[i] = 1 | WADDR      | 1      | 1      | <b>↑</b> | RAM[WADDR][i] |

| Write     |             |             |            |        |        |          | = No change   |

To write data into the RAM4K block, perform the following operations.

- ◆ Supply a valid address on the WADDR[7:0] address input port

- ◆ Supply valid data on the WDATA[15:0] data input port

- ◆ To write or mask selected data bits, set the associated MASK input port accordingly. For example, write operations on data bit D[i] are controlled by the associated MASK[i] input.

- MASK[i] = 0: Write operations are enabled for data line WDATA[i]

- MASK[i] = 1: Mask write operations are disabled for data line WDATA[i]

- ◆ Enable the RAM4K write port (WE = 1)

- ◆ Enable the RAM4K write clock (WCLKE = 1)

- ◆ Apply a rising clock edge on WCLK (assuming that the clock is not inverted)

# **Read Operations**

Figure 19 shows the logic involved in reading a location from RAM. Table 19 describes various read operations for a RAM4K block. By default, all RAM4K read operations are synchronized to the rising edge of RCLK although the clock is invertible as shown in Figure 19.

23

Figure 19: RAM4K Read Logic Select RAM[LOCATION] **Output Register** Location • RDATA[15:0] ΕN RADDR[7:0] **RCLKE**

**Table 19: RAM4K Read Operations**

|                                                             | RADDR[7:0] | RE     | RCLKE | RCLK  |             |

|-------------------------------------------------------------|------------|--------|-------|-------|-------------|

| Out and the same                                            | Addoor     | Read   | Clock | ClI-  | DD4T4[45.0] |

| Operation                                                   | Address    | Enable | Enabe | Clock | RDATA[15:0] |

| After configuration, before first valid Read Data operation | X          | X      | X     | X     | Undefined   |

| Disabled                                                    | X          | X      | Χ     | 0     | No Change   |

| Disabled                                                    |            | X      | 0     | X     | No Change   |

| Disabled                                                    | X          | 0      | Χ     | Χ     | No change   |

| Read Data                                                   | RADDR      | 1      | 1     | 1     | RAM[RADDR]  |

To read data from the RAM4K block, perform the following operations.

- ◆ Supply a valid address on the RADDR[7:0] address input port

- ◆ Enable the RAM4K read port (RE = 1)

- ◆ Enable the RAM4K read clock (RCLKE = 1)

- ◆ Apply a rising clock edge on RCLK

- ◆ After the clock edge, the RAM contents located at the specified address (RADDR) appear on the RDATA output port

## Read Data Register Undefined Immediately after Configuration

Unlike the flip-flops in the Programmable Logic Blocks and Programmable I/O pins, the RDATA[15:0] read data output register is not automatically reset after configuration. Consequently, immediately following configuration and before the first valid Read Data operation, the initial RDATA[15:0] read value is undefined.

#### **Pre-loading RAM Data**

The data contents for a RAM4K block can be optionally pre-loaded during iCE65 configuration. If not pre-loaded during configuration, then the RAM contents must be initialized by the iCE65 application before the RAM contents are valid.

Pre-loading the RAM data in the configuration bitstream increases the size of the configuration image accordingly.

# **RAM Contents Preserved during Configuration**

RAM contents are preserved (write protected) during configuration, assuming that voltage supplies are maintained throughout. Consequently, data can be passed between multiple iCE65 configurations by leaving it in a RAM4K block and then skipping pre-loading during the subsequent reconfiguration. See "Cold Boot Configuration Option" and "Warm Boot Configuration Option" for more information.

#### **Low-Power Setting**

To place a RAM4K block in its lowest power mode, keep WCLKE = 0 and RCLKE = 0. In other words, when not actively using a RAM4K block, disable the clock inputs.

AP\_VCCIO VCCIO\_2 VCCIO\_2 10 kΩ€ **≨**10 kΩ AP\_VCCIO **CDONE** iCE65 (I/O Bank 2) CRESET B ₿ SPI\_VCC **Application** Processor SPI\_SI SPI\_SO iCE65 SPI\_SS\_B (SPI Bank) SPI\_SCK **\$**10 kΩ

Figure 28: iCE65 SPI Peripheral Configuration Interface

The SPI control signals are defined in Table 25.

Table 29: SPI Peripheral Configuration Interface Pins (SPI\_SS\_B Low when CRESET\_B Released)

| Signal   |            | iCE65 I/O |                                                                                                                                                                                                 |

|----------|------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name     | Direction  | Supply    | Description                                                                                                                                                                                     |

| CDONE    | AP ← iCE65 | VCCIO_2   | Configuration Done output from iCE65. Connect to a $10k\Omega$ pull-up resistor to the application processor I/O voltage, AP_VCC.                                                               |

| CRESET_B | AP → iCE65 |           | Configuration Reset input on iCE65. Typically driven by AP using an open-drain driver, which also requires a $10k\Omega$ pull-up resistor to VCCIO_2.                                           |

| SPI_VCC  | Supply     | SPI_VCC   | SPI Flash PROM voltage supply input.                                                                                                                                                            |

| SPI_SI   | AP → iCE65 |           | SPI Serial Input to the iCE65 FPGA, driven by the application processor.                                                                                                                        |

| SPI_SO   | AP ← iCE65 |           | SPI Serial Output from CE65 device to the application processor. Not actually used during SPI peripheral mode configuration but required if the SPI interface is also used to program the NVCM. |

| SPI_SS_B | AP → iCE65 |           | SPI Slave Select output from the application processor. Active Low. Optionally hold Low prior to configuration using a $10k\Omega$ pull-down resistor to ground.                                |

| SPI_SCK  | AP → iCE65 |           | SPI Slave Clock output from the application processor.                                                                                                                                          |

After configuration, the SPI port pins are available to the user-application as additional PIO pins, supplied by the SPI VCC input voltage, essentially providing a fifth "mini" I/O bank.

### **Enabling SPI Configuration Interface**

The optional 10 kΩ pull-down resistor on the SPI SS B signal ensures that the iCE65 FPGA powers up in the SPI peripheral mode. Optionally, the application processor drives the SPI SS B pin Low when CRESET B is released, forcing the iCE65 FPGA into SPI peripheral mode.

# SPI Peripheral Configuration Process

Figure 29 illustrates the interface timing for the SPI peripheral mode and Figure 30 outlines the resulting configuration process. The actual timing specifications appear in Table 60. The application processor (AP) begins by driving the iCE65 CRESET B pin Low, resetting the iCE65 FPGA. Similarly, the AP holds the iCE65's SPI SS B pin Low. The AP must hold the CRESET B pin Low for at least 200 ns. Ultimately, the AP either releases the CRESET B pin and allows it to float High via the  $10 \text{ k}\Omega$  pull-up resistor to VCCIO 2 or drives CRESET B High. The iCE65 FPGA enters SPI peripheral mode when the CRESET B pin returns High while the SPI SS B pin is Low.

# iCE65 Ultra Low-Power mobileFPGA<sup>™</sup> Family

After driving CRESET B High or allowing it to float High, the AP must wait a minimum of  $t_{CR}$  SCK  $\mu$ s, (see Table 60) allowing the iCE65 FPGA to clear its internal configuration memory.

After waiting for the configuration memory to clear, the AP sends the configuration image generated by the iCEcube development system. An SPI peripheral mode configuration image must not use the ColdBoot or WarmBoot options. Send the entire configuration image, without interruption, serially to the iCE65's SPI\_SI input on the falling edge of the SPI SCK clock input. Once the AP sends the 0x7EAA997E synchronization pattern, the generated SPI SCK clock frequency must be within the specified 1 MHz to 25 MHz range (40 ns to 1 µs clock period) while sending the configuration image. Send each byte of the configuration image with most-significant bit (msb) first. The AP sends data to the iCE65 FPGA on the falling edge of the SPI\_SCK clock. The iCE65 FPGA internally captures each incoming SPI SI data bit on the rising edge of the SPI SCK clock. The iCE65's SPI SO output pin is not used during SPI peripheral mode but must connect to the AP if the AP also programs the iCE65's Nonvolatile Configuration Memory (NVCM).

Prior to sending the iCE65 configuration image, an SPI NVCM shut-off sequence must be sent. See AN014 for details.

The iCE65 configuration image must be sent as one contiguous stream without interruption. The SPI SCK clock period must be between 40 ns to 1 µs (1 MHz to 25 MHz).

After sending the entire image, the iCE65 FPGA releases the CDONE output allowing it to float High via the  $10 \text{ k}\Omega$ pull-up resistor to AP VCC. If the CDONE pin remains Low, then an error occurred during configuration and the AP should handle the error accordingly for the application.

After the CDONE output pin goes High, send at least 49 additional dummy bits, effectively 49 additional SPI\_SCK clock cycles measured from rising-edge to rising-edge.

After the additional SPI CLK cycles, the SPI interface pins then become available to the user application loaded in FPGA.

To reconfigure the iCE65 FPGA or to load a different configuration image, merely restart the configuration process by pulsing CRESET B Low or power-cycling the FPGA.

**CDONE** 49 SPI\_SCK Cycles Rising edge to rising edge ≥ 200 ns CRESET B iCE65L01: ≥ 800 µs iCE65L04: ≥ 800 µs iCE65L08: ≥ 1200 µs iCE65 clears internal configuration memory iCE65 enters SPI Peripheral mode with SPI SS B = Low on pins available led I/O pins rising edge of CRESET\_B iCE65 captures SPI SI data on SPI SCK rising edge Configuration image always starts with 0x7EAA997E synchronization word Interface as user-defi SPI\_SI 8 Χ X X X**Entire Configuration Images** Don't Care Send most-significant bit of each byte first SP Pulled High in SPI SO pin via internal pull-up resistor. Not used for SPI Peripheral mode configuration. Used when programming NVCM via SPI itnterface. SPI\_SO

Figure 29: Application Processor Waveforms for SPI Peripheral Mode Configuration Process

The iCE65 configuration image must be sent as one contiguous stream without interruption. The SPI\_SCK clock period must be between 40 ns to 1 µs (1 MHz to 25 MHz).

# iCE65 Ultra Low-Power mobileFPGA<sup>™</sup> Family

Table 31 describes how to maintain voltage compatibility for two interface scenarios. The easiest interface is when the Application Processor's (AP) I/O supply rail and the iCE65's SPI and VCCIO\_2 bank supply rails all connect to the same voltage. The second scenario is when the AP's I/O supply voltage is greater than the iCE65's VCCIO\_2 supply voltage.

**Table 31:** CRESET\_B and CDONE Voltage Compatibility

|                                                | CRESET_B |                                  |                                              |             |                                                                                                                                                                                                                                                                                                                |

|------------------------------------------------|----------|----------------------------------|----------------------------------------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                |          | Open-                            |                                              | CDONE Pull- |                                                                                                                                                                                                                                                                                                                |

| Condition                                      | Direct   | Drain                            | Pull-up                                      | up          | Requirement                                                                                                                                                                                                                                                                                                    |

| VCCIO_AP<br>= VCC_SPI<br>VCCIO_AP<br>= VCCIO_2 | OK       | OK with<br>pull-up               | Required if<br>using<br>open-drain<br>output | Recommended | AP can directly drive CRESET_B High and Low although an open-drain output recommended is if multiple devices control CRESET_B. If using an open-drain driver, the CRESET_B input must include a 10 k $\Omega$ pull-up resistor to VCCIO_2. The 10 k $\Omega$ pull-up resistor to AP_VCCIO is also recommended. |

| AP_VCCIO<br>> VCCIO_2                          | N/A      | Required,<br>requires<br>pull-up | Required                                     | Required    | The AP must control CRESET_B with an open-drain output, which requires a $10~\text{k}\Omega$ pull-up resistor to VCCIO_2. The $10~\text{k}\Omega$ pull-up resistor to AP_VCCIO is required.                                                                                                                    |

# **JTAG Boundary Scan Port**

#### **Overview**

Each iCE65 device includes an IEEE 1149.1-compatible JTAG boundary-scan port. The port supports printed-circuit board (PCB) testing and debugging. It also provides an alternate means to configure the iCE65 device.

# **Signal Connections**

The JTAG port connections are listed in Table 32.

Table 32: iCE65 JTAG Boundary Scan Signals

| Signal | D: 11     |                                                                                                              |

|--------|-----------|--------------------------------------------------------------------------------------------------------------|

| Name   | Direction | Description                                                                                                  |

| TDI    | Input     | Test Data Input. Must be tied off to GND when unused. (no pull-up resistor)*                                 |

| TMS    | Input     | Test Mode Select. Must be tied off to GND when unused. (no pull-up resistor)*                                |

| TCK    | Input     | Test Clock. Must be tied off to GND when unused. (no pull-up resistor)*                                      |

| TDO    | Output    | Test Data Output.                                                                                            |

| TRST_B | Input     | Test Reset, active Low. Must be Low during normal device operation. Must be High to enable JTAG operations.* |

<sup>\*</sup> Must be tied off to GND or VCCIO 1, else VCCIO 1 draws current.

Table 33 lists the ball/pin numbers for the JTAG interface by package code. The JTAG interface is available in select package types. The JTAG port is located in I/O Bank 1 along the right edge of the iCE65 device and powered by the VCCIO\_1 supply inputs. Consequently, the JTAG interface uses the associated I/O standards for I/O Bank 1.

Table 33: JTAG Interface Ball/Pin Numbers by Package

| JTAG Interface | VQ100 | CB132 | CB196 | CB284 |

|----------------|-------|-------|-------|-------|

| TDI            |       | M12   | M12   | T16   |

| TMS            |       | P14   | P14   | V18   |

| TCK            | N/A   | L12   | L12   | R16   |

| TDO            |       | N14   | N14   | U18   |

| TRST_B         |       | M14   | M14   | T18   |

# **iCE65 Pin Descriptions**

Table 36 lists the various iCE65 pins, alphabetically by name. The table indicates the directionality of the signal and the associated I/O bank. The table also indicates if the signal has an internal pull-up resistor enabled during configuration. Finally, the table describes the function of the pin.

| Table 36: iCE65 Pin Description |           |             |                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------------------------------|-----------|-------------|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Signal Name                     | Direction | I/O<br>Bank | Pull-up<br>during<br>Config | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| CDONE                           | Output    | 2           | Yes                         | Configuration Done. Dedicated output. Includes a permanent weak pull-up resistor to VCCIO_2 If driving external devices with CDONE output, connect a 10 k $\Omega$ pull-up resistor to VCCIO_2.                                                                                                                                                                                                                                                                               |

| CRESET_B                        | Input     | 2           | No                          | Configuration Reset, active Low. Dedicated input. No internal pull-up resistor. Either actively drive externally or connect a $10 \text{ k}\Omega$ pull-up resistor to VCCIO_2.                                                                                                                                                                                                                                                                                               |

| GBINO/PIOO<br>GBIN1/PIOO        | Input/IO  | 0           | Yes                         | Global buffer input from I/O Bank 0. Optionally, a full-featured PIO pin.                                                                                                                                                                                                                                                                                                                                                                                                     |

| GBIN2/PIO1<br>GBIN3/PIO1        | Input/IO  | 1           | Yes                         | Global buffer input from I/O Bank 1. Optionally, a full-featured PIO pin.                                                                                                                                                                                                                                                                                                                                                                                                     |

| GBIN4/PIO2<br>GBIN5/PIO2        | Input/IO  | 2           | Yes                         | Global buffer input from I/O Bank 2. Optionally, a full-featured PIO pin.                                                                                                                                                                                                                                                                                                                                                                                                     |

| GBIN6/PIO3                      | Input/IO  | 3           | No                          | Global buffer input from I/O Bank 3. Optionally, a full-featured PIO pin.                                                                                                                                                                                                                                                                                                                                                                                                     |

| GBIN7/PIO3                      | Input/IO  | 3           | No                          | Global buffer input from I/O Bank 3. Optionally, a full-featured PIO pin. Optionally, a differential clock input using the associated differential input pin.                                                                                                                                                                                                                                                                                                                 |

| GND                             | Supply    | All         | N/A                         | Ground. All must be connected.                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| PIOx_yy                         | I/O       | 0,1,2       | Yes                         | Programmable I/O pin defined by the iCE65 configuration bitstream. The 'x' number specifies the I/O bank number in which the I/O pin resides. The "yy' number specifies the I/O number in that bank.                                                                                                                                                                                                                                                                          |

| PIO2/CBSEL0                     | Input/IO  | 2           | Yes                         | Optional ColdBoot configuration SELect input, if ColdBoot mode is enabled. A full-featured PIO pin after configuration.                                                                                                                                                                                                                                                                                                                                                       |

| PIO2/CBSEL1                     | Input/IO  | 2           | Yes                         | Optional ColdBoot configuration SELect input, if ColdBoot mode is enabled. A full-featured PIO pin after configuration.                                                                                                                                                                                                                                                                                                                                                       |

| PIO3_yy/<br>DPwwz               | I/O       | 3           | No                          | Programmable I/O pin that is also half of a differential I/O pair. Only available in I/O Bank 3. The "yy" number specifies the I/O number in that bank. The "ww" number indicates the differential I/O pair. The 'z' indicates the polarity of the pin in the differential pair. 'A'=negative input. 'B'=positive input.                                                                                                                                                      |

| PIOS/SPI_SO                     | I/O       | SPI         | Yes                         | SPI Serial Output. A full-featured PIO pin after configuration.                                                                                                                                                                                                                                                                                                                                                                                                               |

| PIOS /SPI_SI                    | I/O       | SPI         | Yes                         | SPI Serial Input. A full-featured PIO pin after configuration.                                                                                                                                                                                                                                                                                                                                                                                                                |

| PIOS /<br>SPI_SS_B              | I/O       | SPI         | Yes                         | SPI Slave Select. Active Low. Includes an internal weak pull-up resistor to SPI_VCC during configuration. During configuration, the logic level sampled on this pin determines the configuration mode used by the iCE65 device, as shown in Figure 20. An input when sampled at the start of configuration. An input when in SPI Peripheral configuration mode (SPI_SS_B = Low). An output when in SPI Flash configuration mode. A full-featured PIO pin after configuration. |

| PIOS/<br>SPI_SCK                | I/O       | SPI         | Yes                         | SPI Slave Clock. An input when in SPI Peripheral configuration mode (SPI_SS_B = Low). An output when in SPI Flash configuration mode. A full-featured PIO pin after configuration.                                                                                                                                                                                                                                                                                            |

| TDI                             | Input     | 1           | No                          | JTAG Test Data Input. If using the JTAG interface, use a $10k\Omega$ pull-up resistor to VCCIO_1. Tie off to GND when unused.                                                                                                                                                                                                                                                                                                                                                 |

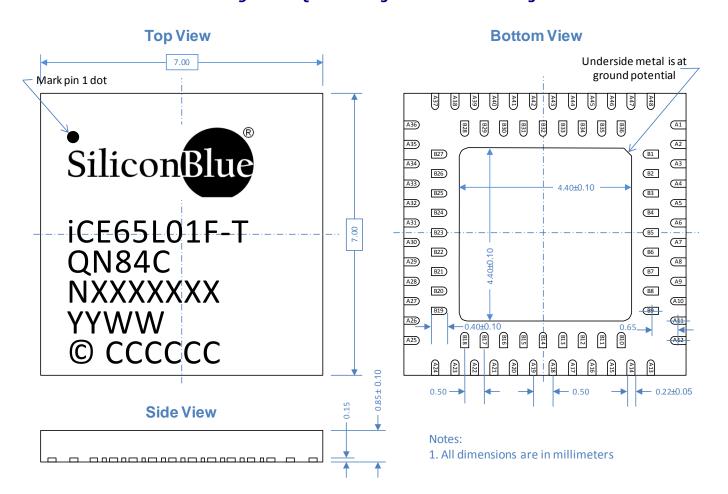

# Package Mechanical Drawing

Figure 35: QN84 Package Mechanical Drawing

# **Top Marking Format**

| Line | Content   | Description  |

|------|-----------|--------------|

| 1    | Logo      | Logo         |

| 2    | iCE65L01F | Part number  |

|      | -T        | Power/Speed  |

| 3    | QN84C     | Package type |

| 3    | ENG       | Engineering  |

| 4    | NXXXXXX   | Lot Number   |

| 5    | YYWW      | Date Code    |

| 6    | © cccccc  | Country      |

# Thermal Resistance

| Junction-to-Ambient * |    |  |  |  |

|-----------------------|----|--|--|--|

| θja (°C/W)            |    |  |  |  |

| 0 LFM 200 LFM         |    |  |  |  |

| 45                    | 44 |  |  |  |

<sup>\*</sup> With PCB thermal vias

Table 39: iCE65 VQ100 Pinout Table

|              | Table 39: ICE65 VQ10         | o Pillout Table |        |

|--------------|------------------------------|-----------------|--------|

| Pin Function | Pin Number                   | Туре            | Bank   |

| GBINO/PIOO   | 90                           | GBIN            | 0      |

| GBIN1/PIO0   | 89                           | GBIN            | 0      |

| PIO0         | 78                           | PIO             | 0      |

| PIO0         | 79                           | PIO             | 0      |

| PIO0         | 80                           | PIO             | 0      |

| PIO0         | 81                           | PIO             | 0      |

| PIO0         | 82                           | PIO             | 0      |

| PIOO         | 83                           | PIO             | 0      |

| PIO0         | 85                           | PIO             | 0      |

| PIOO         | 86                           | PIO             | 0      |

| PIO0         | 87                           | PIO             | 0      |

| PIO0         | 91                           | PIO             | 0      |

|              |                              |                 |        |

| PIO0         | 93                           | PIO             | 0      |

| PIO0         | 94                           | PIO             | 0      |

| PIO0         | 95                           | PIO             | 0      |

| PIO0         | 96                           | PIO             | 0      |

| PIO0         | 97                           | PIO             | 0      |

| PIO0         | 99                           | PIO             | 0      |

| PIO0         | 100                          | PIO             | 0      |

| VCCIO_0      | 88                           | VCCIO           | 0      |

| VCCIO_0      | 92                           | VCCIO           | 0      |

| GBIN2/PIO1   | 63                           | GBIN            | 1      |

| GBIN3/PIO1   | 62                           | GBIN            | 1      |

| PIO1         | 51                           | PIO             | 1      |

| PIO1         | 52                           | PIO             | 1      |

| PIO1         | 53                           | PIO             | 1      |

| PIO1         | 54                           | PIO             | 1      |

| PIO1         | 56                           | PIO             | 1      |

| PIO1         | 57                           | PIO             | 1      |

| PIO1         | 59                           | PIO             | 1      |

| PIO1         | 60                           | PIO             | 1      |

| PIO1         | 64                           | PIO             | 1      |

|              |                              |                 |        |

| PIO1<br>PIO1 | 65<br>66                     | PIO<br>PIO      | 1<br>1 |

| PIO1         | 68                           | PIO             | 1      |

| PIO1         | 69                           | PIO             |        |

|              |                              |                 | 1      |

| PIO1         | 71                           | PIO             | 1      |

| PIO1         | 72                           | PIO             | 1      |

| PIO1         | 73                           | PIO             | 1      |

| PIO1         | 74                           | PIO             | 1      |

| VCCIO_1      | 58                           | VCCIO           | 1      |

| VCCIO_1      | 67                           | VCCIO           | 1      |

| CDONE        | 43                           | CONFIG          | 2      |

| CRESET_B     | 44                           | CONFIG          | 2      |

| GBIN4/PIO2   | iCE65L01: 33<br>iCE65L04: 34 | GBIN            | 2      |

| GBIN5/PIO2   | iCE65L01: 36<br>iCE65L04: 33 | GBIN            | 2      |

| PIO2         | 26                           | PIO             | 2      |

| PIO2         | 27                           | PIO             | 2      |

|              | ·                            |                 | _      |

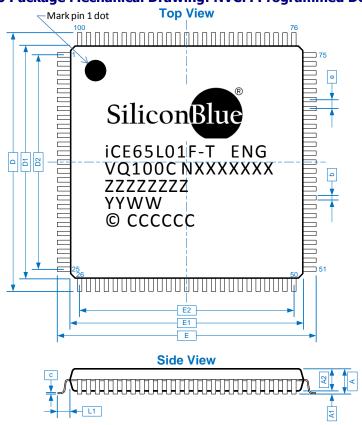

Figure 38: VQ100 Package Mechanical Drawing: NVCM Programmed Device Marking

| Description            |   | Symbol | Min. | Nominal | Max. | Units |

|------------------------|---|--------|------|---------|------|-------|

| Loado por Edgo         | Х |        |      | 25      |      |       |

| Leads per Edge         | Υ |        |      | 25      |      | Leads |

| Number of Signal Leads | 3 | n      |      | 100     |      |       |

| Maximum Size           | Х | E      | _    | 16.0    |      |       |

| (lead tip to lead tip) | Υ | D      | _    | 16.0    |      |       |

| Body Size              | Х | E1     | _    | 14.0    |      |       |

| Body Size              | Υ | D1     | _    | 14.0    | _    |       |

| Edge Pin Center to     | Х | E2     | _    | 12.0    | _    |       |

| Center                 | Υ | D2     | _    | 12.0    |      |       |

| Lead Pitch             |   | е      | _    | 0.50    | _    | mm    |

| Lead Width             |   | b      | 0.17 | 0.20    | 0.27 | mm    |

| Total Package Height   |   | Α      | _    | 1.20    | _    |       |

| Stand Off              |   | A1     | 0.05 | _       | 0.15 |       |

| Body Thickness         |   | A2     | 0.95 | 1.00    | 1.05 |       |

| Lead Length            |   | L1     |      | 1.00    | _    |       |

| Lead Thickness         |   | С      | 0.09 | _       | 0.20 |       |

| Coplanarity            |   |        | _    | 0.08    | _    |       |

# **Top Marking Format**

| Line | Content   | Description        |

|------|-----------|--------------------|

| 1    | Logo      | Logo               |

|      | iCE65L01F | Part number        |

| 2    | -T        | Power/Speed        |

|      | ENG       | Engineering        |

| 3    | VQ100C    | Package type and   |

|      | NXXXXXX   | Lot number         |

| 4    | ZZZZZZZZ  | NVCM Program. code |

| 5    | YYWW      | Date Code          |

| 6    | © CCCCCC  | Country            |

# Thermal Resistance

| Junction-to-Ambient |       |  |  |  |  |

|---------------------|-------|--|--|--|--|

| θJA (°C/W)          |       |  |  |  |  |

| 0 LFM 200 LFM       |       |  |  |  |  |

| 38                  | 38 32 |  |  |  |  |

# iCE65 Ultra Low-Power mobileFPGA<sup>™</sup> Family

| Ball Function | Ball Number | Pin Type | Bank |

|---------------|-------------|----------|------|

| GND           | K2          | GND      | GND  |

| GND           | K10         | GND      | GND  |

| VCC           | В6          | VCC      | VCC  |

| VCC           | F1          | VCC      | VCC  |

| VCC           | F11         | VCC      | VCC  |

| VCC           | K6          | VCC      | VCC  |

| VPP_2V5       | C10         | VPP      | VPP  |

| VPP_FAST      | A9          | VPP      | VPP  |

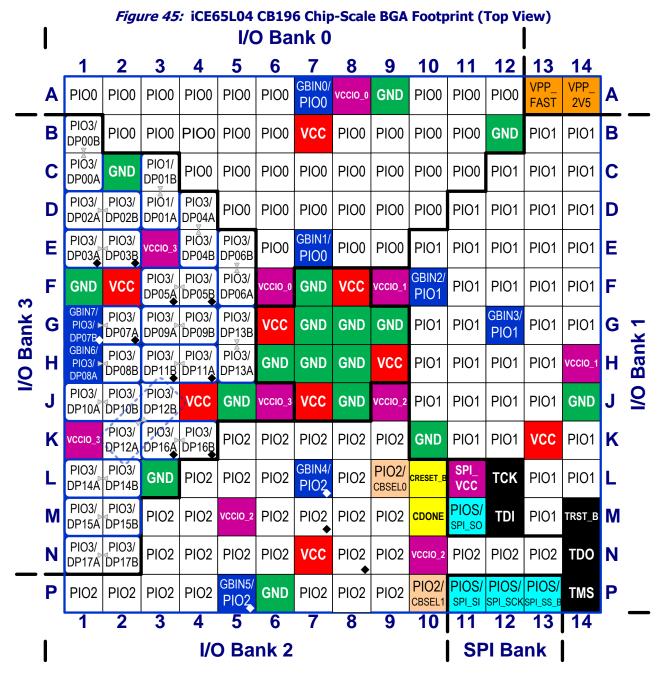

## **CB196 Chip-Scale Ball-Grid Array**

The CB196 package is a chip-scale, fully-populated, ball-grid array with 0.5 mm ball pitch.

## Footprint Diagram

Figure 45 shows the iCE65L04 chip-scale BGA footprint for the 8 x 8 mm CB196 package. The footprint for the iCE65L08 is different than the iCE64L04 footprint, as shown in Figure 46. The pinout differences are highlighted by warning diamonds (♠) in the footprint diagrams and summarized in Table 43.

Although both the iCE65L04 and iCE65L08 are both available in the CB196 package and *almost* completely pin compatible, there are differences as shown in Table 43.

Figure 31 shows the conventions used in the diagram. Also see Table 42 for a complete, detailed pinout for the 196-ball chip-scale BGA packages. The signal pins are also grouped into the four I/O Banks and the SPI interface.

| Ball Function | Ball Number | Pin Type | Bank |

|---------------|-------------|----------|------|

| PIO0          | A5          | PIO      | 0    |

| PIO0          | A6          | PIO      | 0    |

| PIO0          | A10         | PIO      | 0    |

| PIOO          | A11         | PIO      | 0    |

| PIOO          | A12         | PIO      | 0    |

|               |             |          |      |

| PIO0          | B2          | PIO      | 0    |

| PIO0          | B3          | PIO      | 0    |

| PIO0          | B4          | PIO      | 0    |

| PIO0          | B5          | PIO      | 0    |

| PIO0          | B6          | PIO      | 0    |

| PIO0          | B8          | PIO      | 0    |

| PIO0          | B9          | PIO      | 0    |

| PIO0          | B10         | PIO      | 0    |

| PIO0          | B11         | PIO      | 0    |

| PIOO          | C4          | PIO      | 0    |

| PIOO          | C5          | PIO      | 0    |

| PIO0          | C6          | PIO      | 0    |

|               |             |          |      |

| PIO0          | C7          | PIO      | 0    |

| PIO0          | C8          | PIO      | 0    |

| PIO0          | C9          | PIO      | 0    |

| PIO0          | C10         | PIO      | 0    |

| PIO0          | C11         | PIO      | 0    |

| PIO0          | D5          | PIO      | 0    |

| PIO0          | D6          | PIO      | 0    |

| PIO0          | D7          | PIO      | 0    |

| PIO0          | D8          | PIO      | 0    |

| PIO0          | D9          | PIO      | 0    |

| PIO0          | D10         | PIO      | 0    |

| PIOO          | E6          | PIO      | 0    |

| PIOO          | E8          | PIO      | 0    |

| PIO0          | E9          |          | 0    |

|               |             | PIO      |      |

| VCCIO_0       | A8          | VCCIO    | 0    |

| VCCIO_0       | F6          | VCCIO    | 0    |

| GBIN2/PIO1    | F10         | GBIN     | 1    |

| GBIN3/PIO1    | G12         | GBIN     | 1    |

| PIO1          | B13         | PIO      | 1    |

| PIO1          | B14         | PIO      | 1    |

| PIO1          | C12         | PIO      | 1    |

| PIO1          | C13         | PIO      | 1    |

| PIO1          | C13         | PIO      | 1    |

| PIO1          | D11         | PIO      | 1    |

|               |             |          |      |

| PIO1          | D12         | PIO      | 1    |

| PIO1          | D13         | PIO      | 1    |

| PIO1          | D14         | PIO      | 1    |

| PIO1          | E10         | PIO      | 1    |

| PIO1          | E11         | PIO      | 1    |

| PIO1          | E12         | PIO      | 1    |

| PIO1          | E13         | PIO      | 1    |

| PIO1          | E14         | PIO      | 1    |

| PIO1          | F11         | PIO      | 1    |

| PIO1          | F12         | PIO      | 1    |

| PIO1          | F13         | PIO      | 1    |

| LIOI          | LTO         | LIO      | 1    |

|               | Ball Number | Pin Type by Device |                                         |      |            |

|---------------|-------------|--------------------|-----------------------------------------|------|------------|

|               | iCE65L04    | , ,                | , , , , , , , , , , , , , , , , , , , , |      | CB132 Ball |

| Ball Function | iCE65L08    | iCE65L04           | iCE65L08                                | Bank | Equivalent |

| VCCIO_3       | J7          | VCCIO              | VCCIO                                   | 3    | E3         |

| VCCIO_3       | K3          | VCCIO              | VCCIO                                   | 3    | _          |

| VCCIO_3       | N10         | VCCIO              | VCCIO                                   | 3    | Ј6         |

| VCCIO_3       | P5          | VCCIO              | VCCIO                                   | 3    | K1         |

| VCCIO_3       | R3          | VCCIO              | VCCIO                                   | 3    | _          |

| VREF          | M1          | VREF               | VREF                                    | 3    | _          |

| PIOS/SPI_SO   | T15         | SPI                | SPI                                     | SPI  | M11        |

| PIOS/SPI_SI   | V15         | SPI                | SPI                                     | SPI  | P11        |

| PIOS/SPI_SCK  | V16         | SPI                | SPI                                     | SPI  | P12        |

| PIOS/SPI_SS_B | V17         | SPI                | SPI                                     | SPI  | P13        |

| SPI_VCC       | R15         | SPI                | SPI                                     | SPI  | L11        |

| GND           | C12         | GND                | GND                                     | GND  |            |

| GND           | E13         | GND                | GND                                     | GND  | A9         |

| GND           | J3          | GND                | GND                                     | GND  | _          |

| GND           | K5          | GND                | GND                                     | GND  | F1         |

| GND           | K11         | GND                | GND                                     | GND  | F7         |

| GND           | L11         | GND                | GND                                     | GND  | G7         |

| GND           | L12         | GND                | GND                                     | GND  | G8         |

| GND           | L13         | GND                | GND                                     | GND  | G9         |

| GND           | M10         | GND                | GND                                     | GND  | H6         |

| GND           | M11         | GND                | GND                                     | GND  | H7         |

| GND           | M12         | GND                | GND                                     | GND  | H8         |

| GND           | N1          | GND                | GND                                     | GND  | _          |

| GND           | N12         | GND                | GND                                     | GND  | Ј8         |

| GND           | N18         | GND                | GND                                     | GND  | J14        |

| GND           | N20         | GND                | GND                                     | GND  | _          |

| GND           | R7          | GND                | GND                                     | GND  | L3         |

| GND           | T3          | GND                | GND                                     | GND  | _          |

| GND           | V1          | GND                | GND                                     | GND  | _          |

| GND           | V10         | GND                | GND                                     | GND  | P6         |

| GND           | Y12         | GND                | GND                                     | GND  | _          |

| GND           | Y16         | GND                | GND                                     | GND  | _          |

| GND           | AB5         | GND                | GND                                     | GND  | _          |

| GND           | G1          | GND                | GND                                     | GND  | _          |

| GND           | R1          | GND                | GND                                     | GND  | _          |

| VCC           | C8          | VCC                | VCC                                     | VCC  |            |

| VCC           | D3          | VCC                | VCC                                     | VCC  | _          |

| VCC           | K12         | VCC                | VCC                                     | VCC  | F8         |

| VCC           | L10         | VCC                | VCC                                     | VCC  | G6         |

| VCC           | L20         | VCC                | VCC                                     | VCC  | _          |

| VCC           | M13         | VCC                | VCC                                     | VCC  | H9         |

| VCC           | N8          | VCC                | VCC                                     | VCC  | J4         |

| VCC           | N11         | VCC                | VCC                                     | VCC  | J7         |

| VCC           | Y8          | VCC                | VCC                                     | VCC  |            |

| VPP_2V5       | E18         | VPP                | VPP                                     | VPP  | A14        |

| VPP_FAST      | E17         | VPP                | VPP                                     | VPP  | A13        |

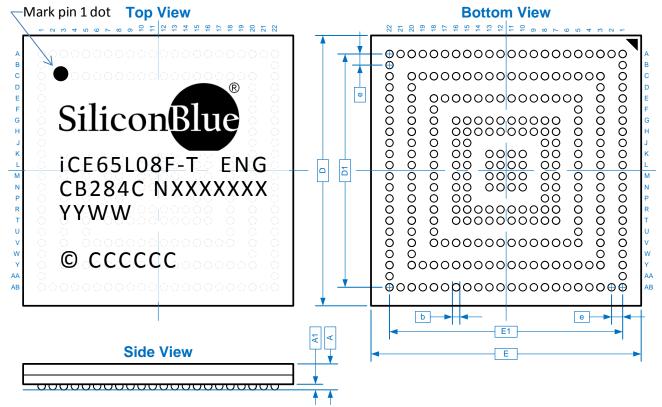

#### Package Mechanical Drawing

# Figure 49: CB284 Package Mechanical Drawing

| Description            |   | Symbol | Min.  | Nominal | Max.  | Units   |

|------------------------|---|--------|-------|---------|-------|---------|

| Number of Ball Columns | Х |        |       | 22      |       | Columns |

| Number of Ball Rows    | Υ |        |       | 22      |       | Rows    |

| Number of Signal Balls |   | n      |       | 284     |       | Balls   |

| Body Size              | Х | Е      | 11.90 | 12.00   | 12.10 |         |

| Body Size              | Υ | D      | 11.90 | 12.00   | 12.10 |         |

| Ball Pitch             |   | е      | _     | 0.50    | _     |         |

| Ball Diameter          |   | b      | 0.27  | _       | 0.37  | mm      |

| Edge Ball Center to    |   | E1     | _     | 10.50   | _     | 111111  |

| Center                 | Υ | D1     | _     | 10.50   | _     |         |

| Package Height         |   | Α      | _     | _       | 1.00  |         |

| Stand Off              |   | A1     | 0.16  | _       | 0.26  |         |

# **Top Marking Format**

| lop Marking Format |           |                  |  |  |  |

|--------------------|-----------|------------------|--|--|--|

| Line               | Content   | Description      |  |  |  |

| 1                  | Logo      | Logo             |  |  |  |

|                    | iCE65L08F | Part number      |  |  |  |

| 2                  | -T        | Power/Speed      |  |  |  |

|                    | ENG       | Engineering      |  |  |  |

| 3                  | CB284C    | Package type and |  |  |  |

|                    | NXXXXXX   | Lot number       |  |  |  |

| 4                  | YYWW      | Date Code        |  |  |  |

| 5                  | N/A       | Blank            |  |  |  |

| 6                  | © CCCCCC  | Country          |  |  |  |

### Thermal Resistance

| THE THAT            | (CSIStario |  |  |  |  |  |

|---------------------|------------|--|--|--|--|--|

| Junction-to-Ambient |            |  |  |  |  |  |

| θја (°              | OJA (°C/W) |  |  |  |  |  |

| 0 LFM               | 200 LFM    |  |  |  |  |  |

| 35                  | 28         |  |  |  |  |  |

| iCE65L08           | Available | Packages   |            | DiePlus            |                        |

|--------------------|-----------|------------|------------|--------------------|------------------------|

| Pad Name           | CB196     | CB284      | Pad        | Χ (μm)             | Υ (μm)                 |

| TDI                | M12       | T16        | 177        | 4,470.5            | 634.615                |

| TMS                | P14       | V18        | 178        | 4,572.5            | 684.615                |

| TCK                | L12       | R16        | 179        | 4,470.5            | 734.615                |

| TDO                | N14       | U18        | 180        | 4,572.5            | 784.615                |

| TRST_B             | M14       | T18        | 181        | 4,470.5            | 834.615                |

| PIO1_00            | M13       | R18        | 182        | 4,572.5            | 884.615                |

| PIO1_01            | K11       | P16        | 183        | 4,470.5            | 934.615                |

| PIO1_02            | L13       | P15        | 184        | 4,572.5            | 984.615                |

| PIO1_03            | L14       | P18        | 185        | 4,470.5            | 1,034.615              |

| GND                | G9        | N18        | 186        | 4,572.5            | 1,084.615              |

| GND                | _         | -          | 187        | 4,470.5            | 1,134.615              |

| PIO1_04            | J11       | N16        | 188        | 4,572.5            | 1,184.615              |

| PIO1_05            | K12       | N15        | 189        | 4,470.5            | 1,234.62               |

| VCCIO_1            | F9        | M18        | 190        | 4,572.5            | 1,287.115              |

| VCCIO_1            | 1 J       | 1.110      | 191        | 4,470.5            | 1,322.115              |

| PIO1_06            | J12       | M15        | 192        | 4,572.5            | 1,357.115              |

| PIO1_06<br>PIO1_07 | K14       | M16        | 192        | 4,470.5            | 1,392.115              |

|                    | KIT       | T20        |            |                    |                        |

| PIO1_08<br>PIO1_09 | _         | W20        | 194<br>195 | 4,572.5<br>4,470.5 | 1,427.115<br>1,462.115 |

|                    | _         |            |            |                    |                        |

| PIO1_10<br>VCC     |           | V20        | 196        | 4,572.5            | 1,497.115              |

| VCC                | H9        | M13        | 197        | 4,470.5<br>4,572.5 | 1,532.115<br>1,567.115 |

| PIO1_11            | _         | R20        | 198<br>199 | 4,470.5            | 1,602.115              |

| PIO1_11<br>PIO1_12 | _         | Y22        | 200        | 4,572.5            | 1,637.115              |

| PIO1_12<br>PIO1_13 | _         | AA22       | 200        | 4,470.5            | 1,672.115              |

|                    | _         |            |            |                    |                        |

| PIO1_14<br>PIO1_15 | <br>J13   | U20<br>W22 | 202<br>203 | 4,572.5            | 1,707.115              |

| _                  |           |            |            | 4,470.5            | 1,742.115              |

| PIO1_16            | H11       | P20        | 204        | 4,572.5            | 1,777.115              |

| PIO1_17            | J10       | V22        | 205        | 4,470.5            | 1,812.115              |

| PIO1_18            | H12       | U22        | 206        | 4,572.5            | 1,847.115              |

| GND<br>GND         | K10       | N20        | 207        | 4,470.5            | 1,882.115              |

| PIO1_19            | —<br>Н13  | —<br>T22   | 208<br>209 | 4,572.5<br>4,470.5 | 1,917.110<br>1,952.115 |

|                    |           |            |            |                    |                        |

| PIO1_20            | —<br>Н10  | M20<br>R22 | 210<br>211 | 4,572.5            | 1,987.115              |

| PIO1_21            | ПТП       |            |            | 4,470.5            | 2,022.115              |

| PIO1_22            |           | P22        | 212        | 4,572.5            | 2,057.115              |

| VCCIO_1<br>VCCIO_1 | F9        | J20<br>    | 213<br>214 | 4,470.5<br>4,572.5 | 2,092.115<br>2,127.115 |

| PIO1_23            | —<br>G10  | —<br>M22   | 214        | 4,372.5            | 2,127.115              |

|                    | G11       | N22        | 215        |                    |                        |

| PIO1_24<br>PIO1_25 | G11       | K22        | 216        | 4,572.5<br>4,470.5 | 2,197.115<br>2,232.115 |

|                    | _         |            |            |                    |                        |

| PIO1_26            | C12       | L22        | 218        | 4,572.5            | 2,267.115              |

| GBIN3/PIO1_27      | G12       | K18        | 219        | 4,470.5            | 2,302.11               |

| GBIN2/PIO1_28      | F10       | L18        | 220        | 4,572.5            | 2,337.115              |

| PIO1_29            | _         | J22        | 221        | 4,470.5            | 2,372.115              |

| iCE65L08           | Available  | Packages |            | DiePlus  | S       |

|--------------------|------------|----------|------------|----------|---------|

| Pad Name           | CB196      | CB284    | Pad        | X (µm)   | Υ (μm)  |

| GND                | F7         | E13      | 270        | 3,216.98 | 4,054.5 |

| GND                | _          | _        | 271        | 3,166.98 | 4,156.5 |

| PIO0_08            | D9         | E15      | 272        | 3,116.98 | 4,054.5 |

| PIO0_09            | C10        | G14      | 273        | 3,064.48 | 4,156.5 |

| PIO0 10            | A10        | A20      | 274        | 3,029.48 | 4,054.5 |

| PIO0_11            | B10        | H13      | 275        | 2,994.48 | 4,156.5 |

| PIO0 12            | _          | A19      | 276        | 2,959.48 | 4,054.5 |

| PIO0_13            | E9         | G13      | 277        | 2,924.48 | 4,156.5 |

| PIO0_14            | _          | C16      | 278        | 2,889.48 | 4,054.5 |

| PIO0_15            | _          | E14      | 279        | 2,854.48 | 4,156.5 |

| VCCIO_0            | F6         | E12      | 280        | 2,819.48 | 4,054.5 |

| VCCIO_0            | _          | _        | 281        | 2,784.48 | 4,156.5 |

| PIO0_16            | _          | A18      | 282        | 2,749.48 | 4,054.5 |

| PIO0_10            | _          | A17      | 283        | 2,714.48 | 4,156.5 |

| PIO0 18            | C9         | C15      | 284        | 2,679.48 | 4,054.5 |

| PIO0_19            | —          | A16      | 285        | 2,644.48 | 4,156.5 |

| PIO0_19            | B9         | C14      | 286        | 2,609.48 | 4,054.5 |

| PIO0_20<br>PIO0_21 | — D3       | H12      | 287        | 2,574.48 | 4,156.5 |

| PIO0_22            | D8         | A15      | 288        | 2,539.48 | 4,054.5 |

| PIO0_22            | C8         | H11      | 289        | 2,504.48 | 4,156.5 |

| PIO0_23            | E8         | C13      | 290        | 2,469.48 | 4,054.5 |

| PIO0_24<br>PIO0_25 | E8         | A14      | 290        | 2,434.48 | 4,156.5 |

|                    |            |          |            |          |         |

| GND<br>GND         | B12        | C12      | 292<br>293 | 2,399.48 | 4,054.5 |

|                    |            |          |            | 2,364.48 | 4,156.5 |

| PIO0_26            | B8         | A13      | 294        | 2,329.48 | 4,054.5 |

| PIO0_27            | D7         | A12      | 295        | 2,294.48 | 4,156.5 |

| PIO0_28            | <b>—</b>   | C11      | 296        | 2,259.48 | 4,054.5 |

| GBIN1/PIO0_29      | E7         | E11      | 297        | 2,224.48 | 4,156.5 |

| GBINO/PIOO_30      | A7         | E10      | 298        | 2,189.48 | 4,054.5 |

| PIO0_31            | _          | G12      | 299        | 2,154.48 | 4,156.5 |

| VCCIO_0            | A8         | A8       | 300        | 2,119.48 | 4,054.5 |

| VCCIO_0            | -          | _        | 301        | 2,084.48 | 4,156.5 |

| PIO0_32            | C7         | A11      | 302        | 2,049.48 | 4,054.5 |

| PIO0_33            |            | G11      | 303        | 2,014.48 | 4,156.5 |

| PIO0_34            | E6         | A10      | 304        | 1,979.48 | 4,054.5 |

| PIO0_35            | _          | C10      | 305        | 1,944.48 | 4,156.5 |

| VCC                | B7         | C8       | 306        | 1,909.48 | 4,054.5 |

| VCC                | <u> </u>   | _        | 307        | 1,874.48 | 4,156.5 |

| PIO0_36            | _          | A9       | 308        | 1,839.48 | 4,054.5 |

| PIO0_37            | A6         | A7       | 309        | 1,804.48 | 4,156.5 |

| PIO0_38            | B6         | C9       | 310        | 1,769.48 | 4,054.5 |

| PIO0_39            | <b>A</b> 5 | A6       | 311        | 1,734.48 | 4,156.5 |

| GND                | G7         | K11      | 312        | 1,699.48 | 4,054.5 |

| GND                | _          | _        | 313        | 1,664.48 | 4,156.5 |

| PIO0 40            | D6         | E9       | 314        | 1,629.48 | 4,054.5 |

| PIO0_41            | C6         | G10      | 315        | 1,594.48 | 4,156.5 |

|                    |            |          |            |          |         |

# **I/O Characteristics**

**Table 49: PIO Pin Electrical Characteristics**

| Symbol             | Description                                |                  | Conditions                    | Minimum | Nominal | Maximum | Units |

|--------------------|--------------------------------------------|------------------|-------------------------------|---------|---------|---------|-------|

| $\mathbf{I}_{l}$   | Input pin                                  | I/O Bank 0, 1, 2 | $V_{IN} = VCCIO_{max}$ to 0 V |         |         | ±10     | μΑ    |

|                    | leakage current                            | I/O Bank 3       | $V_{IN} = VCCIO_{max}$        |         |         |         |       |

| I <sub>oz</sub>    | Three-state I/O pin (Hi-Z) leakage current |                  | $V_{O} = VCCIO_{max}$ to 0 V  |         |         | ±10     | μΑ    |

| C <sub>PIO</sub>   | PIO pin input capacitance                  |                  |                               |         | 6       |         | pF    |

| C <sub>GBIN</sub>  | GBIN global buffer                         | pin input        |                               |         | 6       |         | pF    |

|                    | capacitance                                |                  |                               |         |         |         |       |

| R <sub>PULLU</sub> | Internal PIO pull-เ                        | ıp resistance    | VCCIO = 3.3V                  |         | 40      |         | kΩ    |

| P                  | during configuration                       | on               | VCCIO = 2.5V                  |         | 50      |         | kΩ    |

|                    |                                            |                  | VCCIO = 1.8V                  |         | 90      |         | kΩ    |

|                    |                                            |                  | VCCIO = 1.5V                  |         |         |         | kΩ    |

|                    |                                            |                  | VCCIO = 1.2V                  |         |         |         | kΩ    |

| V <sub>HYST</sub>  | Input hysteresis                           |                  | VCCIO = 1.5V  to  3.3V        |         | 50      |         | mV    |

**NOTE:** All characteristics are characterized and may or may not be tested on each pin on each device.

# Single-ended I/O Characteristics

Table 50: I/O Characteristics (I/O Banks 0, 1, 2 and SPI only) (I/O Bank 3 iCE65L01 only)

|              | Nominal I/O<br>Bank Supply | Input Voltage (V)               |                 | Output Vo       | oltage (V)      | Output Current at<br>Voltage (mA) |                 |

|--------------|----------------------------|---------------------------------|-----------------|-----------------|-----------------|-----------------------------------|-----------------|

| I/O Standard | Voltage                    | V <sub>IL</sub>                 | V <sub>IH</sub> | V <sub>oL</sub> | V <sub>OH</sub> | I <sub>OL</sub>                   | I <sub>OH</sub> |

| LVCMOS33     | 3.3V                       | 0.80                            | 2.00            | 0.4             | 2.40            | 8                                 | 8               |

| LVCMOS25     | 2.5V                       | 0.70                            | 1.70            | 0.4             | 2.00            | 6                                 | 6               |

| LVCMOS18     | 1.8V                       | 35% VCCIO                       | 65% VCCIO       | 0.4             | 1.40            | 4                                 | 4               |

| LVCMOS15     | 1.5V                       | Not supported<br>Use I/O Bank 3 |                 | 0.4             | 1.20            | 2                                 | 2               |

Table 51: I/O Characteristics (I/O Bank 3 and iCE65L04/08 only)

|                 | Supply  | Input Voltage (V)    |                      | Output Voltage (V)   |                      | I/O Attribute    | mA at<br>Voltage                 |

|-----------------|---------|----------------------|----------------------|----------------------|----------------------|------------------|----------------------------------|

| I/O Standard    | Voltage | Max. V <sub>IL</sub> | Min. V <sub>IH</sub> | Max. V <sub>oL</sub> | Min. V <sub>OH</sub> | Name             | I <sub>OL.</sub> I <sub>OH</sub> |

| LVCMOS33        | 3.3V    | 0.80                 | 2.20                 | 0.4                  | 2.40                 | SL_LVCMOS33_8    | ±8                               |

|                 |         |                      |                      |                      |                      | SB_LVCMOS25_16   | ±16                              |

| LVCMOC2E        | 2 51/   | 0.70                 | 1 70                 | 0.4                  | 2.00                 | SB_LVCMOS25_12   | ±12                              |

| LVCMOS25        | 2.5V    | 0.70                 | 1.70                 | 0.4                  |                      | SB_LVCMOS25_8 *  | ±8                               |

|                 |         |                      |                      |                      |                      | SB_LVCMOS25_4    | ±4                               |

|                 |         |                      |                      |                      |                      | SB_LVCMOS18_10   | ±10                              |

| LVCMOC10        | 1.8V    | 35% VCCIO            | 65% VCCIO            | 0.4                  | VCCIO-0.45           | SB_LVCMOS18_8    | ±8                               |

| LVCMOS18        |         |                      |                      |                      |                      | SB_LVCMOS18_4 *  | ±4                               |

|                 |         |                      |                      |                      |                      | SB_LVCMOS18_2    | ±2                               |

| LVCMOC1E        | 1 5\/   | 250/ 1/0010          | CENT VICCIO          | 250/ VCCIO           | 7E0/ VCCTO           | SB_LVCMOS15_4    | ±4                               |

| LVCMOS15        | 1.5V    | 35% VCCIO            | 65% VCCIO            | 25% VCCIO            | 75% VCCIO            | SB_LVCMOS15_2 *  | ±2                               |

|                 |         |                      |                      |                      |                      | SB_MDDR10        | ±10                              |

| MDDD            | 1.8V    | 35% VCCIO            | 65% VCCIO            | 0.4                  | VCCIO-0.45           | SB_MDDR8         | ±8                               |

| MDDR            |         |                      |                      |                      |                      | SB_MDDR4 *       | ±4                               |

|                 |         |                      |                      |                      |                      | SB_MDDR2         | ±2                               |

| SSTL2 (Class 2) | 2 51/   | VREF-0.180           | VREF+0.180           | 0.35                 | VTT - 0.420          | SB_SSTL2_CLASS_2 | ±16.2                            |

| SSTL2 (Class 1) | 2.5V    |                      |                      | 0.54                 | VTT+0.430            | SB_SSTL2_CLASS_1 | ±8.1                             |

| SSTL18 (Full)   | 1.0\/   | VREF-0.125           | VREF+0.125           | 0.28                 | VTT+0.280            | SB_SSTL18_FULL   | ±13.4                            |

| SSTL18 (Half)   | 1.8V    |                      |                      | VTT-0.475            | VTT+0.475            | SB_SSTL18_HALF   | ±6.7                             |

| NOTEC:          |         |                      |                      |                      |                      |                  |                                  |

#### NOTES

SSTL2 and SSTL18 I/O standards require the VREF input pin, which is only available on the CB284 package and die-based products.

|     |             | minimum temperature to -40°C in Figure 2 and Table 48. Added NVCM programming temperature to Table 48.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.3 | 17-DEC-2008 | Added footprint and pinout information for the CS110 Wafer-Level Chip-Scale Ball Grid Array. Clarified that the CB196 footprint shown is for the iCE65L04; the iCE65L08 footprint for the CB196 package is similar but different. Added updated information on Differential Inputs and Outputs, including support for SubLVDS. Updated Electrical Characteristics and AC Timing Guidelines sections. Added support for the LVCMOS15 I/O standard. Corrected the diagram showing the direct differential clock input, Figure 16. Updated the number of I/Os by package in Table 34. Updated company address. Other minor updates throughout.                                  |

| 1.2 | 11-OCT-2008 | Updated I/O Bank 3 characteristics in Table 7 and Table 51. Corrected label in Figure 14. Added JTAG configuration to Table 20. Added pull-up resistor information in Table 22 and Figure 21. Added "Internal Device Reset" section. Updated internal oscillator performance in and Table 57. Updated configuration timing in Table 58 based on new oscillator timing. Completely reorganized the "Package and Pinout Information" section. Added information on CS63 and CB196 packages. Updated information on VPP_2V5 signal in Table 36. Reduced package height for CB132 and CB284 packages to 1.0 mm. Added "Differential Inputs" and "Differential Outputs" sections. |