Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                                              |

|--------------------------------|------------------------------------------------------------------------------|

| Product Status                 | Obsolete                                                                     |

| Number of LABs/CLBs            | 960                                                                          |

| Number of Logic Elements/Cells | 7680                                                                         |

| Total RAM Bits                 | 131072                                                                       |

| Number of I/O                  | 222                                                                          |

| Number of Gates                | -                                                                            |

| Voltage - Supply               | 1.14V ~ 1.26V                                                                |

| Mounting Type                  | Surface Mount                                                                |

| Operating Temperature          | -40°C ~ 85°C (TA)                                                            |

| Package / Case                 | 284-VFBGA, CSPBGA                                                            |

| Supplier Device Package        | 284-CSPBGA (12x12)                                                           |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/ice65l08f-lcb284i |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Programmable Logic Block (PLB)**

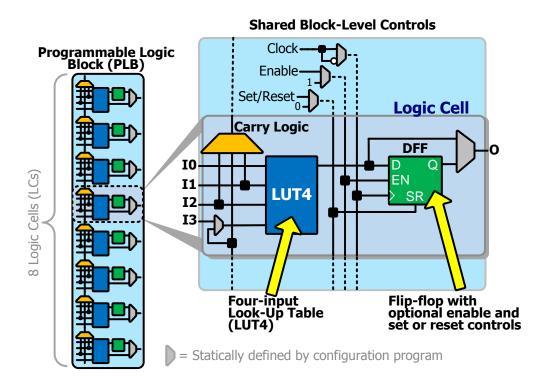

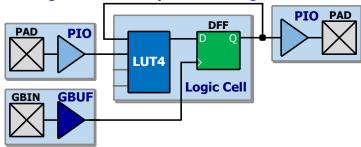

Generally, a logic design for an iCE65 component is created using a high-level hardware description language such as Verilog or VHDL. The Lattice Semiconductor development software then synthesizes the high-level description into equivalent functions built using the programmable logic resources within each iCE65 device. Both sequential and combinational functions are constructed from an array of Programmable Logic Blocks (PLBs). Each PLB contains eight Logic Cells (LCs), as pictured in Figure 4, and share common control inputs, such as clocks, reset, and enable controls.

PLBs are connected to one another and other logic functions using the rich Programmable Interconnect resources.

## Logic Cell (LC)

Each iCE65 device contains thousands of Logic Cells (LCs), as listed in Table 1. Each Logic Cell includes three primary logic elements, shown in Figure 4.

■ A four-input Look-Up Table (LUT4) builds any combinational logic function, of any complexity, of up to four inputs. Similarly, the LUT4 element behaves as a 16xl Read-Only Memory (ROM). Combine and cascade multiple LUT4s to create wider logic functions.

## Figure 4: Programmable Logic Block and Logic Cell

- A 'D'-style Flip-Flop (DFF), with an optional clock-enable and reset control input, builds sequential logic functions. Each DFF also connects to a global reset signal that is automatically asserted immediately following device configuration.

- Carry Logic boosts the logic efficiency and performance of arithmetic functions, including adders, subtracters, comparators, binary counters and some wide, cascaded logic functions.

The output from a Logic Cell is available to all inputs to all eight Logic Cells within the Programmable Logic Block. Similarly, the Logic Cell output feeds into fabric to connect to other features on the iCE65 device.

## iCE65 Ultra Low-Power mobileFPGA<sup>™</sup> Family

## **Look-Up Table (LUT4)**

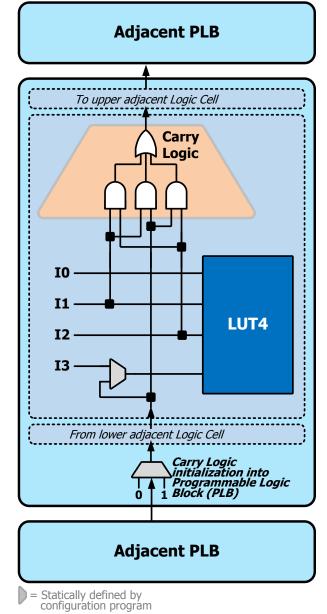

The four-input Look-Up Table (LUT4) function implements any and all combinational logic functions, regardless of complexity, of between zero and four inputs. Zero-input functions include "High" (1) and "Low" (0). The LUT4 function has four inputs, labeled IO, II, I2, and I3. Three of the four inputs are shared with the Carry Logic function, as shown in Figure 4. The bottom-most LUT4 input connects either to the I3 input or to the Carry Logic output from the previous Logic Cell.

The output from the LUT4 function connects to the flip-flop within the same Logic Cell. The LUT4 output or the flip-flop output then connects to the programmable interconnect.

For detailed LUT4 internal timing, see Table 54.

## **'D'-style Flip-Flop (DFF)**

The 'D'-style flip-flop (DFF) optionally stores state information for the application.

The flip-flop has a data input, 'D', and a data output, 'Q'. Additionally, each flip-flop has up to three control signals that are shared among all flip-flops in all Logic Cells within the PLB, as shown in Figure 4. Table 3 describes the behavior of the flip-flop based on inputs and upon the specific DFF design primitive used or synthesized.

Table 3: 'D'-Style Flip-Flop Behavior

| DFF       |                                         | Flip-Flop             |   | Inp | uts |          | Output |

|-----------|-----------------------------------------|-----------------------|---|-----|-----|----------|--------|

| Primitive | Operation                               | Mode                  | D | EN  | SR  | CLK      | Q      |

| All       | Cleared Immediately after Configuration | X                     | Χ | Χ   | Χ   | X        | 0      |

|           | Hold Present Value<br>(Disabled)        |                       | Χ | 0   | Χ   | Χ        | Q      |

|           | Hold Present Value (Static Clock)       |                       | Χ | Χ   | Χ   | 1 or 0   | Q      |

|           | Load with Input Data                    |                       | D | 1*  | 0*  | <b>↑</b> | D      |

| SB_DFFR   | Asynchronous Reset                      | Asynchronous<br>Reset | Χ | Χ   | 1   | Χ        | 0      |

| SB_DFFS   | Asynchronous Set                        | Asynchronous<br>Set   | Χ | Χ   | 1   | X        | 1      |

| SB_DFFSR  | Synchronous Reset                       | Synchronous<br>Reset  | Χ | 1*  | 1   | 1        | 0      |

| SB_DFFSS  | Synchronous Set                         | Synchronous<br>Set    | Χ | 1*  | 1   | <b>†</b> | 1      |

X = don't care,  $\uparrow = rising$  clock edge (default polarity),  $1^* = High$  or unused,  $0^* = Low$  or unused

The CLK clock signal is not optional and is shared among all flip-flops in a Programmable Logic Block. By default, flip-flops are clocked by the rising edge of the PLB clock input, although the clock polarity can be inverted for all the flip-flops in the PLB.

The CLK input optionally connects to one of the following clock sources.

- The output from any one of the eight Global Buffers, or

- A connection from the general-purpose interconnect fabric

The EN clock-enable signal is common to all Logic Cells in a Programmable Logic Block. If the enable signal is not used, then the flip-flop is always enabled. This condition is indicated as "1\*" in Table 3. The asterisk indicates that this is the default state if the control signal is not connected in the application.

Similarly, the SR set/reset signal is common to all Logic Cells in a Programmable Logic Block. If not used, then the flip-flop is never set/reset, except when cleared immediately after configuration or by the Global Reset signal. This condition is indicated as "0\*" in Table 3. The asterisk indicates that this is the default state if the control signal is not connected in the application.

The Carry Logic generates the carry value to feed the next bit in the adder. The calculated carry value replaces the I3 input to the next LUT4 in the upper Logic Cell.

If required by the application, the carry output from the final stage of the adder is available by passing it through the final LUT4.

Figure 5: Carry Logic Structure within a Logic Cell and between PLBs

Table 8 lists the I/O standards that can co-exist in I/O Bank 3, depending on the VCCIO 3 voltage.

Table 8: Compatible I/O Standards in I/O Bank 3 of iCE65L04 and iCE65L08

| VCCIO_3 Voltage             | 3.3V          | 2.5V                                                                     | 1.8V                                                                               | 1.5V            |

|-----------------------------|---------------|--------------------------------------------------------------------------|------------------------------------------------------------------------------------|-----------------|

| Compatible I/O<br>Standards | SB_LVCMOS33_8 | Any SB_LVCMOS25<br>SB_SSTL2_Class_2<br>SB_SSTL2_Class_1<br>SB_LVDS_INPUT | Any SB_LVCMOS18 SB_SSTL18_FULL SB_SSTL18_HALF SB_MDDR10 SB_MDDR8 SB_MDDR4 SB_MDDR2 | Any SB_LVCMOS15 |

|                             |               |                                                                          | SB LVDS INPUT                                                                      |                 |

#### **Programmable Output Drive Strength**

Each PIO in I/O Bank 3 offers programmable output drive strength, as listed in Table 8. For the LVCMOS and MDDR I/O standards, the output driver has settings for static drive currents ranging from 2 mA to 16 mA output drive current, depending on the I/O standard and supply voltage.

The SSTL18 and SSTL2 I/O standards offer full- and half-strength drive current options

## **Differential Inputs and Outputs**

All PIO pins support "single-ended" I/O standards, such as LVCMOS. However, iCE65 FPGAs also support differential I/O standards where a single data value is represented by two complementary signals transmitted or received using a pair of PIO pins. The PIO pins in I/O Bank 3 of iCE65L04 and iCE65L08L08 support Low-Voltage Differential Swing (LVDS) and SubLVDS inputs as shown in Figure 8. Differential outputs are available in all four I/O banks.

#### Differential Inputs Only on I/O Bank 3 of iCE65L04 and iCE65L08

Differential receivers are required for popular applications such as LVDS and LVPECL clock inputs, camera interfaces, and for various telecommunications standards.

Specific pairs of PIO pins in I/O Bank 3 form a differential input. Each pair consists of a DPxxA and DPxxB pin, where "xx" represents the pair number. The DPxxB receives the true version of the signal while the DPxxA receives the complement of the signal. Typically, the resulting signal pair is routed on the printed circuit board (PCB) with matched  $50\Omega$  signal impedance. The differential signaling, the low voltage swing, and the matched signal routing are ideal for communicating very-high frequency signals. Differential signals are generally also more tolerant of system noise and generate little EMI themselves.

The LVDS input circuitry requires 2.5V on the VCCIO\_3 voltage supply. Similarly, the SubLVDS input circuitry requires 1.8V on the VCCIO\_3 voltage supply. For electrical specifications, see "Differential Inputs" on page 100.

Each differential input pair requires an external 100  $\Omega$  termination resistor, as shown in Figure 8.

The PIO pins that make up a differential input pair are indicated with a blue bounding box in the footprint diagrams and in the pinout tables.

For best possible performance, the global buffer inputs (GBIN[7:-0]) connect directly to the their associated global buffers (GBUF[7:0]), bypassing the PIO logic and iCEgate circuitry as shown in Figure 7. Consequently, the direct GBIN-to-GBUF connection cannot be blocked by the iCEgate circuitry. However, it is possible to use iCEgate to block PIO-to-GBUF clock connections.

For additional information on using the iCEgate feature, please refer to the following application note.

AN002: Using iCEgate Blocking for Ultra-Low Power

#### Input Pull-Up Resistors on I/O Banks 0, 1, and 2

The PIO pins in I/O Banks 0, 1, and 2 have an optional input pull-up resistor. Pull-up resistors are not provided in iCE65L04 and iCE65L08 I/O Bank 3. During the iCE65 configuration process, the input pull-up resistor is unconditionally enabled and pulls the input to within a diode drop of the associated I/O bank supply voltage (VCCIO #). This prevents any signals from floating on the circuit board during configuration.

After iCE65 configuration is complete, the input pull-up resistor is optional, defined by a configuration bit. The pull-up resistor is also useful to tie off unused PIO pins. The Lattice iCEcube development software defines all unused PIO pins in I/O Banks 0, 1 and 2 as inputs with the pull-up resistor turned on. The pull-up resistor value depends on the VCCIO voltage applied to the bank, as shown in Table 49.

Note: JTAG inputs TCK, TDI and TMS do not have the input pull-up resistor and must be tied off to GND when unused, else VCCIO\_1 draws current.

#### No Input Pull-up Resistors on I/O Bank 3 of iCE65L04 and iCE65L08

The PIO pins in I/O Bank 3 do not have an internal pull-up resistor. To minimize power consumption, tie unused PIO pins in Bank 3 to a known logic level or drive them as a disabled high-impedance output.

#### **Input Hysteresis**

Inputs typically have about 50 mV of hysteresis, as indicated in Table 49.

#### **Output and Output Enable Signal Path**

As shown in Figure 7, a signal from programmable interconnect feeds the OUT signal on a Programmable I/O pad. This output connects either directly to the associated package pin or is held in an optional output flip-flop. Because all flip-flops are automatically reset after configuration, the output from the output flip-flop can be optionally inverted so that an active-Low output signal is held in the disabled (High) state immediately after configuration.

Similarly, each Programmable I/O pin has an output enable or three-state control called OE. When OE = High, the OUT output signal drives the associated pad, as described in Table 10. When OE = Low, the output driver is in the high-impedance (Hi-Z) state. The OE output enable control signal itself connects either directly to the output buffer or is held in an optional register. The output buffer is optionally permanently enabled or permanently disabled, either to unconditionally drive output signals, or to allow input-only signals.

Table 10: PIO Output Operations (non-registered operation, no inversions)

|                   | OUT         | OE     |      |

|-------------------|-------------|--------|------|

| Operation         | Data Output | Enable | PAD  |

| Three-State       | Χ           | 0      | Hi-Z |

| Drive Output Data | OUT         | 1*     | OUT  |

X = don't care,  $1^* = High or unused$ , Hi-Z = high-impedance, three-stated, floating.

See Input and Output Register Control per PIO Pair for information about the registered input path.

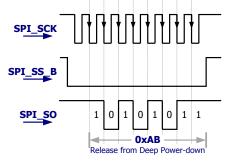

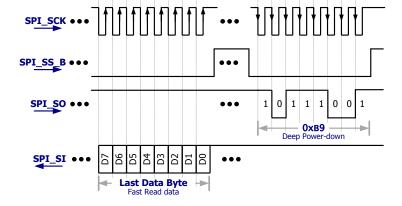

- For lowest possible power consumption after configuration, the PROM should also support the **0xB9** Deep Power Down command and the **0xAB** Release from Deep Power-down Command (see Figure 24 and Figure 26). The low-power mode is optional.

- The PROM must be ready to accept commands 10  $\mu$ s after meeting its power-on conditions. In the PROM data sheet, this may be specified as  $t_{VSL}$  or  $t_{VCSL}$ . It is possible to use slower PROMs by holding the CRESET\_B input Low until the PROM is ready, then releasing CRESET\_B, either under program control or using an external power-on reset circuit.

The Lattice iCEman65 development board and associated programming software uses an ST Micro/Numonyx M25Pxx SPI serial Flash PROM.

#### SPI PROM Size Requirements

Table 27 lists the minimum SPI PROM size required to configure an iCE65 device. Larger PROM sizes are allowed, but not required unless the end application uses the additional space. SPI serial PROM sizes are specified in bits. For each device size, the table shows the required minimum PROM size for "Logic Only" (no BRAM initialization) and "Logic + RAM4K" (RAM4K blocks pre-initialized). Furthermore, the table shows the PROM size for varying numbers of configuration images. Most applications will use a single image. Applications that use the Cold Boot or Warm Boot features may use more than one image.

Table 27: Smallest SPI PROM Size (bits), by Device, by Number of Images

|          | 1 In          | nage             | 2 Im          | ages             | 3 Im          | ages             | 4 Im          | ages             |

|----------|---------------|------------------|---------------|------------------|---------------|------------------|---------------|------------------|

| Device   | Logic<br>Only | Logic +<br>RAM4K |

| iCE65L01 | 256K          | 256K             | 512K          | 512K             | 1M            | 1M               | 1M            | 1M               |

| iCE65L04 | 512K          | 1M               | 1M            | 2M               | 2M            | 2M               | 2M            | 4M               |

| iCE65L08 | 1M            | 2M               | 2M            | 4M               | 4M            | 4M               | 4M            | 8M               |

#### **Enabling SPI Configuration Interface**

To enable the SPI configuration mode, the SPI\_SS\_B pin must be allowed to float High. The SPI\_SS\_B pin has an internal pull-up resistor. If SPI\_SS\_B is Low, then the iCE65 component defaults to the SPI Slave configuration mode.

#### SPI Master Configuration Process

The iCE65 SPI Master Configuration Interface supports a variety of modern, high-density, low-cost SPI serial Flash PROMs. Most modern SPI PROMs include a power-saving Deep Power-down mode. The iCE65 component exploits this mode for additional system power savings.

The iCE65 SPI interface starts by driving SPI\_SS\_B Low, and then sends a Release from Power-down command to the SPI PROM, hexadecimal command code **0xAB**. Figure 24 provides an example waveform. This initial command wakes up the SPI PROM if it is already in Deep Power-down mode. If the PROM is not in Deep Power-down mode, the extra command has no adverse affect other than that it requires a few additional microseconds during the configuration process. The iCE65 device transmits data on the SPI\_SO output, on the falling edge of the SPI\_SCK output. The SPI PROM does not provide any data to the iCE65 device's SPI\_SI input. After sending the last command bit, the iCE65 device de-asserts SPI\_SS\_B High, completing the command. The iCE65 device then waits a minimum of 10 µS before sending the next SPI PROM command.

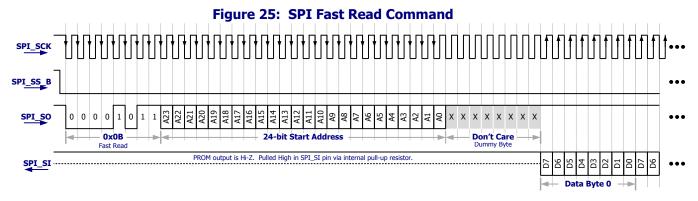

Figure 24: SPI Release from Deep Power-down Command

Figure 25 illustrates the next command issued by the iCE65 device. The iCE65 SPI interface again drives SPI\_SS\_B Low, followed by a Fast Read command, hexadecimal command code 0x0B, followed by a 24-bit start address, transmitted on the SPI\_SO output. The iCE65 device provides data on the falling edge of SPI\_SS\_B. Upon initial power-up, the start address is always 0x00\_0000. After waiting eight additional clock cycles, the iCE65 device begins reading serial data from the SPI PROM. Before presenting data, the SPI PROM's serial data output is high-impedance. The SPI\_SI input pin has an internal pull-up resistor and sees high-impedance as logic '1'.

The external SPI PROM supplies data on the falling edge of the iCE65 device's SPI\_SCK clock output. The iCE65 device captures each PROM data value on the SPI\_SI input, using the rising edge of the SPI\_SCK clock signal. The SPI PROM data starts at the 24-bit address presented by the iCE65 device. PROM data is serially output, byte by byte, with most-significant bit, D7, presented first. The PROM automatically increments an internal byte counter as long as the PROM is selected and clocked.

After transferring the required number configuration data bits, the iCE65 device ends the Fast Read command by de-asserting its SPI\_SS\_B PROM select output, as shown in Figure 26. To conserve power, the iCE65 device then optionally issues a final Deep Power-down command, hexadecimal command code **0xB9**. After de-asserting the SPI\_SS\_B output, the SPI PROM enters its Deep Power-down mode. The final power-down step is optional; the application may use the SPI PROM and can skip this step, controlled by a configuration option.

Figure 26: Final Configuration Data, SPI Deep Power-down Command

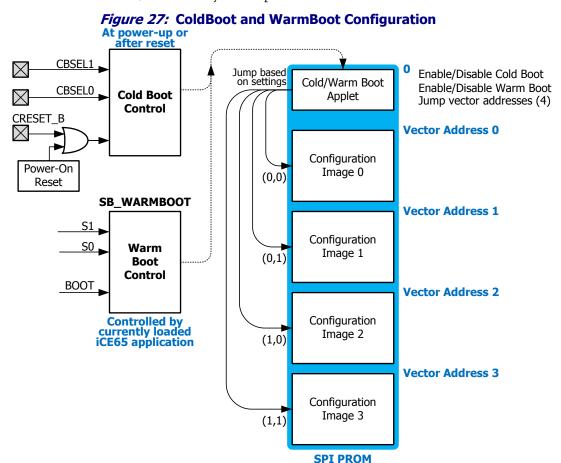

#### **Cold Boot Configuration Option**

By default, the iCE65 FPGA is programmed with a single configuration image, either from internal NVCM memory, from an external SPI Flash PROM, or externally from a processor or microcontroller.

When self loading from NVCM or from an SPI Flash PROM, there is an additional configuration option called Cold Boot mode. When this option is enabled in the configuration bitstream, the iCE65 FPGA boots normally from power-on or a master reset (CRESET\_B = Low pulse), but monitors the value on two PIO pins that are borrowed during configuration, as shown in Figure 27. These pins, labeled PIO2/CBSEL0 and PIO2/CBSEL1, tell the FPGA which of the four possible SPI configurations to load into the device. Table 30 provides the pin or ball locations for these pins.

- Load from initial location, either from NVCM or from address 0 in SPI Flash PROM. For Cold Boot or Warm Boot applications, the initial configuration image contains the cold boot/warm boot applet.

- Check if Cold Boot configuration feature is enabled in the bitstream.

- ◆ If not enabled, FPGA configures normally.

- ◆ If Cold Boot is enabled, then the FPGA reads the logic values on pins CBSEL[1:0]. The FPGA uses the value as a vector and then reads from the indicated vector address.

- ◆ At the selected CBSEL[1:0] vector address, there is a starting address for the selected configuration image.

- For SPI Flash PROMs, the new address is a 24-bit start address in Flash.

- If the selected bitstream is in NVCM, then the address points to the internal NVCM.

- Using the new start address, the FPGA restarts reading configuration memory from the new location.

## iCE65 Ultra Low-Power mobileFPGA<sup>™</sup> Family

After driving CRESET B High or allowing it to float High, the AP must wait a minimum of  $t_{CR}$  SCK  $\mu$ s, (see Table 60) allowing the iCE65 FPGA to clear its internal configuration memory.

After waiting for the configuration memory to clear, the AP sends the configuration image generated by the iCEcube development system. An SPI peripheral mode configuration image must not use the ColdBoot or WarmBoot options. Send the entire configuration image, without interruption, serially to the iCE65's SPI\_SI input on the falling edge of the SPI SCK clock input. Once the AP sends the 0x7EAA997E synchronization pattern, the generated SPI SCK clock frequency must be within the specified 1 MHz to 25 MHz range (40 ns to 1 µs clock period) while sending the configuration image. Send each byte of the configuration image with most-significant bit (msb) first. The AP sends data to the iCE65 FPGA on the falling edge of the SPI\_SCK clock. The iCE65 FPGA internally captures each incoming SPI SI data bit on the rising edge of the SPI SCK clock. The iCE65's SPI SO output pin is not used during SPI peripheral mode but must connect to the AP if the AP also programs the iCE65's Nonvolatile Configuration Memory (NVCM).

Prior to sending the iCE65 configuration image, an SPI NVCM shut-off sequence must be sent. See AN014 for details.

The iCE65 configuration image must be sent as one contiguous stream without interruption. The SPI SCK clock period must be between 40 ns to 1 µs (1 MHz to 25 MHz).

After sending the entire image, the iCE65 FPGA releases the CDONE output allowing it to float High via the  $10 \text{ k}\Omega$ pull-up resistor to AP VCC. If the CDONE pin remains Low, then an error occurred during configuration and the AP should handle the error accordingly for the application.

After the CDONE output pin goes High, send at least 49 additional dummy bits, effectively 49 additional SPI\_SCK clock cycles measured from rising-edge to rising-edge.

After the additional SPI CLK cycles, the SPI interface pins then become available to the user application loaded in FPGA.

To reconfigure the iCE65 FPGA or to load a different configuration image, merely restart the configuration process by pulsing CRESET B Low or power-cycling the FPGA.

**CDONE** 49 SPI\_SCK Cycles Rising edge to rising edge ≥ 200 ns CRESET B iCE65L01: ≥ 800 µs iCE65L04: ≥ 800 µs iCE65L08: ≥ 1200 µs iCE65 clears internal configuration memory iCE65 enters SPI Peripheral mode with SPI SS B = Low on pins available led I/O pins rising edge of CRESET\_B iCE65 captures SPI SI data on SPI SCK rising edge Configuration image always starts with 0x7EAA997E synchronization word Interface as user-defi SPI\_SI 8 Χ X X X**Entire Configuration Images** Don't Care Send most-significant bit of each byte first SP Pulled High in SPI SO pin via internal pull-up resistor. Not used for SPI Peripheral mode configuration. Used when programming NVCM via SPI itnterface. SPI\_SO

Figure 29: Application Processor Waveforms for SPI Peripheral Mode Configuration Process

The iCE65 configuration image must be sent as one contiguous stream without interruption. The SPI\_SCK clock period must be between 40 ns to 1 µs (1 MHz to 25 MHz).

**SPI Peripheral Configuration** Drive  $CRESET_B = 0$ Drive  $SPI_SS_B = 0$ ,  $SPI_SCK = 1$ Wait a minimum of 200 ns Release CRESET\_B or drive  $CRESET_B = 1$ Wait a minimum of iC65L01: 800 µs iC65L04: 800 μs iC65L08: 1200 μs to clear internal config. memory Send NVCM shut-off sequence Send configuration image serially on SPI\_SI to iCE65, mostsignificant bit first, on falling edge of SPI\_SCK. Send the entire image, without interruption. Ensure that SPI\_SCK frequency is between 1 MHz and 25 MHz. CDONE = 1?ERROR! YES Send a minimum of 49 additional dummy bits and 49 additional SPI\_SCK clock cycles (rising-edge to rising-edge) to active the user-I/O pins. SPI interface pins available as userdefined I/O pins in application **Reconfigure?** YES

Figure 30: SPI Peripheral Configuration Process

#### **Voltage Compatibility**

As shown in Figure 23, there are potentially three different supply voltages involved in the SPI Peripheral interface, described in Table 30.

**Table 30: SPI Peripheral Mode Supply Voltages**

|                | rubic bor of the composition of |  |  |  |  |  |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Supply Voltage | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| AP_VCCIO       | I/O supply to the Application Processor (AP)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| VCC_SPI        | Voltage supply for the iCE65 SPI interface.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| VCCIO_2        | Supply voltage for the iCE65 I/O Bank 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

#### **Supported JTAG Commands**

The JTAG interface supports the IEEE 1149.1 mandatory instructions, including EXTEST, SAMPLE/PRELOAD, and BYPASS.

## **Package and Pinout Information**

## Maximum User I/O Pins by Package and by I/O Bank

Table 34 lists the maximum number of user-programmable I/O pins by package, with additional detail showing user I/O pins by I/O bank. In some cases, a smaller iCE65 device is packaged in a larger package with unconnected (N.C.) pins or balls, resulting in fewer overall I/O pins. See Table 35 for device-specific I/O counts by package.

| Table 34: | User I/ | O by | Package, | by I | /C | ) Bank |

|-----------|---------|------|----------|------|----|--------|

|-----------|---------|------|----------|------|----|--------|

|                                 | CB81  | QN84  | VQ100   | CB132   | CB196   | CB284   |

|---------------------------------|-------|-------|---------|---------|---------|---------|

| Package Leads                   | 81    | 84    | 100     | 132     | 196     | 284     |

| Package Body (mm)               | 5 x 5 | 7 x 7 | 14 x 14 | 8 x 8   | 8 x 8   | 12 x 12 |

| Ball Array (balls)              | 9 x 9 | N/A   | N/A     | 14 x 14 | 14 x 14 | 22 x 22 |

| Ball/Lead Pitch (mm)            | 0.5   | 0.5   | 0.5     | 0.5     | 0.5     | 0.5     |

| Maximum user I/O, all I/O banks | 63    | 67    | 72      | 95      | 150     | 222     |

| PIO Pins in Bank 0              | 17    | 17    | 19      | 26      | 37      | 60      |

| PIO Pins in Bank 1              | 16    | 17    | 19      | 21      | 38      | 55      |

| PIO Pins in Bank 2              | 12    | 11    | 12      | 20      | 35      | 53      |

| PIO Pins in Bank 3              | 18    | 18    | 18      | 24      | 36      | 50      |

| PIO Pins in SPI<br>Interface    | 4     | 4     | 4       | 4       | 4       | 4       |

#### **Printed Circuit Board Layout Information**

For information on how to use the iCE65 packages on a printed circuit board (PCB) design, consult the following application note.

■ AN010: iCE65 Printed Circuit Board (PCB Layout) Guidelines

#### Maximum User I/O by Device and Package

Table 35 lists the maximum available user I/O by device and by and package type. Not all devices are available in all packages. Similarly, smaller iCE65 devices may have unconnected balls in some packages. Devices sharing a common package have similar footprints.

Table 35: Maximum User I/O by Device and Package

|         | Device   |          |          |  |  |

|---------|----------|----------|----------|--|--|

| Package | iCE65L01 | iCE65L04 | iCE65L08 |  |  |

| CB81    | 63       | _        | _        |  |  |

| QN84    | 67       | _        | _        |  |  |

| VQ100   | 72       | 72       |          |  |  |

| CB132   | 93       | 95       | _        |  |  |

| CB196   | _        | 150      | 150      |  |  |

| CB284   | _        | 176      | 222      |  |  |

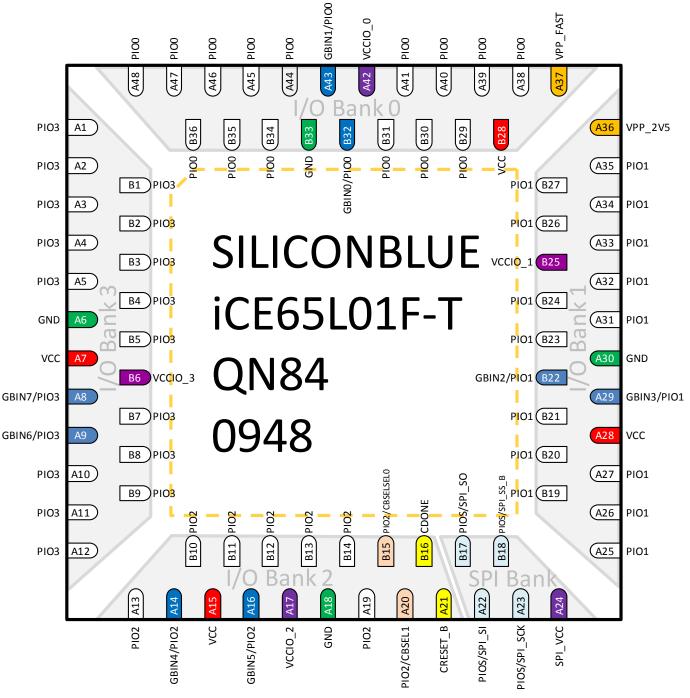

## **QN84 Quad Flat Pack No-Lead**

The QN84 is a Quad Flat Pack No-Lead package with a 0.5 mm pad pitch.

## Footprint Diagram

Figure 34 shows the iCE65 footprint diagram for the QN84 package.

Also see Table 38 for a complete, detailed pinout for the QN84 package.

The signal pins are also grouped into the four I/O Banks and the SPI interface.

Figure 34: iCE65 QN84 Quad Flat Pack No-Lead Footprint (Top View)

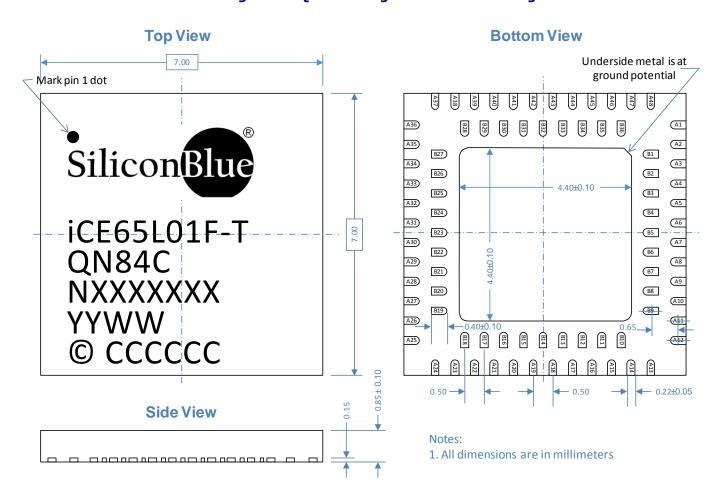

#### Package Mechanical Drawing

Figure 35: QN84 Package Mechanical Drawing

## **Top Marking Format**

| Line | Content   | Description  |

|------|-----------|--------------|

| 1    | Logo      | Logo         |

| 2    | iCE65L01F | Part number  |

|      | -T        | Power/Speed  |

| 3    | QN84C     | Package type |

| 3    | ENG       | Engineering  |

| 4    | NXXXXXX   | Lot Number   |

| 5    | YYWW      | Date Code    |

| 6    | © cccccc  | Country      |

## Thermal Resistance

| Junction-to-Ambient * |      |  |  |  |

|-----------------------|------|--|--|--|

| OJA (°                | C/W) |  |  |  |

| 0 LFM 200 LFM         |      |  |  |  |

| 45 44                 |      |  |  |  |

<sup>\*</sup> With PCB thermal vias

| Ball Function | Ball Number | Pin Type | Bank |

|---------------|-------------|----------|------|

| PIO0          | A5          | PIO      | 0    |

| PIO0          | A6          | PIO      | 0    |

| PIOO          | A8          | PIO      | 0    |

| PIO0          | A10         | PIO      | 0    |

| PIO0          | B3          | PIO      | 0    |

| PIO0          | B4          | PIO      | 0    |

| PIO0          | B5          | PIO      | 0    |

| PIO0          | B8          | PIO      | 0    |

| PIOO          | B9          | PIO      | 0    |

| PIO0          | C5          | PIO      | 0    |

| PIOO          | C7          | PIO      | 0    |

| PIO0          | C8          | PIO      | 0    |

| PIOO          | C9          | PIO      | 0    |

| PIO0          | D5          | PIO      | 0    |

| PIO0          | D7          | PIO      | 0    |

| PIO0          | E5          | PIO      | 0    |

| PIOO          | E6          | PIO      | 0    |

| PIO0          | E7          | PIO      | 0    |

| PIO0          | F7          | PIO      | 0    |

| VCCIO 0       | В7          | VCCIO    | 0    |

|               |             |          |      |

| GBIN2/PIO1    | F9          | GBIN     | 1    |

| GBIN3/PIO1    | F8          | GBIN     | 1    |

| PIO1          | A11         | PIO      | 1    |

| PIO1          | B11         | PIO      | 1    |

| PIO1          | C11         | PIO      | 1    |

| PIO1          | D8          | PIO      | 1    |

| PIO1          | D9          | PIO      | 1    |

| PIO1          | D10         | PIO      | 1    |

| PIO1          | D11         | PIO      | 1    |

| PIO1          | E8          | PIO      | 1    |

| PIO1          | E9          | PIO      | 1    |

| PIO1          | E11         | PIO      | 1    |

| PIO1          | F10         | PIO      | 1    |

| PIO1          | G7          | PIO      | 1    |

| PIO1          | G8          | PIO      | 1    |

| PIO1          | G9          | PIO      | 1    |

| PIO1          | G10         | PIO      | 1    |

| PIO1          | H7          | PIO      | 1    |

| PIO1          | H8          | PIO      | 1    |

| PIO1          | H9          | PIO      | 1    |

| PIO1          | H10         | PIO      | 1    |

| VCCIO_1       | E10         | VCCIO    | 1    |

| CDONE         | J7          | CONFIG   | 2    |

| CRESET_B      | K7          | CONFIG   | 2    |

| GBIN4/PIO2    | L8          | GBIN     | 2    |

| GBIN5/PIO2    | L9          | GBIN     | 2    |

| PIO2          | H4          | PIO      | 2    |

| PIO2          | H5          | PIO      | 2    |

| PIO2          | H11         | PIO      | 2    |

| PIO2          | J4          | PIO      | 2    |

| PIO2          | J5          | PIO      | 2    |

| Ball Function                          | Ball Number     | Pin Type   | Bank       |

|----------------------------------------|-----------------|------------|------------|

| L01/L04: GBIN7/PIO3                    | G1              | GBIN       | 3          |

| L08: GBIN7/DP05B                       |                 |            |            |

| L01/L04: PIO3/DP05A                    | G3              | DPIO       | 3          |

| L08: PIO3/DP05A                        |                 |            |            |

| L01/L04: PIO3/DP05B<br>L08: PIO3/DP11B | G4              | DPIO       | 3          |

| L01/L04: PIO3/DP06A                    | Н3              | DPIO       | 3          |

| L08: PIO3/DP06B<br>L01/L04: PIO3/DP06B | H4              | DPIO       | 3          |

| L08: PIO3/DP11A                        |                 |            |            |

| PIO3/DP07A                             | J3              | DPIO       | 3          |

| PIO3/DP07B                             | J1              | DPIO       | 3          |

| PIO3/DP08A                             | K3              | DPIO       | 3          |

| PIO3/DP08B                             | K4              | DPIO       | 3          |

| PIO3/DP09A                             | L1              | DPIO       | 3          |

| PIO3/DP09B                             | M1              | DPIO       | 3          |

| PIO3/DP10A                             | N1              | DPIO       | 3          |

| PIO3/DP10B                             | P1              | DPIO       | 3          |

| VCCIO_3                                | E3              | VCCIO      | 3          |

| VCCIO_3                                | J6              | VCCIO      | 3          |

| VCCIO_3                                | K1              | VCCIO      | 3          |

|                                        |                 |            |            |

| PIOS/SPI_SO                            | M11             | SPI        | SPI        |

| PIOS/SPI_SI                            | P11             | SPI        | SPI        |

| PIOS/SPI_SCK                           | P12             | SPI        | SPI        |

| PIOS/SPI_SS_B                          | P13             | SPI        | SPI        |

| SPI_VCC                                | L11             | SPI        | SPI        |

| GND                                    | A9              | GND        | GND        |

| GND                                    | F1              | GND        | GND        |

| GND                                    | F7              | GND        | GND        |

| GND                                    | G7              | GND        | GND        |

| GND                                    | G8              | GND        | GND        |

| GND                                    | G9              | GND        | GND        |

| GND                                    | H6              | GND        | GND        |

| GND                                    | H7              | GND        | GND        |

| GND                                    | H8              | GND        | GND        |

| GND                                    | J8              | GND        | GND        |

| GND                                    | J14             | GND        | GND        |

| GND                                    | L3              | GND        | GND        |

| GND                                    | P6              | GND        | GND        |

| VCC                                    | F8              | VCC        | VCC        |

| VCC                                    | G6              | VCC        | VCC        |

| VCC                                    | H9              | VCC<br>VCC | VCC<br>VCC |

| VCC<br>VCC                             | <u>J4</u><br>J7 | VCC        | VCC        |

|                                        |                 |            |            |

| VPP_2V5                                | A14             | VPP        | VPP        |

| VPP_FAST                               | A13             | VPP        | VPP        |

|                                  | Ball Number<br>iCE65L04 | /1 , /         |                |      | CD122 D-II               |

|----------------------------------|-------------------------|----------------|----------------|------|--------------------------|

| Ball Function                    | iCE65L04                | iCE65L04       | iCE65L08       | Bank | CB132 Ball<br>Equivalent |

| PIO3/DP03A                       | H5                      | DPIO           | DPIO           | 3    | D1                       |

| PIO3/DPO3A<br>PIO3/DPO3B         | J5                      | DPIO           | DPIO           | 3    | E1                       |

| PIO3/DPO3B                       | K8                      | DPIO           | DPIO           | 3    | F4                       |

| PIO3/DP04A<br>PIO3/DP04B         | K7                      | DPIO           | DPIO           | 3    | F3                       |

| PIO3/DP05A                       | E3                      | DPIO           | DPIO           |      | 1.3                      |

| PIO3/DP05A<br>PIO3/DP05B         | F3                      | DPIO           | DPIO           | 3    | _                        |

| PIO3/DP06A                       | G3                      | DPIO           | DPIO           |      |                          |

| PIO3/DP06A<br>PIO3/DP06B         | H3                      | DPIO           | DPIO           | 3    |                          |

| PIO3/DP07A (●)                   | B1                      | N.C.           | DPIO           | 3    |                          |

| PIO3/DP07B (●)                   | C1                      | N.C.           | DPIO           | 3    |                          |

|                                  |                         | N.C.           |                | 3    |                          |

| PIO3/DP08A (●)<br>PIO3/DP08B (●) | D1<br>E1                | N.C.<br>N.C.   | DPIO<br>DPIO   | 3    |                          |

|                                  |                         |                |                | •    |                          |

| PIO3/DP09A<br>PIO3/DP09B         | H1<br>J1                | DPIO<br>DPIO   | DPIO<br>DPIO   | 3    |                          |

|                                  |                         |                |                |      | _                        |

| PIO3/DP10A<br>PIO3/DP10B         | K1<br>L1                | DPIO<br>DPIO   | DPIO<br>DPIO   | 3    | _                        |

|                                  |                         |                |                |      | _                        |

| PIO3/DP11A                       | L3                      | DPIO           | DPIO           | 3    |                          |

| GBIN7/PIO3/DP11B                 | L5                      | GBIN           | GBIN           | 3    | G1                       |

| PIO3/DP12A (●)                   | T1                      | N.C.           | DPIO           | 3    | _                        |

| PIO3/DP12B (●)                   | U1                      | N.C.           | DPIO           | 3    | _                        |

| PIO3/DP13A (●)                   | W1                      | N.C.           | DPIO           | 3    | _                        |

| PIO3/DP13B (●)                   | Y1                      | N.C.           | DPIO           | 3    | _                        |

| PIO3/DP14A (●)                   | AA1                     | N.C.           | DPIO           | 3    | _                        |

| PIO3/DP14B (●)                   | AB1                     | N.C.           | DPIO           | 3    | -                        |

| GBIN6/PIO3/DP15A                 | M5                      | GBIN           | GBIN           | 3    | H1                       |

| PIO3/DP15B                       | M3                      | DPIO           | DPIO           |      | _                        |

| PIO3/DP16A                       | N3                      | DPIO           | DPIO           | 3    |                          |

| PIO3/DP16B                       | P3                      | DPIO           | DPIO           | 3    | _                        |

| PIO3/DP17A                       | U3                      | DPIO           | DPIO           | 3    | _                        |

| PIO3/DP17B                       | V3                      | DPIO           | DPIO           | 3    |                          |

| PIO3/DP18A                       | W3<br>Y3                | DPIO           | DPIO           | 3    | _                        |

| PIO3/DP18B                       |                         | DPIO           | DPIO           |      | -                        |

| PIO3/DP19A                       | L7                      | DPIO           | DPIO           | 3    | G3                       |

| PIO3/DP19B                       | L8                      | DPIO           | DPIO           | 3    | G4                       |

| PIO3/DP20A                       | M7                      | DPIO           | DPIO           | 3    | H3                       |

| PIO3/DP20B                       | M8                      | DPIO           | DPIO           |      | H4                       |

| PIO3/DP21A                       | N7                      | DPIO           | DPIO           | 3    | J3                       |

| PIO3/DP21B                       | N5                      | DPIO           | DPIO           | 3    | J1                       |

| PIO3/DP22A                       | P7                      | DPIO           | DPIO           | 3    | K3                       |

| PIO3/DP22B                       | P8                      | DPIO           | DPIO           |      | K4                       |

| PIO3/DP23A<br>PIO3/DP23B         | R5<br>T5                | DPIO<br>DPIO   | DPIO<br>DPIO   | 3    | L1<br>M1                 |

|                                  |                         |                |                |      |                          |

| PIO3/DP24A<br>PIO3/DP24B         | U5<br>V5                | DPIO<br>DPIO   | DPIO<br>DPIO   | 3    | N1<br>P1                 |

|                                  | V5<br>F1                |                | _              | 3    | 71                       |

| VCCIO_3                          | F1<br>P1                | VCCIO<br>VCCIO | VCCIO<br>VCCIO | 3    |                          |

|                                  | L1                      | VCCIO          | ACCIO          | 3    |                          |

| iCE65L04       |       | DiePlus |       |       |     |          |        |

|----------------|-------|---------|-------|-------|-----|----------|--------|

| Pad Name       | VQ100 | CB132   | CB196 | CB284 | Pad | X (µm)   | Υ (μm) |

| PIO2 08        | _     | L6      | Р3    | R10   | 74  | 965.00   | 37.20  |

| VCCIO_2        | 31    | M5      | M5    | T9    | 75  | 1,000.00 | 139.20 |

| PIO2_09        | _     | P5      | K5    | V9    | 76  | 1,035.00 | 37.20  |

| PIO2_10        | _     | M6      | N4    | T10   | 77  | 1,070.00 | 139.20 |

| GND            | 32    | P6      | H7    | V10   | 78  | 1,105.00 | 37.20  |

| PIO2_11        | _     | _       | P4    | Y4    | 79  | 1,140.00 | 139.20 |

| PIO2_12        | _     | _       | L6    | Y5    | 80  | 1,175.00 | 37.20  |

| PIO2_13        | _     | _       | _     | AB6   | 81  | 1,210.00 | 139.20 |

| PIO2_14        | _     | _       | _     | AB7   | 82  | 1,245.00 | 37.20  |

| PIO2_15        | _     | _       | _     | AB8   | 83  | 1,280.00 | 139.20 |

| PIO2_16        | _     | _       | _     | AB9   | 84  | 1,315.00 | 37.20  |

| PIO2_17        | _     | _       | _     | AB10  | 85  | 1,350.00 | 139.20 |

| PIO2_18        | _     | _       | _     | AB11  | 86  | 1,385.00 | 37.20  |

| GND            | _     | Ј8      | H8    | N12   | 87  | 1,420.00 | 139.20 |

| PIO2_19        | _     | _       | K6    | Y6    | 88  | 1,455.00 | 37.20  |

| PIO2_20        | _     | _       | N5    | Y7    | 89  | 1,490.00 | 139.20 |

| VCC            | _     | _       | J4    | Y8    | 90  | 1,525.00 | 37.20  |

| PIO2_21        | _     | _       | M6    | Y9    | 91  | 1,560.00 | 139.20 |

| PIO2_22        | _     | _       | N6    | Y10   | 92  | 1,595.00 | 37.20  |

| GBIN5/PIO2_23  | 33    | P7      | P5    | V11   | 93  | 1,630.00 | 139.20 |

| GBIN4/PIO2_24  | 34    | P8      | L7    | V12   | 94  | 1,665.00 | 37.20  |

| PIO2_25        | _     | _       | _     | AB12  | 95  | 1,700.00 | 139.20 |

| VCCIO_2        | _     | _       | J9    | Y11   | 96  | 1,735.00 | 37.20  |

| PIO2_26        | _     | _       | _     | AB13  | 97  | 1,770.00 | 139.20 |

| PIO2_27        | _     | _       | K7    | AB14  | 98  | 1,805.00 | 37.20  |

| GND            | _     | _       | J5    | Y12   | 99  | 1,840.00 | 139.20 |

| PIO2_28        | _     | _       | K9    | AB15  | 100 | 1,875.00 | 37.20  |

| PIO2_29        | _     | _       | M7    | Y13   | 101 | 1,910.00 | 139.20 |

| PIO2_30        | _     | _       | K8    | Y14   | 102 | 1,945.00 | 37.20  |

| PIO2_31        | _     | _       | P7    | Y15   | 103 | 1,980.00 | 139.20 |

| PIO2_32        | _     | _       | L8    | Y17   | 104 | 2,015.00 | 37.20  |

| PIO2_33        | _     | _       | P8    | Y18   | 105 | 2,050.00 | 139.20 |

| PIO2_34        | _     | _       | N8    | Y19   | 106 | 2,085.00 | 37.20  |

| PIO2_35        | _     | _       | М8    | Y20   | 107 | 2,120.00 | 139.20 |

| VCC            | 35    | J7      | J7    | N11   | 108 | 2,155.00 | 37.20  |

| VCC            | _     | _       | _     | _     | 109 | 2,190.00 | 139.20 |

| PIO2_36        | 36    | P9      | P9    | V13   | 110 | 2,225.00 | 37.20  |

| PIO2_37        | 37    | M7      | N9    | T11   | 111 | 2,260.00 | 139.20 |

| VCCIO_2        | 38    | J9      | N10   | N13   | 112 | 2,295.00 | 37.20  |

| PIO2_38        | _     | L7      | M9    | R11   | 113 | 2,330.00 | 139.20 |

| GND            | 39    | H8      | Ј8    | M12   | 114 | 2,365.00 | 37.20  |

| PIO2_39        | _     | M8      | N12   | T12   | 115 | 2,400.00 | 139.20 |

| PIO2_40        | _     | L8      | N11   | R12   | 116 | 2,435.00 | 37.20  |

| PIO2_41        | 40    | M9      | N13   | T13   | 117 | 2,470.00 | 139.20 |

| PIO2_42/CBSEL0 | 41    | L9      | L9    | R13   | 118 | 2,505.00 | 37.20  |

| PIO2_43/CBSEL1 | 42    | P10     | P10   | V14   | 119 | 2,540.00 | 139.20 |

| CDONE          | 43    | M10     | M10   | T14   | 120 | 2,575.00 | 37.20  |

| iCE65L04 |       | DiePlus | 5     |       |     |          |          |

|----------|-------|---------|-------|-------|-----|----------|----------|

| Pad Name | VQ100 | CB132   | CB196 | CB284 | Pad | X (µm)   | Y (µm)   |

| PIO1 24  | _     | _       | G11   | F20   | 167 | 3,712.80 | 1,812.00 |

| PIO1_25  | _     | _       | F11   | E20   | 168 | 3,610.80 | 1,847.00 |

| PIO1 26  | _     | _       | E10   | D20   | 169 | 3,712.80 | 1,882.00 |

| PIO1_27  | _     | _       | E14   | C20   | 170 | 3,610.80 | 1,917.00 |

| GND      | _     | G8      | G8    | L12   | 171 | 3,712.80 | 1,952.00 |

| GND      | _     | _       | _     | _     | 172 | 3,610.80 | 1,987.00 |

| PIO1 28  | _     | _       | F12   | G22   | 173 | 3,712.80 | 2,022.00 |

| PIO1_29  | _     | G12     | D14   | L16   | 174 | 3,610.80 | 2,057.00 |

| PIO1_30  | 64    | G11     | E13   | L15   | 175 | 3,712.80 | 2,092.00 |

| PIO1_31  | 65    | F12     | C14   | K16   | 176 | 3,610.80 | 2,127.00 |

| VCC      | _     | _       | K13   | L20   | 177 | 3,712.80 | 2,162.00 |

| VCC      | _     | _       | _     | _     | 178 | 3,610.80 | 2,197.00 |

| PIO1_32  | 66    | E14     | E11   | J18   | 179 | 3,712.80 | 2,232.00 |

| PIO1_33  | _     | F11     | C13   | K15   | 180 | 3,610.80 | 2,267.00 |

| VCCIO_1  | 67    | F9      | F9    | K13   | 181 | 3,712.80 | 2,302.00 |

| VCCIO_1  | _     | _       | _     | _     | 182 | 3,610.80 | 2,337.00 |

| PIO1_34  | 68    | E12     | E12   | J16   | 183 | 3,712.80 | 2,377.00 |

| PIO1_35  | 69    | D14     | B14   | H18   | 184 | 3,610.80 | 2,427.00 |

| GND      | 70    | G9      | G9    | L13   | 185 | 3,712.80 | 2,477.00 |

| PIO1_36  | 71    | E11     | B13   | J15   | 186 | 3,610.80 | 2,527.00 |

| PIO1_37  | 72    | D12     | D12   | H16   | 187 | 3,712.80 | 2,577.00 |

| PIO1_38  | 73    | C14     | C12   | G18   | 188 | 3,610.80 | 2,627.00 |

| PIO1_39  | 74    | B14     | D11   | F18   | 189 | 3,712.80 | 2,677.00 |

| VPP_2V5  | 75    | A14     | A14   | E18   | 190 | 3,610.80 | 2,739.68 |

| VPP_FAST | 76    | A13     | A13   | E17   | 191 | 3,097.00 | 2,962.80 |

| VCC      | 77    | F8      | F8    | K12   | 192 | 2,997.00 | 2,860.80 |

| VCC      | 77    | F8      | F8    | K12   | 193 | 2,947.00 | 2,962.80 |

| PIO0_00  | 78    | A12     | C11   | E16   | 194 | 2,897.00 | 2,860.80 |

| PIO0_01  | _     | C12     | _     | G16   | 195 | 2,847.00 | 2,962.80 |

| PIO0_02  | 79    | A11     | A12   | E15   | 196 | 2,797.00 | 2,860.80 |

| PIO0_03  | 80    | C11     | B11   | G15   | 197 | 2,747.00 | 2,962.80 |

| PIO0_04  | _     | D11     |       | H15   | 198 | 2,697.00 | 2,860.80 |

| PIO0_05  | 81    | A10     | D10   | E14   | 199 | 2,647.00 | 2,962.80 |

| PIO0_06  | 82    | C10     | A11   | G14   | 200 | 2,612.00 | 2,860.80 |

| PIO0_07  | 83    | D10     | D9    | H14   | 201 | 2,577.00 | 2,962.80 |

| GND      | 84    | A9      | H6    | E13   | 202 | 2,542.00 | 2,860.80 |

| GND      | _     | _       | _     | _     | 203 | 2,507.00 | 2,962.80 |

| PIO0_08  | 85    | C9      | C10   | G13   | 204 | 2,472.00 | 2,860.80 |

| PIO0_09  | 86    | D9      | A10   | H13   | 205 | 2,437.00 | 2,962.80 |

| PIO0_10  | 87    | C8      | B10   | G12   | 206 | 2,402.00 | 2,860.80 |

| PIO0_11  | _     | D8      | E9    | H12   | 207 | 2,367.00 | 2,962.80 |

| PIO0_12  |       |         |       | A18   | 208 | 2,332.00 | 2,860.80 |

| PIO0_13  | _     |         | _     | A17   | 209 | 2,297.00 | 2,962.80 |

| PIO0_14  |       | _       | _     | A16   | 210 | 2,262.00 | 2,860.80 |

| PIO0_15  | - 00  |         | 40    | A15   | 211 | 2,227.00 | 2,962.80 |

| VCCIO_0  | 88    | A8      | A8    | E12   | 212 | 2,192.00 | 2,860.80 |

| VCCIO_0  |       |         | _     |       | 213 | 2,157.00 | 2,962.80 |

## **AC Timing Guidelines**

The following examples provide some guidelines of device performance. The actual performance depends on the specific application and how it is physically implemented in the iCE65 FPGA using the Lattice iCEcube software. The following guidelines assume typical conditions (VCC = 1.0 V or 1.2 V as specified, temperature =  $25 \,^{\circ}$ C). Apply derating factors using the iCEcube timing analyzer to adjust to other operating regimes.

## **Programmable Logic Block (PLB) Timing**

Table 54 provides timing information for the logic in a Programmable Logic Block (PLB), which includes the paths shown in Figure 55 and Figure 56.

Figure 55 PLB Sequential Timing Circuit

Figure 56 PLB Combinational Timing Circuit

Table 54: Typical Programmable Logic Block (PLB) Timing

|                     |                       |                       | Device: iCE65                                                                                                                                     | L01 L04, L08 |       | 3     |           |       |

|---------------------|-----------------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-------|-------|-----------|-------|

|                     |                       |                       | Power/Speed Grade                                                                                                                                 | -т           | -     | Ł     | <b>–Т</b> |       |

|                     |                       |                       | Nominal VCC                                                                                                                                       | 1.2 V        | 1.0 V | 1.2 V | 1.2 V     |       |

| Symbol              | From                  | То                    | Description                                                                                                                                       | Тур.         | Тур.  | Тур.  | Тур.      | Units |

|                     |                       | Sequen                | tial Logic Paths                                                                                                                                  |              |       |       |           |       |

| F <sub>TOGGLE</sub> | GBIN<br>input         | GBIN<br>input         | Flip-flop toggle frequency. DFF flip-flop output fed back to LUT4 input with 4-input XOR, clocked on same clock edge.                             | 256          | 224   | 256   | 256       | MHz   |

| t <sub>CKO</sub>    | DFF<br>clock<br>input | PIO<br>output         | Logic cell flip-flop (DFF) clock-to-output time, measured from the DFF CLK input to PIO output, including interconnect delay.                     | 5.4          | 16.5  | 8.7   | 7.1       | ns    |

| t <sub>GBCKLC</sub> | GBIN<br>input         | DFF<br>clock<br>input | Global Buffer Input (GBIN) delay, though Global Buffer (GBUF) clock network to clock input on the logic cell DFF flip-flop.                       | 2.2          | 7.3   | 3.8   | 2.7       | ns    |

| t <sub>SULI</sub>   | PIO<br>input          | GBIN<br>input         | Minimum setup time on PIO input, through LUT4, to DFF flip-flop D-input before active clock edge on the GBIN input, including interconnect delay. | 1.0          | 4.0   | 2.1   | 1.2       | ns    |

| t <sub>HDLI</sub>   | GBIN<br>input         | PIO<br>input          | Minimum hold time on PIO input, through LUT4, to DFF flip-flop D-input after active clock edge on the GBIN input, including interconnect delay.   | 0            | 0     | 0     | 0         | ns    |

|                     |                       | Combin                | ational Logic Paths                                                                                                                               |              |       |       |           |       |

| t <sub>LUT4IN</sub> | PIO<br>input          | LUT4<br>input         | Asynchronous delay from PIO input pad to adjacent PLB interconnect.                                                                               | 2.6          | 9.8   | 5.2   | 3.3       | ns    |

| t <sub>ILO</sub>    | LUT4<br>input         | LUT4<br>output        | Logic cell LUT4 combinational logic propagation delay, regardless of logic complexity from input to output.                                       | 0.6          | 1.9   | 1.0   | 0.6       | ns    |

| t <sub>LUT4IN</sub> | LUT4<br>output        | PIO<br>output         | Asynchronous delay from adjacent PLB interconnect to PIO output pad.                                                                              | 4.9          | 16.0  | 8.4   | 6.6       | ns    |

|     |             | minimum temperature to -40°C in Figure 2 and Table 48. Added NVCM programming temperature to Table 48.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.3 | 17-DEC-2008 | Added footprint and pinout information for the CS110 Wafer-Level Chip-Scale Ball Grid Array. Clarified that the CB196 footprint shown is for the iCE65L04; the iCE65L08 footprint for the CB196 package is similar but different. Added updated information on Differential Inputs and Outputs, including support for SubLVDS. Updated Electrical Characteristics and AC Timing Guidelines sections. Added support for the LVCMOS15 I/O standard. Corrected the diagram showing the direct differential clock input, Figure 16. Updated the number of I/Os by package in Table 34. Updated company address. Other minor updates throughout.                                  |

| 1.2 | 11-OCT-2008 | Updated I/O Bank 3 characteristics in Table 7 and Table 51. Corrected label in Figure 14. Added JTAG configuration to Table 20. Added pull-up resistor information in Table 22 and Figure 21. Added "Internal Device Reset" section. Updated internal oscillator performance in and Table 57. Updated configuration timing in Table 58 based on new oscillator timing. Completely reorganized the "Package and Pinout Information" section. Added information on CS63 and CB196 packages. Updated information on VPP_2V5 signal in Table 36. Reduced package height for CB132 and CB284 packages to 1.0 mm. Added "Differential Inputs" and "Differential Outputs" sections. |

| 1.1 | 4-SEPT-2008 | Updated package roadmap (Table 2) and updated ordering codes (Figure 2). Updated Figure 7. Updated Figure 24. Added CS63 package footprint (Figure 36), pinout (Table 39) and Package.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 1.0 | 31-MAY-2008 | Initial public release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |