Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                                              |

|--------------------------------|------------------------------------------------------------------------------|

| Product Status                 | Obsolete                                                                     |

| Number of LABs/CLBs            | 960                                                                          |

| Number of Logic Elements/Cells | 7680                                                                         |

| Total RAM Bits                 | 131072                                                                       |

| Number of I/O                  | 222                                                                          |

| Number of Gates                | -                                                                            |

| Voltage - Supply               | 1.14V ~ 1.26V                                                                |

| Mounting Type                  | Surface Mount                                                                |

| Operating Temperature          | 0°C ~ 70°C (TA)                                                              |

| Package / Case                 | 284-VFBGA, CSPBGA                                                            |

| Supplier Device Package        | 284-CSPBGA (12x12)                                                           |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/ice65l08f-tcb284c |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Input Signal Path**

As shown in Figure 7, a signal from a package pin optionally feeds directly into the device, or is held in an input register. The input signal connects to the programmable interconnect resources through the IN signal. Table 9 describes the input behavior, assuming that the output path is not used or if a bidirectional I/O, that the output driver is in its high-impedance state (Hi-Z). Table 9 also indicates the effect of the Power-Saving I/O Bank iCEgate Latch and the Input Pull-Up Resistors on I/O Banks 0, 1, and 2.

See Input and Output Register Control per PIO Pair for information about the registered input path.

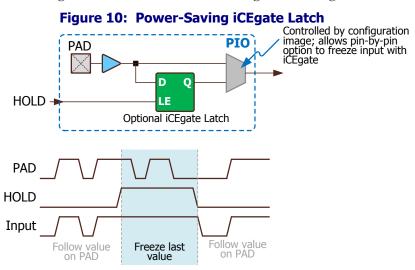

#### Power-Saving I/O Bank iCEgate Latch

To save power, the optional iCEgate latch can selectively freeze the state of individual, non-registered inputs within an I/O bank. Registered inputs are effectively frozen by their associated clock or clock-enable control. As shown in Figure 10, the iCEgate HOLD control signal captures the external value from the associated asynchronous input. The HOLD signal prevents switching activity on the PIO pad from affecting internal logic or programmable interconnect. Minimum power consumption occurs when there is no switching. However, individual pins within the I/O bank can bypass the iCEgate latch and directly feed into the programmable interconnect, remaining active during low-power operation. This behavior is described in Table 9. The decision on which asynchronous inputs use the iCEgate feature and which inputs bypass it is determined during system design. In other words, the iCEgate function is part of the source design used to create the iCE65 configuration image.

| Table 9:  | PTO Non    | -Registered  | Input O  | nerations   |

|-----------|------------|--------------|----------|-------------|

| I UDIC J. | 1 10 11011 | IXCHISECI CU | TIIDUL O | DCI GCIOII3 |

|                           | HOLD          | Bitstrean   | n Setting   | PAD       | IN             |

|---------------------------|---------------|-------------|-------------|-----------|----------------|

|                           |               | Controlled  | Input Pull- |           | Input Value to |

| Operation                 | iCEgate Latch | by iCEgate? | Up Enabled? | Pin Value | Interconnect   |

| Data Input                | 0             | X           | X           | PAD       | PAD Value      |

| Pad Floating, No Pull-up  | 0             | Χ           | No          | Z         | (Undefined)    |

| Pad Floating, Pull-up     | 0             | Χ           | Yes         | Z         | 1              |

| Data Input, Latch         | Χ             | No          | X           | PAD       | PAD Value      |

| Bypassed                  |               |             |             |           |                |

| Pad Floating, No Pull-up, | X             | No          | No          | Z         | (Undefined)    |

| Latch Bypassed            |               |             |             |           |                |

| Pad Floating, Pull-up,    | X             | No          | Yes         | Z         | 1              |

| Latch Bypassed            |               |             |             |           |                |

| Low Power Mode, Hold      | 1             | Yes         | X           | X         | Last Captured  |

| Last Value                |               |             |             |           | PAD Value      |

There are four iCEgate HOLD controls, one per each I/O bank. The iCEgate HOLD control input originates within the interconnect fabric, near the middle of the I/O edge. Consequently, the HOLD signal is optionally controlled externally through a PIO pin or from other logic within the iCE65 device.

For best possible performance, the global buffer inputs (GBIN[7:-0]) connect directly to the their associated global buffers (GBUF[7:0]), bypassing the PIO logic and iCEgate circuitry as shown in Figure 7. Consequently, the direct GBIN-to-GBUF connection cannot be blocked by the iCEgate circuitry. However, it is possible to use iCEgate to block PIO-to-GBUF clock connections.

For additional information on using the iCEgate feature, please refer to the following application note.

AN002: Using iCEgate Blocking for Ultra-Low Power

#### Input Pull-Up Resistors on I/O Banks 0, 1, and 2

The PIO pins in I/O Banks 0, 1, and 2 have an optional input pull-up resistor. Pull-up resistors are not provided in iCE65L04 and iCE65L08 I/O Bank 3. During the iCE65 configuration process, the input pull-up resistor is unconditionally enabled and pulls the input to within a diode drop of the associated I/O bank supply voltage (VCCIO #). This prevents any signals from floating on the circuit board during configuration.

After iCE65 configuration is complete, the input pull-up resistor is optional, defined by a configuration bit. The pull-up resistor is also useful to tie off unused PIO pins. The Lattice iCEcube development software defines all unused PIO pins in I/O Banks 0, 1 and 2 as inputs with the pull-up resistor turned on. The pull-up resistor value depends on the VCCIO voltage applied to the bank, as shown in Table 49.

Note: JTAG inputs TCK, TDI and TMS do not have the input pull-up resistor and must be tied off to GND when unused, else VCCIO\_1 draws current.

#### No Input Pull-up Resistors on I/O Bank 3 of iCE65L04 and iCE65L08

The PIO pins in I/O Bank 3 do not have an internal pull-up resistor. To minimize power consumption, tie unused PIO pins in Bank 3 to a known logic level or drive them as a disabled high-impedance output.

#### **Input Hysteresis**

Inputs typically have about 50 mV of hysteresis, as indicated in Table 49.

#### **Output and Output Enable Signal Path**

As shown in Figure 7, a signal from programmable interconnect feeds the OUT signal on a Programmable I/O pad. This output connects either directly to the associated package pin or is held in an optional output flip-flop. Because all flip-flops are automatically reset after configuration, the output from the output flip-flop can be optionally inverted so that an active-Low output signal is held in the disabled (High) state immediately after configuration.

Similarly, each Programmable I/O pin has an output enable or three-state control called OE. When OE = High, the OUT output signal drives the associated pad, as described in Table 10. When OE = Low, the output driver is in the high-impedance (Hi-Z) state. The OE output enable control signal itself connects either directly to the output buffer or is held in an optional register. The output buffer is optionally permanently enabled or permanently disabled, either to unconditionally drive output signals, or to allow input-only signals.

Table 10: PIO Output Operations (non-registered operation, no inversions)

|                   | OUT         | OE     |      |

|-------------------|-------------|--------|------|

| Operation         | Data Output | Enable | PAD  |

| Three-State       | Χ           | 0      | Hi-Z |

| Drive Output Data | OUT         | 1*     | OUT  |

X = don't care,  $1^* = High or unused$ , Hi-Z = high-impedance, three-stated, floating.

See Input and Output Register Control per PIO Pair for information about the registered input path.

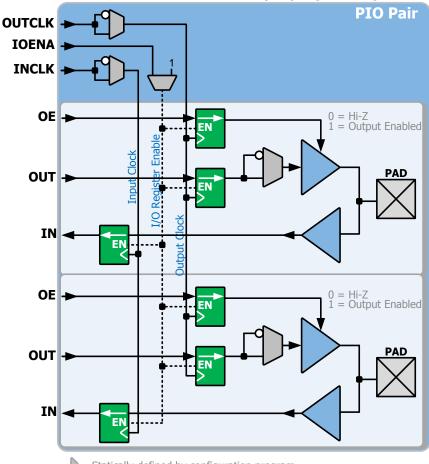

#### **Input and Output Register Control per PIO Pair**

PIO pins are grouped into pairs for synchronous control. Registers within pairs of PIO pins share common input clock, output clock, and I/O clock enable control signals, as illustrated in Figure 11. The combinational logic paths are removed from the drawing for clarity.

The INCLK clock signal only controls the input flip-flops within the PIO pair.

The OUTCLK clock signal controls the output flip-flops and the output-enable flip-flops within the PIO pair.

If desired in the iCE65 application, the INCLK and OUTCLK signals can be connected together.

The IOENA clock-enable input, if used, enables all registers in the PIO pair, as shown in Figure 11. By default, the registers are always enabled.

Before laying out your printed-circuit board, run the design through the iCEcube development software to verify that your selected pinout complies with these I/O register pairing requirements. See tables in "Die Cross Reference" starting on page 84.

Figure 11: PIO Pairs Share Clock and Clock Enable Controls (only registered paths shown for clarity)

= Statically defined by configuration program

The pairing of PIO pairs is most evident in the tables in "Die Cross Reference" starting on page 84.

#### **Device Configuration**

As described in Table 20, iCE65 components are configured for a specific application by loading a binary configuration bitstream image, generated by the Lattice development system. For high-volume applications, the bitstream image is usually permanently programmed in the on-chip NVCM, However, the bitstream image can also be stored external in a standard, low-cost commodity SPI serial Flash PROM. The iCE65 component can automatically load the image using the SPI Master Configuration Interface. Similarly, the iCE65 configuration data can be downloaded from an external processor, microcontroller, or DSP processor using an SPI-like serial interface or an IEEE 1149 JTAG interface.

Table 20: iCE65 Device Configuration Modes

| Mode              | Analogy                 | Configuration Data Source                                                                                                                                                        |

|-------------------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NVCM              | ASIC                    | Internal, lowest-cost, secure, one-time programmable Nonvolatile Configuration Memory (NVCM)                                                                                     |

| SPI Flash         | Microprocessor          | External, low-cost, commodity, SPI serial Flash PROM                                                                                                                             |

| SPI<br>Peripheral | Processor<br>Peripheral | Configured by external device, such as a processor, microcontroller, or DSP using practically any data source, such as system Flash, a disk image, or over a network connection. |

| JTAG              | JTAG                    | JTAG configuration requires sending a special command sequence on the SPI interface to enable JTAG configuration. Configuration is controlled by and external device.            |

#### **Configuration Mode Selection**

The iCE65 configuration mode is selected according to the following priority described below and illustrated in Figure 20.

- After exiting the Power-On Reset (POR) state or when CRESET\_B returns High after being held Low for 250 ns or more, the iCE65 FPGA samples the logical value on its SPI\_SS\_B pin. Like other programmable I/O pins, the SPI\_SS\_B pin has an internal pull-up resistor (see Input Pull-Up Resistors on I/O Banks 0, 1, and 2).

- If the SPI SS B pin is sampled as a logic 'l' (High), then ...

- ◆ Check if the iCE65 is enabled to configure from the Nonvolatile Configuration Memory (NVCM). If the iCE65 device has NVCM memory ('F' ordering code) but the NVCM is yet unprogrammed, then the iCE65 device is not enabled to configure from NVCM. Conversely, if the NVCM is programmed, the iCE65 device will configure from NVCM.

- If enabled to configure from NVCM, the iCE65 device configures itself using NVCM.

- If not enabled to configure from NVCM, then the iCE65 FPGA configures using the SPI Master Configuration Interface.

- If the SPI\_SS\_B pin is sampled as a logic '0' (Low), then the iCE65 device waits to be configured from an external controller or from another iCE65 device in SPI Master Configuration Mode using an SPI-like interface.

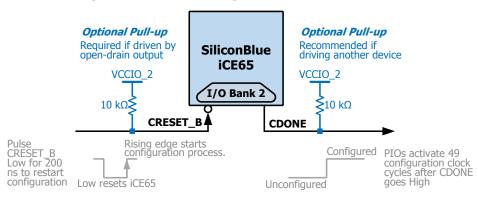

Figure 21: iCE65 Configuration Control Pins

Figure 21 shows the two iCE65 configuration control pins, CRESET\_B and CDONE. Table 23 lists the ball/pin numbers for the configuration control pins by package. When driven Low for at least 200 ns, the dedicated Configuration Reset input, CRESET\_B, resets the iCE65 device. When CRESET\_B returns High, the iCE65 FPGA restarts the configuration process from its power-on conditions (Cold Boot). The CRESET\_B pin is a pure input with no internal pull-up resistor. If driven by open-drain driver or un-driven, then connect the CRESET\_B pin to a  $10 \text{ k}\Omega$  pull-up resistor connected to the VCCIO 2 supply.

Table 23: Configuration Control Ball/Pin Numbers by Package

| Configuration |      |      |       |       |       |       |

|---------------|------|------|-------|-------|-------|-------|

| Control Pins  | CB81 | QN84 | VQ100 | CB132 | CB196 | CB284 |

| CRESET_B      | Ј6   | A21  | 44    | L10   | L10   | R14   |

| CDONE         | H6   | B16  | 43    | M10   | M10   | T14   |

The iCE65 device signals the end of the configuration process by actively turning off the internal pull-down transistor on the Configuration Done output pin, CDONE. The pin has a permanent, weak internal pull-up resistor to the VCCIO\_2 rail. If the iCE65 device drives other devices, then optionally connect the CDONE pin to a 10 k $\Omega$  pull-up resistor connected to the VCCIO\_2 supply.

The PIO pins activate according to their configured function after 49 configuration clock cycles. The internal oscillator is the configuration clock source for the SPI Master Configuration Interface and when configuring from

\* Note: only 14 of the 16 RAM4K Memory Blocks may be pre-initialized in the iCE65L01.

Nonvolatile Configuration Memory (NVCM). When using the SPI Peripheral Configuration Interface, the configuration clock source is the SPI\_SCK clock input pin.

#### **Internal Oscillator**

During SPI Master or NVCM configuration mode, the controlling clock signal is generated from an internal oscillator. The oscillator starts operating at the Default frequency. During the configuration process, however, bit settings within the configuration bitstream can specify a higher-frequency mode in order to maximize SPI bandwidth and reduce overall configuration time. See Table 57: Internal Oscillator Frequency on page 105 for the specified oscillator frequency range.

Using the SPI Master Configuration Interface, internal oscillator controls all the interface timing and clocks the SPI serial Flash PROM via the SPI\_SCK clock output pin.

The oscillator output, which also supplies the SPI SCK clock output during the SPI Flash configuration process, has a 50% duty cycle.

#### **Internal Device Reset**

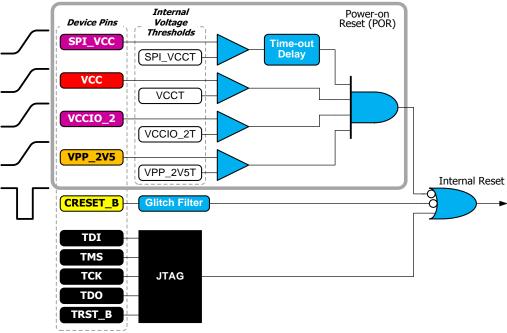

Figure 22 presents the various signals that internally reset the iCE65 internal logic.

- Power-On Reset (POR)

- CRESET B Pin

- ITAG Interface

**Figure 22: iCE65 Internal Reset Circuitry**

#### Power-On Reset (POR)

The Power-on Reset (POR) circuit monitors specific voltage supply inputs and holds the device in reset until all the relevant supplies exceed the internal voltage thresholds. The SPI\_VCC supply also has an additional time-out delay to allow an attached SPI serial PROM to power up properly. Table 24 shows the POR supply inputs. The Nonvolatile Configuration Memory (NVCM) requires that the VPP\_2V5 supply be connected, even if the application does not use the NVCM.

Table 24: Power-on Reset (POR) Voltage Resources

| Supply Rail | iCE65 Production Devices |

|-------------|--------------------------|

| VCC         | Yes                      |

| SPI_VCC     | Yes                      |

| VCCIO_1     | No                       |

| VCCIO_2     | Yes                      |

| VPP_2V5     | Yes                      |

#### CRESET\_B Pin

The CRESET B pin resets the iCE65 internal logic when Low.

#### JTAG Interface

Specific command sequences also reset the iCE65 internal logic.

#### **SPI Master Configuration Interface**

All iCE65 devices, including those with NVCM, can be configured from an external, commodity SPI serial Flash PROM, as shown in Figure 23. The SPI configuration interface is essentially its own independent I/O bank, powered by the VCC\_SPI supply input. Presently, most commercially-available SPI serial Flash PROMs require a 3.3V supply.

- For lowest possible power consumption after configuration, the PROM should also support the **0xB9** Deep Power Down command and the **0xAB** Release from Deep Power-down Command (see Figure 24 and Figure 26). The low-power mode is optional.

- The PROM must be ready to accept commands 10  $\mu$ s after meeting its power-on conditions. In the PROM data sheet, this may be specified as  $t_{VSL}$  or  $t_{VCSL}$ . It is possible to use slower PROMs by holding the CRESET\_B input Low until the PROM is ready, then releasing CRESET\_B, either under program control or using an external power-on reset circuit.

The Lattice iCEman65 development board and associated programming software uses an ST Micro/Numonyx M25Pxx SPI serial Flash PROM.

#### SPI PROM Size Requirements

Table 27 lists the minimum SPI PROM size required to configure an iCE65 device. Larger PROM sizes are allowed, but not required unless the end application uses the additional space. SPI serial PROM sizes are specified in bits. For each device size, the table shows the required minimum PROM size for "Logic Only" (no BRAM initialization) and "Logic + RAM4K" (RAM4K blocks pre-initialized). Furthermore, the table shows the PROM size for varying numbers of configuration images. Most applications will use a single image. Applications that use the Cold Boot or Warm Boot features may use more than one image.

Table 27: Smallest SPI PROM Size (bits), by Device, by Number of Images

|          | 1 In          | nage             | 2 Im          | ages             | 3 Im          | ages             | 4 Images      |                  |

|----------|---------------|------------------|---------------|------------------|---------------|------------------|---------------|------------------|

| Device   | Logic<br>Only | Logic +<br>RAM4K |

| iCE65L01 | 256K          | 256K             | 512K          | 512K             | 1M            | 1M               | 1M            | 1M               |

| iCE65L04 | 512K          | 1M               | 1M            | 2M               | 2M            | 2M               | 2M            | 4M               |

| iCE65L08 | 1M            | 2M               | 2M            | 4M               | 4M            | 4M               | 4M            | 8M               |

#### **Enabling SPI Configuration Interface**

To enable the SPI configuration mode, the SPI\_SS\_B pin must be allowed to float High. The SPI\_SS\_B pin has an internal pull-up resistor. If SPI\_SS\_B is Low, then the iCE65 component defaults to the SPI Slave configuration mode.

#### SPI Master Configuration Process

The iCE65 SPI Master Configuration Interface supports a variety of modern, high-density, low-cost SPI serial Flash PROMs. Most modern SPI PROMs include a power-saving Deep Power-down mode. The iCE65 component exploits this mode for additional system power savings.

The iCE65 SPI interface starts by driving SPI\_SS\_B Low, and then sends a Release from Power-down command to the SPI PROM, hexadecimal command code **0xAB**. Figure 24 provides an example waveform. This initial command wakes up the SPI PROM if it is already in Deep Power-down mode. If the PROM is not in Deep Power-down mode, the extra command has no adverse affect other than that it requires a few additional microseconds during the configuration process. The iCE65 device transmits data on the SPI\_SO output, on the falling edge of the SPI\_SCK output. The SPI PROM does not provide any data to the iCE65 device's SPI\_SI input. After sending the last command bit, the iCE65 device de-asserts SPI\_SS\_B High, completing the command. The iCE65 device then waits a minimum of 10 µS before sending the next SPI PROM command.

Table 28: ColdBoot Select Ball/Pin Numbers by Package

| ColdBoot Select | CB81 | QN84 | VQ100 | CB132 | CB196 | CB284 |

|-----------------|------|------|-------|-------|-------|-------|

| PIO2/CBSEL0     | G5   | B15  | 41    | L9    | L9    | R13   |

| PIO2/CBSEL1     | H5   | A20  | 42    | P10   | P10   | V14   |

When creating the initial configuration image, the Lattice development software loads the start address for up to four configuration images in the bitstream. The value on the CBSEL[1:0] pins tell the configuration controller to read a specific start address, then to load the configuration image stored at the selected address. The multiple bitstreams are stored either in the SPI Flash or in the internal NVCM.

After configuration, the CBSEL[1:0] pins become normal PIO pins available to the application.

The Cold Boot feature allows the iCE65 to be reprogrammed for special application requirements such as the following.

- A normal operating mode and a self-test or diagnostics mode.

- Different applications based on switch settings.

- Different applications based on a card-slot ID number.

#### **Warm Boot Configuration Option**

The Warm Boot configuration is similar to the Cold Boot feature, but is completely under the control of the FPGA application.

A special design primitive, SB\_WARMBOOT, allows an FPGA application to choose between four configuration images using two internal signal ports, Sl and S0, as shown in Figure 27. These internal signal ports connect to programmable interconnect, which in turn can connect to PLB logic and/or PIO pins.

After selecting the desired configuration image, the application then asserts the internal signal BOOT port High to force the FPGA to restart the configuration process from the specified vector address stored in PROM.

A Warm Boot application can only jump to another configuration image that DOES NOT have Warm Boot enabled. There is no such restriction for Cold Boot applications.

#### **Time-Out and Retry**

When configuring from external SPI Flash, the iCE65 device looks for a synchronization word. If the device does not find a synchronization word within its timeout period, the device automatically attempts to restart the configuration process from the very beginning. This feature is designed to address any potential power-sequencing issues that may occur between the iCE65 device and the external PROM.

The iCE65 device attempts to reconfigure six times. If not successful after six attempts, the iCE65 FPGA automatically goes into low-power mode.

#### **SPI Peripheral Configuration Interface**

Using the SPI peripheral configuration interface, an application processor (AP) serially writes a configuration image to an iCE65 FPGA using the iCE65's SPI interface, as shown in Figure 23. The iCE65's SPI configuration interface is a separate, independent I/O bank, powered by the VCC\_SPI supply input. Typically, VCC\_SPI is the same voltage as the application processor's I/O. The configuration control signals, CDONE and CRESET\_B, are supplied by the separate I/O Bank 2 voltage input, VCCIO\_2.

This same SPI peripheral interface supports programming for the iCE65's Nonvolatile Configuration Memory (NVCM).

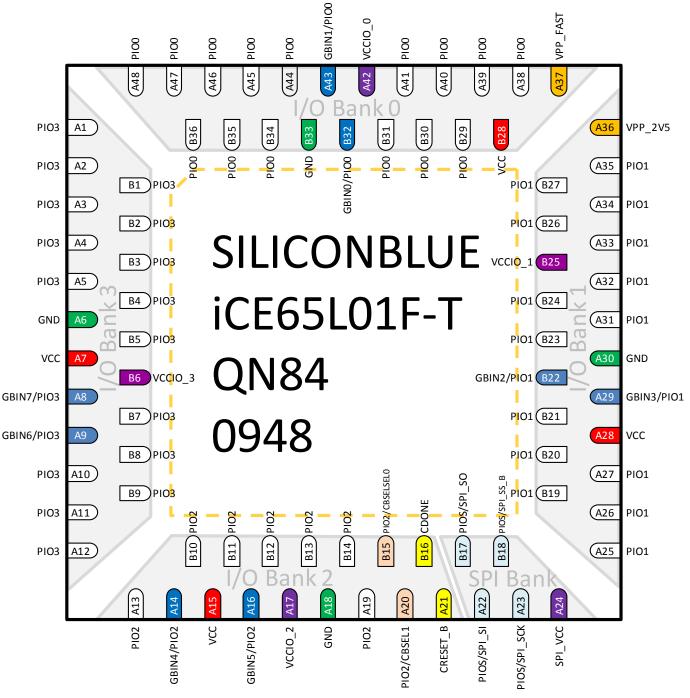

#### **QN84 Quad Flat Pack No-Lead**

The QN84 is a Quad Flat Pack No-Lead package with a 0.5 mm pad pitch.

#### Footprint Diagram

Figure 34 shows the iCE65 footprint diagram for the QN84 package.

Also see Table 38 for a complete, detailed pinout for the QN84 package.

The signal pins are also grouped into the four I/O Banks and the SPI interface.

Figure 34: iCE65 QN84 Quad Flat Pack No-Lead Footprint (Top View)

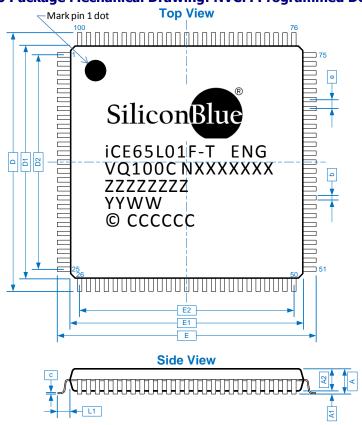

Figure 38: VQ100 Package Mechanical Drawing: NVCM Programmed Device Marking

| Description            | Symbol | Min. | Nominal | Max. | Units |       |

|------------------------|--------|------|---------|------|-------|-------|

| Loado por Edgo         | Х      |      |         | 25   |       |       |

| Leads per Edge         | Υ      |      |         | 25   |       | Leads |

| Number of Signal Leads | 3      | n    |         | 100  |       |       |

| Maximum Size           | Х      | E    | _       | 16.0 |       |       |

| (lead tip to lead tip) | Υ      | D    | _       | 16.0 |       |       |

| Body Size              | Х      | E1   | _       | 14.0 |       |       |

| Body Size              | Υ      | D1   | _       | 14.0 | _     |       |

| Edge Pin Center to     | Х      | E2   | _       | 12.0 | _     |       |

| Center                 |        | D2   | _       | 12.0 |       |       |

| Lead Pitch             |        | е    | _       | 0.50 | _     | mm    |

| Lead Width             |        | b    | 0.17    | 0.20 | 0.27  | mm    |

| Total Package Height   |        | Α    | _       | 1.20 | _     |       |

| Stand Off              |        | A1   | 0.05    | _    | 0.15  |       |

| Body Thickness         |        | A2   | 0.95    | 1.00 | 1.05  |       |

| Lead Length            |        | L1   |         | 1.00 | _     |       |

| Lead Thickness         |        | С    | 0.09    | _    | 0.20  |       |

| Coplanarity            |        |      | _       | 0.08 | _     |       |

## **Top Marking Format**

| Line | Content   | Description        |

|------|-----------|--------------------|

| 1    | Logo      | Logo               |

|      | iCE65L01F | Part number        |

| 2    | -T        | Power/Speed        |

|      | ENG       | Engineering        |

| 3    | VQ100C    | Package type and   |

|      | NXXXXXX   | Lot number         |

| 4    | ZZZZZZZZ  | NVCM Program. code |

| 5    | YYWW      | Date Code          |

| 6    | © CCCCCC  | Country            |

### Thermal Resistance

| Junction-to-Ambient |         |  |  |

|---------------------|---------|--|--|

| θJA (°C/W)          |         |  |  |

| 0 LFM               | 200 LFM |  |  |

| 38 32               |         |  |  |

Figure 42: iCE65L04 CB132 Chip-Scale BGA Footprint (Top View)

|        |   |                |      |                |                | I/      | /О В           | ank            | 0              |                 |                 |                 |      |                   |                |   |          |

|--------|---|----------------|------|----------------|----------------|---------|----------------|----------------|----------------|-----------------|-----------------|-----------------|------|-------------------|----------------|---|----------|

|        |   | 1              | 2    | 3              | 4              | 5       | 6              | 7              | 8              | 9               | 10              | 11              | 12   | 13                | 14             | 1 |          |

|        |   | PIO0           | PIO0 | PIO0           | PIO0           | PIO0    | GBIN0/<br>PIO0 | GBIN1/<br>PIO0 | VCCIO_0        | GND             | PIO0            | PIO0            | PIO0 | VPP_<br>FAST      | VPP_<br>2V5    | A |          |

|        | В | PIO3/<br>DP00A | X    |                |                |         |                |                |                |                 | X               |                 |      | X                 | PIO1           | В |          |

|        | С | PIŌ3/<br>DP00B |      | PIO3/<br>DP01A | PIO0           | PIO0    | PIO0           | PIO0           | PIO0           | PIO0            | PIO0            | PIO0            | PIO0 |                   | PIO1           | С |          |

|        | D | PIO3/<br>DP03A | X    | PIÔ3/<br>DP01B | PIO3/<br>DP02A | PIO0    | PIO0           | PIO0           | PIO0           | PIO0            | PIO0            | PIO0            | PIO1 |                   | PIO1           | D |          |

|        | Ε | PIO3/<br>DP03B |      | VCCIO_3        | PIÔ3/<br>DP02B |         |                |                |                | X               | X               | PIO1            | PIO1 |                   | PIO1           | Ε |          |

|        | F | GND            |      | PIO3/<br>DP04B | PIO3/<br>DP04A |         | VCCIO_0        | GND            | vcc            | VCCIO_1         | X               | PIO1            | PIO1 |                   | GBIN3/<br>PIO1 | F |          |

| × 3    | G | GBIN7/<br>PIO3 |      | PIO3/<br>DP05A | PIO3/<br>DP05B | X       | VCC            | GND            | GND            | GND             |                 | PIO1            | PIO1 |                   | GBIN2/<br>PIO1 | G | <b>X</b> |

| Bank 3 | Н | GBIN6/<br>PIO3 |      | PIO3/<br>DP06A | PIO3/<br>DP06B |         | GND            | GND            | GND            | VCC             |                 | PIO1            | PIO1 |                   | VCCIO_1        | Н | Bank     |

| 9      | J | PIO3/<br>DP07B |      | PIO3/<br>DP07A | VCC            |         | VCCIO_3        | vcc            | GND            | VCCIO_2         |                 | PIO1            | PIO1 |                   | GND            | J | 9        |

|        | K | VCCIO_3        |      | PIO3/<br>DP08A | PIO3/<br>DP08B |         |                |                |                |                 |                 | PIO1            | PIO1 |                   | PIO1           | K |          |

|        | L | PIO3/<br>DP09A |      | GND            | PIO2           | PIO2    | PIO2           | PIO2           | PIO2           | PIO2/<br>CBSEL0 | CRESET_B        | SPI_<br>VCC     | TCK  |                   | PIO1           | L |          |

|        | M | PIŌ3/<br>DP09B |      | PIO2           | PIO2           | VCCIO_2 | PIO2           | PIO2           | PIO2           | PIO2            | CDONE           | PIOS/<br>SPI_SO | TDI  |                   | TRST_B         | M |          |

|        | N | PIO3/<br>DP10A |      |                |                |         |                |                |                |                 |                 | SPI             | Ban  | k                 | TDO            | N |          |

| _      | Р | PIÔ3/<br>DP10B | PIO2 | PIO2           | PIO2           | PIO2    | GND            | GBIN5/<br>PIO2 | GBIN4/<br>PIO2 | PIO2            | PIO2/<br>CBSEL1 | PIOS/<br>SPI_SI |      | PIOS/<br>SPI_SS_B | TMS            | Р | _        |

|        |   | 1              | 2    | 3              | 4              | 5       | 6              | 7              | 8              | 9               | 10              | 11              | 12   | 13                | 14             |   |          |

|        |   |                |      |                |                |         |                | OB             | ank            | 2               |                 |                 |      |                   | J              |   |          |

**I/O Bank 0** 1 2 3 4 5 6 7 8 9 10 11 12 | 13 14 GBIN0/ GBIN1/ VPP PIO0 PIO0 PIO0 PIO<sub>0</sub> PIO0 PIO0 PIO0 VCCIO\_0 GND PIO0 Α PIO0 PIO<sub>0</sub> **FAST** 2V5 PIO3/ B PIO1 B DP00A PIÔ3/ PIO3/ PIO0 PIO0 PIO0 PIO0 PIO0 PIO0 PIO0 PIO0 PIO<sub>0</sub> C PIO1 DP00B DP01A PIO3/ PIŌ3/ PIO3/ PIO0 D PIO0 PIO0 PIO0 PIO0 PIO0 PIO0 **PIO1** PI01 **D** DP03A DP01B DP02A PIŌ3/ PIŌ3/ PIO1 E **PI01 PIO1** VCCIO\_3 DP03B DP02B PIO3/ PIO3/ GBIN3/ F **GND GND** PIO1 VCCIO 0 VCC VCCIO PIO1 **PI01** DP04B DP04A GBIN2/ PIO3/ G DP05B GBIN7/ PIO3/ **GND** PIO1 PIO<sub>1</sub> VCC **GND GND** G DP05A DP11B **PI01** Bank PIO3/ GBIN6/ PIŌ3/ VCCIO\_1 **GND GND GND VCC** PIO1 PIO<sub>1</sub> DP06A DP06B DP11A PIO3/ PIO3/ **VCC** VCCIO 3 **VCC GND** VCCIO\_2 PIO<sub>1</sub> PIO<sub>1</sub> **GND** DP07B DP07A PIO3/ PIO3/ PI01 **K** VCCIO\_3 PIO1 PIO<sub>1</sub> DP08A DP08B PIO3/ **SPI** PI02/ PIO<sub>2</sub> PIO<sub>2</sub> PIO<sub>2</sub> **GND** PIO<sub>2</sub> **PIO2** CRESET\_E **TCK** PIO1 DP09A VCC CBSEL0 PIÔ3/ PIOS/ PIO2 PIO2 VCCIO\_2 PIO2 | PIO2 | PIO2 PIO2 CDONE TDI TRST\_B M DP09B SPI\_SO PIO3/ TDO N DP10A SPI Bank GBIN5/ GBIN4/ PIŌ3/ PIO2/ PIOS/ PIOS/PIOS/ PIO2 Р **PIO2** PIO2 PIO<sub>2</sub> PIO2 **GND** TMS PIO2 PIO<sub>2</sub> DP10B CBSEL SPI\_SCK SPI\_SS SPI\_SI 4 1 2 3 5 7 8 9 11 12 13 I 14 6 10

I/O Bank 2

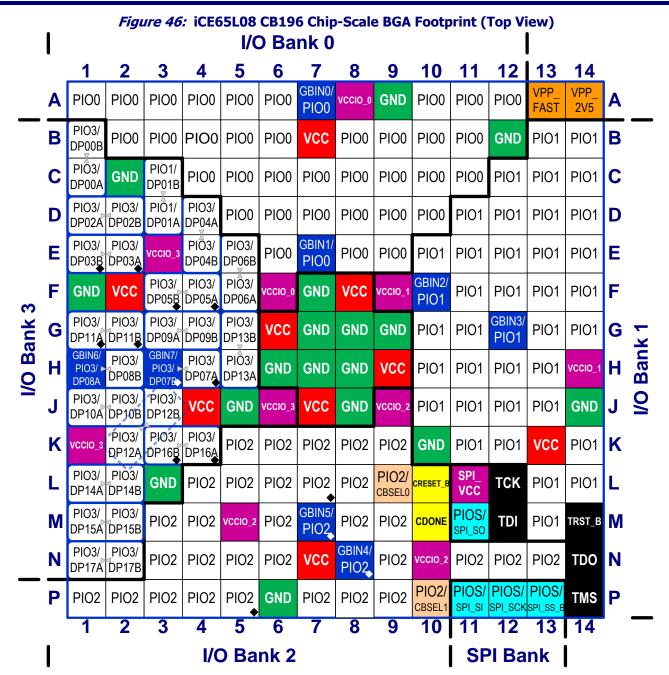

Figure 43: iCE65L08 CB132 Chip-Scale BGA Footprint (Top View)

#### Pinout Table

Table 42 provides a detailed pinout table for the iCE65L04 in the CB196 chip-scale BGA package. Pins are generally arranged by I/O bank, then by ball function. The pinout for the iCE65L08 is different than the iCE64L04 pinout.

Although both the iCE65L04 and iCE65L08 are both available in the CB196 package and *almost* completely pin compatible, there are differences as shown in Table 43.

Table 42: iCE65L04 CB196 Chip-scale BGA Pinout Table

| Ball Function | Ball Number | Pin Type | Bank |

|---------------|-------------|----------|------|

| GBINO/PIOO    | A7          | GBIN     | 0    |

| GBIN1/PIO0    | E7          | GBIN     | 0    |

| PIO0          | A1          | PIO      | 0    |

| PIO0          | A2          | PIO      | 0    |

| PIO0          | A3          | PIO      | 0    |

| PIO0          | A4          | PIO      | 0    |

| Ball Function         | Ball Number                                | Pin Type   | Bank |

|-----------------------|--------------------------------------------|------------|------|

| PIO1                  | F14                                        | PIO        | 1    |

| PIO1                  | G10                                        | PIO        | 1    |

| PIO1                  | G11                                        | PIO        | 1    |

| PIO1                  | G13                                        | PIO        | 1    |

| PIO1                  | G14                                        | PIO        | 1    |

| PIO1                  | H10                                        | PIO        | 1    |

| PIO1                  | H11                                        | PIO        | 1    |

| PIO1                  | H12                                        | PIO        | 1    |

| PIO1                  | H13                                        | PIO        | 1    |

| PIO1                  | J10                                        | PIO        | 1    |

| PIO1                  | J11                                        | PIO        | 1    |

| PIO1                  | J12                                        | PIO        | 1    |

| PIO1                  | J13                                        | PIO        | 1    |

| PIO1                  | K11                                        | PIO        | 1    |

| PIO1                  | K12                                        | PIO        | 1    |

| PIO1                  | K14                                        | PIO        | 1    |

| PIO1                  | L13                                        | PIO        | 1    |

| PIO1                  | L14                                        | PIO        | 1    |

| PIO1                  | M13                                        | PIO        | 1    |

| TCK                   | L12                                        | JTAG       | 1    |

| TDI                   | M12                                        | JTAG       | 1    |

| TDO                   | N14                                        | JTAG       | 1    |

| TMS                   | P14                                        | JTAG       | 1    |

| TRST_B                | M14                                        | JTAG       | 1    |

| VCCIO_1               | F9                                         | VCCIO      | 1    |

| VCCIO_1               | H14                                        | VCCIO      | 1    |

|                       |                                            |            |      |

| CDONE                 | M10                                        | CONFIG     | 2    |

| CRESET_B              | L10                                        | CONFIG     | 2    |

| <b>GBIN4/PIO2 (♦)</b> | <i>iCE65L04:</i> L7                        | GBIN       | 2    |

|                       | <i>iCE65L08:</i> N8                        |            |      |

| GBIN5/PIO2 (♦)        | <i>iCE65L04:</i> P5<br><i>iCE65L08:</i> M7 | GBIN       | 2    |

| PIO2                  | K5                                         | PIO        | 2    |

| PIO2                  | K6                                         | PIO        | 2    |

| PIO2                  | K7                                         | PIO        | 2    |

| PIO2                  | K8                                         | PIO        | 2    |

| PIO2                  | K9                                         | PIO        | 2    |

| PIO2                  | L4                                         | PIO        | 2    |

| PIO2                  | L5                                         | PIO        | 2    |

| PIO2                  | L6                                         | PIO        | 2    |

| PIO2                  | L8                                         | PIO        | 2    |

| PIO2                  | M3                                         | PIO        | 2    |

| PIO2                  | M4                                         | PIO        | 2    |

| PIO2                  | M6                                         | PIO        | 2    |

| PIO2 ( <b>♦</b> )     | <i>iCE65L04:</i> M7                        | PIO        | 2    |

| DIO2                  | <i>iCE65L08:</i> P5                        | DIO        | 2    |

| PIO2<br>PIO2          | M8<br>M9                                   | PIO<br>PIO | 2 2  |

| PIO2                  | N3                                         | PIO        | 2    |

| PIO2                  | N4                                         | PIO        | 2    |

| PIO2                  | N5                                         | PIO        | 2    |

| PIO2                  | N6                                         | PIO        | 2    |

| FIUZ                  | INU                                        | LIO        | 4    |

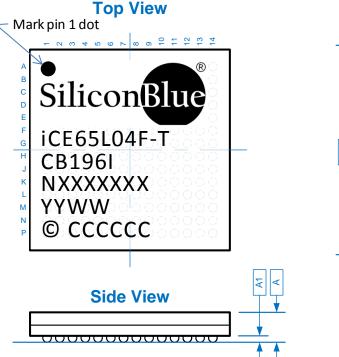

#### Package Mechanical Drawing

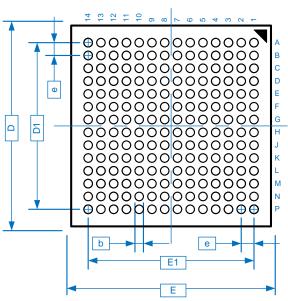

# Figure 47: (a) iCE65L04 CB196 Package Mechanical Drawing

CB196: 8 x8 mm, 196-ball, 0.5 mm ball-pitch, fully-populated, chip-scale ball grid array

Symbol

Ε

D

е

b E1

D1

Α

Α1

Χ

Χ

Description

Number of Ball Columns

Number of Ball Rows

Number of Signal Balls

Body Size

Edge Ball Center to Center

Ball Pitch

**Ball Diameter**

Package Height

Stand Off

**Bottom View**

## **Top Marking Format**

| Min. | Nominal | Max. | Units   |  |  |  |

|------|---------|------|---------|--|--|--|

|      | 14      |      | Columns |  |  |  |

|      | 14      |      | Rows    |  |  |  |

|      | 196     |      | Balls   |  |  |  |

| 7.90 | 8.00    | 8.10 |         |  |  |  |

| 7.90 | 8.00    | 8.10 |         |  |  |  |

| _    | 0.50    | _    |         |  |  |  |

| 0.27 | _       | 0.37 | mm      |  |  |  |

| _    | 6.50    |      | 111111  |  |  |  |

| _    | 6.50    | _    |         |  |  |  |

| _    | _       | 1.00 |         |  |  |  |

| 0.16 | _       | 0.26 |         |  |  |  |

| Content   | Description                                                  |  |  |  |  |

|-----------|--------------------------------------------------------------|--|--|--|--|

| Logo      | Logo                                                         |  |  |  |  |

| iCE65L04F | Part number                                                  |  |  |  |  |

| -T        | Power/Speed                                                  |  |  |  |  |

| CB196I    | Package type                                                 |  |  |  |  |

| ENG       | Engineering                                                  |  |  |  |  |

| NXXXXXX   | Lot Number                                                   |  |  |  |  |

| YYWW      | Date Code                                                    |  |  |  |  |

| © CCCCCC  | Country                                                      |  |  |  |  |

|           | Logo<br>iCE65L04F<br>-T<br>CB196I<br>ENG<br>NXXXXXXX<br>YYWW |  |  |  |  |

#### Thermal Resistance

| Junction-to-Ambient |         |  |  |  |  |  |  |

|---------------------|---------|--|--|--|--|--|--|

| θja (°C/W)          |         |  |  |  |  |  |  |

| 0 LFM               | 200 LFM |  |  |  |  |  |  |

| 42                  | 34      |  |  |  |  |  |  |

| iCE65L04       |       | DiePlus |       |       |     |          |        |

|----------------|-------|---------|-------|-------|-----|----------|--------|

| Pad Name       | VQ100 | CB132   | CB196 | CB284 | Pad | X (µm)   | Υ (μm) |

| PIO2 08        | _     | L6      | Р3    | R10   | 74  | 965.00   | 37.20  |

| VCCIO_2        | 31    | M5      | M5    | T9    | 75  | 1,000.00 | 139.20 |

| PIO2_09        | _     | P5      | K5    | V9    | 76  | 1,035.00 | 37.20  |

| PIO2_10        | _     | M6      | N4    | T10   | 77  | 1,070.00 | 139.20 |

| GND            | 32    | P6      | H7    | V10   | 78  | 1,105.00 | 37.20  |

| PIO2_11        | _     | _       | P4    | Y4    | 79  | 1,140.00 | 139.20 |

| PIO2_12        | _     | _       | L6    | Y5    | 80  | 1,175.00 | 37.20  |

| PIO2_13        | _     | _       | _     | AB6   | 81  | 1,210.00 | 139.20 |

| PIO2_14        | _     | _       | _     | AB7   | 82  | 1,245.00 | 37.20  |

| PIO2_15        | _     | _       | _     | AB8   | 83  | 1,280.00 | 139.20 |

| PIO2_16        | _     | _       | _     | AB9   | 84  | 1,315.00 | 37.20  |

| PIO2_17        | _     | _       | _     | AB10  | 85  | 1,350.00 | 139.20 |

| PIO2_18        | _     | _       | _     | AB11  | 86  | 1,385.00 | 37.20  |

| GND            | _     | Ј8      | H8    | N12   | 87  | 1,420.00 | 139.20 |

| PIO2_19        | _     | _       | K6    | Y6    | 88  | 1,455.00 | 37.20  |

| PIO2_20        | _     | _       | N5    | Y7    | 89  | 1,490.00 | 139.20 |

| VCC            | _     | _       | J4    | Y8    | 90  | 1,525.00 | 37.20  |

| PIO2_21        | _     | _       | M6    | Y9    | 91  | 1,560.00 | 139.20 |

| PIO2_22        | _     | _       | N6    | Y10   | 92  | 1,595.00 | 37.20  |

| GBIN5/PIO2_23  | 33    | P7      | P5    | V11   | 93  | 1,630.00 | 139.20 |

| GBIN4/PIO2_24  | 34    | P8      | L7    | V12   | 94  | 1,665.00 | 37.20  |

| PIO2_25        | _     | _       | _     | AB12  | 95  | 1,700.00 | 139.20 |

| VCCIO_2        | _     | _       | J9    | Y11   | 96  | 1,735.00 | 37.20  |

| PIO2_26        | _     | _       | _     | AB13  | 97  | 1,770.00 | 139.20 |

| PIO2_27        | _     | _       | K7    | AB14  | 98  | 1,805.00 | 37.20  |

| GND            | _     | _       | J5    | Y12   | 99  | 1,840.00 | 139.20 |

| PIO2_28        | _     | _       | K9    | AB15  | 100 | 1,875.00 | 37.20  |

| PIO2_29        | _     | _       | M7    | Y13   | 101 | 1,910.00 | 139.20 |

| PIO2_30        | _     | _       | K8    | Y14   | 102 | 1,945.00 | 37.20  |

| PIO2_31        | _     | _       | P7    | Y15   | 103 | 1,980.00 | 139.20 |

| PIO2_32        | _     | _       | L8    | Y17   | 104 | 2,015.00 | 37.20  |

| PIO2_33        | _     | _       | P8    | Y18   | 105 | 2,050.00 | 139.20 |

| PIO2_34        | _     | _       | N8    | Y19   | 106 | 2,085.00 | 37.20  |

| PIO2_35        | _     | _       | М8    | Y20   | 107 | 2,120.00 | 139.20 |

| VCC            | 35    | J7      | J7    | N11   | 108 | 2,155.00 | 37.20  |

| VCC            | _     | _       | _     | _     | 109 | 2,190.00 | 139.20 |

| PIO2_36        | 36    | P9      | P9    | V13   | 110 | 2,225.00 | 37.20  |

| PIO2_37        | 37    | M7      | N9    | T11   | 111 | 2,260.00 | 139.20 |

| VCCIO_2        | 38    | J9      | N10   | N13   | 112 | 2,295.00 | 37.20  |

| PIO2_38        | _     | L7      | M9    | R11   | 113 | 2,330.00 | 139.20 |

| GND            | 39    | H8      | J8    | M12   | 114 | 2,365.00 | 37.20  |

| PIO2_39        | _     | M8      | N12   | T12   | 115 | 2,400.00 | 139.20 |

| PIO2_40        | _     | L8      | N11   | R12   | 116 | 2,435.00 | 37.20  |

| PIO2_41        | 40    | M9      | N13   | T13   | 117 | 2,470.00 | 139.20 |

| PIO2_42/CBSEL0 | 41    | L9      | L9    | R13   | 118 | 2,505.00 | 37.20  |

| PIO2_43/CBSEL1 | 42    | P10     | P10   | V14   | 119 | 2,540.00 | 139.20 |

| CDONE          | 43    | M10     | M10   | T14   | 120 | 2,575.00 | 37.20  |

| iCE65L08           |          | Packages     | DiePlus |         |        |  |  |  |

|--------------------|----------|--------------|---------|---------|--------|--|--|--|

| Pad Name           | CB196    | CB284        | Pad     | X (µm)  | Υ (μm) |  |  |  |

| PIO2 28            | _        | Y13          | 132     | 2,062.5 | 139.5  |  |  |  |

| GBIN5/PIO2 29      | M7       | V11          | 133     | 2,097.5 | 37.5   |  |  |  |

| GBIN4/PIO2_30      | N8       | V12          | 134     | 2,132.5 | 139.5  |  |  |  |

| GND                | J8       | Y12          | 135     | 2,167.5 | 37.5   |  |  |  |

| GND                | _        | _            | 136     | 2,202.5 | 139.5  |  |  |  |

| PIO2_31            | P8       | Y14          | 137     | 2,237.5 | 37.5   |  |  |  |

| PIO2_32            | -        | AB15         | 138     | 2,272.5 | 139.5  |  |  |  |

| PIO2_33            | M8       | V13          | 139     | 2,307.5 | 37.5   |  |  |  |

| PIO2 34            | _        | AB16         | 140     | 2,342.5 | 139.5  |  |  |  |

| PIO2_35            | L8       | Y15          | 141     | 2,377.5 | 37.5   |  |  |  |

| PIO2_36            | _        | AB17         | 142     | 2,412.5 | 139.5  |  |  |  |

| PIO2_30            | N9       | AB18         | 143     | 2,447.5 | 37.5   |  |  |  |

| PIO2 38            |          | AB19         | 144     | 2,482.5 | 139.5  |  |  |  |

| PIO2_38            | _        | AB20         | 145     | 2,517.5 | 37.5   |  |  |  |

| PIO2_39<br>PIO2_40 |          | AB20<br>AB21 | 146     | 2,517.5 | 139.5  |  |  |  |

| PIO2_40<br>PIO2_41 |          | Y17          | 146     | 2,552.5 | 37.5   |  |  |  |

|                    | _        |              |         |         |        |  |  |  |

| PIO2_42            |          | AB22         | 148     | 2,622.5 | 139.5  |  |  |  |

| PIO2_43            | -        | Y18          | 149     | 2,657.5 | 37.5   |  |  |  |

| PIO2_44            | P9       | Y19          | 150     | 2,692.5 | 139.5  |  |  |  |

| VCC                | N7       | N11          | 151     | 2,727.5 | 37.5   |  |  |  |

| VCC                | —<br>М9  |              | 152     | 2,762.5 | 139.5  |  |  |  |

| PIO2_45            |          | Y20          | 153     | 2,797.5 | 37.5   |  |  |  |

| PIO2_46            | K8       | T11          | 154     | 2,832.5 | 139.5  |  |  |  |

| VCCIO_2            | J9       | N13          | 155     | 2,867.5 | 37.5   |  |  |  |

| VCCIO_2            | —<br>N11 |              | 156     | 2,902.5 | 139.5  |  |  |  |

| PIO2_47            | N11      | R11          | 157     | 2,937.5 | 37.5   |  |  |  |

| GND                | Ј8       | M12          | 158     | 2,972.5 | 139.5  |  |  |  |

| GND                | _        |              | 159     | 3,007.5 | 37.5   |  |  |  |

| PIO2_48            | N12      | T12          | 160     | 3,042.5 | 139.5  |  |  |  |

| PIO2_49            | K9       | R12          | 161     | 3,077.5 | 37.5   |  |  |  |

| PIO2_50            | N13      | T13          | 162     | 3,112.5 | 139.5  |  |  |  |

| PIO2_51/CBSEL0     | L9       | R13          | 163     | 3,147.5 | 37.5   |  |  |  |

| PIO2_52/CBSEL1     | P10      | V14          | 164     | 3,182.5 | 139.5  |  |  |  |

| CDONE              | M10      | T14          | 165     | 3,217.5 | 37.5   |  |  |  |

| CRESET_B           | L10      | R14          | 166     | 3,260.0 | 139.5  |  |  |  |

| PIOS_00/SPI_SO     | M11      | T15          | 167     | 3,320.0 | 37.5   |  |  |  |

| PIOS_01/SPI_SI     | P11      | V15          | 168     | 3,370.0 | 139.5  |  |  |  |

| GND                | Ј8       | Y16          | 169     | 3,420.0 | 37.5   |  |  |  |

| GND                | _        | _            | 170     | 3,470.0 | 139.5  |  |  |  |

| PIOS_02/SPI_SCK    | P12      | V16          | 171     | 3,520.0 | 37.5   |  |  |  |

| PIOS_03/SPI_SS_B   | P13      | V17          | 172     | 3,570.0 | 139.5  |  |  |  |

| VCC                |          | _            | 173     | 3,620.0 | 37.5   |  |  |  |

| VCC                | _        | _            | 174     | 3,670.0 | 139.5  |  |  |  |

| SPI_VCC            | L11      | R15          | 175     | 3,720.0 | 37.5   |  |  |  |

| SPI_VCC            | -        | _            | 176     | 3,770.0 | 139.5  |  |  |  |

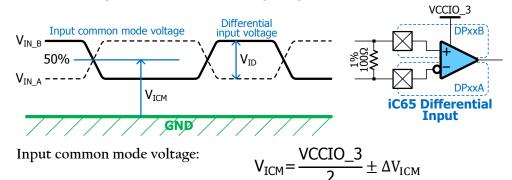

#### **Differential Inputs**

Figure 50: Differential Input Specifications

Differential input voltage:

$$V_{ID} = |V_{IN\_B} - V_{IN\_A}|$$

Table 52: Recommended Operating Conditions for Differential Inputs

| I/O      | V    | CCIO_3 ( | V)   |         | $V_{ID}$ (mV) |     |                                    | V <sub>ICM</sub> (V)       |                                    |

|----------|------|----------|------|---------|---------------|-----|------------------------------------|----------------------------|------------------------------------|

| Standard | Min  | Nom      | Max  | Min Nom |               | Max | Min                                | Nom                        | Max                                |

| LVDS     | 2.38 | 2.50     | 2.63 | 250     | 350           | 450 | $\frac{\text{VCCIO}_3}{2} - 0.30$  | $\frac{\text{VCCIO}_3}{2}$ | $\frac{\text{VCCIO}\_3}{2} + 0.30$ |

| SubLVDS  | 1.71 | 1.80     | 1.89 | 100     | 150           | 200 | $\frac{\text{VCCIO}\_3}{2} - 0.25$ | VCCIO_3                    | $\frac{\text{VCCIO}\_3}{2} + 0.25$ |

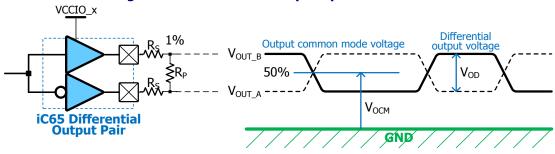

#### **Differential Outputs**

**Figure 51: Differential Output Specifications**

Output common mode voltage:

$$V_{OCM} = \frac{VCCIO_x}{2} \pm \Delta V_{OCM}$$

Differential output voltage:

$$V_{OD} = |V_{OUT\_B} - V_{OUT\_A}|$$

Table 53: Recommended Operating Conditions for Differential Outputs

| I/O      | VCCIO_x (V) |      |      | Ω   |                | V <sub>OD</sub> (mV) |     |     | V <sub>OCM</sub> (V)            |                          |                                 |  |

|----------|-------------|------|------|-----|----------------|----------------------|-----|-----|---------------------------------|--------------------------|---------------------------------|--|

| Standard | Min         | Nom  | Max  | Rs  | R <sub>P</sub> | Min Nom Max          |     | Max | Min                             | Nom                      | Max                             |  |

| LVDS     | 2.38        | 2.50 | 2.63 | 150 | 140            | 300                  | 350 | 400 | $\frac{\text{VCCIO}}{2} - 0.15$ | $\frac{\text{VCCIO}}{2}$ | $\frac{\text{VCCIO}}{2} + 0.15$ |  |

| SubLVDS  | 1.71        | 1.80 | 1.89 | 270 | 120            | 100                  | 150 | 200 | $\frac{\text{VCCIO}}{2} - 0.10$ | $\frac{\text{VCCIO}}{2}$ | $\frac{\text{VCCIO}}{2} + 0.10$ |  |

## iCE65 Ultra Low-Power mobileFPGA<sup>™</sup> Family

Table 60 provides various timing specifications for the SPI peripheral mode interface.

Table 60: SPI Peripheral Mode Timing

|                             |          |         |                                                                                                         |         | All G | ades  |     |

|-----------------------------|----------|---------|---------------------------------------------------------------------------------------------------------|---------|-------|-------|-----|

| Symbol                      | From     | То      | Description                                                                                             | Min.    | Max.  | Units |     |

| t <sub>CR_SCK</sub>         | CRESET_B | SPI_SCK | Minimum time from a rising edge on CRESET_B until                                                       | iC65L01 | 800   | _     | μs  |

|                             |          |         | the first SPI write operation, first SPI_SCK. During this time, the iCE65 FPGA is clearing its internal | iC65L04 | 800   |       |     |

|                             |          |         | configuration memory                                                                                    | iC65L08 | 1200  |       |     |

| t <sub>SUSPISI</sub>        | SPI_SI   | SPI_SCK | Setup time on SPI_SI before the rising SPI_SCK clock e                                                  | 12      | _     | ns    |     |

| t <sub>HDSPISI</sub>        | SPI_SCK  | SPI_SI  | Hold time on SPI_SI after the rising SPI_SCK clock edge                                                 | e       | 12    | _     | ns  |

| <b>t</b> <sub>SPISCKH</sub> | SPI_SCK  | SPI_SCK | SPI_SCK clock High time                                                                                 |         | 20    | _     | ns  |

| t <sub>SPISCKL</sub>        | SPI_SCK  | SPI_SCK | SPI_SCK clock Low time                                                                                  | 20      | _     | ns    |     |

| t <sub>SPISCKCYC</sub>      | SPI_SCK  | SPI_SCK | SPI_SCK clock period*                                                                                   | 40      | 1,000 | ns    |     |

| F <sub>SPI SCK</sub>        | SPI_SCK  | SPI_SCK | Sustained SPI_SCK clock frequency*                                                                      |         | 1     | 25    | MHz |

<sup>\* =</sup> Applies after sending the synchronization pattern.

#### **Power Consumption Characteristics**

#### **Core Power**

Table 61 shows the power consumed on the internal VCC supply rail when the device is filled with 16-bit binary counters, measured with a 32.768 kHz and at 32.0 MHz. Low power (-L) at 1.0 V operation and high-performance (-T) version at 1.2V operation is provided.

Table 61: VCC Power Consumption for Device Filled with 16-Bit Binary Counters

|                    |             |       |      | iCE65L01 |      | iCE6    | 5L04 | iCE65   | Units |     |

|--------------------|-------------|-------|------|----------|------|---------|------|---------|-------|-----|

| Symbol             | Description | Grade | VCC  | Typical  | Max. | Typical | Max. | Typical | Max.  |     |

| -                  | f _0        | -L    | 1.0V | 12       |      | 26      |      | 54      |       | μA  |

| I <sub>CCOK</sub>  | f =0,       | -T    | 1.2V | 19       |      | 43      |      | 90      |       |     |

| -                  | f ≤ 32.768  | -L    | 1.0V | 15       |      | 31      |      | 62      |       |     |

| 1 <sub>CC32K</sub> | kHz         | -T    | 1.2V | 23       |      | 50      |      | 100     |       | μA  |

| -                  | f = 32.0    | -L    | 1.0V | 3        |      | 7       |      | 14      |       | m A |

| <b>L</b> CC32M     | MHz         | -T    | 1.2V | 4        |      | 8       |      | 17      |       | mA  |

#### I/O Power

Table 62 provides the static current by I/O bank. The typical current for I/O Banks 0, 1, 2 and the SPI bank is not measurable within the accuracy of the test environment. The PIOs in I/O Bank 3 use different circuitry and dissipate a small amount of static current.

Table 62: I/O Bank Static Current (f = 0 MHz)

|  | Symbol               |            | Description                                                                                | Typical                           | Max | Units |

|--|----------------------|------------|--------------------------------------------------------------------------------------------|-----------------------------------|-----|-------|

|  | I <sub>cco o</sub>   | I/O Bank 0 | Static current consumption per I/O bank.                                                   | « 1                               |     | μA    |

|  | I <sub>cco 1</sub>   | I/O Bank 1 | f = 0 MHz. No PIO pull-up resistors enabled. All inputs grounded. All outputs driving Low. | « 1                               |     | μA    |

|  | $\mathbf{I}_{CCO_2}$ | I/O Bank 2 |                                                                                            | « 1                               |     | μA    |

|  | I <sub>CCO_3</sub>   | I/O Bank 3 |                                                                                            | iCE65L01: « 1<br>iCE65L04/08: 1.2 |     | μΑ    |

|  | I <sub>CCO_SPI</sub> | SPI Bank   |                                                                                            | « 1                               |     | μA    |

NOTE: The typical static current for I/O Banks 0, 1, 2, and the SPI bank is less than the accuracy of the device tester.

#### **Power Estimator**

To estimate the power consumption for a specific application, please download and use the iCE65 Power Estimator Spreadsheet our use the power estimator built into the iCEcube software.

iCE65 Power Estimator Spreadsheet

# **iCE65 Ultra Low-Power mobileFPGA**<sup>™</sup> **Family**

## **Revision History**

| Version | Date         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|---------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.42    | 30-MAR-2012  | Changed company name. Updated Table 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 2.41    | 1-AUG-2011   | Added VQ100 marking for NVCM programming.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 2.4     | 13-MAY-2011  | Added L01 CB121 package Figure 39. Added note "else VCCIO_1 draws current" to JTAG inputs TCK, TDI and TMS do not have the input pull-up resistor and must be tied off to GND when unused, Table 32. Input pin leakage current Table 49 split by bank. QN84 package drawing, Figure 35, added note "underside metal is at ground potential", increased thermal resistance. Added Marking Format and Thermal resistance to CB81 Packag Mechanical Drawing Figure 33. Added coplanarity specification to VQ100 Package Mechanical Drawing Figure 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 2.3     | 18-OCT-2010  | Added L01 CB81 and L08 CB132 packages.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 2.2.3   | 12-OCT-2010  | Changed Figure 29: Application Processor Waveforms for SPI Peripheral Mode Configuration Process and Table 60 from 300 µs CRESET_B to 800 µs for iCE65L01/04 and 1200 µs for iCE65L08.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 2.2.2   | 8-OCT-2010   | Added iCE65L04 marking specification to Figure 47 CB196 Package Mechanical Drawing.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 2.2.1   | 5-OCT-2010   | Changed FSPI_SCK from 0.125 MHz to 1 MHz in SPI Peripheral Configuration Interface and in Table 60.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 2.2     | 6-AUG-2010   | Programmable Interconnect section removed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 2.1.1   | 26-MAY-2010  | Switched labels on Figure 53 LVCMOS Output High, VCCIO = 1.8V with VCCIO = 2.5V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2.1     | 15-MAR-2010  | Added JTAG unused input tie off guideline. Added marking specification and thermal characteristics to package drawings. Added production datasheet for iCE65L01 with timing update, including QN84, VQ100 and CB132. Added NVCM shut-off on SPI configuration. Added non-standard VCCIO operating conditions. Increased the minimum voltage supply specification for LVCMOS33 to 3.14V in Table 48.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 2.0.1   | 12-NOV-2009  | Recommended Operation Conditions, Table 47, replaced junction with ambient.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 2.0     | 14-SEPT-2009 | Finalized production data sheet for iCE65L04 and iCE65L08. Improved SubLVDS input specification V <sub>ICM</sub> in Table 52. CS63 and CC72 packages removed and placed in iCE DiCE KGD, Known Good Die datasheet. Added "IBIS Models for I/O Banks 0, 1, 2 and the SPI Bank". Added "Printed Circuit Board Layout Information".                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 1.5.1   | 13-JUL-2009  | Updated the text in "SPI PROM Requirements" section. Minor label change in Figure 48.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 1.5     | 20-JUN-2009  | Updated timing information and added –T high-speed device option (affected Figure 2, Table 48, Table 54, Table 55, Table 56, and Table 61). Added support for 3.3V LVCMOS I/Os in I/O Bank 3 (affected Figure 7, Table 5, Table 7, Table 8, Table 47, Table 48, and Table 51). Added a section about the SPI Peripheral Configuration Interface and timing in Table 60. Added a warning that a Warm Boot operation can only jump to another configuration image that has Warm Boot disabled. Updated configuration image size and configuration time for the iCE65L02 in Table 27 and Table 58. Reduced the minimum voltage supply specification for LVCMOS33 to 2.7V in Table 48. Added information about which power rails can be disconnected without effecting the Power-On Reset (POR) circuit and clarified description of VPP_2V5 pin in Table 36. Added I/O characterization curves (Figure 52, Figure 53, and Figure 54). Minor changes to Figure 20 and Figure 21. Changed timing per Figures 54-58 and Tables 55-57.                                                                              |