Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                            |  |

|----------------------------|------------------------------------------------------------|--|

| Product Status             | Active                                                     |  |

| Core Processor             | 56800E                                                     |  |

| Core Size                  | 16-Bit                                                     |  |

| Speed                      | 40MHz                                                      |  |

| Connectivity               | EBI/EMI, SCI, SPI                                          |  |

| Peripherals                | POR, PWM, WDT                                              |  |

| Number of I/O              | 62                                                         |  |

| Program Memory Size        | 256KB (128K x 16)                                          |  |

| Program Memory Type        | FLASH                                                      |  |

| EEPROM Size                | -                                                          |  |

| RAM Size                   | 8K x 16                                                    |  |

| Voltage - Supply (Vcc/Vdd) | 2.25V ~ 3.6V                                               |  |

| Data Converters            | A/D 16x12b                                                 |  |

| Oscillator Type            | External                                                   |  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                         |  |

| Mounting Type              | Surface Mount                                              |  |

| Package / Case             | 144-LQFP                                                   |  |

| Supplier Device Package    | 144-LQFP (20x20)                                           |  |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc56f8156vfve |  |

|                            |                                                            |  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 56F8356/56F8156 General Description

Note: Features in italics are NOT available in the 56F8156 device.

- Up to 60 MIPS at 60MHz core frequency

- DSP and MCU functionality in a unified, C-efficient architecture

- Access up to 1MB of off-chip program and data memory

- Chip Select Logic for glueless interface to ROM and SRAM

- 256KB of Program Flash

- 4KB of Program RAM

- 8KB of Data Flash

- 16KB of Data RAM

- 16KB of Boot Flash

- Up to two 6-channel PWM modules

- Four 4-channel, 12-bit ADCs

- Temperature Sensor

- Up to two Quadrature Decoders

- Optional on-chip regulator

- FlexCAN module

- Two Serial Communication Interfaces (SCIs)

- Up to two Serial Peripheral Interfaces (SPIs)

- Up to four general-purpose Quad Timers

- Computer Operating Properly (COP) / Watchdog

- JTAG/Enhanced On-Chip Emulation (OnCE™) for unobtrusive, real-time debugging

- Up to 62 GPIO lines

- 144-pin LQFP Package

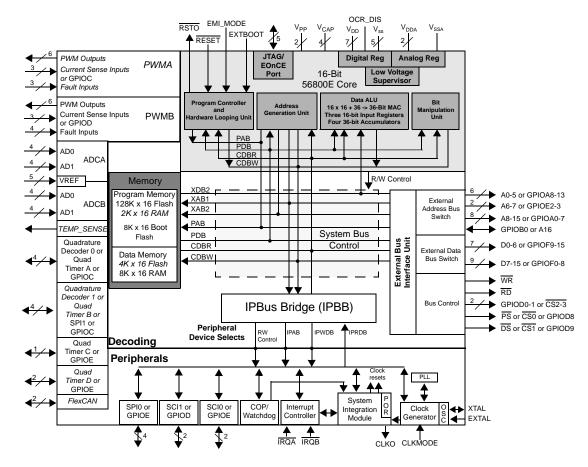

56F8356 / 56F8156 Block Diagram

56F8356 Technical Data, Rev. 13

## Table 2-2 Signal and Package Information for the 144-Pin LQFP (Continued)

| Signal Name             | Pin No. | Туре                       | State<br>During<br>Reset                                     | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------------------|---------|----------------------------|--------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DS<br>(CS1)<br>(GPIOD9) | 47      | Output<br>Input/<br>Output | In reset,<br>output is<br>disabled,<br>pull-up is<br>enabled | Data Memory Select — This signal is actually $\overline{CS1}$ in the EMI,<br>which is programmed at reset for compatibility with the 56F80x DS<br>signal. DS is asserted low for external data memory access.Depending upon the state of the DRV bit in the EMI bus control<br>register (BCR), $\overline{DS}$ is tri-stated when the external bus is inactive. $\overline{CS1}$ resets to provide the $\overline{DS}$ function as defined on the 56F80x<br>devices.Port D GPIO — This GPIO pin can be individually programmed as<br>an input or output pin. |

|                         |         |                            |                                                              | To deactivate the internal pull-up resistor, clear bit 9 in the GPIOD_PUR register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| GPIOD0                  | 48      | Input/<br>Output           | Input,<br>pull-up<br>enabled                                 | <b>Port D GPIO</b> — These two GPIO pins can be individually programmed as input or output pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| (CS2)                   |         | Output                     | enabled                                                      | <b>Chip Select</b> — $\overline{CS2}$ - $\overline{CS3}$ may be programmed within the EMI                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| GPIOD1                  | 49      |                            |                                                              | module to act as chip selects for specific areas of the external memory map.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| (CS3)                   |         |                            |                                                              | Depending upon the state of the DRV bit in the EMI bus control register (BCR), A0–A16 and EMI control signals are tri-stated when the external bus is inactive.                                                                                                                                                                                                                                                                                                                                                                                              |

|                         |         |                            |                                                              | Most designs will want to change the DRV state to DRV = 1 instead of using the default setting.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                         |         |                            |                                                              | At reset, these pins are configured as GPIO.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                         |         |                            |                                                              | To deactivate the internal pull-up resistor, clear the appropriate GPIO bit in the GPIOD_PUR register.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                         |         |                            |                                                              | Example: GPIOD0, clear bit 0 in the GPIOD_PUR register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| TXD0                    | 4       | Output                     | In reset,<br>output is                                       | Transmit Data — SCI0 transmit data output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| (GPIOE0)                |         | Input/<br>Output           | disabled,<br>pull-up is<br>enabled                           | <b>Port E GPIO</b> — This GPIO pin can be individually programmed as an input or output pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                         |         |                            |                                                              | After reset, the default state is SCI output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                         |         |                            |                                                              | To deactivate the internal pull-up resistor, clear bit 0 in the GPIOE_PUR register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

## Table 2-2 Signal and Package Information for the 144-Pin LQFP (Continued)

| Signal Name | Pin No. | Туре             | State<br>During<br>Reset            | Signal Description                                                                                                                                                                                   |

|-------------|---------|------------------|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RXD0        | 5       | Input            | Input,                              | Receive Data — SCI0 receive data input                                                                                                                                                               |

| (GPIOE1)    |         | Input/<br>Output | pull-up<br>enabled                  | <b>Port E GPIO</b> — This GPIO pin can be individually programmed as an input or output pin.                                                                                                         |

|             |         |                  |                                     | After reset, the default state is SCI output.                                                                                                                                                        |

|             |         |                  |                                     | To deactivate the internal pull-up resistor, clear bit 1 in the GPIOE_PUR register.                                                                                                                  |

| TXD1        | 42      | Output           | In reset,<br>output is              | Transmit Data — SCI1 transmit data output                                                                                                                                                            |

| (GPIOD6)    |         | Input/<br>Output | disabled,<br>pull-up is<br>enabled  | <b>Port D GPIO</b> — This GPIO pin can be individually programmed as an input or output pin.                                                                                                         |

|             |         |                  | chabled                             | After reset, the default state is SCI output.                                                                                                                                                        |

|             |         |                  |                                     | To deactivate the internal pull-up resistor, clear bit 6 in the GPIOD_PUR register.                                                                                                                  |

| RXD1        | 43      | Input            | Input,<br>pull-up                   | Receive Data — SCI1 receive data input                                                                                                                                                               |

| (GPIOD7)    |         | Input/<br>Output | enabled                             | <b>Port D GPIO</b> — This GPIO pin can be individually programmed as an input or output pin.                                                                                                         |

|             |         |                  |                                     | After reset, the default state is SCI input.                                                                                                                                                         |

|             |         |                  |                                     | To deactivate the internal pull-up resistor, clear bit 7 in the GPIOD_PUR register.                                                                                                                  |

| тск         | 121     | Schmitt<br>Input | Input,<br>pulled low<br>internally  | <b>Test Clock Input</b> — This input pin provides a gated clock to synchronize the test logic and shift serial data to the JTAG/EOnCE port. The pin is connected internally to a pull-down resistor. |

| TMS         | 122     | Schmitt<br>Input | Input,<br>pulled high<br>internally | <b>Test Mode Select Input</b> — This input pin is used to sequence the JTAG TAP controller's state machine. It is sampled on the rising edge of TCK and has an on-chip pull-up resistor.             |

|             |         |                  |                                     | To deactivate the internal pull-up resistor, set the JTAG bit in the SIM_PUDR register.                                                                                                              |

|             |         |                  |                                     | <b>Note:</b> Always tie the TMS pin to V <sub>DD</sub> through a 2.2K resistor.                                                                                                                      |

| TDI         | 123     | Schmitt<br>Input | Input,<br>pulled high<br>internally | <b>Test Data Input</b> — This input pin provides a serial input data stream to the JTAG/EOnCE port. It is sampled on the rising edge of TCK and has an on-chip pull-up resistor.                     |

|             |         |                  |                                     | To deactivate the internal pull-up resistor, set the JTAG bit in the SIM_PUDR register.                                                                                                              |

#### Table 4-10 External Memory Integration Registers Address Map (Continued) (EMI\_BASE = \$00 F020)

| Register Acronym | Address Offset | Register Description                  | Reset Value                                                                                    |

|------------------|----------------|---------------------------------------|------------------------------------------------------------------------------------------------|

| CSOR 0           | \$8            | Chip Select Option Register 0         | 0x5FCB programmed for chip<br>select for program space, word<br>wide, read and write, 11 waits |

| CSOR 1           | \$9            | Chip Select Option Register 1         | 0x5FAB programmed for chip<br>select for data space, word<br>wide, read and write, 11 waits    |

| CSOR 2           | \$A            | Chip Select Option Register 2         |                                                                                                |

| CSOR 3           | \$B            | Chip Select Option Register 3         |                                                                                                |

| CSOR 4           | \$C            | Chip Select Option Register 4         |                                                                                                |

| CSOR 5           | \$D            | Chip Select Option Register 5         |                                                                                                |

| CSOR 6           | \$E            | Chip Select Option Register 6         |                                                                                                |

| CSOR 7           | \$F            | Chip Select Option Register 7         |                                                                                                |

| CSTC 0           | \$10           | Chip Select Timing Control Register 0 |                                                                                                |

| CSTC 1           | \$11           | Chip Select Timing Control Register 1 |                                                                                                |

| CSTC 2           | \$12           | Chip Select Timing Control Register 2 |                                                                                                |

| CSTC 3           | \$13           | Chip Select Timing Control Register 3 |                                                                                                |

| CSTC 4           | \$14           | Chip Select Timing Control Register 4 |                                                                                                |

| CSTC 5           | \$15           | Chip Select Timing Control Register 5 |                                                                                                |

| CSTC 6           | \$16           | Chip Select Timing Control Register 6 |                                                                                                |

| CSTC 7           | \$17           | Chip Select Timing Control Register 7 |                                                                                                |

| BCR              | \$18           | Bus Control Register                  | 0x016B sets the default<br>number of wait states to 11 for<br>both read and write accesses     |

### Table 4-11 Quad Timer A Registers Address Map (TMRA\_BASE = \$00 F040)

| Register Acronym | Address Offset | Register Description |

|------------------|----------------|----------------------|

| TMRA0_CMP1       | \$0            | Compare Register 1   |

| TMRA0_CMP2       | \$1            | Compare Register 2   |

| TMRA0_CAP        | \$2            | Capture Register     |

| TMRA0_LOAD       | \$3            | Load Register        |

| TMRA0_HOLD       | \$4            | Hold Register        |

| TMRA0_CNTR       | \$5            | Counter Register     |

| TMRA0_CTRL       | \$6            | Control Register     |

| Table 4-12 Quad Timer B Registers Address Map (Continued) |

|-----------------------------------------------------------|

| (TMRB_BASE = \$00 F080)                                   |

| Quad Timer B is NOT available in the 56F8156 device       |

| Register Acronym | Address Offset | Register Description                   |

|------------------|----------------|----------------------------------------|

| TMRB1_SCR        | \$17           | Status and Control Register            |

| TMRB1_CMPLD1     | \$18           | Comparator Load Register 1             |

| TMRB1_CMPLD2     | \$19           | Comparator Load Register 2             |

| TMRB1_COMSCR     | \$1A           | Comparator Status and Control Register |

|                  |                | Reserved                               |

| TMRB2_CMP1       | \$20           | Compare Register 1                     |

| TMRB2_CMP2       | \$21           | Compare Register 2                     |

| TMRB2_CAP        | \$22           | Capture Register                       |

| TMRB2_LOAD       | \$23           | Load Register                          |

| TMRB2_HOLD       | \$24           | Hold Register                          |

| TMRB2_CNTR       | \$25           | Counter Register                       |

| TMRB2_CTRL       | \$26           | Control Register                       |

| TMRB2_SCR        | \$27           | Status and Control Register            |

| TMRB2_CMPLD1     | \$28           | Comparator Load Register 1             |

| TMRB2_CMPLD2     | \$29           | Comparator Load Register 2             |

| TMRB2_COMSCR     | \$2A           | Comparator Status and Control Register |

|                  |                | Reserved                               |

| TMRB3_CMP1       | \$30           | Compare Register 1                     |

| TMRB3_CMP2       | \$31           | Compare Register 2                     |

| TMRB3_CAP        | \$32           | Capture Register                       |

| TMRB3_LOAD       | \$33           | Load Register                          |

| TMRB3_HOLD       | \$34           | Hold Register                          |

| TMRB3_CNTR       | \$35           | Counter Register                       |

| TMRB3_CTRL       | \$36           | Control Register                       |

| TMRB3_SCR        | \$37           | Status and Control Register            |

| TMRB3_CMPLD1     | \$38           | Comparator Load Register 1             |

| TMRB3_CMPLD2     | \$39           | Comparator Load Register 2             |

| TMRB3_COMSCR     | \$3A           | Comparator Status and Control Register |

| Register Acronym | Address Offset | Register Description                   |

|------------------|----------------|----------------------------------------|

| TMRC2_SCR        | \$27           | Status and Control Register            |

| TMRC2_CMPLD1     | \$28           | Comparator Load Register 1             |

| TMRC2_CMPLD2     | \$29           | Comparator Load Register 2             |

| TMRC2_COMSCR     | \$2A           | Comparator Status and Control Register |

|                  |                | Reserved                               |

| TMRC3_CMP1       | \$30           | Compare Register 1                     |

| TMRC3_CMP2       | \$31           | Compare Register 2                     |

| TMRC3_CAP        | \$32           | Capture Register                       |

| TMRC3_LOAD       | \$33           | Load Register                          |

| TMRC3_HOLD       | \$34           | Hold Register                          |

| TMRC3_CNTR       | \$35           | Counter Register                       |

| TMRC3_CTRL       | \$36           | Control Register                       |

| TMRC3_SCR        | \$37           | Status and Control Register            |

| TMRC3_CMPLD1     | \$38           | Comparator Load Register 1             |

| TMRC3_CMPLD2     | \$39           | Comparator Load Register 2             |

| TMRC3_COMSCR     | \$3A           | Comparator Status and Control Register |

#### Table 4-13 Quad Timer C Registers Address Map (Continued) (TMRC\_BASE = \$00 F0C0)

#### Table 4-14 Quad Timer D Registers Address Map (TMRD\_BASE = \$00 F100) Quad Timer D is NOT available in the 56F8156 device

| Register Acronym | Address Offset | Register Description                   |

|------------------|----------------|----------------------------------------|

| TMRD0_CMP1       | \$0            | Compare Register 1                     |

| TMRD0_CMP2       | \$1            | Compare Register 2                     |

| TMRD0_CAP        | \$2            | Capture Register                       |

| TMRD0_LOAD       | \$3            | Load Register                          |

| TMRD0_HOLD       | \$4            | Hold Register                          |

| TMRD0_CNTR       | \$5            | Counter Register                       |

| TMRD0_CTRL       | \$6            | Control Register                       |

| TMRD0_SCR        | \$7            | Status and Control Register            |

| TMRD0_CMPLD1     | \$8            | Comparator Load Register 1             |

| TMRD0_CMPLD2     | \$9            | Comparator Load Register 2             |

| TMRD0_COMSCR     | \$A            | Comparator Status and Control Register |

#### Table 4-23 Serial Communication Interface 0 Registers Address Map (SCI0\_BASE = \$00 F280)

| Register Acronym | Address Offset | Register Description |

|------------------|----------------|----------------------|

| SCI0_SCIBR       | \$0            | Baud Rate Register   |

| SCI0_SCICR       | \$1            | Control Register     |

|                  |                | Reserved             |

| SCI0_SCISR       | \$3            | Status Register      |

| SCI0_SCIDR       | \$4            | Data Register        |

#### Table 4-24 Serial Communication Interface 1 Registers Address Map (SCI1\_BASE = \$00 F290)

| Register Acronym | Address Offset | Register Description |

|------------------|----------------|----------------------|

| SCI1_SCIBR       | \$0            | Baud Rate Register   |

| SCI1_SCICR       | \$1            | Control Register     |

|                  |                | Reserved             |

| SCI1_SCISR       | \$3            | Status Register      |

| SCI1_SCIDR       | \$4            | Data Register        |

#### Table 4-25 Serial Peripheral Interface 0 Registers Address Map (SPI0\_BASE = \$00 F2A0)

| Register Acronym | Address Offset | Register Description        |

|------------------|----------------|-----------------------------|

| SPI0_SPSCR       | \$0            | Status and Control Register |

| SPI0_SPDSR       | \$1            | Data Size Register          |

| SPI0_SPDRR       | \$2            | Data Receive Register       |

| SPI0_SPDTR       | \$3            | Data Transmitter Register   |

| (0.10/1_2/02_2 +0011220) |                |                                   |             |  |  |  |  |  |  |

|--------------------------|----------------|-----------------------------------|-------------|--|--|--|--|--|--|

| Register Acronym         | Address Offset | Register Description              | Reset Value |  |  |  |  |  |  |

| GPIOA_IENR               | \$5            | Interrupt Enable Register         | 0 x 0000    |  |  |  |  |  |  |

| GPIOA_IPOLR              | \$6            | Interrupt Polarity Register       | 0 x 0000    |  |  |  |  |  |  |

| GPIOA_IPR                | \$7            | Interrupt Pending Register        | 0 x 0000    |  |  |  |  |  |  |

| GPIOA_IESR               | \$8            | Interrupt Edge-Sensitive Register | 0 x 0000    |  |  |  |  |  |  |

| GPIOA_PPMODE             | \$9            | Push-Pull Mode Register           | 0 x 3FFF    |  |  |  |  |  |  |

| GPIOA_RAWDATA            | \$A            | Raw Data Input Register           | —           |  |  |  |  |  |  |

#### Table 4-29 GPIOA Registers Address Map (Continued) (GPIOA\_BASE = \$00 F2E0)

### Table 4-30 GPIOB Registers Address Map (GPIOB\_BASE = \$00F300)

| Register Acronym | Address Offset | Register Description              | Reset Value                                  |

|------------------|----------------|-----------------------------------|----------------------------------------------|

| GPIOB_PUR        | \$0            | Pull-up Enable Register           | 0 x 00FF                                     |

| GPIOB_DR         | \$1            | Data Register                     | 0 x 0000                                     |

| GPIOB_DDR        | \$2            | Data Direction Register           | 0 x 0000                                     |

| GPIOB_PER        | \$3            | Peripheral Enable Register        | 0 x 000F for 20-bit EMI address<br>at reset. |

|                  |                |                                   | 0 x 0000 for all other cases.                |

|                  |                |                                   | See Table 4-4 for details.                   |

| GPIOB_IAR        | \$4            | Interrupt Assert Register         | 0 x 0000                                     |

| GPIOB_IENR       | \$5            | Interrupt Enable Register         | 0 x 0000                                     |

| GPIOB_IPOLR      | \$6            | Interrupt Polarity Register       | 0 x 0000                                     |

| GPIOB_IPR        | \$7            | Interrupt Pending Register        | 0 x 0000                                     |

| GPIOB_IESR       | \$8            | Interrupt Edge-Sensitive Register | 0 x 0000                                     |

| GPIOB_PPMODE     | \$9            | Push-Pull Mode Register           | 0 x 00FF                                     |

| GPIOB_RAWDATA    | \$A            | Raw Data Input Register           | —                                            |

### Table 4-31 GPIOC Registers Address Map (GPIOC\_BASE = \$00 F310)

| Register Acronym | Address Offset | Register Description       | Reset Value |

|------------------|----------------|----------------------------|-------------|

| GPIOC_PUR        | \$0            | Pull-up Enable Register    | 0 x 07FF    |

| GPIOC_DR         | \$1            | Data Register              | 0 x 0000    |

| GPIOC_DDR        | \$2            | Data Direction Register    | 0 x 0000    |

| GPIOC_PER        | \$3            | Peripheral Enable Register | 0 x 07FF    |

| Register Acronym | Address Offset | Register Description                             |

|------------------|----------------|--------------------------------------------------|

| SIM_CONTROL      | \$0            | Control Register                                 |

| SIM_RSTSTS       | \$1            | Reset Status Register                            |

| SIM_SCR0         | \$2            | Software Control Register 0                      |

| SIM_SCR1         | \$3            | Software Control Register 1                      |

| SIM_SCR2         | \$4            | Software Control Register 2                      |

| SIM_SCR3         | \$5            | Software Control Register 3                      |

| SIM_MSH_ID       | \$6            | Most Significant Half JTAG ID                    |

| SIM_LSH_ID       | \$7            | Least Significant Half JTAG ID                   |

| SIM_PUDR         | \$8            | Pull-up Disable Register                         |

|                  |                | Reserved                                         |

| SIM_CLKOSR       | \$A            | Clock Out Select Register                        |

| SIM_GPS          | \$B            | Quad Decoder 1 / Timer B / SPI 1 Select Register |

| SIM_PCE          | \$C            | Peripheral Clock Enable Register                 |

| SIM_ISALH        | \$D            | I/O Short Address Location High Register         |

| SIM_ISALL        | \$E            | I/O Short Address Location Low Register          |

#### Table 4-35 System Integration Module Registers Address Map (SIM\_BASE = \$00 F350)

#### Table 4-36 Power Supervisor Registers Address Map (LVI\_BASE = \$00 F360)

| Register Acronym | Address Offset | Register Description |

|------------------|----------------|----------------------|

| LVI_CONTROL      | \$0            | Control Register     |

| LVI_STATUS       | \$1            | Status Register      |

#### Table 4-37 Flash Module Registers Address Map (FM\_BASE = \$00 F400)

| Register Acronym | Address Offset | Register Description        |  |  |  |

|------------------|----------------|-----------------------------|--|--|--|

| FMCLKD           | \$0            | Clock Divider Register      |  |  |  |

| FMMCR            | \$1            | Module Control Register     |  |  |  |

|                  |                | Reserved                    |  |  |  |

| FMSECH           | \$3            | Security High Half Register |  |  |  |

| FMSECL           | \$4            | Security Low Half Register  |  |  |  |

- Programmable priority levels for each IRQ

- Two programmable Fast Interrupts

- Notification to SIM module to restart clocks out of Wait and Stop modes

- Drives initial address on the address bus after reset

For further information, see **Table 4-5**, Interrupt Vector Table Contents.

# 5.3 Functional Description

The Interrupt Controller is a slave on the IPBus. It contains registers allowing each of the 82 interrupt sources to be set to one of four priority levels, excluding certain interrupts of fixed priority. Next, all of the interrupt requests of a given level are priority encoded to determine the lowest numerical value of the active interrupt requests for that level. Within a given priority level, zero is the highest priority, while number 81 is the lowest.

## 5.3.1 Normal Interrupt Handling

Once the ITCN has determined that an interrupt is to be serviced and which interrupt has the highest priority, an interrupt vector address is generated. Normal interrupt handling concatenates the VBA and the vector number to determine the vector address. In this way, an offset is generated into the vector table for each interrupt.

## 5.3.2 Interrupt Nesting

Interrupt exceptions may be nested to allow an IRQ of higher priority than the current exception to be serviced. The following tables define the nesting requirements for each priority level.

| SR[9] <sup>1</sup> | SR[8] <sup>1</sup> | Permitted Exceptions  | Masked Exceptions  |

|--------------------|--------------------|-----------------------|--------------------|

| 0                  | 0                  | Priorities 0, 1, 2, 3 | None               |

| 0                  | 1                  | Priorities 1, 2, 3    | Priority 0         |

| 1                  | 0                  | Priorities 2, 3       | Priorities 0, 1    |

| 1                  | 1                  | Priority 3            | Priorities 0, 1, 2 |

Table 5-1 Interrupt Mask Bit Definition

1. Core status register bits indicating current interrupt mask within the core.

#### **Table 5-2 Interrupt Priority Encoding**

| IPIC_LEVEL[1:0] <sup>1</sup> | Current Interrupt<br>Priority Level | Required Nested<br>Exception Priority |

|------------------------------|-------------------------------------|---------------------------------------|

| 00                           | No Interrupt or SWILP               | Priorities 0, 1, 2, 3                 |

| 01                           | Priority 0                          | Priorities 1, 2, 3                    |

| 10                           | Priority 1                          | Priorities 2, 3                       |

| 11                           | Priorities 2 or 3                   | Priority 3                            |

| Add.<br>Offset | Register<br>Name |        | 15     | 14        | 13     | 12        | 11   | 10          | 9      | 8                 | 7         | 6       | 5                                         | 4          | 3             | 2                   | 1         | 0                    |

|----------------|------------------|--------|--------|-----------|--------|-----------|------|-------------|--------|-------------------|-----------|---------|-------------------------------------------|------------|---------------|---------------------|-----------|----------------------|

| \$0            | IPR0             | R<br>W | 0      | 0         | BKPT_  | U0 IPL    | STPC | NT IPL      | 0      | 0                 | 0         | 0       | 0                                         | 0          | 0             | 0                   | 0         | 0                    |

| \$1            | IPR1             | R<br>W | 0      | 0         | 0      | 0         | 0    | 0           | 0      | 0                 | 0         | 0       | RX_RE                                     | G IPL      | TX_REG IPL    |                     | TRBUF IPL |                      |

| \$2            | IPR2             | R      | FMCE   | BE IPL    | FMC    | C IPL     | FMEF | rr ipl      | LOC    | K IPL             | LVI       | IPL     | 0                                         | 0 IRQB IPL |               |                     | IRQA IPL  |                      |

| \$3            | IPR3             | R<br>W |        | IOD<br>PL |        | IOE<br>PL |      | IOF         | FCMSG  | BUF IPL           | FCWK      | UP IPL  | FCERF                                     | I<br>R IPL | FCBO          | FF IPL              | 0         | 0                    |

| \$4            | IPR4             | R      | SPI0_F | RCV IPL   | SPI1_X | MIT IPL   |      | _RCV<br>PL  | 0      | 0                 | 0         | 0       | GPIC<br>IPL                               |            |               | IOB<br>PL           |           | PIOC<br>PL           |

| \$5            | IPR5             | R<br>W | DEC1_> | (IRQ IPL  | DEC1_H | HRQ IPL   |      | _RCV<br>PL  | SCI1_R | ERR IPL           | 0         | 0       | SCI1_TI                                   | DL IPL     | SCI1_X        | MIT IPL             | SPI0_2    | KMIT IPL             |

| \$6            | IPR6             | R<br>W | TMR    | C0 IPL    | TMR    | 03 IPL    | TMR  | D2 IPL      | TMR    | D1 IPL            | TMR       | D0 IPL  | 0                                         | 0          | DEC0_>        | (IRQ IPL            | DEC0_     | HIRQ IPL             |

| \$7            | IPR7             | R<br>W | TMR    | A0 IPL    | TMRE   | 33 IPL    | TMRE | 32 IPL      | TMRE   | 31 IPL            | TMRE      | 30 IPL  | TMRC                                      | B IPL      | TMR           | C2 IPL              | TMR       | C1 IPL               |

| \$8            | IPR8             | R<br>W | SCI0_F | RCV IPL   | SCI0_R | ERR IPL   | 0    | 0           | SCI0_T | IDL IPL           | SCI0_X    | MIT IPL | TMRAS                                     | 3 IPL      | TMR           | A2 IPL              | TMR       | A1 IPL               |

| \$9            | IPR9             | R<br>W | PWMA   | A F IPL   | PWME   | 3 F IPL   |      | IA_RL<br>PL | PWMB   | _RL IPL           | ADCA_     | _ZC IPL | ABCB_Z                                    | CIPL       | ADCA_         | CC IPL              | ADCB      | _CC IPL              |

| \$A            | VBA              | R<br>W | 0      | 0         | 0      |           |      |             |        |                   | VECTO     | R BASE  | ADDRESS                                   |            |               |                     |           |                      |

| \$В            | VBA0             | R<br>W | 0      | 0         | 0      | 0         | 0    | 0           | 0      | 0                 | 0         |         | FAST INTERRUPT 0                          |            |               |                     |           |                      |

| \$C            | FIVAL0           | R<br>W |        |           |        |           |      |             |        | FAST IN           |           |         |                                           |            |               |                     |           |                      |

| \$D            | FIVAH0           | R<br>W | 0      | 0         | 0      | 0         | 0    | 0           | 0      | 0                 | 0         | 0       | 0 FAST INTERRUPT 0<br>VECTOR ADDRESS HIGH |            |               | н                   |           |                      |

| \$E            | FIM1             | R<br>W | 0      | 0         | 0      | 0         | 0    | 0           | 0      | 0                 | 0         |         |                                           | FAST       | INTERR        | UPT 1               |           |                      |

| \$F            | FIVAL1           | R<br>W |        |           |        |           |      | •           |        | FAST IN<br>CTOR A |           |         |                                           |            |               |                     |           |                      |

| \$10           | FIVAH1           | R<br>W | 0      | 0         | 0      | 0         | 0    | 0           | 0      | 0                 | 0         | 0       | 0                                         |            |               | r interr<br>R addre |           | Н                    |

| \$11           | IRQP0            | R<br>W |        |           |        |           |      |             | PE     | NDING ['          | 16:2]     |         |                                           |            |               |                     |           | 1                    |

| \$12           | IRQP1            | R<br>W |        |           |        |           |      |             |        | PENDI             | NG [32:1] | 7]      |                                           |            |               |                     |           |                      |

| \$13           | IRQP2            | R<br>W |        |           |        |           |      |             |        | PENDI             | NG [48:3: | 3]      |                                           |            |               |                     |           |                      |

| \$14           | IRQP3            | R<br>W |        |           |        |           |      |             |        | PENDI             | NG [64:49 | 9]      |                                           |            |               |                     |           |                      |

| \$15           | IRQP4            | R<br>W |        |           |        |           |      |             |        | PENDI             | NG [80:6  | 5]      |                                           |            |               |                     |           |                      |

| \$16           | IRQP5            | R      | 1      | 1         | 1      | 1         | 1    | 1           | 1      | 1                 | 1         | 1       | 1                                         | 1          | 1             | 1                   | 1         | PEND-<br>ING<br>[81] |

|                | Reserved         | W      |        |           |        |           |      |             |        |                   |           |         |                                           |            |               |                     |           |                      |

| \$1D           | ICTL             | R      | INT    | IF        | PIC    |           |      |             | VAB    |                   |           |         | INT_DIS                                   | 1          | IRQB<br>STATE | IRQA<br>STATE       | IRQB      | IRQA                 |

|                |                  | W      |        |           |        |           |      |             |        |                   |           |         |                                           |            |               |                     | EDG       | EDG                  |

|                |                  |        |        | = Reserv  | ved    |           |      |             |        |                   |           |         |                                           |            |               |                     |           |                      |

## 5.6.5 Interrupt Priority Register 4 (IPR4)

| Base + \$4 | 15   | 14   | 13    | 12   | 11    | 10   | 9 | 8 | 7 | 6 | 5  | 4   | 3  | 2   | 1   | 0   |

|------------|------|------|-------|------|-------|------|---|---|---|---|----|-----|----|-----|-----|-----|

| Read       | SPI0 | _RCV | SPI1_ | XMIT | SPI1_ | _RCV | 0 | 0 | 0 | 0 | GP | IOA | GP | IOB | GPI | IOC |

| Write      | IF   | ۲L   | IF    | ۲L   | IF    | Ľ    |   |   |   |   | IF | ۲L  | IF | ۲L  | IF  | ۲L  |

| RESET      | 0    | 0    | 0     | 0    | 0     | 0    | 0 | 0 | 0 | 0 | 0  | 0   | 0  | 0   | 0   | 0   |

Figure 5-7 Interrupt Priority Register 4 (IPR4)

## 5.6.5.1 SPI0 Receiver Full Interrupt Priority Level (SPI0\_RCV IPL)— Bits 15–14

This field is used to set the interrupt priority level for IRQs. This IRQ is limited to priorities 0 through 2. They are disabled by default.

- 00 = IRQ disabled (default)

- 01 = IRQ is priority level 0

- 10 = IRQ is priority level 1

- 11 = IRQ is priority level 2

## 5.6.5.2 SPI1 Transmit Empty Interrupt Priority Level (SPI1\_XMIT IPL)— Bits 13–12

This field is used to set the interrupt priority level for IRQs. This IRQ is limited to priorities 0 through 2. They are disabled by default.

- 00 = IRQ disabled (default)

- 01 = IRQ is priority level 0

- 10 = IRQ is priority level 1

- 11 = IRQ is priority level 2

## 5.6.5.3 SPI1 Receiver Full Interrupt Priority Level (SPI1\_RCV IPL)— Bits 11–10

This field is used to set the interrupt priority level for IRQs. This IRQ is limited to priorities 0 through 2. They are disabled by default.

- 00 = IRQ disabled (default)

- 01 = IRQ is priority level 0

- 10 = IRQ is priority level 1

- 10 = IRQ is priority level 1

- 11 = IRQ is priority level 2

## 5.6.8.5 Timer B, Channel 0 Interrupt Priority Level (TMRB0 IPL)—Bits 7–6

This field is used to set the interrupt priority level for IRQs. This IRQ is limited to priorities 0 through 2. They are disabled by default.

- 00 = IRQ disabled (default)

- 01 = IRQ is priority level 0

- 10 = IRQ is priority level 1

- 11 = IRQ is priority level 2

## 5.6.8.6 Timer C, Channel 3 Interrupt Priority Level (TMRC3 IPL)—Bits 5–4

This field is used to set the interrupt priority level for IRQs. This IRQ is limited to priorities 0 through 2. They are disabled by default.

- 00 = IRQ disabled (default)

- 01 = IRQ is priority level 0

- 10 = IRQ is priority level 1

- 11 = IRQ is priority level 2

## 5.6.8.7 Timer C, Channel 2 Interrupt Priority Level (TMRC2 IPL)—Bits 3–2

This field is used to set the interrupt priority level for IRQs. This IRQ is limited to priorities 0 through 2. They are disabled by default.

- 00 = IRQ disabled (default)

- 01 = IRQ is priority level 0

- 10 = IRQ is priority level 1

- 11 = IRQ is priority level 2

## 5.6.8.8 Timer C, Channel 1 Interrupt Priority Level (TMRC1 IPL)—Bits 1–0

This field is used to set the interrupt priority level for IRQs. This IRQ is limited to priorities 0 through 2. They are disabled by default.

- 00 = IRQ disabled (default)

- 01 = IRQ is priority level 0

- 10 = IRQ is priority level 1

- 11 = IRQ is priority level 2

# 6.5 Register Descriptions

| Table | 6-1 | SIM | Reg | isters |

|-------|-----|-----|-----|--------|

|       |     |     |     | F350)  |

| Address Offset | Address Acronym | Register Name                            | Section Location |

|----------------|-----------------|------------------------------------------|------------------|

| Base + \$0     | SIM_CONTROL     | Control Register                         | 6.5.1            |

| Base + \$1     | SIM_RSTSTS      | Reset Status Register                    | 6.5.2            |

| Base + \$2     | SIM_SCR0        | Software Control Register 0              | 6.5.3            |

| Base + \$3     | SIM_SCR1        | Software Control Register 1              | 6.5.3            |

| Base + \$4     | SIM_SCR2        | Software Control Register 2              | 6.5.3            |

| Base + \$5     | SIM_SCR3        | Software Control Register 3              | 6.5.3            |

| Base + \$6     | SIM_MSH_ID      | Most Significant Half of JTAG ID         | 6.5.4            |

| Base + \$7     | SIM_LSH_ID      | Least Significant Half of JTAG ID        | 6.5.5            |

| Base + \$8     | SIM_PUDR        | Pull-up Disable Register                 | 6.5.6            |

|                |                 | Reserved                                 |                  |

| Base + \$A     | SIM_CLKOSR      | CLKO Select Register                     | 6.5.7            |

| Base + \$B     | SIM_GPS         | GPIO Peripheral Select Register          | 6.5.7            |

| Base + \$C     | SIM_PCE         | Peripheral Clock Enable Register         | 6.5.8            |

| Base + \$D     | SIM_ISALH       | I/O Short Address Location High Register | 6.5.9            |

| Base + \$E     | SIM_ISALL       | I/O Short Address Location Low Register  | 6.5.10           |

| Add.<br>Offset | Register<br>Name |         | 15  | 14   | 13   | 12   | 11    | 10   | 9     | 8    | 7     | 6    | 5      | 4    | 3    | 2      | 1     | 0      |

|----------------|------------------|---------|-----|------|------|------|-------|------|-------|------|-------|------|--------|------|------|--------|-------|--------|

| \$0            | SIM_             | R       | 0   | 0    | 0    | 0    | 0     | 0    | 0     | 0    | 0     | EMI_ | ONCE   | SW   |      | OP_    |       | IT_    |

| ΨŪ             | CONTROL          | W       |     |      |      |      |       |      |       |      |       | MODE | EBL    | RST  | DIS  | ABLE   | DISA  | ABLE   |

| \$1            | SIM_             | R       | 0   | 0    | 0    | 0    | 0     | 0    | 0     | 0    | 0     | 0    | SWR    | COPR | EXTR | POR    | 0     | 0      |

|                | RSTSTS           | W       |     |      |      |      |       |      |       |      |       |      |        |      |      |        |       |        |

| \$2            | SIM_SCR0         | R       |     |      |      |      |       |      |       | FIE  | LD    |      |        |      |      |        |       |        |

|                |                  | N<br>N  |     |      |      |      |       |      |       |      |       |      |        |      |      |        |       |        |

| \$3            | SIM_SCR1         | R<br>W  |     |      |      |      |       |      |       | FIE  | LD    |      |        |      |      |        |       |        |

|                |                  | R       |     |      |      |      |       |      |       |      |       |      |        |      |      |        |       |        |

| \$4            | SIM_SCR2         | W       |     |      |      |      |       |      |       | FIE  | LD    |      |        |      |      |        |       |        |

|                |                  | R       |     |      |      |      |       |      |       |      |       |      |        |      |      |        |       |        |

| \$5            | SIM_SCR3         | W       |     |      |      |      |       |      |       | FIE  | LD    |      |        |      |      |        |       |        |

| <b>*</b> C     | SIM_MSH_         | R       | 0   | 0    | 0    | 0    | 0     | 0    | 0     | 1    | 1     | 1    | 1      | 1    | 0    | 1      | 0     | 0      |

| \$6            | ID               | W       |     |      |      |      |       |      |       |      |       |      |        |      |      |        |       |        |

| \$7            | SIM_LSH_ID       | R       | 0   | 1    | 0    | 0    | 0     | 0    | 0     | 0    | 0     | 0    | 0      | 1    | 1    | 1      | 0     | 1      |

| Ψï             |                  | W       |     |      |      |      |       |      |       |      |       |      |        |      |      |        |       |        |

| \$8            | SIM_PUDR         | R       | 0   | PWMA | CAN  | EMI_ | RESET | IRQ  | хвоот | PWMB | PWMA  | 0    | CTRL   | 0    | JTAG | 0      | 0     | 0      |

|                | _                | W       | 0   | 1    | -    | MODE | -     |      |       |      | 0     |      | _      |      |      |        |       |        |

|                | Reserved         |         | -   |      |      | -    | -     | -    |       |      |       |      |        |      |      |        |       |        |

| \$A            | SIM_<br>CLKOSR   | R<br>W  | 0   | 0    | 0    | 0    | 0     | 0    | A23   | A22  | A21   | A20  | CLKDIS |      | (    | CLKOSE | L     |        |

|                | CEROSK           | vv<br>R | 0   | 0    | 0    | 0    | 0     | 0    | 0     | 0    | 0     | 0    | 0      | 0    |      |        | 1     |        |

| \$B            | SIM_GPS          | W       | 0   | 0    | 0    | 0    | 0     | 0    | 0     | 0    | 0     | 0    | 0      | 0    | C3   | C2     | C1    | C0     |

|                |                  | R       |     |      |      |      |       |      |       |      |       |      |        |      |      |        | PWM   | PWM    |

| \$C            | SIM_PCE          | W       | EMI | ADCB | ADCA | CAN  | DEC1  | DEC0 | TMRD  | TMRC | TMRB  | TMRA | SCI1   | SCI0 | SPI1 | SPI0   | B     | A      |

| <b>*</b> D     | 0114 104111      | R       | 1   | 1    | 1    | 1    | 1     | 1    | 1     | 1    | 1     | 1    | 1      | 1    | 1    | 1      |       |        |

| φD             | \$D SIM_ISALH W  |         |     |      |      |      |       |      |       |      |       |      |        |      |      |        | ISAL[ | 23:22] |

| \$E            | SIM_ISALL        | R       |     |      |      |      |       |      |       | ISAL | 21.61 |      |        |      |      |        |       |        |

| φ⊑             | SINI_ISALL       | W       |     |      |      |      |       |      |       | ISAL | 21.0] |      |        |      |      |        |       |        |

= Reserved

### Figure 6-2 SIM Register Map Summary

## 6.5.1 SIM Control Register (SIM\_CONTROL)

| Base + \$0 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6    | 5    | 4   | 3    | 2   | 1    | 0   |

|------------|----|----|----|----|----|----|---|---|---|------|------|-----|------|-----|------|-----|

| Read       | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | EMI_ | ONCE | SW  | STO  | DP_ | WA   | IT_ |

| Write      |    |    |    |    |    |    |   |   |   | MODE | EBL  | RST | DISA | BLE | DISA | BLE |

| RESET      | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0    | 0    | 0   | 0    | 0   | 0    | 0   |

## Figure 6-3 SIM Control Register (SIM\_CONTROL)

## 6.5.1.1 Reserved—Bits 15–7

This bit field is reserved or not implemented. It is read as 0 and cannot be modified by writing.

| Base + \$2 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8    | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|------------|----|----|----|----|----|----|---|------|---|---|---|---|---|---|---|---|

| Read       |    |    |    |    |    |    |   | FIEL |   |   |   |   |   |   |   |   |

| Write      |    |    |    |    |    |    |   | FIEL | D |   |   |   |   |   |   |   |

| POR        | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0    | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

Figure 6-5 SIM Software Control Register 0 (SIM\_SCR0)

## 6.5.3.1 Software Control Data 1 (FIELD)—Bits 15–0

This register is reset only by the Power-On Reset (POR). It has no part-specific functionality and is intended for use by a software developer to contain data that will be unaffected by the other reset sources (RESET pin, software reset, and COP reset).

## 6.5.4 Most Significant Half of JTAG ID (SIM\_MSH\_ID)

This read-only register displays the most significant half of the JTAG ID for the chip. This register reads \$01F4.

| Base + \$6 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|------------|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

| Read       | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 0 | 0 |

| Write      |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| RESET      | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 0 | 0 |

### Figure 6-6 Most Significant Half of JTAG ID (SIM\_MSH\_ID)

## 6.5.5 Least Significant Half of JTAG ID (SIM\_LSH\_ID)

This read-only register displays the least significant half of the JTAG ID for the chip. This register reads \$601D.

| Base + \$7 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|------------|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

| Read       | 0  | 1  | 1  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 1 |

| Write      |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| RESET      | 0  | 1  | 1  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 1 |

Figure 6-7 Least Significant Half of JTAG ID (SIM\_LSH\_ID)

**Note:** Once the lockout recovery sequence has completed, the user must reset both the JTAG TAP controller (by asserting TRST) and the device (by asserting external chip reset) to return to normal unsecured operation.

## 7.2.4 Product Analysis

The recommended method of unsecuring a programmed device for product analysis of field failures is via the backdoor key access. The customer would need to supply Technical Support with the backdoor key and the protocol to access the backdoor routine in the Flash. Additionally, the KEYEN bit that allows backdoor key access must be set.

An alternative method for performing analysis on a secured hybrid controller would be to mass-erase and reprogram the Flash with the original code, but modify the security bytes.

To insure that a customer does not inadvertently lock himself out of the device during programming, it is recommended that he program the backdoor access key first, his application code second, and the security bytes within the FM configuration field last.

# Part 8 General Purpose Input/Output (GPIO)

# 8.1 Introduction

This section is intended to supplement the GPIO information found in the **56F8300 Peripheral User Manual** and contains only chip-specific information. This information supercedes the generic information in the **56F8300 Peripheral User Manual**.

# 8.2 Memory Maps

The width of the GPIO port defines how many bits are implemented in each of the GPIO registers. Based on this and the default function of each of the GPIO pins, the reset values of the GPIOx\_PUR and GPIOx\_PER registers change from port to port. Tables 4-29 through 4-34 define the actual reset values of these registers.

# 8.3 Configuration

There are six GPIO ports defined on the 56F8356/56F8156. The width of each port and the associated peripheral function is shown in **Table 8-1** and **Table 8-2**. The specific mapping of GPIO port pins is shown in **Table 8-3**.

# 10.10 Serial Peripheral Interface (SPI) Timing

| Characteristic                                                          | Symbol           | Min        | Max          | Unit     | See Figure                    |

|-------------------------------------------------------------------------|------------------|------------|--------------|----------|-------------------------------|

| Cycle time<br>Master<br>Slave                                           | t <sub>C</sub>   | 50<br>50   |              | ns<br>ns | 10-10, 10-11,<br>10-12, 10-13 |

| Enable lead time<br>Master<br>Slave                                     | t <sub>ELD</sub> | <br>25     | _            | ns<br>ns | 10-13                         |

| Enable lag time<br>Master<br>Slave                                      | t <sub>ELG</sub> | <br>100    | _            | ns<br>ns | 10-13                         |

| Clock (SCK) high time<br>Master<br>Slave                                | t <sub>CH</sub>  | 17.6<br>25 | _            | ns<br>ns | 10-10, 10-11,<br>10-12, 10-13 |

| Clock (SCK) low time<br>Master<br>Slave                                 | t <sub>CL</sub>  | 24.1<br>25 | _            | ns<br>ns | 10-13                         |

| Data set-up time required for inputs<br>Master<br>Slave                 | t <sub>DS</sub>  | 20<br>0    |              | ns<br>ns | 10-10, 10-11,<br>10-12, 10-13 |

| Data hold time required for inputs<br>Master<br>Slave                   | t <sub>DH</sub>  | 0<br>2     | _            | ns<br>ns | 10-10, 10-11,<br>10-12, 10-13 |

| Access time (time to data active from<br>high-impedance state)<br>Slave | t <sub>A</sub>   | 4.8        | 15           | ns       | 10-13                         |

| Disable time (hold time to high-impedance state)<br>Slave               | t <sub>D</sub>   | 3.7        | 15.2         | ns       | 10-13                         |

| Data Valid for outputs<br>Master<br>Slave (after enable edge)           | t <sub>DV</sub>  | _          | 4.5<br>20.4  | ns<br>ns | 10-10, 10-11,<br>10-12, 10-13 |

| Data invalid<br>Master<br>Slave                                         | t <sub>DI</sub>  | 0<br>0     | _            | ns<br>ns | 10-10, 10-11,<br>10-12        |

| Rise time<br>Master<br>Slave                                            | t <sub>R</sub>   |            | 11.5<br>10.0 | ns<br>ns | 10-10, 10-11,<br>10-12, 10-13 |

## Table 10-18 SPI Timing<sup>1</sup>

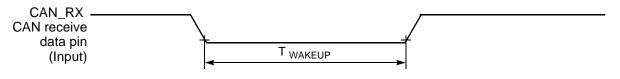

Figure 10-18 Bus Wake Up Detection

# 10.15 JTAG Timing

| Symbol            | Min                                                                                                                               | Мах                                                                                                                                                                          | Unit                                                                                                                                                                                                                                                                                              | See Figure                                                                                                                                                       |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f <sub>OP</sub>   | DC                                                                                                                                | SYS_CLK/8                                                                                                                                                                    | MHz                                                                                                                                                                                                                                                                                               | 10-19                                                                                                                                                            |

| f <sub>OP</sub>   | DC                                                                                                                                | SYS_CLK/4                                                                                                                                                                    | MHz                                                                                                                                                                                                                                                                                               | 10-19                                                                                                                                                            |

| t <sub>PW</sub>   | 50                                                                                                                                | _                                                                                                                                                                            | ns                                                                                                                                                                                                                                                                                                | 10-19                                                                                                                                                            |

| t <sub>DS</sub>   | 5                                                                                                                                 | _                                                                                                                                                                            | ns                                                                                                                                                                                                                                                                                                | 10-20                                                                                                                                                            |

| t <sub>DH</sub>   | 5                                                                                                                                 | _                                                                                                                                                                            | ns                                                                                                                                                                                                                                                                                                | 10-20                                                                                                                                                            |

| t <sub>DV</sub>   |                                                                                                                                   | 30                                                                                                                                                                           | ns                                                                                                                                                                                                                                                                                                | 10-20                                                                                                                                                            |

| t <sub>TS</sub>   | —                                                                                                                                 | 30                                                                                                                                                                           | ns                                                                                                                                                                                                                                                                                                | 10-20                                                                                                                                                            |

| t <sub>TRST</sub> | 2T <sup>2</sup>                                                                                                                   | _                                                                                                                                                                            | ns                                                                                                                                                                                                                                                                                                | 10-21                                                                                                                                                            |

|                   | f <sub>OP</sub><br>f <sub>OP</sub><br>t <sub>PW</sub><br>t <sub>DS</sub><br>t <sub>DH</sub><br>t <sub>DV</sub><br>t <sub>TS</sub> | $\begin{array}{c c} f_{OP} & DC \\ \hline f_{OP} & DC \\ \hline t_{PW} & 50 \\ \hline t_{DS} & 5 \\ \hline t_{DH} & 5 \\ \hline t_{DV} & - \\ \hline t_{TS} & - \end{array}$ | $\begin{array}{c c c c c c c c c c } \hline f_{OP} & DC & SYS_CLK/8 \\ \hline f_{OP} & DC & SYS_CLK/4 \\ \hline f_{PW} & 50 & \\ \hline t_{PW} & 50 & \\ \hline t_{DS} & 5 & \\ \hline t_{DH} & 5 & \\ \hline t_{DH} & 5 & \\ \hline t_{DV} & & 30 \\ \hline t_{TS} & & 30 \\ \hline \end{array}$ | $f_{OP}$ DC SYS_CLK/8 MHz $f_{OP}$ DC SYS_CLK/4 MHz $f_{OP}$ DC SYS_CLK/4 MHz $t_{PW}$ 50 — ns $t_{DS}$ 5 — ns $t_{DH}$ 5 — ns $t_{DV}$ — 30 ns $t_{TS}$ — 30 ns |

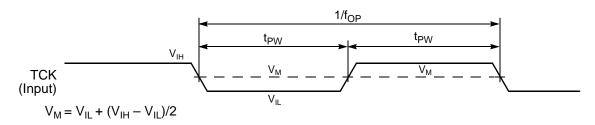

### Table 10-23 JTAG Timing

1. TCK frequency of operation must be less than 1/8 the processor rate.

2. T = processor clock period (nominally 1/60MHz)

Figure 10-19 Test Clock Input Timing Diagram

where:

- $T_T$  = Thermocouple temperature on top of package (<sup>o</sup>C)

- $\Psi_{JT}$  = Thermal characterization parameter (<sup>o</sup>C)/W

- $P_D$  = Power dissipation in package (W)

The thermal characterization parameter is measured per JESD51-2 specification using a 40-gauge type T thermocouple epoxied to the top center of the package case. The thermocouple should be positioned so that the thermocouple junction rests on the package. A small amount of epoxy is placed over the thermocouple junction and over about 1mm of wire extending from the junction. The thermocouple wire is placed flat against the package case to avoid measurement errors caused by cooling effects of the thermocouple wire.

When heat sink is used, the junction temperature is determined from a thermocouple inserted at the interface between the case of the package and the interface material. A clearance slot or hole is normally required in the heat sink. Minimizing the size of the clearance is important to minimize the change in thermal performance caused by removing part of the thermal interface to the heat sink. Because of the experimental difficulties with this technique, many engineers measure the heat sink temperature and then back-calculate the case temperature using a separate measurement of the thermal resistance of the interface. From this case temperature, the junction temperature is determined from the junction-to-case thermal resistance.

# **12.2 Electrical Design Considerations**

# CAUTION This device contains protective circuitry to guard against damage due to high static voltage or electrical fields. However, normal precautions are advised to avoid application of any voltages higher than maximum-rated voltages to this high-impedance circuit. Reliability of operation is enhanced if unused inputs are tied to an appropriate voltage level.

Use the following list of considerations to assure correct device operation:

- Provide a low-impedance path from the board power supply to each  $V_{DD}$  pin on the device, and from the board ground to each  $V_{SS}$  (GND) pin

- The minimum bypass requirement is to place six 0.01–0.1 $\mu$ F capacitors positioned as close as possible to the package supply pins. The recommended bypass configuration is to place one bypass capacitor on each of the V<sub>DD</sub>/V<sub>SS</sub> pairs, including V<sub>DDA</sub>/V<sub>SSA</sub>. Ceramic and tantalum capacitors tend to provide better performance tolerances.