# E·XFL Renesas Electronics America Inc - <u>R5S72621W144FP#U0 Datasheet</u>

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Last Time Buy                                                                      |

|----------------------------|------------------------------------------------------------------------------------|

| Core Processor             | SH2A-FPU                                                                           |

| Core Size                  | 32-Bit Single-Core                                                                 |

| Speed                      | 144MHz                                                                             |

| Connectivity               | CANbus, I <sup>2</sup> C, SCI, SD, SIO, SPI, USB                                   |

| Peripherals                | DMA, POR, PWM, WDT                                                                 |

| Number of I/O              | 89                                                                                 |

| Program Memory Size        | -                                                                                  |

| Program Memory Type        | ROMIess                                                                            |

| EEPROM Size                | -                                                                                  |

| RAM Size                   | 1M x 8                                                                             |

| Voltage - Supply (Vcc/Vdd) | 1.1V ~ 3.6V                                                                        |

| Data Converters            | A/D 4x10b                                                                          |

| Oscillator Type            | External                                                                           |

| Operating Temperature      | -20°C ~ 85°C (TA)                                                                  |

| Mounting Type              | Surface Mount                                                                      |

| Package / Case             | 176-LQFP                                                                           |

| Supplier Device Package    | 176-LFQFP (24x24)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r5s72621w144fp-u0 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|       | 9.5.1    | Endian/Access Size and Data Alignment                      | 291 |

|-------|----------|------------------------------------------------------------|-----|

|       | 9.5.2    | Normal Space Interface                                     |     |

|       | 9.5.3    | Access Wait Control                                        | 298 |

|       | 9.5.4    | CSn Assert Period Expansion                                | 300 |

|       | 9.5.5    | MPX-I/O Interface                                          | 301 |

|       | 9.5.6    | SDRAM Interface                                            | 306 |

|       | 9.5.7    | Burst ROM (Clocked Asynchronous) Interface                 | 342 |

|       | 9.5.8    | SRAM Interface with Byte Selection                         | 344 |

|       | 9.5.9    | PCMCIA Interface                                           | 348 |

|       | 9.5.10   | Burst ROM (Clocked Synchronous) Interface                  | 355 |

|       | 9.5.11   | Wait between Access Cycles                                 | 356 |

|       | 9.5.12   | Bus Arbitration                                            | 364 |

|       | 9.5.13   | Others                                                     | 366 |

| Secti | on 10 I  | Direct Memory Access Controller                            |     |

| 10.1  |          |                                                            |     |

| 10.2  |          | ıtput Pins                                                 |     |

| 10.3  | -        | Descriptions                                               |     |

|       | 10.3.1   | DMA Source Address Registers (SAR)                         |     |

|       | 10.3.2   | DMA Destination Address Registers (DAR)                    |     |

|       | 10.3.3   | DMA Transfer Count Registers (DMATCR)                      |     |

|       | 10.3.4   | DMA Channel Control Registers (CHCR)                       |     |

|       | 10.3.5   | DMA Reload Source Address Registers (RSAR)                 |     |

|       | 10.3.6   | DMA Reload Destination Address Registers (RDAR)            |     |

|       | 10.3.7   | DMA Reload Transfer Count Registers (RDMATCR)              |     |

|       | 10.3.8   | DMA Operation Register (DMAOR)                             |     |

|       | 10.3.9   | DMA Extension Resource Selectors 0 to 7 (DMARS0 to DMARS7) |     |

| 10.4  | Operatio | on                                                         | 408 |

|       | 10.4.1   | Transfer Flow                                              | 408 |

|       | 10.4.2   | DMA Transfer Requests                                      | 410 |

|       | 10.4.3   | Channel Priority                                           | 417 |

|       | 10.4.4   | DMA Transfer Types                                         | 417 |

|       | 10.4.5   | Number of Bus Cycles and DREQ Pin Sampling Timing          |     |

| 10.5  | Usage N  | lotes                                                      | 430 |

|       | 10.5.1   | Timing of DACK and TEND Outputs                            | 430 |

|       | 10.5.2   | Notes on Using Flag Bits                                   | 430 |

| Secti | on 11 I  | Multi-Function Timer Pulse Unit 2                          | 431 |

| 11.1  |          |                                                            |     |

| 11.2  |          | ıtput Pins                                                 |     |

|       |          | ±                                                          |     |

| Bit | Bit Name | Initial<br>Value | R/W | Description                                                                                                                               |

|-----|----------|------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | HIZCNT*  | 0                | R/W | High-Z Control                                                                                                                            |

|     |          |                  |     | Specifies the state in software standby mode, deep standby mode, or bus-released state for CKE, $\overline{RAS}$ , and $\overline{CAS}$ . |

|     |          |                  |     | 0: High impedance in software standby mode, deep standby mode, or bus-released state for CKE, RAS, and CAS.                               |

|     |          |                  |     | 1: Driven in software standby mode, deep standby mode, or bus-released state for CKE, RAS, and CAS.                                       |

Note: \* For High-Z control of CKIO, see section 5, Clock Pulse Generator.

#### 9.4.2 CSn Space Bus Control Register (CSnBCR) (n = 0 to 6)

CSnBCR is a 32-bit readable/writable register that specifies the memory connected to each space, the number of idle cycles between bus cycles, and the bus width.

Do not access external memory for the corresponding area until CSnBCR initial setting and pin setting are completed.

Idle cycles may be inserted even when they are not specified. For details, see section 9.5.11, Wait between Access Cycles.

| Bit:                   | 31     | 30       | 29       | 28       | 27       | 26       | 25       | 24       | 23       | 22       | 21       | 20       | 19       | 18       | 17       | 16       |

|------------------------|--------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|

|                        | -      |          | IWW[2:0] |          | IV       | RWD[2:   | 0]       | IV       | VRWS[2:  | 0]       | IV       | VRRD[2:  | 0]       | IV       | VRRS[2:  | 0]       |

| Initial value:<br>R/W: | 0<br>R | 0<br>R/W | 1<br>R/W | 1<br>R/W |

| Bit:                   | 15     | 14       | 13       | 12       | 11       | 10       | 9        | 8        | 7        | 6        | 5        | 4        | 3        | 2        | 1        | 0        |

|                        | -      | Т        | TYPE[2:0 | ]        | ENDIAN   | BSZ      | [1:0]    | -        | -        | -        | -        | -        | -        | -        | -        | -        |

| Initial value:         | 0      | 0        | 0        | 0        | 0        | 1        | 0        | 0        | 0        | 0        | 0        | 0        | 0        | 0        | 0        | 0        |

| R/W:                   | R      | R/W      | R/W      | R/W      | R/W      | R/W      | R/W      | R        | R        | R        | R        | R        | R        | R        | R        | R        |

# (2) Operation when Error Occurs during Normal Mode Operation, and Operation is Restarted in PWM Mode 1

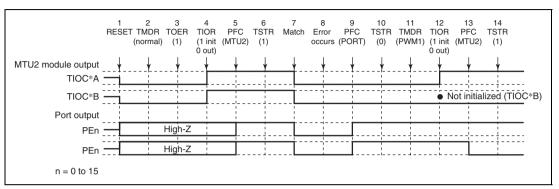

Figure 11.116 shows an explanatory diagram of the case where an error occurs in normal mode and operation is restarted in PWM mode 1 after re-setting.

# Figure 11.116 Error Occurrence in Normal Mode, Recovery in PWM Mode 1

1 to 10 are the same as in figure 11.115.

- 11. Set PWM mode 1.

- 12. Initialize the pins with TIOR. (In PWM mode 1, the TIOC\*B side is not initialized. If initialization is required, initialize in normal mode, and then switch to PWM mode 1.)

- 13. Set the multi-function timer pulse unit 2 output with the general I/O port.

- 14. Operation is restarted by TSTR.

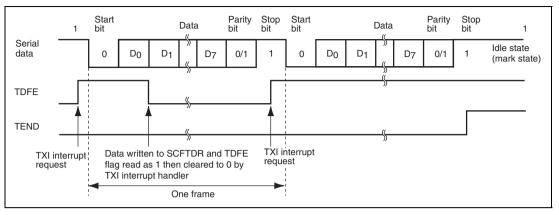

Figure 15.5 shows an example of the operation for transmission.

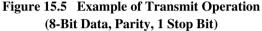

4. When modem control is enabled in channel 1 on the SH7262, and channels 1 and 3 on the SH7264, transmission can be stopped and restarted in accordance with the CTS input value. When CTS is set to 1, if transmission is in progress, the line goes to the mark state after transmission of one frame. When CTS is set to 0, the next transmit data is output starting from the start bit.

Figure 15.6 shows an example of the operation when modem control is used.

Figure 15.6 Example of Operation Using Modem Control (CTS)

# Section 16 Renesas Serial Peripheral Interface

This LSI includes two-channel Renesas serial peripheral interfaces.

This module is capable of full-duplex serial communication.

# 16.1 Features

This module has the following features.

• SPI transfer functions

Use of MOSI (master out/slave in), MISO (master in/slave out), SSL (slave select), and RSPCK (SPI clock) signals allow for serial communications through SPI operation (four-wire method).

Capable of serial communications in master/slave mode Supports mode fault error detection (only in SPI slave mode) Supports overrun error detection (only in SPI slave mode) Switching of the polarity of the serial transfer clock Switching of the clock phase of serial transfer

• Data format

MSB-first/LSB-first selectable

Transfer bit-length is selectable as 8, 16, or 32 bits.

• Bit rate

RSPCK can be divided by a maximum of 4096 in master mode RSPCK can be generated by dividing B\u00f6 by the on-chip baud rate generator. An externally input clock can be used as a serial clock.

Buffer configuration

8 bytes for transmission and 32 bytes for reception.

When this module recognises the end of the Arbitration field while receiving a message, it starts comparing the received identifier to the identifiers set in the Mailboxes, starting from Mailbox-31 down to Mailbox-0. It first checks the MBC if it is configured as a receive box, and reads LAFM, and reads the CAN-ID of Mailbox-31 (if configured as receive) to finally compare them to the received ID. If it does not match, the same check takes place at Mailbox-30 (if configured as receive). Once this module finds a matching identifier, it stores the number of Mailbox-[N] into an internal buffer, stops the search, and goes back to idle state, waiting for the EndOfFrame (EOF) to come. When the 6<sup>th</sup> bit of EOF is notified by the CAN Interface logic, the received message is written or abandoned, depending on the NMC bit. No modification of configuration during communication is allowed. Entering Halt Mode is one of ways to modify configuration. If it is written into the corresponding Mailbox, including the CAN-ID, i.e., there is a possibility that the CAN-ID is overwritten by a different CAN-ID of the received message due to the LAFM used. This also implies that, if the identifier of a received message matches to ID + LAFM of 2 or more Mailboxes, the higher numbered Mailbox will always store the relevant messages and the lower numbered Mailbox will never receive messages. Therefore, the settings of the identifiers and LAFMs need to be carefully selected.

With regards to the reception of data and remote frames described in the above flow diagram the clearing of the UMSR flag after the reading of IRR is to detect situations where a message is overwritten by a new incoming message stored in the same mailbox (if its NMC = 1) while the interrupt service routine is running. If during the final check of UMSR a overwrite condition is detected the message needs to be discarded and read again.

In case UMSR is set and the Mailbox is configured for overrun (NMC = 0) the message is still valid, however it is obsolete as it is not reflecting the latest message monitored on the CAN Bus.

Please access the full Mailbox content before clearing the related RXPR/RFPR flag.

Please note that in the case a received remote frame is overwritten by a data frame, both the remote frame receive interrupt (IRR2) and data frame received interrupt (IRR1) and also the Receive Flags (RXPR and RFPR) are set. In an analogous way, the overwriting of a data frame by a remote frame, leads to setting both IRR2 and IRR1.

When a message is received and stored into a Mailbox all the fields of the data not received are stored as zero. The same applies when a standard frame is received. The extended identifier part (EXTID[17:0]) is written as zero.

#### 22.7.8 Transmitter Channel 2 Status Register (TRCS)

The 30-bit register stores the channel status information to be transmitted. For each channel, channel status information per frame consists of 192 bits. Because necessary data covers only the 30 bits that are set in the following register, zeros continue to be sent after the transmission of the first 30 bits.

| Bit:           | 31 | 30   | 29     | 28     | 27      | 26   | 25     | 24 |

|----------------|----|------|--------|--------|---------|------|--------|----|

|                | -  | -    | CLAC   | C[1:0] |         | FS   | [3:0]  |    |

| Initial value: | -  | -    | 0      | 0      | 0       | 0    | 0      | 0  |

| R/W:           | W  | W    | W      | W      | W       | W    | W      | W  |

| Bit:           | 23 | 22   | 21     | 20     | 19      | 18   | 17     | 16 |

|                |    | CHNC | D[3:0] |        |         | SRCN | O[3:0] |    |

| Initial value: | 0  | 0    | 0      | 0      | 0       | 0    | 0      | 0  |

| R/W:           | W  | W    | W      | W      | W       | W    | W      | W  |

| Bit:           | 15 | 14   | 13     | 12     | 11      | 10   | 9      | 8  |

|                |    |      |        | CATC   | D[7:0]  |      |        |    |

| Initial value: | 0  | 0    | 0      | 0      | 0       | 0    | 0      | 0  |

| R/W:           | W  | W    | W      | W      | W       | W    | W      | W  |

| Bit:           | 7  | 6    | 5      | 4      | 3       | 2    | 1      | 0  |

|                | -  | -    |        | (      | CTL[4:0 | ]    |        | -  |

| Initial value: | 0  | 0    | 0      | 0      | 0       | 0    | 0      | 0  |

| R/W:           | W  | W    | W      | W      | W       | W    | W      | W  |

| Bit      | Bit Name  | Initial<br>Value | R/W | Description           |

|----------|-----------|------------------|-----|-----------------------|

| 31, 30   |           |                  | W   | Reserved              |

| 29, 28   | CLAC[1:0] | All 0            | W   | Clock Accuracy        |

|          |           |                  |     | 00: Level 2           |

|          |           |                  |     | 01: Level 1           |

|          |           |                  |     | 10: Level 3           |

|          |           |                  |     | 11: Reserved          |

| 27 to 24 | FS[3:0]   | All 0            | W   | Sample Frequency (FS) |

|          |           |                  |     | 0000: 44.1 kHz        |

|          |           |                  |     | 0010: 48 kHz          |

|          |           |                  |     | 0011: 32 kHz          |

| Bit Name         | Initial<br>Value | R/W                                | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------------|------------------|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BITEND           | 0                | R/W                                | Specifies treatment of the bit order of the input data from the serial sound interface.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                  |                  |                                    | When this bit is set to 1, the bits within each byte are rearranged to place them in reverse order, bit $0 \rightarrow$ bit 7 to bit $7 \rightarrow$ bit 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| BUFEND0<br>[1:0] | 01               | R/W                                | <ul> <li>These bits select whether to change the order of 16-bit units of data transferred from the serial sound interface or suppress the stream data. In the serial sound interface, either "padding mode" or "non-padding mode" is selectable. In non-padding mode, each 32 bits of data transferred from the serial sound interface are CD-ROM data. Since the CD-ROM decoder has two 16-bit input data registers, the order of the 16-bit data can be swapped within the 32 bits. On the other hand, in padding mode each 32 bits of data transferred from the serial sound interface includes padding. Since the padding is without meaning, it should be kept out of the input stream to the decoder. This suppression can be specified by the setting of this register.</li> <li>The CD-ROM decoder handles data as a stream of 16-bit data, and this register controls which 16-bit portion of each 32 bits of data transferred from the serial sound interface should be input first.</li> <li>00: The 16 bits of stream data that would otherwise be processed first is discarded.</li> <li>01: The higher-order 16 bits of each 32 bits of data received from the serial sound interface are placed first in the stream to the decoder.</li> <li>10: The lower-order 16 bits of each 32 bits of data</li> </ul> |

|                  |                  |                                    | received from the serial sound interface are placed<br>first in the stream to the decoder.<br>11: Setting prohibited                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                  | BITEND           | Bit Name Value BITEND 0 BUFEND0 01 | Bit Name Value R/W BITEND 0 R/W BUFEND0 01 R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Bit     | Bit Name | Initial<br>Value | R/W | Description                                                                                                                                                                 |

|---------|----------|------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31 to 0 | FIFOPORT | All 0            | R/W | FIFO Port                                                                                                                                                                   |

|         | [31:0]   |                  |     | Accessing these bits allow reading the received data from the FIFO buffer or writing the transmit data to the FIFO buffer.                                                  |

|         |          |                  |     | These bits can be accessed only while the FRDY bit in each control register (CFIFOCTR, D0FIFOCTR, or D1FIFOCTR) is 1.                                                       |

|         |          |                  |     | The valid bits in this register depend on the settings<br>of the MBW bits (access bit width setting) and<br>BIGEND bit (endian setting) as shown in tables 26.7<br>to 26.9. |

#### Table 26.7 Endian Operation in 32-Bit Access (when MBW = 10)

| <b>BIGEND Bit</b> | Bits 31 to 24 | Bits 23 to 16 | Bits 15 to 8  | Bits 7 to 0   |

|-------------------|---------------|---------------|---------------|---------------|

| 0                 | N + 3 address | N + 2 address | N + 1 address | N + 0 address |

| 1                 | N + 0 address | N + 1 address | N + 2 address | N + 3 address |

#### Table 26.8 Endian Operation in 16-Bit Access (when MBW = 01)

| <b>BIGEND Bit</b> | Bits 31 to 24           | Bits 23 to 16            | Bits 15 to 8          | Bits 7 to 0          |

|-------------------|-------------------------|--------------------------|-----------------------|----------------------|

| 0                 | Writing: invalid,       | reading: prohibited*     | N + 1 address         | N + 0 address        |

| 1                 | N + 0 address           | N + 1 address            | Writing: invalid,     | reading: prohibited* |

| Nata: * D         | ading data from the inv | alid hita in a word or k | outo unit io probibit | ad                   |

Reading data from the invalid bits in a word or byte unit is prohibited. Note: \*

#### Table 26.9 Endian Operation in 8-Bit Access (when MBW = 00)

| BIGEND E | Bit Bits 31 to 24         | Bits 23 to 16                                        | Bits 15 to 8          | Bits 7 to 0 |  |  |  |  |

|----------|---------------------------|------------------------------------------------------|-----------------------|-------------|--|--|--|--|

| 0        | Writir                    | Writing: invalid, reading: prohibited* N + 0 address |                       |             |  |  |  |  |

| 1        | N + 0 address             | N + 0 address Writing: invalid, reading: prohibited* |                       |             |  |  |  |  |

| Note: *  | Reading data from the inv | alid bits in a word o                                | r byte unit is prohib | ited.       |  |  |  |  |

Reading data from the invalid bits in a word or byte unit is prohibited. inote:

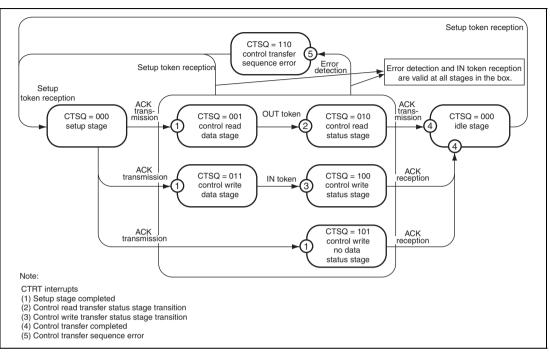

bits when the setup stage ends, and it generates a CTRT interrupt after the interrupt status is cleared.)

Figure 26.7 Control Transfer Stage Transitions

#### (6) Frame Update Interrupt

Figure 26.8 shows an example of the SOFR interrupt output timing of this module. With the host controller function selected, an interrupt is generated at the timing at which the frame number is updated. With the function controller function selected, the SOFR interrupt is generated when the frame number is updated.

When the function controller function is selected, this module updates the frame number and generates an SOFR interrupt if it detects a new SOF packet during full-speed operation. During high-speed operation, however, this module does not update the frame number, or generates no SOFR interrupt until the module enters the  $\mu$ SOF locked state. Also, the SOF interpolation function is not activated. The  $\mu$ SOF lock state is the state in which  $\mu$ SOF packets with different frame numbers are received twice continuously without error occurrence.

The conditions under which the  $\mu$ SOF lock monitoring begins and stops are as follows.

| Register<br>Name    | Bit Name | Setting<br>Contents     | Remarks                                                                                       |

|---------------------|----------|-------------------------|-----------------------------------------------------------------------------------------------|

| DCPMAXP<br>PIPEMAXP | DEVSEL   | Selects a device        | Referenced only when the host controller function is selected.                                |

|                     | MXPS     | Maximum packet size     | Compliant with the USB standard.                                                              |

| PIPEPERI            | IFIS     | Buffer flush            | PIPE1 and PIPE2: Can be set (only when<br>isochronous transfer has been<br>selected)          |

|                     |          |                         | PIPE3 to PIPE9: Cannot be set                                                                 |

|                     | IITV     | Interval counter        | PIPE1 and PIPE2: Can be set (only when<br>isochronous transfer has been<br>selected)          |

|                     |          |                         | PIPE3 to PIPE5: Cannot be set                                                                 |

|                     |          |                         | PIPE6 to PIPE9: Can be set (only when the host<br>controller function has been<br>selected)   |

| DCPCTR<br>PIPEnCTR  | BSTS     | Buffer status           | For the DCP, receive buffer status and transmit buffer status are switched with the ISEL bit. |

|                     | INBUFM   | IN buffer monitor       | Mounted for PIPE3 to PIPE5.                                                                   |

|                     | SUREQ    | SETUP request           | Can be set only for the DCP.                                                                  |

|                     |          |                         | Can be controlled only when the host controller function has been selected.                   |

|                     | SUREQCLR | SUREQ clear             | Can be set only for the DCP.                                                                  |

|                     |          |                         | Can be controlled only when the host controller function has been selected.                   |

|                     | CSCLR    | CSSTS clear             | Can be controlled only when the host controller function has been selected.                   |

|                     | CSSTS    | SPLIT status indication | Can be referenced only when the host controller function has been selected.                   |

|                     | ATREPM   | Auto response           | PIPE1 to PIPE5: Can be set                                                                    |

|                     |          | mode                    | Can be controlled only when the function controller function has been selected.               |

| Continuous or Non-<br>Continuous Transfer<br>Mode | Method of Determining if Reading or Transmitting Data is Enabled                                                                                                                                                                                                                                    |

|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Continuous transfer<br>(CNTMD = 1)                | In the receiving direction (DIR = 0), reading data from the FIFO buffer is enabled when:                                                                                                                                                                                                            |

|                                                   | <ul> <li>The number of the data bytes received in the FIFO buffer assigned to<br/>the selected pipe becomes the same as the number of assigned data<br/>bytes (DCP: fixed at 256 bytes, pipes 1 to 5 (BUFSIZE + 1) × 64).</li> </ul>                                                                |

|                                                   | • This module receives a short packet other than a zero-length packet.                                                                                                                                                                                                                              |

|                                                   | <ul> <li>This module receives a zero-length packet when data is already<br/>stored in the FIFO buffer assigned to the selected pipe.<br/>or</li> </ul>                                                                                                                                              |

|                                                   | • This module receives the number of packets equal to the transaction counter value specified for the selected pipe. (PIPE1 to PIPE5 only)                                                                                                                                                          |

|                                                   | In the transmitting direction (DIR = 1), transmitting data from the FIFO buffer is enabled when:                                                                                                                                                                                                    |

|                                                   | <ul> <li>The number of the data bytes written to the FIFO buffer becomes the<br/>same as the number of data bytes in a single FIFO buffer plane<br/>assigned to the selected pipe.</li> <li>or</li> </ul>                                                                                           |

|                                                   | • The number of data bytes less than the size of a single FIFO buffer plane (including 0-byte data) assigned to the selected pipe is written to the FIFO buffer and then 1 is written to BVAL.                                                                                                      |

|                                                   | • In a DMA transfer, the DMA transfer end sampling enable (TENDE) bit<br>is set to 1, a number of data bytes less than the size of a single FIFO<br>buffer plane assigned to the selected pipe (or 0 bytes) is written to the<br>FIFO buffer, and the DMA transfer end signal is received (PIPE1 to |

RENESAS

PIPE5 only).

#### 27.7.6 Horizontal Valid Video Start Position Register (VIDEO\_HSTART)

| Bit:                   | 31     | 30     | 29     | 28     | 27     | 26     | 25     | 24       | 23       | 22       | 21       | 20       | 19       | 18       | 17       | 16       |

|------------------------|--------|--------|--------|--------|--------|--------|--------|----------|----------|----------|----------|----------|----------|----------|----------|----------|

|                        | -      | -      | -      | -      | -      | -      | -      | -        | -        | -        | -        | -        | -        | -        | -        | -        |

| Initial value:<br>R/W: | 0<br>R   | 0<br>R   | 0<br>R   | 0<br>R   | 0<br>R   | 0<br>R   | 0<br>R   | 0<br>R   | 0<br>R   |

| Bit:                   | 15     | 14     | 13     | 12     | 11     | 10     | 9      | 8        | 7        | 6        | 5        | 4        | 3        | 2        | 1        | 0        |

|                        | -      | -      | -      | -      | -      | -      | -      |          |          |          | VIDEC    | _HSTAR   | T[8:0]   |          |          |          |

| Initial value:<br>R/W: | 0<br>R | 1<br>R/W | 0<br>R/W | 0<br>R/W | 0<br>R/W | 1<br>R/W | 0<br>R/W | 1<br>R/W | 0<br>R/W | 0<br>R/W |

| Bit     | Bit Name              | Initial<br>Value | R/W | Description                                                                                                        |

|---------|-----------------------|------------------|-----|--------------------------------------------------------------------------------------------------------------------|

| 31 to 9 |                       | All 0            | R   | Reserved                                                                                                           |

|         |                       |                  |     | These bits are always read as 0. The write value should always be 0.                                               |

| 8 to 0  | VIDEO_<br>HSTART[8:0] | H'114            | R/W | These bits specify in number of DV_CLK cycles<br>the horizontal start position of the valid video in<br>the field. |

Note: Capture does not occur when the right edge of video has been cut.

# 28.4 Interrupts

This module has five interrupt sources: input data FIFO empty (IDEI), output data FIFO full (ODFI), output data FIFO overwrite (OVF), output data FIFO underflow (UDF), and conversion end (CEF). Table 28.11 summarizes the interrupts.

| Interrupt Request          | Abbreviation | Interrupt Condition                 | Direct Memory<br>Access Controller<br>Activation |

|----------------------------|--------------|-------------------------------------|--------------------------------------------------|

| Input data FIFO empty      | IDEI         | IINT = 1, IEN = 1, and<br>SRCEN = 1 | Possible                                         |

| Output data FIFO full      | ODFI         | OINT = 1, OEN = 1, and<br>SRCEN = 1 | Possible                                         |

| Output data FIFO overwrite | OVF          | OVF = 1, OVEN = 1, and<br>SRCEN = 1 | Not possible                                     |

| Output data FIFO underflow | UDF          | UDF = 1, UDEN = 1, and<br>SRCEN = 1 | Not possible                                     |

| Conversion end             | CEF          | CEF = 1, CEEN = 1, and<br>SRCEN = 1 | Not possible                                     |

#### **Table 28.11 Interrupt Requests and Generation Conditions**

When the interrupt condition is satisfied, the CPU executes the interrupt exception handling routine. The interrupt source flags should be cleared in the routine.

The IDEI and ODFI interrupts can activate the direct memory access controller when the direct memory access controller is set to allow this. If the direct memory access controller is activated, the interrupts from this module are not sent to the CPU. When the direct memory access controller has written data to SRCID resulting in the number of data units in the input data FIFO exceeding that of the specified triggering number, the IINT bit is cleared to 0. Similarly, when the direct memory access controller has read data from SRCOD resulting in the number of data units in the output data FIFO being less than the specified triggering number, the OINT bit is cleared to 0.

#### Table 32.20 Port J Data Registers 0 (PJDR0) Read/Write Operation

| 210011 | 0 0 01 102100             |                       |                                                            |

|--------|---------------------------|-----------------------|------------------------------------------------------------|

| PJIOR0 | Pin Function              | <b>Read Operation</b> | Write Operation                                            |

| 0      | General input             | Pin state             | Can write to PJDR0, but it has no effect on the pin state. |

|        | Other than general input  | Pin state             | Can write to PJDR0, but it has no effect on the pin state. |

| 1      | General output            | PJDR0 value           | Value written is output from pin                           |

|        | Other than general output | PJDR0 value           | Can write to PJDR0, but it has no effect on the pin state  |

#### • Bits 11 to 0 of PJDR0

#### 32.2.33 Port J Port Register 0 (PJPR0)

PJPR0 is a 16-bit read-only register, in which the PJ11PR to PJ0PR bits correspond to the PJ11 to PJ0 pins, respectively. PJPR0 always returns the states of the pins regardless of the PJCR0 to PGCR2 settings.

| Bit:           | 15  | 14     | 13 | 12     | 11         | 10         | 9         | 8         | 7         | 6                 | 5         | 4         | 3         | 2         | 1         | 0         |

|----------------|-----|--------|----|--------|------------|------------|-----------|-----------|-----------|-------------------|-----------|-----------|-----------|-----------|-----------|-----------|

|                | -   | -      | -  | -      | PJ11<br>PR | PJ10<br>PR | PJ9<br>PR | PJ8<br>PR | PJ7<br>PR | PJ6<br>PR         | PJ5<br>PR | PJ4<br>PR | PJ3<br>PR | PJ2<br>PR | PJ1<br>PR | PJ0<br>PR |

| Initial value: | 0   | 0      | 0  | 0      | PJ11       | PJ10       | PJ9       | PJ8       | PJ7       | PJ6               | PJ5       | PJ4       | PJ3       | PJ2       | PJ1       | PJ0       |

| R/W:           | R   | R      | R  | R      | R          | R          | R         | R         | R         | R                 | R         | R         | R         | R         | R         | R         |

| Bit            | Bit | t Name | e  | Initia | l Valu     | e R        | /w        | De        | scrip     | tion              |           |           |           |           |           |           |

| 15 to 12       |     |        |    | All 0  |            | R          |           | Re        | serve     | d                 |           |           |           |           |           |           |

|                |     |        |    |        |            |            |           |           |           | its are<br>ould a |           | -         |           | 0. The    | e write   | e         |

|                |     |        |    |        |            |            |           |           |           |                   |           |           |           |           |           |           |

#### (2) Canceling Software Standby Mode

Software standby mode is canceled by interrupts (NMI or IRQ) or a reset (power-on reset). Clock signal starts to be output from the CKIO pin.

• Canceling by an interrupt

When the falling edge or rising edge of the NMI pin (selected by the NMI edge select bit (NMIE) in interrupt control register 0 (ICR0) of the interrupt controller) or the falling edge or rising edge of an IRQ pin (IRQ7 to IRQ0) (selected by the IRQn sense select bits (IRQn1S and IRQn0S) in interrupt control register 1 (ICR1) of the interrupt controller) is detected, clock oscillation is started. This clock pulse is supplied only to the oscillation settling counter (watchdog timer) used to count the oscillation settling time.

After the elapse of the time set in the clock select bits (CKS[2:0]) in the watchdog timer control/status register (WTCSR) of the watchdog timer before the transition to software standby mode, the watchdog timer overflow occurs. Since this overflow indicates that the clock has been stabilized, the clock pulse will be supplied to the entire chip after this overflow. Software standby mode is thus cleared and NMI interrupt exception handling (IRQ interrupt exception handling in case of IRQ) is started. If the priority level of the generated interrupt is equal to or lower than the interrupt mask level specified in the status register (SR) of the CPU, the interrupt request is not accepted and software standby mode is not canceled.

When canceling software standby mode by the NMI interrupt or IRQ interrupt, set the CKS[2:0] bits so that the watchdog timer overflow period will be equal to or longer than the oscillation settling time.

The clock output phase of the CKIO pin may be unstable immediately after detecting an interrupt and until software standby mode is canceled. When software standby mode is canceled by the falling edge of the NMI pin, the NMI pin should be high when software standby mode is entered (when the clock pulse stops) and should be low when software standby mode is canceled (when the clock is initiated after the oscillation settling). When software standby mode is canceled by the rising edge of the NMI pin, the NMI pin should be low when software standby mode is canceled by the rising edge of the NMI pin, the NMI pin should be low when software standby mode is entered (when the clock pulse stops) and should be high when software standby mode is entered (when the clock pulse stops) and should be high when software standby mode is canceled (when the clock is initiated after the oscillation settling) (This is the same with the IRQ pin.)

• Canceling by a reset

When the  $\overline{\text{RES}}$  pin is driven low, software standby mode is canceled and the LSI enters the power-on reset state. After that, if the  $\overline{\text{RES}}$  pin is driven high, the power-on reset exception handling is started.

Keep the  $\overline{\text{RES}}$  pin low until the clock oscillation settles. The internal clock will continue to be output to the CKIO pin.

# 35.5 Operation

# 35.5.1 PWM Operation

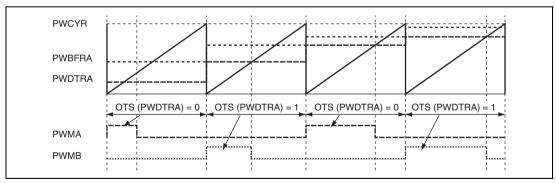

PWM waveforms are output from pins PWM1A to PWM1H and PWM2A to PWM2H as shown in figure 35.7.

# (1) Initial Settings

Set the PWM output polarity in PWPR\_n; select the clock to be input to PWCNT\_n with the CKS2 to CKS0 bits in PWCRn; set the PWM conversion cycle in PWCYR\_n; and set the first frame of data in PWBFR\_nA, PWBFR\_nC, PWBFR\_nE, and PWBFR\_nG.

# (2) Activation

When the CST bit in PWCR\_n is set to 1, PWCNT\_n starts counting up. On compare match between PWCNT\_n and PWCYR\_n, data is transferred from the buffer register to the duty register and the CMF bit in PWCR\_n is set to 1. At the same time, if the IE bit in PWCR\_n has been set to 1, an interrupt can be requested or the direct memory access controller can be activated.

# (3) Waveform Output

The PWM outputs selected by the OTS bits in PWDTR\_nA, PWDTR\_nC, PWDTR\_nE, and PWDTR\_nG go high when a compare match occurs between PWCNT\_n and PWCYR\_n. The PWM outputs not selected by the OTS bit are low. When a compare match occurs between PWCNT\_n and PWDTR\_nA, PWDTR\_nC, PWDTR\_nE, or PWDTR\_nG, the corresponding PWM output goes low. If the corresponding bit in PWPR\_n is set to 1, the output is inverted.

Figure 35.7 PWM Operation

### 35.6 Usage Note

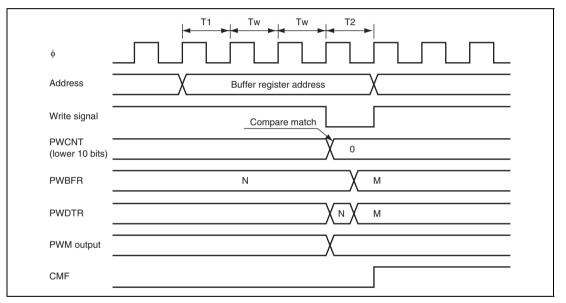

#### 35.6.1 Conflict between Buffer Register Write and Compare Match

If a PWBFR\_n write is performed in the state immediately after a cycle register compare match, the buffer register and duty register are both modified. PWM output changed by the cycle register compare match is not changed by modification of the duty register due to conflict. This may result in unanticipated duty output.

Buffer register modification must be completed before automatic transfer by the direct memory access controller, exception handling due to a compare match interrupt, or the occurrence of a cycle register compare match on detection of the rise of CMF (compare match flag) in PWCR\_n.

Figure 35.9 Conflict between Buffer Register Write and Compare Match

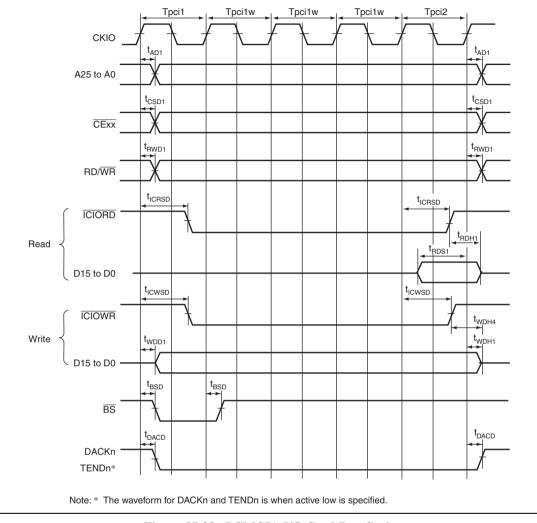

#### Figure 37.38 PCMCIA I/O Card Bus Cycle (TED = 0 Cycle, TEH = 0 Cycle, No Wait)

| Item                                                                                                                                                                                                                                                                                                                                                                   | Page | Revision (See Manual for Details)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul><li>26.4.4 FIFO Buffer Memory</li><li>(2) FIFO Port Functions</li><li>(a) FIFO Port Selection</li></ul>                                                                                                                                                                                                                                                            | 1518 | Description amended<br>Also, the bus width to be accessed should be selected<br>using the MBW bit. The buffer memory access direction<br>conforms to the DIR bit in PIPE CFG. The ISEL bit<br>determines this only for the DCP.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| <ul> <li>26.4.5 Control Transfers</li> <li>(DCP)</li> <li>(2) Control Transfers when<br/>the Function Controller<br/>Function is Selected</li> <li>(b) Data Stage</li> </ul>                                                                                                                                                                                           | 1526 | Description deleted<br>A transaction is executed by setting the PID bits in the<br>DCPCTR register to BUF. The BRDY interrupt or the<br>BEMP interrupt can be used to detect the end of data<br>transfer. Use the BRDY interrupt to detect the end of<br>control write transfers and the BEMP interrupt to detect the<br>end of control read transfers.<br>With control write transfers during high-speed operation,<br>the NYET handshake response is carried out based on the<br>state of the buffer memory.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| <ul> <li>26.4.8 Isochronous</li> <li>Transfers (PIPE1 and PIPE2)</li> <li>(3) Interval Counter</li> <li>(c) Interval Counting and</li> <li>Transfer Control when the</li> <li>Function Controller Function</li> <li>is Selected</li> <li>Figure 26.19 Relationship</li> <li>between (μ) Frames and</li> <li>Expected Token Reception</li> <li>when IITV = 1</li> </ul> | 1539 | Figure amended<br>USB bus<br>PID bit setting<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>Token<br>To |

| 27.7.24 α Control Area Start<br>Position Registers<br>(GROPEDPHV1 and<br>GROPEDPHV2)<br>Figure 27.22 α Control Area<br>Settings                                                                                                                                                                                                                                        |      | Figure amended  Reference Hsync  GROPEDPH + 10  Graphics image area  Graphics image area                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 27.7.35 Horizontal Sync<br>Signal Timing Control<br>Register<br>(PANEL_HSYNC_TIM)                                                                                                                                                                                                                                                                                      | 1619 | Bit         Bit Name         Initial<br>Value         Description           26 to 16         HSYNC_START         H'000         R/W         Description           [10:0]         R/W         panel clock cycles the interval between the<br>reference horizontal sync signal and the point<br>where the horizontal sync signal (HSYNC) for<br>panel is set to 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

RENESAS