# E·XFL Renesas Electronics America Inc - <u>R5S72625P144FP#UZ Datasheet</u>

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Last Time Buy                                                                      |

|----------------------------|------------------------------------------------------------------------------------|

| Core Processor             | SH2A-FPU                                                                           |

| Core Size                  | 32-Bit Single-Core                                                                 |

| Speed                      | 144MHz                                                                             |

| Connectivity               | CANbus, I <sup>2</sup> C, SCI, SD, SIO, SPI, USB                                   |

| Peripherals                | DMA, POR, PWM, WDT                                                                 |

| Number of I/O              | 89                                                                                 |

| Program Memory Size        | -                                                                                  |

| Program Memory Type        | ROMIess                                                                            |

| EEPROM Size                | -                                                                                  |

| RAM Size                   | 640K × 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 1.1V ~ 3.6V                                                                        |

| Data Converters            | A/D 4x10b                                                                          |

| Oscillator Type            | External                                                                           |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                  |

| Mounting Type              | Surface Mount                                                                      |

| Package / Case             | 176-LQFP                                                                           |

| Supplier Device Package    | 176-LFQFP (24x24)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r5s72625p144fp-uz |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|      | 26.3.16  | Interrupt Status Register 0 (INTSTS0)                              | 1390 |

|------|----------|--------------------------------------------------------------------|------|

|      | 26.3.17  | Interrupt Status Register 1 (INTSTS1)                              | 1395 |

|      | 26.3.18  | BRDY Interrupt Status Register (BRDYSTS)                           | 1401 |

|      | 26.3.19  | NRDY Interrupt Status Register (NRDYSTS)                           | 1403 |

|      | 26.3.20  | BEMP Interrupt Status Register (BEMPSTS)                           | 1405 |

|      | 26.3.21  | Frame Number Register (FRMNUM)                                     | 1406 |

|      | 26.3.22  | µFrame Number Register (UFRMNUM)                                   | 1409 |

|      | 26.3.23  | USB Address Register (USBADDR)                                     | 1410 |

|      | 26.3.24  | USB Request Type Register (USBREQ)                                 | 1411 |

|      | 26.3.25  | USB Request Value Register (USBVAL)                                | 1412 |

|      | 26.3.26  | USB Request Index Register (USBINDX)                               | 1413 |

|      | 26.3.27  | USB Request Length Register (USBLENG)                              | 1414 |

|      | 26.3.28  | DCP Configuration Register (DCPCFG)                                | 1415 |

|      | 26.3.29  | DCP Maximum Packet Size Register (DCPMAXP)                         | 1417 |

|      | 26.3.30  | DCP Control Register (DCPCTR)                                      |      |

|      | 26.3.31  | Pipe Window Select Register (PIPESEL)                              | 1428 |

|      | 26.3.32  | Pipe Configuration Register (PIPECFG)                              | 1429 |

|      | 26.3.33  | Pipe Buffer Setting Register (PIPEBUF)                             | 1436 |

|      | 26.3.34  | Pipe Maximum Packet Size Register (PIPEMAXP)                       | 1439 |

|      | 26.3.35  | Pipe Timing Control Register (PIPEPERI)                            |      |

|      | 26.3.36  | PIPEn Control Registers (PIPEnCTR) (n = 1 to 9)                    | 1443 |

|      | 26.3.37  | PIPEn Transaction Counter Enable Registers (PIPEnTRE) (n = 1 to 5) | 1464 |

|      | 26.3.38  | PIPEn Transaction Counter Registers (PIPEnTRN) (n = 1 to 5)        | 1466 |

|      | 26.3.39  | Device Address n Configuration Registers (DEVADDn) (n = 0 to A)    | 1468 |

|      | 26.3.40  | USB AC Characteristics Switching Register 1 (USBACSWR1)            | 1471 |

| 26.4 | Operatio | n                                                                  | 1472 |

|      | 26.4.1   | System Control and Oscillation Control                             | 1472 |

|      | 26.4.2   | Interrupt Functions                                                | 1476 |

|      | 26.4.3   | Pipe Control                                                       | 1499 |

|      | 26.4.4   | FIFO Buffer Memory                                                 | 1509 |

|      | 26.4.5   | Control Transfers (DCP)                                            | 1524 |

|      | 26.4.6   | Bulk Transfers (PIPE1 to PIPE5)                                    | 1528 |

|      | 26.4.7   | Interrupt Transfers (PIPE6 to PIPE9)                               | 1530 |

|      | 26.4.8   | Isochronous Transfers (PIPE1 and PIPE2)                            | 1531 |

|      | 26.4.9   | SOF Interpolation Function                                         | 1543 |

|      | 26.4.10  | Pipe Schedule                                                      | 1544 |

| 26.5 | Usage N  | otes                                                               | 1546 |

|      | 26.5.1   | Procedure for Setting the USB Transceiver                          | 1546 |

|      | 26.5.2   | Power Supply for USB Transceiver                                   | 1546 |

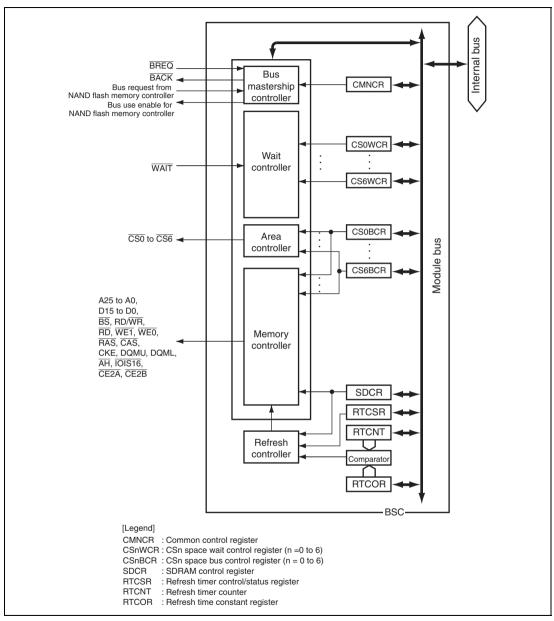

Figure 9.1 shows a block diagram of this module.

Figure 9.1 Block Diagram of Bus State Controller

| Name     | I/O    | Function                                                                             |

|----------|--------|--------------------------------------------------------------------------------------|

| WE0/DQML | Output | Indicates that D7 to D0 are being written to.                                        |

|          |        | Connected to the byte select signal when a SRAM with byte selection is connected.    |

|          |        | Functions as the select signals for D7 to D0 when SDRAM is connected.                |

| RAS      | Output | Connects to RAS pin when SDRAM is connected.                                         |

| CAS      | Output | Connects to CAS pin when SDRAM is connected.                                         |

| CKE      | Output | Connects to CKE pin when SDRAM is connected.                                         |

| WAIT     | Input  | External wait input                                                                  |

| BREQ     | Input  | Bus request input                                                                    |

| BACK     | Output | Bus enable output                                                                    |

| IOIS16   | Input  | Indicates 16-bit I/O of PCMIA.                                                       |

|          |        | Enabled only in little endian mode. The pin should be driven low in big endian mode. |

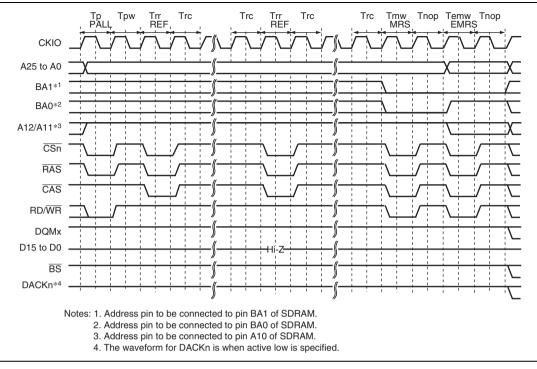

Figure 9.31 EMRS Command Issue Timing

#### (2) Basic Timing for I/O Card Interface

Figures 9.42 and 9.43 show the basic timing for the PCMCIA I/O card interface.

When accessing an I/O card through the PCMCIA interface, be sure to access the space as cachedisabled.

Switching between I/O card and IC memory card interfaces in the respective address spaces is accomplished by the SA[1:0] bit settings in CS5WCR and CS6WCR.

The IOIS16 pin can be used for dynamic adjustment of the width of the I/O bus in access to an I/O card via the PCMCIA interface when little endian mode has been selected. When the bus width of area 5 or 6 is set to 16 bits and the IOIS16 signal is driven high during a cycle of word-unit access to the I/O card bus, the bus width will be recognized as 8 bits and only 8 bits of data will be accessed during the current cycle of the I/O card bus. Operation will automatically continue with access to the remaining 8 bits of data.

The  $\overline{IOIS16}$  signal is sampled on falling edges of the CKIO in Tpci0 as well as all Tpci0w cycles for which the TED3 to TED0 bits are set to 1.5 cycles or more, and the  $\overline{CE2A}$  and  $\overline{CE2B}$  signals are updated after 1.5 cycles of the CKIO signal from the sampling point of Tpci0. Ensure that the  $\overline{IOIS16}$  signal is defined at all sampling points and does not change along the way.

Set the TED3 to TED0 bits to satisfy the requirement of the PC card in use with regard to setup timing from  $\overline{\text{ICIORD}}$  or  $\overline{\text{ICIORD}}$  to  $\overline{\text{CE1}}$  or  $\overline{\text{CE2}}$ .

The basic waveforms for dynamic bus-size adjustment are shown in figure 9.43.

Since the  $\overline{IOIS16}$  signal is not supported in big endian mode, the  $\overline{IOIS16}$  signal should be fixed to the low level when big endian mode has been selected.

#### Table 11.15 TIORH\_3 (Channel 3)

|               |               |               |               |                    | Description                    |

|---------------|---------------|---------------|---------------|--------------------|--------------------------------|

| Bit 7<br>IOB3 | Bit 6<br>IOB2 | Bit 5<br>IOB1 | Bit 4<br>IOB0 | TGRB_3<br>Function | TIOC3B Pin Function            |

| 0             | 0             | 0             | 0             | Output             | Output retained*               |

|               |               |               | 1             | compare register   | Initial output is 0            |

|               |               |               |               | register           | 0 output at compare match      |

|               |               | 1             | 0             |                    | Initial output is 0            |

|               |               |               |               |                    | 1 output at compare match      |

|               |               |               | 1             |                    | Initial output is 0            |

|               |               |               |               |                    | Toggle output at compare match |

|               | 1             | 0             | 0             |                    | Output retained                |

|               |               |               | 1             |                    | Initial output is 1            |

|               |               |               |               |                    | 0 output at compare match      |

|               |               | 1             | 0             |                    | Initial output is 1            |

|               |               |               |               |                    | 1 output at compare match      |

|               |               |               | 1             |                    | Initial output is 1            |

|               |               |               |               |                    | Toggle output at compare match |

| 1             | Х             | 0             | 0             |                    | Input capture at rising edge   |

|               |               |               | 1             | register           | Input capture at falling edge  |

|               |               | 1             | Х             |                    | Input capture at both edges    |

| [Leaen        | d]            |               |               |                    |                                |

[Legend]

X: Don't care

Note: \* After power-on reset, 0 is output until TIOR is set.

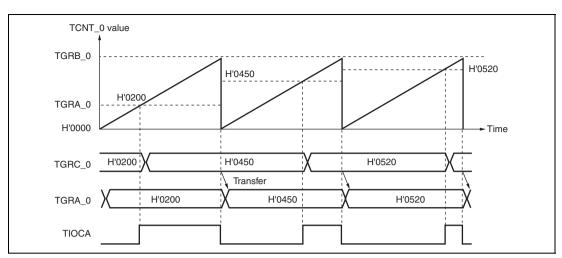

Figure 11.19 Example of Buffer Operation When TCNT\_0 Clearing is Selected for TGRC\_0 to TGRA\_0 Transfer Timing

#### 11.4.4 Cascaded Operation

In cascaded operation, two 16-bit counters for different channels are used together as a 32-bit counter.

This function works by counting the channel 1 counter clock upon overflow/underflow of TCNT\_2 as set in bits TPSC0 to TPSC2 in TCR.

Underflow occurs only when the lower 16-bit TCNT is in phase-counting mode.

Table 11.42 shows the register combinations used in cascaded operation.

Note: When phase counting mode is set for channel 1, the counter clock setting is invalid and the counters operates independently in phase counting mode.

#### Table 11.42 Cascaded Combinations

| Combination      | Upper 16 Bits | Lower 16 Bits |

|------------------|---------------|---------------|

| Channels 1 and 2 | TCNT_1        | TCNT_2        |

For simultaneous input capture of TCNT\_1 and TCNT\_2 during cascaded operation, additional input capture input pins can be specified by the input capture control register (TICCR). The edge detection that is the condition for input capture uses a signal representing the logical OR of the original input pin and the added input pins. For details, see (4) Cascaded Operation Example (c).

#### (c) Initialization

In complementary PWM mode, there are six registers that must be initialized. In addition, there is a register that specifies whether to generate dead time (it should be used only when dead time generation should be disabled).

Before setting complementary PWM mode with bits MD3 to MD0 in the timer mode register (TMDR), the following initial register values must be set.

TGRC\_3 operates as the buffer register for TGRA\_3, and should be set with 1/2 the PWM carrier cycle + dead time Td. The timer cycle buffer register (TCBR) operates as the buffer register for the timer cycle data register (TCDR), and should be set with 1/2 the PWM carrier cycle. Set dead time Td in the timer dead time data register (TDDR).

When dead time is not needed, the TDER bit in the timer dead time enable register (TDER) should be cleared to 0, TGRC\_3 and TGRA\_3 should be set to 1/2 the PWM carrier cycle + 1, and TDDR should be set to 1.

Set the respective initial PWM duty values in buffer registers TGRD\_3, TGRC\_4, and TGRD\_4.

The values set in the five buffer registers excluding TDDR are transferred simultaneously to the corresponding compare registers when complementary PWM mode is set.

Set TCNT\_4 to H'0000 before setting complementary PWM mode.

| Table 11.54 | <b>Registers and</b> | Counters 1 | Requiring | Initialization |

|-------------|----------------------|------------|-----------|----------------|

|-------------|----------------------|------------|-----------|----------------|

| Register/Counter                | Set Value                                                                                                      |

|---------------------------------|----------------------------------------------------------------------------------------------------------------|

| TGRC_3                          | 1/2 PWM carrier cycle + dead time Td (1/2 PWM carrier cycle + 1 when dead time generation is disabled by TDER) |

| TDDR                            | Dead time Td (1 when dead time generation is disabled by TDER)                                                 |

| TCBR                            | 1/2 PWM carrier cycle                                                                                          |

| TGRD_3, TGRC_4, TGRD_4          | Initial PWM duty value for each phase                                                                          |

| TCNT_4                          | H'0000                                                                                                         |

| Note: The TGBC 3 set value must | he the sum of 1/2 the PWM carrier cycle set in TCBB and                                                        |

Note: The TGRC\_3 set value must be the sum of 1/2 the PWM carrier cycle set in TCBR and dead time Td set in TDDR. When dead time generation is disabled by TDER, TGRC\_3 must be set to 1/2 the PWM carrier cycle + 1.

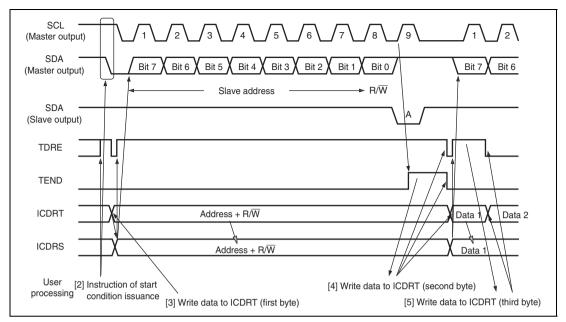

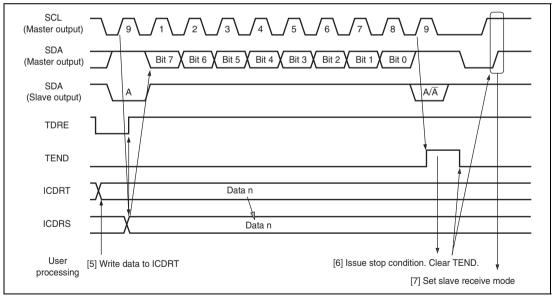

Figure 17.5 Master Transmit Mode Operation Timing (1)

Figure 17.6 Master Transmit Mode Operation Timing (2)

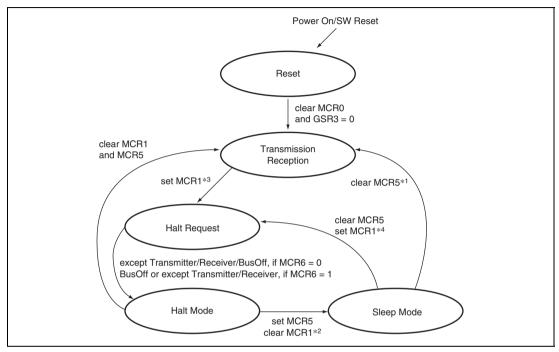

Figure 20.15 shows allowed state transitions.

- Please don't set MCR5 (Sleep Mode) without entering Halt Mode.

- After MCR1 is set, please don't clear it before GSR4 is set and this module enters Halt Mode.

Figure 20.15 Halt Mode/Sleep Mode

- Notes: 1. MCR5 can be cleared by automatically by detecting a dominant bit on the CAN Bus if MCR7 is set or by writing '0'.

- 2. MCR1 is cleared in SW. Clearing MCR1 and setting MCR5 have to be carried out by the same instruction.

- 3. MCR1 must not be cleared in SW, before GSR4 is set. MCR1 can be set automatically in HW when this module moves to Bus Off and MCR14 and MCR6 are both set.

- 4. When MCR5 is cleared and MCR1 is set at the same time, this module moves to Halt Request. Right after that, it moves to Halt Mode with no reception/transmission.

The following table shows conditions to access registers.

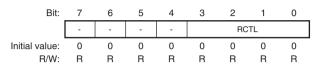

# 21.3.11 IEBus Receive Control Field Register (IERCTL)

IERCTL indicates the control field value in slave/broadcast reception. This register is enabled when slave/broadcast receive starts, and the contents are changed at the time of setting the RXS flag in IERSR. This register cannot be modified.

| Bit    | Bit Name | Initial<br>Value | R/W | Description                                                                                                                                                                                       |

|--------|----------|------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7 to 4 | _        | All 0            | R   | Reserved                                                                                                                                                                                          |

|        |          |                  |     | These bits are always read as 0. The write value should always be 0.                                                                                                                              |

| 3 to 0 | RCTL     | 0000             | R   | IEBus Receive Control Field                                                                                                                                                                       |

|        |          |                  |     | Indicates the control field value in slave/broadcast reception. This register is enabled when slave/broadcast reception starts, and the contents are changed at the time of setting the RXS flag. |

### 24.4.2 Multi Mode

Multi mode should be selected when performing A/D conversion once on one or more channels.

In multi mode, A/D conversion is performed once for a maximum of eight specified analog input channels, as follows:

- 1. A/D conversion starts from the analog input channel with the lowest number (e.g. AN0, AN1, ..., AN3) when the ADST bit in ADCSR is set to 1 by software, the multi-function timer pulse unit 2, or external trigger input.

- 2. When A/D conversion is completed on each channel, the A/D conversion result is sequentially transferred to the A/D data register corresponding to that channel.

- 3. After A/D conversion on all selected channels has completed, the ADF bit in ADCSR is set to 1. If the ADIE bit is set to 1 at this time, an ADI interrupt request is generated.

- 4. The ADST bit that remains 1 during A/D conversion is automatically cleared to 0 when A/D conversion is completed, and the A/D converter becomes idle. If the ADST bit is cleared to 0 during A/D conversion, A/D conversion is halted and the A/D converter becomes idle. The ADF bit is cleared by reading ADF while ADF = 1, then writing 0 to the ADF bit.

A/D conversion is to be performed once on all the specified channels. The conversion results are transferred for storage into the A/D data registers corresponding to the channels.

When the operating mode or analog input channel selection must be changed during A/D conversion, to prevent incorrect operation, first clear the ADST bit to 0 to halt A/D conversion. After making the necessary changes, set the ADST bit to 1. A/D conversion will start again from the first channel in the group. The ADST bit can be set at the same time as the mode or channel selection is changed.

Typical operations when three channels (AN0 to AN2) are selected in multi mode are described next. Figure 24.3 shows a timing diagram for this example.

- 1. Multi mode is selected (MDS2 = 1, MDS1 = 0), analog input channels AN0 to AN2 are selected (CH[2:0] = 010), and A/D conversion is started (ADST = 1).

- 2. A/D conversion of the first channel (AN0) starts. When A/D conversion is completed, the A/D conversion result is transferred into ADDRA.

- 3. Next, the second channel (AN1) is selected automatically and A/D conversion starts.

- 4. Conversion proceeds in the same way through the third channel (AN2).

- 5. When conversion of all selected channels (AN0 to AN2) is completed, the ADF flag is set to 1 and the ADST bit cleared to 0.

- 6. If the ADIE bit is set to 1 at this time, an ADI interrupt is requested.

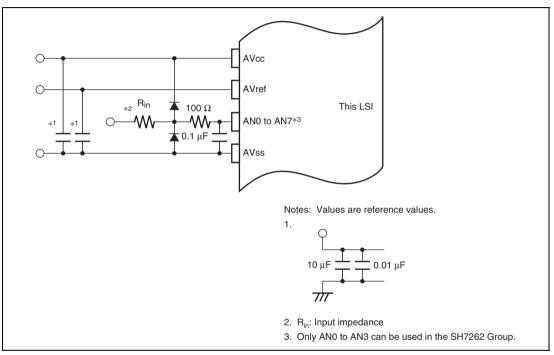

# 24.7.4 Processing of Analog Input Pins

To prevent damage from voltage surges at the analog input pins (AN0 to AN7), connect an input protection circuit like the one shown in figure 24.8. The circuit shown also includes a CR filter to suppress noise. This circuit is shown as an example; the circuit constants should be selected according to actual application conditions.

Figure 24.9 shows an equivalent circuit diagram of the analog input ports and table 24.7 lists the analog input pin specifications.

Figure 24.8 Example of Analog Input Protection Circuit

# 25.4 Operation

#### 25.4.1 Access Sequence

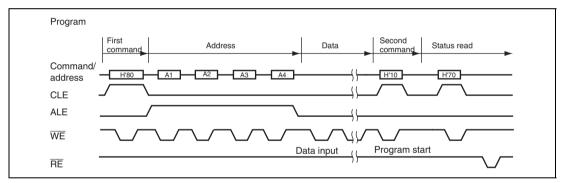

This module performs accesses in several independent stages.

For example, NAND-type flash memory programming consists of the following five stages.

- First command issue stage (program setup command)

- Address issue stage (program address)

- Data stage (output)

- Second command issue stage (program start command)

- Status read stage

NAND-type flash memory programming access is achieved by executing these five stages sequentially. An access to flash memory is completed at the end of the final stage (status read stage).

Figure 25.2 Programming Operation for NAND-Type Flash Memory and Stages

For details on NAND-type flash memory read operation, see section 25.4.4, Command Access Mode.

#### 25.4.2 Operating Modes

Two operating modes are supported.

- Command access mode

- Sector access mode

The ECC generation and error check are performed in sector access mode.

## 26.3.22 µFrame Number Register (UFRMNUM)

UFRMNUM is a register that indicates the µframe number.

This register is initialized by a power-on reset.

| Bit:           | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1       | 0  |

|----------------|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---------|----|

|                | _  | -  | _  | _  | _  | _  | _ | _ | — | _ | — | _ | _ | U | FRNM[2: | 0] |

| Initial value: | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0       | 0  |

| R/W:           | R  | R  | R  | R  | R  | R  | R | R | R | R | R | R | R | R | R       | R  |

| Bit     | Bit Name   | Initial<br>Value | R/W | Description                                                                                 |

|---------|------------|------------------|-----|---------------------------------------------------------------------------------------------|

| 15 to 3 | _          | All 0            | R   | Reserved                                                                                    |

|         |            |                  |     | These bits are always read as 0. The write value should always be 0.                        |

| 2 to 0  | UFRNM[2:0] | 000              | R   | μFrame                                                                                      |

|         |            |                  |     | The $\mu$ frame number can be confirmed.                                                    |

|         |            |                  |     | This module sets these bits to indicate the $\mu$ frame number during high-speed operation. |

|         |            |                  |     | During operation other than high-speed operation, this module sets these bits to B'000.     |

|         |            |                  |     | Read these bits twice to check that the same value is read.                                 |

| Bit    | Bit Name   | Initial<br>Value | R/W | Description                                                                                                                                                                                                                                               |

|--------|------------|------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4      | DIR        | 0                | R/W | Transfer Direction                                                                                                                                                                                                                                        |

|        |            |                  |     | Specifies the transfer direction for the selected pipe.                                                                                                                                                                                                   |

|        |            |                  |     | 0: Receiving direction                                                                                                                                                                                                                                    |

|        |            |                  |     | 1: Sending direction                                                                                                                                                                                                                                      |

|        |            |                  |     | When this bit has been set to 0, this module uses the selected pipe in the receiving direction, and when this bit has been set to 1, this module uses the selected pipe in the transmitting direction.                                                    |

|        |            |                  |     | Modify these bits when the value of CSSTS is 0, the PID bits are set to NAK, and no pipe is specified by the CURPIPE bits.                                                                                                                                |

|        |            |                  |     | To modify these bits after completing USB communication using the selected pipe, write 1 and then 0 to ACLRM continuously to clear the FIFO buffer assigned to the selected pipe while the CSSTS, PID, and CURPIPE bits are in the above-described state. |

|        |            |                  |     | Before modifying these bits after modifying the PID<br>bits for the selected pipe from BUF to NAK, check<br>that CSSTS and PBUSY are 0. However, if the PID<br>bits have been modified to NAK by this module,<br>checking PBUSY is not necessary.         |

| 3 to 0 | EPNUM[3:0] | 0000             | R/W | Endpoint Number                                                                                                                                                                                                                                           |

|        |            |                  |     | These bits specify the endpoint number for the selected pipe.                                                                                                                                                                                             |

|        |            |                  |     | Setting 0000 means unused pipe.                                                                                                                                                                                                                           |

|        |            |                  |     | Modify these bits while CSSTS is 0 and PID is NAK.                                                                                                                                                                                                        |

|        |            |                  |     | Before modifying these bits after modifying the PID<br>bits for the selected pipe from BUF to NAK, check<br>that CSSTS and PBUSY are 0. However, if the PID<br>bits have been modified to NAK by this module,<br>checking PBUSY is not necessary.         |

|        |            |                  |     | Do not make the settings such that the combination<br>of the set values in the DIR and EPNUM bits should<br>be the same for two or more pipes (EPNUM = $0000$<br>can be set for all the pipes).                                                           |

| Bit       | Bit Name           | Initial<br>Value | R/W | Description                                                                                                                                                           |

|-----------|--------------------|------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4         | VIDEO_MODE         | 0                | R/W | Specifies the operating mode for the video receiving block.                                                                                                           |

|           |                    |                  |     | 0: Video recording mode<br>(Be sure to set the EX_SYNC_MODE bit in the<br>SGMODE register to 0)                                                                       |

|           |                    |                  |     | 1: Video display mode<br>(Be sure to set the EX_SYNC_MODE bit in the<br>SGMODE register to 1)                                                                         |

| 3, 2      |                    | All 0            | R   | Reserved                                                                                                                                                              |

|           |                    |                  |     | These bits are always read as 0. The write value should always be 0.                                                                                                  |

| 1         | VIDEO_DISP_<br>EXE | 0                | R/W | Enables the video supplying block operation.<br>Setting to 1 starts video supply to the graphics<br>blocks. The register setting is updated with the<br>VSYNC timing. |

|           |                    |                  |     | 0: Disabled                                                                                                                                                           |

|           |                    |                  |     | 1: Enabled                                                                                                                                                            |

| 0         | VIDEO_MAIN_<br>EXE | 0                | R/W | Enables the video receiving block operation.<br>Setting to 1 starts video storing in the large-<br>capacity on-chip RAM or SDRAM.<br>0: Disabled* <sup>2</sup>        |

|           |                    |                  |     | 1: Enabled                                                                                                                                                            |

|           |                    |                  |     |                                                                                                                                                                       |

| Notes: 1. |                    |                  |     | d supplying blocks proceeds after bit<br>N_EXE, respectively, is set to 1, and detection of                                                                           |

VSYCN. Operation stops when the protocol for the internal bus is ended after the corresponding bit has been cleared to 0.2. To disable the video receiving block operation, please follow the procedure shown in

section 27.10.1, The Procedure of Disabling the Video Receiving Block Operation.

|                                     | Register     |                |                |                |                |                |                |               |               |

|-------------------------------------|--------------|----------------|----------------|----------------|----------------|----------------|----------------|---------------|---------------|

| Module Name                         | Abbreviation | Bit 31/23/15/7 | Bit 30/22/14/6 | Bit 29/21/13/5 | Bit 28/20/12/4 | Bit 27/19/11/3 | Bit 26/18/10/2 | Bit 25/17/9/1 | Bit 24/16/8/0 |

| I <sup>°</sup> C bus<br>interface 3 | ICCR1_2      | ICE            | RCVD           | MST            | TRS            | CKS[3]         | CKS[2]         | CKS[1]        | CKS[0]        |

|                                     | ICCR2_2      | BBSY           | SCP            | SDAO           | SDAOP          | SCLO           | _              | IICRST        | _             |

|                                     | ICMR_2       | MLS            | _              | _              | _              | BCWP           | BC[2]          | BC[1]         | BC[0]         |

|                                     | ICIER_2      | TIE            | TEIE           | RIE            | NAKIE          | STIE           | ACKE           | ACKBR         | ACKBT         |

|                                     | ICSR_2       | TDRE           | TEND           | RDRF           | NACKF          | STOP           | AL/OVE         | AAS           | ADZ           |

|                                     | SAR_2        | SVA[6]         | SVA[5]         | SVA[4]         | SVA[3]         | SVA[2]         | SVA[1]         | SVA[0]        | FS            |

|                                     | ICDRT_2      |                |                |                |                |                |                |               |               |

|                                     | ICDRR_2      |                |                |                |                |                |                |               |               |

|                                     | NF2CYC_2     | _              | _              | _              | CKS4           | _              | _              | PRS           | NF2CYC        |

| Serial sound<br>interface           | SSICR_0      | _              | СКЅ            | TUIEN          | TOIEN          | RUIEN          | ROIEN          | IIEN          | _             |

|                                     |              | CHNL[1]        | CHNL[0]        | DWL[2]         | DWL[1]         | DWL[0]         | SWL[2]         | SWL[1]        | SWL[0]        |

|                                     |              | SCKD           | SWSD           | SCKP           | SWSP           | SPDP           | SDTA           | PDTA          | DEL           |

|                                     |              | CKDV[3]        | CKDV[2]        | CKDV[1]        | CKDV[0]        | MUEN           | _              | TEN           | REN           |

|                                     | SSISR_0      | _              | _              | TUIRQ          | TOIRQ          | RUIRQ          | ROIRQ          | IIRQ          | _             |

|                                     |              | _              | _              | _              | _              | _              | _              | _             | _             |

|                                     |              | _              | _              | _              | _              | _              | _              | _             | _             |

|                                     |              | _              | TCHNO[1]       | TCHNO[0]       | TSWNO          | RCHNO[1]       | RCHNO[0]       | RSWNO         | IDST          |

|                                     | SSIFCR_0     | _              | _              | _              | _              | _              | _              | _             | _             |

|                                     |              | _              | _              | _              | _              | _              | _              | _             | _             |

|                                     |              | _              | _              | _              | _              | _              | _              | _             | _             |

|                                     |              | TTRG[1]        | TTRG[0]        | RTRG[1]        | RTRG[0]        | TIE            | RIE            | TFRST         | RFRST         |

|                                     | SSIFSR_0     | _              | _              | _              | _              | TDC[3]         | TDC[2]         | TDC[1]        | TDC[0]        |

|                                     |              | _              | _              | _              |                | _              | _              | _             | TDE           |

|                                     |              | _              | _              | _              |                | RDC[3]         | RDC[2]         | RDC[1]        | RDC[0]        |

|                                     |              | _              | —              | _              | _              | _              | —              | _             | RDF           |

|                                     | SSIFTDR_0    |                |                |                |                |                |                |               |               |

|                                     |              |                |                |                |                |                |                |               |               |

|                                     |              |                |                |                |                |                |                |               |               |

|                                     |              |                |                |                |                |                |                |               |               |

|                   | Register     |                |                |                |                |                |                |                 |                 |

|-------------------|--------------|----------------|----------------|----------------|----------------|----------------|----------------|-----------------|-----------------|

| Module Name       | Abbreviation | Bit 31/23/15/7 | Bit 30/22/14/6 | Bit 29/21/13/5 | Bit 28/20/12/4 | Bit 27/19/11/3 | Bit 26/18/10/2 | Bit 25/17/9/1   | Bit 24/16/8/0   |

| Renesas           | TDAD         | _              | _              | _              | _              | _              | _              | _               | _               |

| SPDIF             |              |                |                |                |                |                |                |                 |                 |

|                   |              |                |                |                |                |                |                |                 |                 |

|                   |              |                |                |                |                |                |                |                 |                 |

|                   | RDAD         | _              |                |                |                |                | _              | _               | _               |

|                   |              |                |                |                |                |                |                |                 |                 |

|                   |              |                |                |                |                |                |                |                 |                 |

|                   |              |                |                |                |                |                |                |                 |                 |

| CD-ROM<br>decoder | CROMEN       | SUBC_EN        | CROM_EN        | CROM_STP       |                | _              | _              | _               | _               |

|                   | CROMSY0      | SY_AUT         | SY_IEN         | SY_DEN         |                |                | _              | _               | _               |

|                   | CROMCTL0     | MD_DESC        | _              | MD_AUTO        | MD_AUTOS1      | MD_AUTOS2      | MD_SEC[2]      | MD_SEC[1]       | MD_SEC[0]       |

|                   | CROMCTL1     | M2F2EDC        | MD_DEC[2]      | MD_DEC[1]      | MD_DEC[0]      |                |                | MD_<br>PQREP[1] | MD_<br>PQREP[0] |

|                   | CROMCTL3     | STP_ECC        | STP_EDC        | _              | STP_MD         | STP_MIN        | _              | _               | _               |

|                   | CROMCTL4     | _              | LINK2          | —              | EROSEL         | NO_ECC         | _              | _               | _               |

|                   | CROMCTL5     | _              |                |                |                |                |                |                 | MSF_LBA_<br>SEL |

|                   | CROMST0      | _              | _              | ST_SYIL        | ST_SYNO        | ST_BLKS        | ST_BLKL        | ST_SECS         | ST_SECL         |

|                   | CROMST1      | _              | _              | _              | _              | ER2_HEAD0      | ER2_HEAD1      | ER2_HEAD2       | ER2_HEAD3       |

|                   | CROMST3      | ER2_SHEAD0     | ER2_SHEAD1     | ER2_SHEAD2     | ER2_SHEAD3     | ER2_SHEAD4     | ER2_SHEAD5     | ER2_SHEAD6      | ER2_SHEAD7      |

|                   | CROMST4      | NG_MD          | NG_MDCMP1      | NG_MDCMP2      | NG_MDCMP3      | NG_MDCMP4      | NG_MDDEF       | NG_MDTIM1       | NG_MDTIM2       |

|                   | CROMST5      | ST_AMD[2]      | ST_AMD[1]      | ST_AMD[0]      | ST_MDX         | LINK_ON        | LINK_DET       | LINK_SDET       | LINK_OUT1       |

|                   | CROMST6      | ST_ERR         | _              | ST_ECCABT      | ST_ECCNG       | ST_ECCP        | ST_ECCQ        | ST_EDC1         | ST_EDC2         |

|                   | CBUFST0      | BUF_REF        | BUF_ACT        | _              | _              | _              |                | _               | _               |

|                   | CBUFST1      | BUF_ECC        | BUF_EDC        |                | BUF_MD         | BUF_MIN        |                | _               | _               |

|                   | CBUFST2      | BUF_NG         |                |                |                |                | _              | _               | _               |

|                   | HEAD00       | HEAD00[7]      | HEAD00[6]      | HEAD00[5]      | HEAD00[4]      | HEAD00[3]      | HEAD00[2]      | HEAD00[1]       | HEAD00[0]       |

|                   | HEAD01       | HEAD01[7]      | HEAD01[6]      | HEAD01[5]      | HEAD01[4]      | HEAD01[3]      | HEAD01[2]      | HEAD01[1]       | HEAD01[0]       |

|                   | HEAD02       | HEAD02[7]      | HEAD02[6]      | HEAD02[5]      | HEAD02[4]      | HEAD02[3]      | HEAD02[2]      | HEAD02[1]       | HEAD02[0]       |

|                   | HEAD03       | HEAD03[7]      | HEAD03[6]      | HEAD03[5]      | HEAD03[4]      | HEAD03[3]      | HEAD03[2]      | HEAD03[1]       | HEAD03[0]       |