# E. Renesas Electronics America Inc - <u>R5S72640P144FP#UZ Datasheet</u>

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2 0 0 0 0 0                |                                                                                    |

|----------------------------|------------------------------------------------------------------------------------|

| Product Status             | Last Time Buy                                                                      |

| Core Processor             | SH2A-FPU                                                                           |

| Core Size                  | 32-Bit Single-Core                                                                 |

| Speed                      | 144MHz                                                                             |

| Connectivity               | I <sup>2</sup> C, SCI, SD, SIO, SPI, USB                                           |

| Peripherals                | DMA, POR, PWM, WDT                                                                 |

| Number of I/O              | 115                                                                                |

| Program Memory Size        | -                                                                                  |

| Program Memory Type        | ROMIess                                                                            |

| EEPROM Size                | -                                                                                  |

| RAM Size                   | 1M x 8                                                                             |

| Voltage - Supply (Vcc/Vdd) | 1.1V ~ 3.6V                                                                        |

| Data Converters            | A/D 8x10b                                                                          |

| Oscillator Type            | External                                                                           |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                  |

| Mounting Type              | Surface Mount                                                                      |

| Package / Case             | 208-LQFP                                                                           |

| Supplier Device Package    | 208-LFQFP (28x28)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r5s72640p144fp-uz |

|                            |                                                                                    |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 5.7 Oscillation Stabilizing Time

#### 5.7.1 Oscillation Stabilizing Time of the On-chip Crystal Oscillator

In the case of using a crystal resonator, please wait longer than the oscillation stabilizing time at the following cases, to keep the oscillation stabilizing time of the on-chip crystal oscillator (In the case of inputting an external clock input, it is not necessary).

- Power on

- Releasing the software standby mode or deep standby mode by RES pin

- Changing from halting oscillation to running oscillation by power-on reset or register setting (AUDIO\_X1, RTC\_X1)

- Changing the gain of the on-chip crystal oscillator by  $\overline{\text{RES}}$  pin (EXTAL)

#### 5.7.2 Oscillation Stabilizing Time of the PLL circuit

The clock from EXTAL in the clock mode 0 and 2 or USB\_X1 in the clock mode 1 and 3 is supplied to the PLL circuit. So, regardless of whether using a crystal resonator or inputting an external clock from EXTAL (clock mode 0 and 2) or USB\_X1 (clock mode 1 and 3), please wait longer than the oscillation stabilizing time at the following cases, to keep the oscillation stabilizing time of the PLL circuit.

- Power on (in the case of using the crystal resonator)/start inputting external clock (in the case of inputting the external clock)

- Releasing the software standby mode or deep standby mode by  $\overline{\text{RES}}$  pin

#### [Remarks]

The oscillation stabilizing time is kept by the counter running in the LSI at the following cases.

- Releasing the software standby mode or deep standby mode by the other than  $\overline{\text{RES}}$  pin

- Changing the gain of the on-chip crystal oscillator by the register setting (EXTAL)

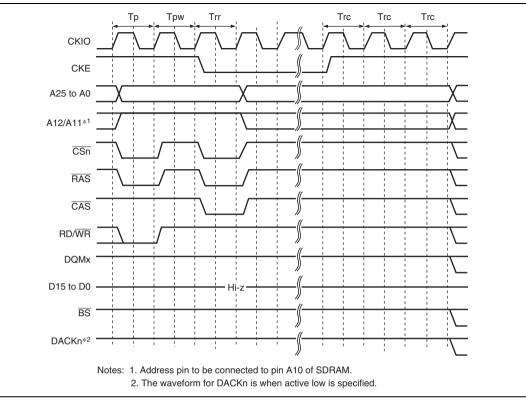

Figure 9.27 Self-Refresh Timing

#### Table 11.14 TIOR\_2 (Channel 2)

|               |               |               |               | Description        |                                |  |  |  |

|---------------|---------------|---------------|---------------|--------------------|--------------------------------|--|--|--|

| Bit 7<br>IOB3 | Bit 6<br>IOB2 | Bit 5<br>IOB1 | Bit 4<br>IOB0 | TGRB_2<br>Function | TIOC2B Pin Function            |  |  |  |

| 0             | 0             | 0             | 0             | Output             | Output retained*               |  |  |  |

|               |               |               | 1             | compare            | Initial output is 0            |  |  |  |

|               |               |               |               | register           | 0 output at compare match      |  |  |  |

|               |               | 1             | 0             | _                  | Initial output is 0            |  |  |  |

|               |               |               |               |                    | 1 output at compare match      |  |  |  |

|               |               |               | 1             |                    | Initial output is 0            |  |  |  |

|               |               |               |               |                    | Toggle output at compare match |  |  |  |

|               | 1             | 0             | 0             | _                  | Output retained                |  |  |  |

|               |               |               | 1             | _                  | Initial output is 1            |  |  |  |

|               |               |               |               |                    | 0 output at compare match      |  |  |  |

|               |               | 1             | 0             | _                  | Initial output is 1            |  |  |  |

|               |               |               |               |                    | 1 output at compare match      |  |  |  |

|               |               |               | 1             |                    | Initial output is 1            |  |  |  |

|               |               |               |               |                    | Toggle output at compare match |  |  |  |

| 1             | Х             | 0             | 0             |                    | Input capture at rising edge   |  |  |  |

|               |               |               | 1             | register           | Input capture at falling edge  |  |  |  |

|               |               | 1             | Х             | _                  | Input capture at both edges    |  |  |  |

| [Legen        | d]            |               |               |                    |                                |  |  |  |

#### Description

[Legend]

X: Don't care

Note: \* After power-on reset, 0 is output until TIOR is set.

#### 11.3.24 Timer Cycle Buffer Register (TCBR)

TCBR is a 16-bit register used only in complementary PWM mode. It functions as a buffer register for the TCDR register. The TCBR register values are transferred to the TCDR register with the transfer timing set in the TMDR register. The initial value of TCBR is H'FFFF.

| Bit: 15          | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|------------------|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

|                  |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|                  |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| Initial value: 1 | 1  | 1  | 1  | 1  | 1  | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

Note: Accessing the TCBR in 8-bit units is prohibited. Always access in 16-bit units.

#### 11.3.25 Timer Interrupt Skipping Set Register (TITCR)

TITCR is an 8-bit readable/writable register that enables or disables interrupt skipping and specifies the interrupt skipping count. This module has one TITCR.

| Bit:           | 7     | 6   | 5       | 4   | 3     | 2   | 1       | 0   |

|----------------|-------|-----|---------|-----|-------|-----|---------|-----|

|                | T3AEN | 3/  | ACOR[2: | 0]  | T4VEN | 4   | VCOR[2: | 0]  |

| Initial value: | 0     | 0   | 0       | 0   | 0     | 0   | 0       | 0   |

| R/W:           | R/W   | R/W | R/W     | R/W | R/W   | R/W | R/W     | R/W |

| Bit    | Bit Name   | Initial<br>value | R/W | Description                                                                           |

|--------|------------|------------------|-----|---------------------------------------------------------------------------------------|

| 7      | T3AEN      | 0                | R/W | T3AEN                                                                                 |

|        |            |                  |     | Enables or disables TGIA_3 interrupt skipping.                                        |

|        |            |                  |     | 0: TGIA_3 interrupt skipping disabled                                                 |

|        |            |                  |     | 1: TGIA_3 interrupt skipping enabled                                                  |

| 6 to 4 | 3ACOR[2:0] | 000              | R/W | These bits specify the TGIA_3 interrupt skipping count within the range from 0 to 7.* |

|        |            |                  |     | For details, see table 11.38.                                                         |

| 3      | T4VEN      | 0                | R/W | T4VEN                                                                                 |

|        |            |                  |     | Enables or disables TCIV_4 interrupt skipping.                                        |

|        |            |                  |     | 0: TCIV_4 interrupt skipping disabled                                                 |

|        |            |                  |     | 1: TCIV_4 interrupt skipping enabled                                                  |

| Bit | Bit Name | Initial<br>Value | R/W   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----|----------|------------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | WRE      | 0                | R/(W) | Initial Output Suppression Enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|     |          |                  | ,     | Selects the waveform output when synchronous<br>counter clearing occurs in complementary PWM mode.<br>The initial output is suppressed only when synchronous<br>clearing occurs within the Tb interval at the trough in<br>complementary PWM mode. When synchronous<br>clearing occurs outside this interval, the initial value<br>specified in TOCR is output regardless of the WRE bit<br>setting. The initial value is also output when<br>synchronous clearing occurs in the Tb interval at the<br>trough immediately after TCNT_3 and TCNT_4 start<br>operation. |

|     |          |                  |       | For the Tb interval at the trough in complementary PWM mode, see figure 11.40.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|     |          |                  |       | 0: Outputs the initial value specified in TOCR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|     |          |                  |       | 1: Suppresses initial output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|     |          |                  |       | [Setting condition]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|     |          |                  |       | • When 1 is written to WRE after reading WRE = 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

Note: \* Do not set to 1 when complementary PWM mode is not selected.

#### 11.3.30 Bus Master Interface

The timer counters (TCNT), general registers (TGR), timer subcounter (TCNTS), timer cycle buffer register (TCBR), timer dead time data register (TDDR), timer cycle data register (TCDR), timer A/D converter start request control register (TADCR), timer A/D converter start request cycle set registers (TADCOR), and timer A/D converter start request cycle set buffer registers (TADCOBR) are 16-bit registers. A 16-bit data bus to the bus master enables 16-bit read/writes. 8-bit read/write is not possible. Always access in 16-bit units.

All registers other than the above registers are 8-bit registers. These are connected to the CPU by a 16-bit data bus, so 16-bit read/writes and 8-bit read/writes are both possible.

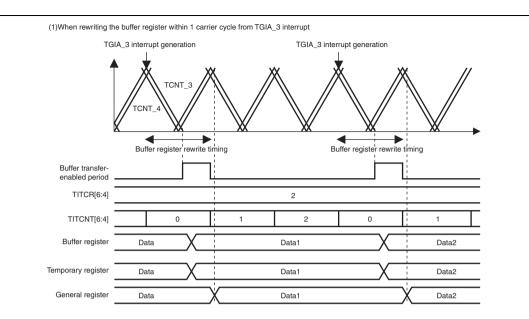

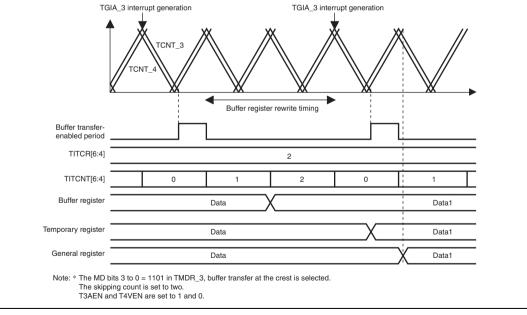

(2)When rewriting the buffer register after passing 1 carrier cycle from TGIA\_3 interrupt

Figure 11.71 Example of Operation when Buffer Transfer is Linked with Interrupt Skipping (BTE1 = 1 and BTE0 = 0)

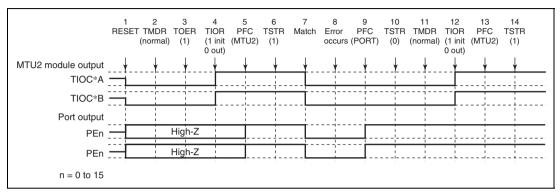

#### (1) Operation when Error Occurs during Normal Mode Operation, and Operation is Restarted in Normal Mode

Figure 11.115 shows an explanatory diagram of the case where an error occurs in normal mode and operation is restarted in normal mode after re-setting.

#### Figure 11.115 Error Occurrence in Normal Mode, Recovery in Normal Mode

- 1. After a reset, the module output is low and ports are in the high-impedance state.

- 2. After a reset, the TMDR setting is for normal mode.

- 3. For channels 3 and 4, enable output with TOER before initializing the pins with TIOR.

- 4. Initialize the pins with TIOR. (The example shows initial high output, with low output on compare-match occurrence.)

- 5. Set the multi-function timer pulse unit 2 output with the general I/O port.

- 6. The count operation is started by TSTR.

- 7. Output goes low on compare-match occurrence.

- 8. An error occurs.

- 9. Set port output with the general I/O port and output the inverse of the active level.

- 10. The count operation is stopped by TSTR.

- 11. Not necessary when restarting in normal mode.

- 12. Initialize the pins with TIOR.

- 13. Set the multi-function timer pulse unit 2 output with the general I/O port.

- 14. Operation is restarted by TSTR.

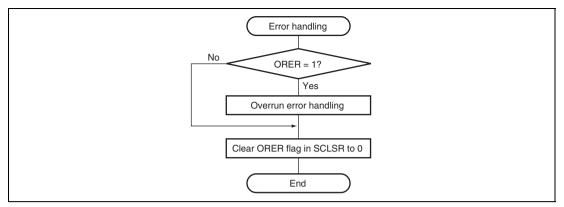

In serial reception, this module operates as described below.

- 1. Reception is started in synchronization with serial clock input or output.

- Receive data is shifted into SCRSR in order from the LSB to the MSB. After the data reception, whether the receive data can be loaded from SCRSR into SCFRDR or not is checked. If this check is passed, the RDF flag is set to 1 and the received data is stored in SCFRDR. If the check is not passed (overrun error is detected), further reception is prevented.

- 3. After setting RDF to 1, if the receive FIFO data full interrupt enable bit (RIE) is set to 1 in SCSCR, a receive-data-full interrupt (RXI) request is generated. If the ORER bit is set to 1 and the receive-data-full interrupt enable bit (RIE) or the receive error interrupt enable bit (REIE) in SCSCR is also set to 1, a break interrupt (BRI) request is generated.

#### 15.6.3 Restriction on Direct Memory Controller Usage

When the direct memory access controller writes data to SCFTDR due to a TXI interrupt request, the state of the TEND flag becomes undefined. Therefore, the TEND flag should not be used as the transfer end flag in such a case.

#### 15.6.4 Break Detection and Processing

Break signals can be detected by reading the RxD pin directly when a framing error (FER) is detected. In the break state the input from the RxD pin consists of all 0s, so the FER flag is set and the parity error flag (PER) may also be set.

Note that, although transfer of receive data to SCFRDR is halted in the break state, the receive operation is continued.

#### 15.6.5 Sending a Break Signal

The I/O condition and level of the TxD pin are determined by the SPB2IO and SPB2DT bits in the serial port register (SCSPTR). This feature can be used to send a break signal.

Until TE bit is set to 1 (enabling transmission) after initializing, the TxD pin does not work. During the period, mark status is performed by the SPB2DT bit. Therefore, the SPB2IO and SPB2DT bits should be set to 1 (high level output).

To send a break signal during serial transmission, clear the SPB2DT bit to 0 (designating low level), then clear the TE bit to 0 (halting transmission). When the TE bit is cleared to 0, the transmitter is initialized regardless of the current transmission state, and 0 is output from the TxD pin.

#### 15.6.6 Receive Data Sampling Timing and Receive Margin (Asynchronous Mode)

This module operates on a base clock with a frequency 16 or 8 times the bit rate. In reception, the falling edge of the start bit is sampled at the base clock to perform synchronization internally. Receive data is latched at the rising edge of the eighth or fourth base clock pulse. When this module operates on a base clock with a frequency 16 times the bit rate, the receive data is sampled at the timing shown in figure 15.19.

## 16.4 Operation

In this section, the serial transfer period means a period from the beginning of driving valid data to the fetching of the final valid data.

## 16.4.1 Overview of Operations

This module is capable of serial transfers in slave mode and master mode. A particular mode of this module can be selected by using the MSTR bit in the control register (SPCR). Table 16.4 gives the relationship between the modes and SPCR settings, and a description of each mode.

| Mode                               | Slave (SPI Operation)                 | Master (SPI Operation)                  |

|------------------------------------|---------------------------------------|-----------------------------------------|

| MSTR bit setting                   | 0                                     | 1                                       |

| MODFEN bit setting                 | 0 or 1                                | 0                                       |

| RSPCK signal                       | Input                                 | Output                                  |

| MOSI signal                        | Input                                 | Output                                  |

| MISO signal                        | Output/Hi-Z                           | Input                                   |

| SSL signal                         | Input                                 | Output                                  |

| SSL polarity modification function | Supported                             | Supported                               |

| Transfer rate                      | Up to B <sub>\$\phi</sub> /8          | Up to B∳/2                              |

| Clock source                       | RSPCK input                           | On-chip baud rate generator             |

| Clock polarity                     | Тwo                                   | Two                                     |

| Clock phase                        | Тwo                                   | Two                                     |

| First transfer bit                 | MSB/LSB                               | MSB/LSB                                 |

| Transfer data length               | 8 to 32 bits                          | 8 to 32 bits                            |

| Burst transfer                     | Possible (CPHA = 1)                   | Possible (CPHA = 0,1)                   |

| RSPCK delay control                | Not supported                         | Supported                               |

| SSL negation delay control         | Not supported                         | Supported                               |

| Next-access delay control          | Not supported                         | Supported                               |

| Transfer activation method         | SSL input active or RSPCK oscillation | Transmit buffer is written when SPE = 1 |

| Sequence control                   | Not supported                         | Supported                               |

Table 16.4

Relationship between Modes and SPCR and Description of Each Mode

## **19.3** Register Descriptions

Table 19.2 shows the register configuration.

#### Table 19.2 Register Configuration

| Register Name                 | Abbreviation | R/W  | Initial Value | Address    | Access<br>Size |

|-------------------------------|--------------|------|---------------|------------|----------------|

| Mode register                 | SIMDR        | R/W  | H'8000        | H'FFFF4800 | 16             |

| Clock select register         | SISCR        | R/W  | H'8000        | H'FFFF4802 | 16             |

| Transmit data assign register | SITDAR       | R/W  | H'0000        | H'FFFF4804 | 16             |

| Receive data assign register  | SIRDAR       | R/W  | H'0000        | H'FFFF4806 | 16             |

| Control register              | SICTR        | R/W  | H'0000        | H'FFFF480C | 16             |

| FIFO control register         | SIFCTR       | R/W* | H'1000        | H'FFFF4810 | 16             |

| Status register               | SISTR        | R/W* | H'0000        | H'FFFF4814 | 16             |

| Interrupt enable register     | SIIER        | R/W  | H'0000        | H'FFFF4816 | 16             |

| Transmit data register        | SITDR        | W    | Undefined     | H'FFFF4820 | 8, 16, 32      |

| Receive data register         | SIRDR        | R    | Undefined     | H'FFFF4824 | 8, 16, 32      |

|                               |              |      |               |            |                |

Note: \* This register has readable/writable bits and read-only bits. For details, see descriptions for each register.

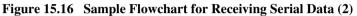

#### Figure 20.20 Time Slave

• Function to be implemented by software

Some of the TTCAN functions need to be implemented in software. The main details are reported hereafter. Please refer to ISO-11898-4 for more details.

- Change from Init\_Watch\_Trigger to Watch\_Trigger

This module offers the two registers TCMR0 and TCMR2 as H/W support for Init\_Watch\_Trigger and Watch\_Trigger respectively. The SW is requested to enable TCMR0 and disable TCMR2 up to the first reference message is detected on the CAN Bus and then disable TCMR0 and enable TCMR2.- Schedule Synchronization state machine.

Only reception of Next\_is\_Gap interrupt is supported. The application needs to take care of stopping all transmission at the end of the current basic cycle by setting the related TXCR flags.Master-Slave Mode control.

Only automatic cycle time synchronization and CCR increment is supported.

— Message status count

Software has to count scheduling errors for periodic messages in exclusive windows.

|          |            | Initial |     |                                                                      |

|----------|------------|---------|-----|----------------------------------------------------------------------|

| Bit      | Bit Name   | Value   | R/W | Description                                                          |

| 23 to 20 | CHNO[3:0]  | All 0   | W   | Channel Number                                                       |

|          |            |         |     | 0000: Don't care                                                     |

|          |            |         |     | 0001: A (left channel)                                               |

|          |            |         |     | 0010: B (right channel)                                              |

|          |            |         |     | 0011: C                                                              |

| 19 to 16 | SRCNO[3:0] | All 0   | W   | Source Number                                                        |

|          |            |         |     | 0000: Don't care                                                     |

|          |            |         |     | 0001: 1                                                              |

|          |            |         |     | 0010: 2                                                              |

|          |            |         |     | 0011: 3                                                              |

| 15 to 8  | CATCD[7:0] | All 0   | W   | Category Code (Example)                                              |

|          |            |         |     | 00000000: 2-channel general format                                   |

|          |            |         |     | 00000001: 2-channel compact disc (IEC 908)                           |

|          |            |         |     | 00000010: 2-channel PCM encoder/decoder                              |

|          |            |         |     | 00000011: 2-channel digital audio tape recorder                      |

| 7, 6     |            | All 0   | W   | Reserved                                                             |

|          |            |         |     | The write value should always be 0.                                  |

| 5 to 1   | CTL[4:0]   | All 0   | W   | Control                                                              |

|          |            |         |     | The control bits are copied from the source (see IEC60958 standard). |

| 0        |            | 0       | W   | Reserved                                                             |

|          |            |         |     | The write value should always be 0.                                  |

| -        |            |         |     | •                                                                    |

Notes: 1. Channel status data requests do not support DMA.

2. When receiver user buffer overrun occurs, the current data in the buffer data of SPDIF is overwritten by the next incoming data from SPDIF interface.

#### 22.9.2 Receiver Module Initialization

The device defaults to an idle state when it comes out of reset, or can be put into an idle state by writing 0 to bit RME in the CTRL register. Whilst idle the module has the following settings:

- The receiver idle status bit is set to 1, all other status bits are cleared to 0.

- Synchronization between channels 1 and 2 is set to 0 (0 for channel 1, 1 for channel 2).

- Both Word\_count and frame\_count are set to 0.

Channel status registers, user data registers and audio data registers will retain its value prior to putting the module into idle. To exit the idle state the user must write 1 to the bit RME in the CTRL register.

#### 22.9.3 Receiver Module Data Transfer

Once the module has left the idle state it is ready for data transfer. Data transfer timing can be achieved in three ways. The transfer can be done by interrupts, or by polling the status register, or by DMA. There is a shared interrupt line (transmit and receive) and a single receiver DMA request line. Data transfer for the receiver can be interrupted by error signals caused by:

- 1. Clock recovery failure.

- 2. Transmission loss or interference indicated by a preamble error.

- 3. Parity check failure.

Transmission loss or interference can cause the start of subframe or start of block preamble to be misplaced or not present.

Parity check failure occurs when the parity bit is incorrect, this can be caused by any of the above.

RENESAS

Clock Recovery Deviation

The receive margin for clock recovery is based on the following equation:

$$M = \left| \left( 0.5 - \frac{1}{2N} \right) - (L - 0.5) F - \frac{|D - 0.5|}{N} (1 + F) \right| \times 100\%$$

## 24.3.2 A/D Control/Status Register (ADCSR)

ADCSR is a 16-bit readable/writable register that selects the mode, controls the A/D converter, and enables or disables starting of A/D conversion by external trigger input.

| Initial value: 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0  | Bit: | 15  | 14   | 13       | 12       | 11       | 10       | 9        | 8        | 7        | 6        | 5        | 4        | 3        | 2        | 1        | 0        |

|-----------------------------------------------------|------|-----|------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|

|                                                     |      | ADF | ADIE | ADST     |          | TR       | GS[3:0]  |          |          | CKS[2:0  | ]        |          | MDS[2:0  | ]        |          | CH[2:0]  |          |

| R/W:R/(W)*1 R/W |      | -   | 0    | 0<br>R/W | 0<br>B/W | 0<br>R/W | 0<br>B/W | 0<br>B/W |

Note: \*1 Only 0 can be written to clear the flag after 1 is read.

| Bit | Bit Name | Initial<br>Value | R/W                 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-----|----------|------------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15  | ADF      | 0                | R/(W)* <sup>1</sup> | <ul> <li>A/D End Flag</li> <li>Status flag indicating the end of A/D conversion.</li> <li>[Clearing conditions]</li> <li>Cleared by reading ADF while ADF = 1, then writing 0 to ADF</li> <li>Cleared when the direct memory access controller is activated by ADI interrupt and ADDR is read</li> <li>[Setting conditions]</li> <li>A/D conversion ends in single mode</li> <li>A/D conversion ends for the selected channels in multi mode</li> <li>A/D conversion ends for the selected channels in scan mode</li> </ul> |

| 14  | ADIE     | 0                | R/W                 | <ul> <li>A/D Interrupt Enable</li> <li>Enables or disables the interrupt (ADI) requested at the end of A/D conversion. Set the ADIE bit while A/D conversion is not being made.</li> <li>0: A/D end interrupt request (ADI) is disabled</li> <li>1: A/D end interrupt request (ADI) is enabled</li> </ul>                                                                                                                                                                                                                   |

condition as when BVAL = 1). Whether to sample the DMA transfer end signal can be specified through the TENDE bit in DnFBCFG.

Note that this function cannot be used when the DMA transfer size is set to 16 bytes.

#### (c) DnFIFO Auto Clear Mode (D0FIFO/D1FIFO Port Reading Direction)

If 1 is set for the DCLRM bit in DnFIFOSEL, the module automatically clears the buffer memory of the selected pipe when reading of the data from the buffer memory has been completed.

Table 26.25 shows the packet reception and buffer memory clearing processing for each of the various settings. As shown, the buffer clear conditions depend on the value set to the BFRE bit. Using the DCLRM bit eliminates the need for the buffer to be cleared even if a situation occurs that necessitates clearing of the buffer. This makes it possible to carry out DMA transfers without involving software.

This function can be set only in the buffer memory reading direction.

|                               | Register Setting           |                            |                               |                               |  |  |  |  |  |

|-------------------------------|----------------------------|----------------------------|-------------------------------|-------------------------------|--|--|--|--|--|

| Buffer Status                 | DCL                        | RM = 0                     | DCL                           | RM = 1                        |  |  |  |  |  |

| When Packet is Received       | BFRE = 0                   | BFRE = 1                   | BFRE = 0                      | BFRE = 1                      |  |  |  |  |  |

| Buffer full                   | Doesn't need to be cleared | Doesn't need to be cleared | Doesn't need to be cleared    | Doesn't need<br>to be cleared |  |  |  |  |  |

| Zero-length packet reception  | Needs to be<br>cleared     | Needs to be<br>cleared     | Doesn't need to be cleared    | Doesn't need to be cleared    |  |  |  |  |  |

| Normal short packet reception | Doesn't need to be cleared | Needs to be<br>cleared     | Doesn't need<br>to be cleared | Doesn't need<br>to be cleared |  |  |  |  |  |

| Transaction count ended       | Doesn't need to be cleared | Needs to be cleared        | Doesn't need to be cleared    | Doesn't need to be cleared    |  |  |  |  |  |

#### Table 26.25 Packet Reception and Buffer Memory Clearing Processing

#### Table 32.9 Multiplexed Pins (Port H)

|                  | 0          | 1          |  |  |  |

|------------------|------------|------------|--|--|--|

| Setting Register | Function 1 | Function 2 |  |  |  |

| PHCR1            | PH7        | AN7        |  |  |  |

|                  | PH6        | AN6        |  |  |  |

|                  | PH5        | AN5        |  |  |  |

|                  | PH4        | AN4        |  |  |  |

| PHCR0            | PH3        | AN3        |  |  |  |

|                  | PH2        | AN2        |  |  |  |

|                  | PH1        | AN1        |  |  |  |

|                  | PH0        | ANO        |  |  |  |

Setting Mode Bit (PHnMD)

#### Table 32.10 Multiplexed Pins (Port J)

|                  | Setting Mode Bit (PJnMD[2:0]) |            |            |             |            |            |  |

|------------------|-------------------------------|------------|------------|-------------|------------|------------|--|

|                  | 000                           | 001        | 010        | 011         | 100        | 101        |  |

| Setting Register | Function 1                    | Function 2 | Function 3 | Function 4  | Function 5 | Function 6 |  |

| PJCR2            | PJ11                          | PWM2H      | DACK1      | _           | _          |            |  |

|                  | PJ10                          | PWM2G      | DREQ1      |             | _          | —          |  |

|                  | PJ9                           | PWM2F      | TEND1      | AUDIO_XOUT* | _          | —          |  |

|                  | PJ8                           | PWM2E      | RTS3       | _           | _          | —          |  |

| PJCR1            | PJ7                           | TIOC1B     | CTS3       |             | _          | —          |  |

|                  | PJ6                           | TIOC1A     | SCK3       |             | _          | —          |  |

|                  | PJ5                           | IERxD      | TxD3       | _           | _          |            |  |

|                  | PJ4                           | IETxD      | RxD3       |             | _          | —          |  |

| PJCR0            | PJ3                           | CRx1       | CRx0/CRx1  | IRQ1        | _          | _          |  |

|                  | PJ2                           | CTx1       | CTx0&CTx1  | CS2         | SCK0       | LCD_M_DISP |  |

|                  | PJ1                           | CRx0       | IERxD      | IRQ0        | RxD0       |            |  |

|                  | PJ0                           | CTx0       | IETxD      | CS1         | TxD0       | A0         |  |

| Bit    | Bit Name   | Initial Value | R/W | Description                                                          |                         |  |  |  |

|--------|------------|---------------|-----|----------------------------------------------------------------------|-------------------------|--|--|--|

| 13, 12 | PB7MD[1:0] | 00/01         | R/W | PB7 Mode                                                             |                         |  |  |  |

|        |            |               |     | Select the function of the PB7.                                      |                         |  |  |  |

|        |            |               |     | Boot mode 0                                                          | Boot mode 1 to 3        |  |  |  |

|        |            |               |     | 00: Setting prohibited                                               | 00: PB7 (initial mode)  |  |  |  |

|        |            |               |     | 01: A7 (initial value)                                               | 01: A7 (initial value)  |  |  |  |

|        |            |               |     | 10: Setting prohibited                                               | 10: TIOC0D              |  |  |  |

|        |            |               |     | 11: Setting prohibited                                               | 11: Setting prohibited  |  |  |  |

| 11, 10 | _          | All 0         | R   | Reserved                                                             |                         |  |  |  |

|        |            |               |     | These bits are always i<br>value should always be                    |                         |  |  |  |

| 9, 8   | PB6MD[1:0] | 00/01         | R/W | PB6 Mode                                                             |                         |  |  |  |

|        |            |               |     | Select the function of the                                           | ne PB6.                 |  |  |  |

|        |            |               |     | Boot mode 0                                                          | Boot mode 1 to 3        |  |  |  |

|        |            |               |     | 00: Setting prohibited                                               | 00: PB6 (initial value) |  |  |  |

|        |            |               |     | 01: A6 (initial value)                                               | 01: A6 (initial value)  |  |  |  |

|        |            |               |     | 10: Setting prohibited                                               | 10: TIOC0C              |  |  |  |

|        |            |               |     | 11: Setting prohibited                                               | 11: Setting prohibited  |  |  |  |

| 7, 6   |            | All 0         | R   | Reserved                                                             |                         |  |  |  |

|        |            |               |     | These bits are always read as 0. The write value should always be 0. |                         |  |  |  |

| 5, 4   | PB5MD[1:0] | 00/01         | R/W | PB5 Mode                                                             |                         |  |  |  |

|        |            |               |     | Select the function of the                                           | ne PB5.                 |  |  |  |

|        |            |               |     | Boot mode 0                                                          | Boot mode 1 to 3        |  |  |  |

|        |            |               |     | 00: Setting prohibited                                               | 00: PB5 (initial value) |  |  |  |

|        |            |               |     | 01: A5 (initial value)                                               | 01: A5 (initial value)  |  |  |  |

|        |            |               |     | 10: Setting prohibited                                               | 10: TIOC0B              |  |  |  |

|        |            |               |     | 11: Setting prohibited                                               | 11: Setting prohibited  |  |  |  |

| 3, 2   |            | All 0         | R   | Reserved                                                             |                         |  |  |  |

|        |            |               |     | These bits are always read as 0. The write value should always be 0. |                         |  |  |  |

## Table 37.2 DC Characteristics (8) [USB 2.0 Host/Function Module-Related Pins\* (High-Speed)]

| Item                                                       | Symbol  | Min.  | Тур. | Max. | Unit | Test<br>Conditions |

|------------------------------------------------------------|---------|-------|------|------|------|--------------------|

| Squelch detection threshold voltage (differential voltage) | VHSSQ   | 100   |      | 150  | mV   |                    |

| Common mode voltage range                                  | VHSCM   | -50   |      | 500  | mV   |                    |

| Idle state                                                 | VHSOI   | -10.0 |      | 10.0 | mV   |                    |

| Output high voltage                                        | Vнsoн   | 360   | —    | 440  | mV   |                    |

| Output low voltage                                         | VHSOL   | -10.0 |      | 10.0 | mV   |                    |

| Chirp J output voltage (difference)                        | VCHIRPJ | 700   |      | 1100 | mV   |                    |

| Chirp K output voltage (difference)                        | Vсніврк | -900  | _    | -500 | mV   |                    |

| Note: * DP and DM pins                                     |         |       |      |      |      |                    |

Table 37.3

Permissible Output Currents

| Item                                      |                              | Symbol                            | Min. | Тур. | Max. | Unit |

|-------------------------------------------|------------------------------|-----------------------------------|------|------|------|------|

| Permissible output low                    | PE5 to PE0                   | I <sub>ol</sub>                   | _    | _    | 10   | mA   |

| current (per pin)                         | Output pins other than above |                                   |      |      | 2    | mA   |

| Permissible output low current (total)    |                              | $\Sigma I_{OL}$                   |      | _    | 150  | mA   |

| Permissible output high current (per pin) |                              | $-\mathbf{I}_{OH}$                |      | _    | 2    | mA   |

| Permissible output high current (total)   |                              | $\Sigma - \mathbf{I}_{\text{OH}}$ |      |      | 150  | mA   |

Caution: To protect the LSI's reliability, do not exceed the output current values in table 37.3.

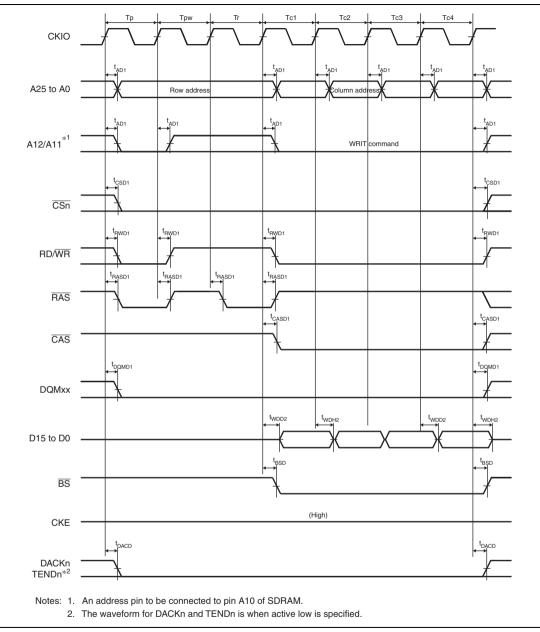

## Figure 37.30 Synchronous DRAM Burst Write Bus Cycle (Four Write Cycles) (Bank Active Mode: PRE + ACT + WRITE Commands, Different Row Addresses, WTRCD = 0 Cycle, TRWL = 0 Cycle)