# E·XFL Renesas Electronics America Inc - <u>R5S72645P144FP#UZ Datasheet</u>

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Last Time Buy                                                                      |

|----------------------------|------------------------------------------------------------------------------------|

| Core Processor             | SH2A-FPU                                                                           |

| Core Size                  | 32-Bit Single-Core                                                                 |

| Speed                      | 144MHz                                                                             |

| Connectivity               | CANbus, I <sup>2</sup> C, SCI, SD, SIO, SPI, USB                                   |

| Peripherals                | DMA, POR, PWM, WDT                                                                 |

| Number of I/O              | 115                                                                                |

| Program Memory Size        | -                                                                                  |

| Program Memory Type        | ROMIess                                                                            |

| EEPROM Size                | -                                                                                  |

| RAM Size                   | 640K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 1.1V ~ 3.6V                                                                        |

| Data Converters            | A/D 8x10b                                                                          |

| Oscillator Type            | External                                                                           |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                  |

| Mounting Type              | Surface Mount                                                                      |

| Package / Case             | 208-LQFP                                                                           |

| Supplier Device Package    | 208-LFQFP (28x28)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r5s72645p144fp-uz |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Product<br>Classification | Product Code    |             | IEBus<br>Controller | Controller<br>Area<br>Network | Operating<br>Temperature                             | Package |

|---------------------------|-----------------|-------------|---------------------|-------------------------------|------------------------------------------------------|---------|

| SH7264                    | R5S72640W144FPU | 1 Mbyte*1   | Not included        | Not included                  | Regular                                              | 208-pin |

| Group                     | R5S72641W144FPU | _           | Not included        | Included                      | specifications                                       | QFP     |

|                           | R5S72642W144FPU | _           | Included            | Not included                  | +85 °C)                                              |         |

|                           | R5S72643W144FPU | -           | Included            | Included                      | -                                                    | -       |

|                           | R5S72640P144FPU | _           | Not included        | Not included                  | Wide-range<br>specifications<br>- (-40 to<br>+85 °C) |         |

|                           | R5S72641P144FPU | -           | Not included        | Included                      |                                                      |         |

|                           | R5S72642P144FPU |             | Included            | Not included                  |                                                      |         |

|                           | R5S72643P144FPU | _           | Included            | Included                      | -                                                    |         |

|                           | R5S72644W144FPU | 640 Kbyte*2 | Not included        | Not included                  | specifications<br>(-20 to                            |         |

|                           | R5S72645W144FPU | _           | Not included        | Included                      |                                                      |         |

|                           | R5S72646W144FPU | -           | Included            | Not included                  |                                                      |         |

|                           | R5S72647W144FPU | _           | Included            | Included                      | -                                                    |         |

|                           | R5S72644P144FPU | -           | Not included        | Not included                  | Wide-range<br>specifications<br>- (-40 to            |         |

|                           | R5S72645P144FPU | _           | Not included        | Included                      |                                                      |         |

|                           | R5S72646P144FPU | _           | Included            | Not included                  | +85 °C)                                              |         |

|                           | R5S72647P144FPU | _           | Included            | Included                      | _                                                    |         |

Notes: 1. Hereinafter referred to as "1-Mbyte version" in this manual.

2. Hereinafter referred to as "640-Kbyte version" in this manual.

### 6.5.3 Interrupt Exception Handling

When an interrupt occurs, its priority level is ascertained by the interrupt controller. NMI is always accepted, but other interrupts are only accepted if they have a priority level higher than the priority level set in the interrupt mask level bits (I3 to I0) of the status register (SR).

When an interrupt is accepted, interrupt exception handling begins. In interrupt exception handling, the CPU fetches the exception service routine start address which corresponds to the accepted interrupt from the exception handling vector table, and saves SR and the program counter (PC) to the stack. In the case of interrupt exception handling other than NMI with usage of the register banks enabled, general registers R0 to R14, control register GBR, system registers MACH, MACL, and PR, and the vector table address offset of the interrupt exception handling to be executed are saved in the register banks. In the case of exception handling due to an address error, NMI interrupt, or instruction, saving is not performed to the register banks. If saving has been performed to all register banks (0 to 14), automatic saving to the stack is performed instead of register bank saving. In this case, an interrupt controller setting must have been made so that register bank overflow exceptions are not accepted (the BOVE bit in IBNR of the interrupt controller is 0). If a setting to accept register bank overflow exceptions has been made (the BOVE bit in IBNR of the interrupt controller is 1), register bank overflow exception occurs. Next, the priority level value of the accepted interrupt is written to the I3 to I0 bits in SR. For NMI, however, the priority level is 16, but the value set in the I3 to I0 bits is H'F (level 15). Then, after jumping to the start address fetched from the exception handling vector table, program execution starts. The jump that occurs is not a delayed branch. See section 7.6, Operation, for further details of interrupt exception handling.

| Register Name                  | Abbreviation | R/W | Initial<br>Value | Address    | Access<br>Size |

|--------------------------------|--------------|-----|------------------|------------|----------------|

| Interrupt priority register 18 | IPR18        | R/W | H'0000           | H'FFFE0C18 | 16, 32         |

| Interrupt priority register 19 | IPR19        | R/W | H'0000           | H'FFFE0C1A | 16, 32         |

| Interrupt priority register 20 | IPR20        | R/W | H'0000           | H'FFFE0C1C | 16, 32         |

| Interrupt priority register 21 | IPR21        | R/W | H'0000           | H'FFFE0C1E | 16, 32         |

| Interrupt priority register 22 | IPR22        | R/W | H'0000           | H'FFFE0C20 | 16, 32         |

Notes: 1. For 1-Mbyte version, when the NMI pin is high, becomes H'8000; when low, becomes H'0000. For 640-Kbyte version, when the pin is high, becomes H'8001; when low, becomes H'0001.

2. Only 0 can be written after reading 1, to clear the flag.

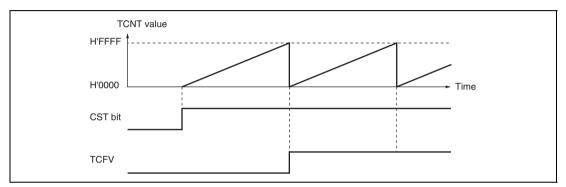

#### (b) Free-Running Count Operation and Periodic Count Operation:

Immediately after a reset, the TCNT counters of this module are all designated as free-running counters. When the relevant bit in TSTR is set to 1 the corresponding TCNT counter starts up-count operation as a free-running counter. When TCNT overflows (from H'FFFF to H'0000), the TCFV bit in TSR is set to 1. If the value of the corresponding TCIEV bit in TIER is 1 at this point, this module requests an interrupt. After overflow, TCNT starts counting up again from H'0000.

Figure 11.5 illustrates free-running counter operation.

When compare match is selected as the TCNT clearing source, the TCNT counter for the relevant channel performs periodic count operation. The TGR register for setting the period is designated as an output compare register, and counter clearing by compare match is selected by means of bits CCLR0 to CCLR2 in TCR. After the settings have been made, TCNT starts up-count operation as a periodic counter when the corresponding bit in TSTR is set to 1. When the count value matches the value in TGR, the TGF bit in TSR is set to 1 and TCNT is cleared to H'0000.

If the value of the corresponding TGIE bit in TIER is 1 at this point, this module requests an interrupt. After a compare match, TCNT starts counting up again from H'0000.

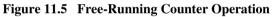

### 11.7.15 Reset Sync PWM Mode Buffer Operation and Compare Match Flag

When setting buffer operation for reset sync PWM mode, set the BFA and BFB bits of TMDR\_4 to 0. The TIOC4C pin will be unable to produce its waveform output if the BFA bit of TMDR\_4 is set to 1.

In reset sync PWM mode, the channel 3 and channel 4 buffers operate in accordance with the BFA and BFB bit settings of TMDR\_3. For example, if the BFA bit of TMDR\_3 is set to 1, TGRC\_3 functions as the buffer register for TGRA\_3. At the same time, TGRC\_4 functions as the buffer register for TGRA\_4.

The TGFC bit and TGFD bit of TSR\_3 and TSR\_4 are not set when TGRC\_3 and TGRD\_3 are operating as buffer registers.

Figure 11.109 shows an example of operations for TGR\_3, TGR\_4, TIOC3, and TIOC4, with TMDR\_3's BFA and BFB bits set to 1, and TMDR\_4's BFA and BFB bits set to 0.

Figure 11.109 Buffer Operation and Compare-Match Flags in Reset Synchronous PWM Mode

## Section 19 Serial I/O with FIFO

This LSI includes a clock-synchronized serial I/O module with FIFO.

### **19.1** Features

- Serial transfer

- 16-stage 32-bit FIFOs (independent transmission and reception)

- Supports 8-bit monaural/16-bit monaural/16-bit stereo audio input and output

- MSB first for data transmission

- Supports a maximum of 48-kHz sampling rate

- Synchronization by frame synchronization pulse

- Connectable to linear, audio, or A-Law or μ-Law CODEC chip

- Supports both master and slave modes

- Serial clock

- AUDIO\_CLK or AUDIO\_X1 can be selected as the clock source.

- Interrupts: One type

- DMA transfer: Two types

- Transmit FIFO transfer requests and receive FIFO transfer requests

| TFWM2 to<br>TFWM0 | Number of<br>Requested<br>Stages | Transmit Request Issued                        | Used Areas |

|-------------------|----------------------------------|------------------------------------------------|------------|

| 000               | 1                                | There are sixteen stages of empty area.        | Smallest   |

| 100               | 4                                | There are twelve or more stages of empty area. | ♠          |

| 101               | 8                                | There are eight or more stages of empty area.  |            |

| 110               | 12                               | There are four or more stages of empty area.   | _ ↓        |

| 111               | 16                               | There is one or more stage of empty area.      | Largest    |

#### Table 19.8 Conditions to Issue Transmit Request

#### Table 19.9 Conditions to Issue Receive Request

| RFWM2 to<br>RFWM0 | Number of<br>Requested Stages | Receive Request Issued                         | Used Areas |

|-------------------|-------------------------------|------------------------------------------------|------------|

| 000               | 1                             | There is one or more stage of valid data.      | Smallest   |

| 100               | 4                             | There are four stages of valid data or more.   | _ ♠        |

| 101               | 8                             | There are eight stages of valid data or more.  | -          |

| 110               | 12                            | There are twelve stages of valid data or more. | -          |

| 111               | 16                            | There are sixteen stages of valid data.        | Largest    |

The number of stages of the FIFO is sixteen. Accordingly, an overflow error or underflow error occurs if data area or empty area exceeds sixteen FIFO stages. The transfer request is canceled when the above condition is not satisfied even if the FIFO is not empty or full.

#### (3) Number of FIFOs

The usage state of the transmit FIFO and receive FIFO are indicated by the TFUA and FRUA bits in the FIFO control register as below:

- Transmit FIFO: The number of empty FIFO stages is indicated by the TFUA4 to TFUA0 bits in SIFCTR.

- Receive FIFO: The number of valid data stages is indicated by the RFUA4 to RFUA0 bits in SIFCTR.

The above register contents indicate the possible data numbers that can be transferred by the CPU or direct memory access controller.

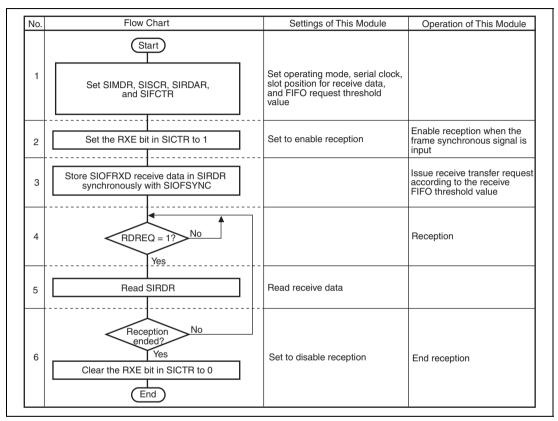

### (4) Reception in Slave Mode

Figure 19.9 shows an example of reception settings and operation when this module is used as a slave.

Figure 19.9 Example of Receive Operation in Slave Mode

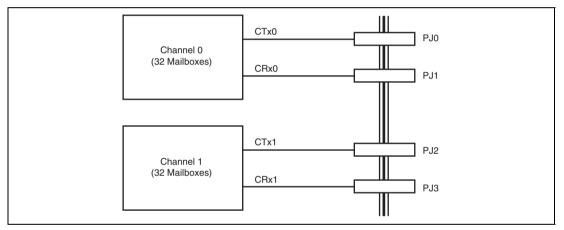

### 20.8 Setting I/O Ports

The I/O ports for this module must be specified before or during the configuration mode. For details on the settings of I/O ports, see section 32, General Purpose I/O Ports. Two methods are available using two channels of this module in this LSI.

- Using this module as a 2-channel module (channels 0 and 1) Each channel has 32 Mailboxes.

- Using this module as a 1-channel module (channels 0 and 1 functioning as a single channel)

When the second method is used, see section 20.9.1, Notes on Port Setting for Multiple Channels Used as Single Channel.

Figures 20.28 and 20.29 show connection examples for individual port settings.

Figure 20.28 Connection Example when Using This Module as 2-Channel Module (32 Mailboxes × 2 Channels)

|          |            | Initial |     |                                                                      |

|----------|------------|---------|-----|----------------------------------------------------------------------|

| Bit      | Bit Name   | Value   | R/W | Description                                                          |

| 23 to 20 | CHNO[3:0]  | All 0   | W   | Channel Number                                                       |

|          |            |         |     | 0000: Don't care                                                     |

|          |            |         |     | 0001: A (left channel)                                               |

|          |            |         |     | 0010: B (right channel)                                              |

|          |            |         |     | 0011: C                                                              |

| 19 to 16 | SRCNO[3:0] | All 0   | W   | Source Number                                                        |

|          |            |         |     | 0000: Don't care                                                     |

|          |            |         |     | 0001: 1                                                              |

|          |            |         |     | 0010: 2                                                              |

|          |            |         |     | 0011: 3                                                              |

| 15 to 8  | CATCD[7:0] | All 0   | W   | Category Code (Example)                                              |

|          |            |         |     | 00000000: 2-channel general format                                   |

|          |            |         |     | 00000001: 2-channel compact disc (IEC 908)                           |

|          |            |         |     | 00000010: 2-channel PCM encoder/decoder                              |

|          |            |         |     | 00000011: 2-channel digital audio tape recorder                      |

| 7, 6     |            | All 0   | W   | Reserved                                                             |

|          |            |         |     | The write value should always be 0.                                  |

| 5 to 1   | CTL[4:0]   | All 0   | W   | Control                                                              |

|          |            |         |     | The control bits are copied from the source (see IEC60958 standard). |

| 0        | _          | 0       | W   | Reserved                                                             |

|          |            |         |     | The write value should always be 0.                                  |

| Bit | Bit Name | Initial<br>Value | R/W | Description                                                                                                                                                                                                                                               |

|-----|----------|------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9   | DBLB     | 0                | R/W | Double Buffer Mode                                                                                                                                                                                                                                        |

|     |          |                  |     | Selects either single or double buffer mode for the FIFO buffer used by the selected pipe.                                                                                                                                                                |

|     |          |                  |     | 0: Single buffer                                                                                                                                                                                                                                          |

|     |          |                  |     | 1: Double buffer                                                                                                                                                                                                                                          |

|     |          |                  |     | This bit is valid when PIPE1 to PIPE5 are selected.                                                                                                                                                                                                       |

|     |          |                  |     | When this bit has been set to 1, this module assigns<br>two planes of the FIFO buffer size specified by the<br>BUFSIZE bits in PIPEBUF to the selected pipe.                                                                                              |

|     |          |                  |     | Specifically, the following expression determines the FIFO buffer size assigned to the selected pipe by this module.                                                                                                                                      |

|     |          |                  |     | (BUFSIZE + 1) $\times$ 64 $\times$ (DBLB + 1) [bytes]                                                                                                                                                                                                     |

|     |          |                  |     | Modify these bits while CSSTS is 0 and PID is NAK and before the pipe is selected by the CURPIPE bits.                                                                                                                                                    |

|     |          |                  |     | To modify these bits after completing USB communication using the selected pipe, write 1 and then 0 to ACLRM continuously to clear the FIFO buffer assigned to the selected pipe while the CSSTS, PID, and CURPIPE bits are in the above-described state. |

|     |          |                  |     | Before modifying these bits after modifying the PID<br>bits for the selected pipe from BUF to NAK, check<br>that CSSTS and PBUSY are 0. However, if the PID<br>bits have been modified to NAK by this module,<br>checking PBUSY is not necessary.         |

| Bit | Bit Name | Initial<br>Value | R/W  | Description                                                                                                                                                                                                                                                                                                                |

|-----|----------|------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 13  | CSCLR    | 0                | R/W* | C-SPLIT Status Clear Bit                                                                                                                                                                                                                                                                                                   |

|     |          |                  |      | When the host controller function is selected, setting this bit to 1 allows this module to clear the CSSTS bit to 0.                                                                                                                                                                                                       |

|     |          |                  |      | 0: Writing invalid                                                                                                                                                                                                                                                                                                         |

|     |          |                  |      | 1: Clears the CSSTS bit to 0.                                                                                                                                                                                                                                                                                              |

|     |          |                  |      | For the transfer using the split transaction, to restart<br>the next transfer with the S-SPLIT forcibly, set this bit<br>to 1. However, for the normal split transaction, this<br>module automatically clears the CSSTS bit to 0 upon<br>completion of the C-SPLIT; therefore, clearing the<br>CSSTS bit is not necessary. |

|     |          |                  |      | Controlling the CSSTS bit through this bit must be<br>done while UACT is 0 and thus communication is<br>halted or while no transfer is being performed with<br>bus disconnection detected.                                                                                                                                 |

|     |          |                  |      | Setting this bit to 1 while CSSTS is 0 has no effect.                                                                                                                                                                                                                                                                      |

|     |          |                  |      | When the function controller function is selected, be sure to write 0 to this bit.                                                                                                                                                                                                                                         |

| 12  | CSSTS    | 0                | R    | CSSTS Status Bit                                                                                                                                                                                                                                                                                                           |

|     |          |                  |      | Indicates the C-SPLIT status of the split transaction when the host controller function is selected.                                                                                                                                                                                                                       |

|     |          |                  |      | 0: START-SPLIT (S-SPLIT) transaction being<br>processed or the transfer not using the split<br>transaction in progress                                                                                                                                                                                                     |

|     |          |                  |      | 1: C-SPLIT transaction being processed                                                                                                                                                                                                                                                                                     |

|     |          |                  |      | This module sets this bit to 1 upon start of the C-<br>SPLIT and clears this bit to 0 upon detection of C-<br>SPLIT completion.                                                                                                                                                                                            |

|     |          |                  |      | If the USB device is detached when processing of a C-SPLIT transaction is in progress, the CSSTS bit may remain set to 1. In such a case (DTCH = 1 detected), use the CSCLR bit to clear the CSSTS bit to 0.                                                                                                               |

|     |          |                  |      | Indicates the valid value only when the host controller function is selected.                                                                                                                                                                                                                                              |

| 11  |          | 0                | R    | Reserved                                                                                                                                                                                                                                                                                                                   |

|     |          |                  |      | This bit is always read as 0. The write value should always be 0.                                                                                                                                                                                                                                                          |

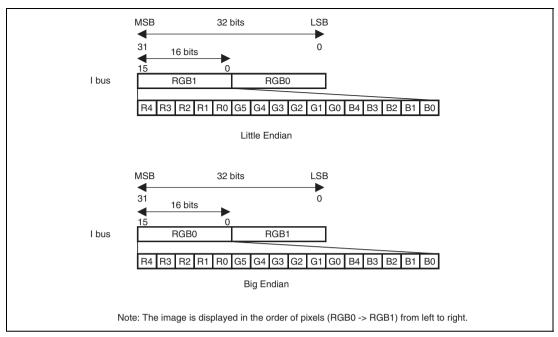

Figure 27.15 Description of Endian

#### 32.2.30 Port J Control Register 0 to 2 (PJCR0 to PJCR2)

PJCR2 to PJCR0 are 16-bit readable/writable registers that are used to select the functions of the multiplexed pins on port J.

#### Bit: 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 . PJ11MD[1:0] . PJ10MD[1:0] . PJ9MD[1:0] \_ PJ8MD[1:0] -. . 0 0 0 0 Initial value: 0 0 0 0 0 0 0 0 0 0 0 0 R R R/W R/W R R R/W· R R/W R/W R R R/W R/W R R/W R/W Bit **Bit Name Initial Value** R/W Description 15.14 All 0 R Reserved These bits are always read as 0. The write value should always be 0. 13.12 PJ11MD[1:0] R/W PJ11 Mode 00 Select the function of the PJ11. 00: PJ11 10: DACK1 01: PWM2H 11: Setting prohibited 11, 10 All 0 R Reserved These bits are always read as 0. The write value should always be 0. PJ10MD[1:0] 9,8 00 R/W PJ10 Mode Select the function of the PJ10. 00: PJ10 10: DREQ1 01: PWM2G 11: Setting prohibited 7,6 All 0 R Reserved These bits are always read as 0. The write value should always be 0. 5,4 PJ9MD[1:0] R/W PJ9 Mode 00 Select the function of the PJ9. 00: PJ9 10: TEND1 01: PWM2F 11: AUDIO XOUT (640-Kbyte version only) 3, 2 All 0 R Reserved These bits are always read as 0. The write value should always be 0.

### (1) Port J Control Register 2 (PJCR2: Available Only in the SH7264 Group)

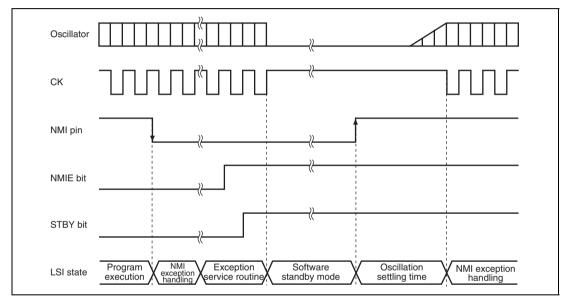

#### 33.3.3 Software Standby Mode Application Example

This example describes a transition to software standby mode on the falling edge of the NMI signal, and cancellation on the rising edge of the NMI signal. The timing is shown in figure 33.1.

When the NMI pin is changed from high to low level while the NMI edge select bit (NMIE) in the interrupt control register 0 (ICR0) is set to 0 (falling edge detection), the NMI interrupt is accepted. When the NMIE bit is set to 1 (rising edge detection) by the NMI exception service routine, the STBY and DEEP bits in STBCR1 are set to 1 and 0 respectively, and a SLEEP instruction is executed, software standby mode is entered. Thereafter, software standby mode is canceled when the NMI pin is changed from low to high level.

Figure 33.1 NMI Timing in Software Standby Mode (Application Example)

### 35.5 Operation

### 35.5.1 PWM Operation

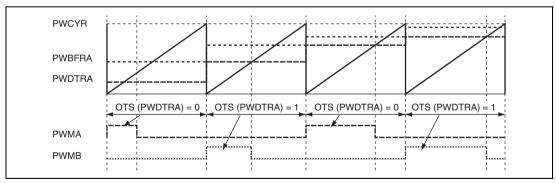

PWM waveforms are output from pins PWM1A to PWM1H and PWM2A to PWM2H as shown in figure 35.7.

### (1) Initial Settings

Set the PWM output polarity in PWPR\_n; select the clock to be input to PWCNT\_n with the CKS2 to CKS0 bits in PWCRn; set the PWM conversion cycle in PWCYR\_n; and set the first frame of data in PWBFR\_nA, PWBFR\_nC, PWBFR\_nE, and PWBFR\_nG.

### (2) Activation

When the CST bit in PWCR\_n is set to 1, PWCNT\_n starts counting up. On compare match between PWCNT\_n and PWCYR\_n, data is transferred from the buffer register to the duty register and the CMF bit in PWCR\_n is set to 1. At the same time, if the IE bit in PWCR\_n has been set to 1, an interrupt can be requested or the direct memory access controller can be activated.

### (3) Waveform Output

The PWM outputs selected by the OTS bits in PWDTR\_nA, PWDTR\_nC, PWDTR\_nE, and PWDTR\_nG go high when a compare match occurs between PWCNT\_n and PWCYR\_n. The PWM outputs not selected by the OTS bit are low. When a compare match occurs between PWCNT\_n and PWDTR\_nA, PWDTR\_nC, PWDTR\_nE, or PWDTR\_nG, the corresponding PWM output goes low. If the corresponding bit in PWPR\_n is set to 1, the output is inverted.

Figure 35.7 PWM Operation

| Module Name                    | Register Name                                    | Abbreviation | Number<br>of Bits | Address    | Access<br>Size |

|--------------------------------|--------------------------------------------------|--------------|-------------------|------------|----------------|

| I <sup>2</sup> C bus interface | I <sup>2</sup> C bus interrupt enable register_2 | ICIER_2      | 8                 | H'FFFEE803 | 8              |

| 3                              | I <sup>2</sup> C bus status register_2           | ICSR_2       | 8                 | H'FFFEE804 | 8              |

|                                | Slave address register_2                         | SAR_2        | 8                 | H'FFFEE805 | 8              |

|                                | I <sup>2</sup> C bus transmit data register_2    | ICDRT_2      | 8                 | H'FFFEE806 | 8              |

|                                | I <sup>2</sup> C bus receive data register_2     | ICDRR_2      | 8                 | H'FFFEE807 | 8              |

|                                | NF2CYC register_2                                | NF2CYC_2     | 8                 | H'FFFEE808 | 8              |

| Serial sound                   | Control register_0                               | SSICR_0      | 32                | H'FFFF0000 | 8, 16, 32      |

| interface                      | Status register_0                                | SSISR_0      | 32                | H'FFFF0004 | 8, 16, 32      |

|                                | FIFO control register_0                          | SSIFCR_0     | 32                | H'FFFF0010 | 8, 16, 32      |

|                                | FIFO status register_0                           | SSIFSR_0     | 32                | H'FFFF0014 | 8, 16, 32      |

|                                | Transmit FIFO data register 0                    | SSIFTDR_0    | 32                | H'FFFF0018 | 32             |

|                                | Receive FIFO data register 0                     | SSIFRDR_0    | 32                | H'FFFF001C | 8, 16, 32      |

|                                | Control register_1                               | SSICR_1      | 32                | H'FFFF0800 | 8, 16, 32      |

|                                | Status register_1                                | SSISR_1      | 32                | H'FFFF0804 | 8, 16, 32      |

|                                | FIFO control register_1                          | SSIFCR_1     | 32                | H'FFFF0810 | 8, 16, 32      |

|                                | FIFO status register_1                           | SSIFSR_1     | 32                | H'FFFF0814 | 8, 16, 32      |

|                                | Transmit FIFO data register 1                    | SSIFTDR_1    | 32                | H'FFFF0818 | 32             |

|                                | Receive FIFO data register 1                     | SSIFRDR_1    | 32                | H'FFFF081C | 32             |

|                                | Control register_2                               | SSICR_2      | 32                | H'FFFF1000 | 8, 16, 32      |

|                                | Status register_2                                | SSISR_2      | 32                | H'FFFF1004 | 8, 16, 32      |

|                                | FIFO control register_2                          | SSIFCR_2     | 32                | H'FFFF1010 | 8, 16, 32      |

|                                | FIFO status register_2                           | SSIFSR_2     | 32                | H'FFFF1014 | 8, 16, 32      |

|                                | Transmit FIFO data register 2                    | SSIFTDR_2    | 32                | H'FFFF1018 | 32             |

|                                | Receive FIFO data register 2                     | SSIFRDR_2    | 32                | H'FFFF101C | 32             |

|                                | Control register_3                               | SSICR_3      | 32                | H'FFFF1800 | 8, 16, 32      |

|                                | Status register_3                                | SSISR_3      | 32                | H'FFFF1804 | 8, 16, 32      |

|                                | FIFO control register_3                          | SSIFCR_3     | 32                | H'FFFF1810 | 8, 16, 32      |

|                                | FIFO status register_3                           | SSIFSR_3     | 32                | H'FFFF1814 | 8, 16, 32      |

|                                | Transmit FIFO data register 3                    | SSIFTDR_3    | 32                | H'FFFF1818 | 32             |

|                                | Receive FIFO data register 3                     | SSIFRDR_3    | 32                | H'FFFF181C | 32             |

| Module Name       | Register Name                                                           | Abbreviation | Number<br>of Bits | Address    | Access<br>Size |

|-------------------|-------------------------------------------------------------------------|--------------|-------------------|------------|----------------|

| CD-ROM<br>decoder | Pre-ECC correction subheader:<br>channel number (byte 17) data register | SHEAD01      | 8                 | H'FFFF901D | 8              |

|                   | Pre-ECC correction subheader:<br>sub-mode (byte 18) data register       | SHEAD02      | 8                 | H'FFFF901E | 8              |

|                   | Pre-ECC correction subheader:<br>data type (byte 19) data register      | SHEAD03      | 8                 | H'FFFF901F | 8              |

|                   | Pre-ECC correction subheader:<br>file number (byte 20) data register    | SHEAD04      | 8                 | H'FFFF9020 | 8              |

|                   | Pre-ECC correction subheader: channel number (byte 21) data register    | SHEAD05      | 8                 | H'FFFF9021 | 8              |

|                   | Pre-ECC correction subheader:<br>sub-mode (byte 22) data register       | SHEAD06      | 8                 | H'FFFF9022 | 8              |

|                   | Pre-ECC correction subheader:<br>data type (byte 23) data register      | SHEAD07      | 8                 | H'FFFF9023 | 8              |

|                   | Post-ECC correction header:<br>minutes data register                    | HEAD20       | 8                 | H'FFFF9024 | 8              |

|                   | Post-ECC correction header: seconds data register                       | HEAD21       | 8                 | H'FFFF9025 | 8              |

|                   | Post-ECC correction header:<br>frames (1/75 second) data register       | HEAD22       | 8                 | H'FFFF9026 | 8              |

|                   | Post-ECC correction header:<br>mode data register                       | HEAD23       | 8                 | H'FFFF9027 | 8              |

|                   | Post-ECC correction subheader:<br>file number (byte 16) data register   | SHEAD20      | 8                 | H'FFFF9028 | 8              |

|                   | Post-ECC correction subheader: channel number (byte 17) data register   | SHEAD21      | 8                 | H'FFFF9029 | 8              |

|                   | Post-ECC correction subheader:<br>sub-mode (byte 18) data register      | SHEAD22      | 8                 | H'FFFF902A | 8              |

|                   | Post-ECC correction subheader:<br>data type (byte 19) data register     | SHEAD23      | 8                 | H'FFFF902B | 8              |

|                   | Post-ECC correction subheader:<br>file number (byte 20) data register   | SHEAD24      | 8                 | H'FFFF902C | 8              |

|                   | Post-ECC correction subheader: channel number (byte 21) data register   | SHEAD25      | 8                 | H'FFFF902D | 8              |

|               | Register     |                |                | D'1 00/04/40/5 |                |                |                |               |               |

|---------------|--------------|----------------|----------------|----------------|----------------|----------------|----------------|---------------|---------------|

| Module Name   | Abbreviation | Bit 31/23/15/7 | Bit 30/22/14/6 | Bit 29/21/13/5 | Bit 28/20/12/4 | Bit 27/19/11/3 | Bit 26/18/10/2 | Bit 25/17/9/1 | Bit 24/16/8/0 |

| Video display | VIDEO_FIELD_ | VIDEO_FIEL     | VIDEO_FIEL     | VIDEO_FIEL     | VIDEO_FIEL     | VIDEO_FIEL     | VIDEO_FIEL     | VIDEO_FIEL    | VIDEO_FIEL    |

| controller 3  | OFFSET       | D_OFFSET       | D_OFFSET       | D_OFFSET       | D_OFFSET       | D_OFFSET       | D_OFFSET       | D_OFFSET      | D_OFFSET      |

|               |              | [31]           | [30]           | [29]           | [28]           | [27]           | [26]           | [25]          | [24]          |

|               |              | VIDEO_FIEL     | VIDEO_FIEL     | VIDEO_FIEL     | VIDEO_FIEL     | VIDEO_FIEL     | VIDEO_FIEL     | VIDEO_FIEL    | VIDEO_FIEL    |

|               |              | D_OFFSET       | D_OFFSET       | D_OFFSET       | D_OFFSET       | D_OFFSET       | D_OFFSET       | D_OFFSET      | D_OFFSET      |

|               |              | [23]           | [22]           | [21]           | [20]           | [19]           | [18]           | [17]          | [16]          |

|               |              | VIDEO_FIEL     | VIDEO_FIEL     | VIDEO_FIEL     | VIDEO_FIEL     | VIDEO_FIEL     | VIDEO_FIEL     | VIDEO_FIEL    | VIDEO_FIEL    |

|               |              | D_OFFSET       | D_OFFSET       | D_OFFSET       | D_OFFSET       | D_OFFSET       | D_OFFSET       | D_OFFSET[9]   | D_OFFSET[8]   |

|               |              | [15]           | [14]           | [13]           | [12]           | [11]           | [10]           |               |               |

|               |              | VIDEO_FIEL     | VIDEO_FIEL     | VIDEO_FIEL     | VIDEO_FIEL     | VIDEO_FIEL     | VIDEO_FIEL     | VIDEO_FIEL    | VIDEO_FIEL    |

|               |              | D_OFFSET[7]    | D_OFFSET[6]    | D_OFFSET[5]    | D_OFFSET[4]    | D_OFFSET[3]    | D_OFFSET[2]    | D_OFFSET[1]   | D_OFFSET[0]   |

|               | VIDEO_LINE   | _              | _              | _              | _              | _              | _              | _             | _             |

|               | BUFF_NUM     | _              | _              | _              | _              | _              | _              | _             | _             |

|               |              | _              | _              | _              |                | _              | _              | _             | VIDEO_LINE    |

|               |              |                |                |                |                |                |                |               | BUFF_NUM      |

|               |              |                |                |                |                |                |                |               | [8]           |

|               |              | VIDEO_LINE     | VIDEO_LINE     | VIDEO_LINE     | VIDEO_LINE     | VIDEO_LINE     | VIDEO_LINE     | VIDEO_LINE    | VIDEO_LINE    |

|               |              | BUFF_NUM       | BUFF_NUM       | BUFF_NUM       | BUFF_NUM       | BUFF_NUM       | BUFF_NUM       | BUFF_NUM      | BUFF_NUM      |

|               |              | [7]            | [6]            | [5]            | [4]            | [3]            | [2]            | [1]           | [0]           |

|               | VIDEO_DISP   | —              | —              | _              | _              | _              | —              | _             | VIDEO_DISP    |

|               | _SIZE        |                |                |                |                |                |                |               | _HEIGHT[8]    |

|               |              | VIDEO_DISP     | VIDEO_DISP     | VIDEO_DISP     | VIDEO_DISP     | VIDEO_DISP     | VIDEO_DISP     | VIDEO_DISP    | VIDEO_DISP    |

|               |              | _HEIGHT[7]     | _HEIGHT[6]     | _HEIGHT[5]     | _HEIGHT[4]     | _HEIGHT[3]     | _HEIGHT[2]     | _HEIGHT[1]    | _HEIGHT[0]    |

|               |              | —              | _              | _              | _              | _              | _              | VIDEO_DISP    | VIDEO_DISP    |

|               |              |                |                |                |                |                |                | _WIDTH[9]     | _WIDTH[8]     |

|               |              | VIDEO_DISP     | VIDEO_DISP     | VIDEO_DISP     | VIDEO_DISP     | VIDEO_DISP     | VIDEO_DISP     | VIDEO_DISP    | VIDEO_DISP    |

|               |              | _WIDTH[7]      | _WIDTH[6]      | _WIDTH[5]      | _WIDTH[4]      | _WIDTH[3]      | _WIDTH[2]      | _WIDTH[1]     | _WIDTH[0]     |

|               | VIDEO_DISP_  | _              |                |                |                | _              | _              |               | _             |

|               | HSTART       | _              | _              |                | _              |                | _              |               |               |

|               |              | _              | _              | _              |                | _              |                | VIDEO_DISP    | VIDEO_DISP    |

|               |              |                |                |                |                |                |                | _HSTART[9]    | _HSTART[8]    |

|               |              | VIDEO_DISP     | VIDEO_DISP     | VIDEO_DISP     | VIDEO_DISP     | VIDEO_DISP     | VIDEO_DISP     | VIDEO_DISP    | VIDEO_DISP    |

|               |              | _HSTART[7]     | _HSTART[6]     | _HSTART[5]     | _HSTART[4]     | _HSTART[3]     | _HSTART[2]     | _HSTART[1]    | _HSTART[0]    |

| UMSR11038                             |

|---------------------------------------|

| USBACSWR1 1471                        |

| USBADDR 1410                          |

| USBINDX 1413                          |

| USBLENG1414                           |

| USBREQ 1411                           |

| USBVAL                                |

| WRCSR                                 |

| WTCNT                                 |

| WTCSR                                 |

| XTALCTR                               |

| Relationship between access size      |

| and number of bursts                  |

| Relationship between refresh requests |

| and bus cycles                        |

| Renesas serial peripheral interface   |

| Renesas serial peripheral interface   |

| timing                                |

| Renesas SPDIF interface               |

| Reset sequence                        |

| Reset state                           |

| Reset-synchronized PWM mode           |

| Restoration from bank                 |

| Restoration from stack                |

| Restriction on direct memory access   |

| controller usage                      |

| RISC-type instruction set             |

| Roles of mailboxes                    |

| Rounding 105                          |

|                                       |

### S

| Sampling rate converter  | 1637 |

|--------------------------|------|

| Saving to bank           | 202  |

| Saving to stack          | 204  |

| Scan mode                | 1273 |

| SD host interface        | 1667 |

| SD host interface timing | 2040 |

| SDRAM interface          | 306  |

| Searching cache          | 218  |

| Sector access mode                    | 1327  |

|---------------------------------------|-------|

| Self-refreshing                       | 331   |

| Sending a break signal                | 772   |

| Serial bit clock control              | 936   |

| Serial communication interface        |       |

| with FIFO                             | 707   |

| Serial communication interface        |       |

| with FIFO timing                      | 2018  |

| Serial I/O with FIFO                  | 939   |

| Serial I/O with FIFO timing           | 2027  |

| Serial sound interface                |       |

| Serial sound interface timing         | 2025  |

| Setting analog input voltage          | 1282  |

| Setting I/O ports for controller area |       |

| network                               | 1080  |

| Shift instructions                    | 83    |

| Sign extension of word data           | 56    |

| Single address mode                   | 420   |

| Single mode                           | 1268  |

| Single read                           | 318   |

| Single write                          |       |

| Slave mode operation                  | 841   |

| Slave receive operation               | . 876 |

| Slave transmit operation              | 873   |

| Sleep mode 1055,                      | 1806  |

| Slot illegal instructions             | 148   |

| Software standby mode                 | 1807  |

| SRAM interface with byte selection    | 344   |

| Stack after interrupt exception       |       |

| handling                              | 194   |

| Stack status after exception          |       |

| handling ends                         | 151   |

| Standby control circuit               |       |

| Status register (SR)                  | 50    |

| Stopping and resuming CD-DSP          |       |

| operation                             |       |

| Supported DMA transfers               | 417   |

| Syndrome calculation                  | 1248  |

| System configuration example          |       |

| System control instructions           | 85    |