Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                      |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 32MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART, USB                          |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT          |

| Number of I/O              | 37                                                                    |

| Program Memory Size        | 64KB (64K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | 2K x 8                                                                |

| RAM Size                   | 8K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 3.6V                                                          |

| Data Converters            | A/D 10x12b; D/A 1x12b                                                 |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 48-LQFP                                                               |

| Supplier Device Package    | 48-LQFP (7x7)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l052c8t7 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Figure 43. | TFBGA64 – 64-ball, 5 x 5 mm, 0.5 mm pitch, thin profile fine pitch ball |     |

|------------|-------------------------------------------------------------------------|-----|

|            | ,grid array recommended footprint                                       | 119 |

| Figure 44. | TFBGA64 marking example (package top view)                              | 120 |

| Figure 45. | LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package outline         | 121 |

| Figure 46. | LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat recommended footprint   | 122 |

| Figure 47. | LQFP48 marking example (package top view)                               | 123 |

| Figure 48. | Standard WLCSP36 - 2.61 x 2.88 mm, 0.4 mm pitch wafer level chip scale  |     |

|            | package outline                                                         | 124 |

| Figure 49. | Standard WLCSP36 - 2.61 x 2.88 mm, 0.4 mm pitch wafer level chip scale  |     |

|            | recommended footprint                                                   | 125 |

| Figure 50. | Standard WLCSP36 marking example (package top view)                     | 126 |

| Figure 51. | Thin WLCSP36 - 2.61 x 2.88 mm, 0.4 mm pitch wafer level chip scale      |     |

|            | package outline                                                         | 127 |

| Figure 52. | Thin WLCSP36 - 2.61 x 2.88 mm, 0.4 mm pitch wafer level chip scale      |     |

|            | package recommended footprint                                           | 128 |

| Figure 53. | LQFP32 - 32-pin, 7 x 7 mm low-profile quad flat package outline         | 129 |

| Figure 54. | LQFP32 - 32-pin, 7 x 7 mm low-profile quad flat recommended footprint   | 130 |

| Figure 55. | LQFP32 marking example (package top view)                               | 131 |

| Figure 56. | UFQFPN32 - 32-pin, 5x5 mm, 0.5 mm pitch ultra thin fine pitch quad flat |     |

|            | package outline                                                         | 132 |

| Figure 57. | UFQFPN32 - 32-pin, 5x5 mm, 0.5 mm pitch ultra thin fine pitch quad flat |     |

|            | recommended footprint                                                   |     |

| Figure 58. | UFQFPN32 marking example (package top view)                             | 134 |

| Figure 59. | Thermal resistance                                                      | 136 |

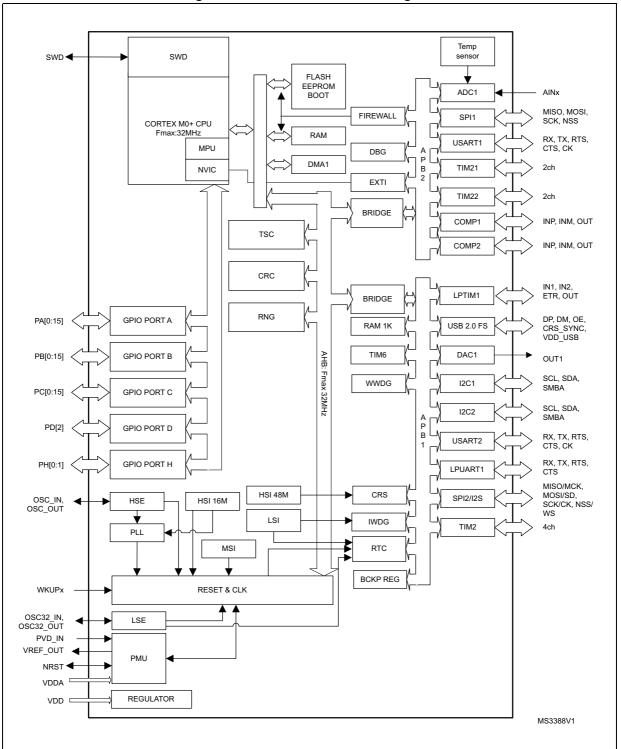

Figure 1. STM32L052x6/8 block diagram

### • Stop mode without RTC

The Stop mode achieves the lowest power consumption while retaining the RAM and register contents. All clocks are stopped, the PLL, MSI RC, HSI and LSI RC, HSE and LSE crystal oscillators are disabled.

Some peripherals featuring wakeup capability can enable the HSI RC during Stop mode to detect their wakeup condition.

The voltage regulator is in the low-power mode. The device can be woken up from Stop mode by any of the EXTI line, in 3.5  $\mu$ s, the processor can serve the interrupt or resume the code. The EXTI line source can be any GPIO. It can be the PVD output, the comparator 1 event or comparator 2 event (if internal reference voltage is on). It can also be wakened by the USB/USART/I2C/LPUART/LPTIMER wakeup events.

### • Standby mode with RTC

The Standby mode is used to achieve the lowest power consumption and real time clock. The internal voltage regulator is switched off so that the entire  $V_{CORE}$  domain is powered off. The PLL, MSI RC, HSE crystal and HSI RC oscillators are also switched off. The LSE or LSI is still running. After entering Standby mode, the RAM and register contents are lost except for registers in the Standby circuitry (wakeup logic, IWDG, RTC, LSI, LSE Crystal 32 KHz oscillator, RCC\_CSR register).

The device exits Standby mode in 60 µs when an external reset (NRST pin), an IWDG reset, a rising edge on one of the three WKUP pins, RTC alarm (Alarm A or Alarm B), RTC tamper event, RTC timestamp event or RTC Wakeup event occurs.

### Standby mode without RTC

The Standby mode is used to achieve the lowest power consumption. The internal voltage regulator is switched off so that the entire  $V_{CORE}$  domain is powered off. The PLL, MSI RC, HSI and LSI RC, HSE and LSE crystal oscillators are also switched off. After entering Standby mode, the RAM and register contents are lost except for registers in the Standby circuitry (wakeup logic, IWDG, RTC, LSI, LSE Crystal 32 KHz oscillator, RCC\_CSR register).

The device exits Standby mode in 60  $\mu$ s when an external reset (NRST pin) or a rising edge on one of the three WKUP pin occurs.

*Note:* The RTC, the IWDG, and the corresponding clock sources are not stopped automatically by entering Stop or Standby mode.

# 3.3 ARM<sup>®</sup> Cortex<sup>®</sup>-M0+ core with MPU

The Cortex-M0+ processor is an entry-level 32-bit ARM Cortex processor designed for a broad range of embedded applications. It offers significant benefits to developers, including:

- a simple architecture that is easy to learn and program

- ultra-low power, energy-efficient operation

- excellent code density

- deterministic, high-performance interrupt handling

- upward compatibility with Cortex-M processor family

- platform security robustness, with integrated Memory Protection Unit (MPU).

The Cortex-M0+ processor is built on a highly area and power optimized 32-bit processor core, with a 2-stage pipeline Von Neumann architecture. The processor delivers exceptional energy efficiency through a small but powerful instruction set and extensively optimized design, providing high-end processing hardware including a single-cycle multiplier.

The Cortex-M0+ processor provides the exceptional performance expected of a modern 32bit architecture, with a higher code density than other 8-bit and 16-bit microcontrollers.

Owing to its embedded ARM core, the STM32L052x6/8 are compatible with all ARM tools and software.

## Nested vectored interrupt controller (NVIC)

The ultra-low-power STM32L052x6/8 embed a nested vectored interrupt controller able to handle up to 32 maskable interrupt channels and 4 priority levels.

The Cortex-M0+ processor closely integrates a configurable Nested Vectored Interrupt Controller (NVIC), to deliver industry-leading interrupt performance. The NVIC:

- includes a Non-Maskable Interrupt (NMI)

- provides zero jitter interrupt option

- provides four interrupt priority levels

The tight integration of the processor core and NVIC provides fast execution of Interrupt Service Routines (ISRs), dramatically reducing the interrupt latency. This is achieved through the hardware stacking of registers, and the ability to abandon and restart load-multiple and store-multiple operations. Interrupt handlers do not require any assembler wrapper code, removing any code overhead from the ISRs. Tail-chaining optimization also significantly reduces the overhead when switching from one ISR to another.

To optimize low-power designs, the NVIC integrates with the sleep modes, that include a deep sleep function that enables the entire device to enter rapidly stop or standby mode.

This hardware block provides flexible interrupt management features with minimal interrupt latency.

| USART modes/features <sup>(1)</sup> | USART1 and USART2 |  |  |  |

|-------------------------------------|-------------------|--|--|--|

| Modbus communication                | X                 |  |  |  |

| Auto baud rate detection (4 modes)  | X                 |  |  |  |

| Driver Enable                       | Х                 |  |  |  |

### Table 13. USART implementation (continued)

1. X = supported.

2. This mode allows using the USART as an SPI master.

# 3.18.3 Low-power universal asynchronous receiver transmitter (LPUART)

The devices embed one Low-power UART. The LPUART supports asynchronous serial communication with minimum power consumption. It supports half duplex single wire communication and modem operations (CTS/RTS). It allows multiprocessor communication.

The LPUART has a clock domain independent from the CPU clock. It can wake up the system from Stop mode using baudrates up to 46 Kbaud. The Wakeup events from Stop mode are programmable and can be:

- Start bit detection

- Or any received data frame

- Or a specific programmed data frame

Only a 32.768 kHz clock (LSE) is needed to allow LPUART communication up to 9600 baud. Therefore, even in Stop mode, the LPUART can wait for an incoming frame while having an extremely low energy consumption. Higher speed clock can be used to reach higher baudrates.

LPUART interface can be served by the DMA controller.

# 3.18.4 Serial peripheral interface (SPI)/Inter-integrated sound (I2S)

Up to two SPIs are able to communicate at up to 16 Mbits/s in slave and master modes in full-duplex and half-duplex communication modes. The 3-bit prescaler gives 8 master mode frequencies and the frame is configurable to 8 bits or 16 bits. The hardware CRC generation/verification supports basic SD Card/MMC modes.

The USARTs with synchronous capability can also be used as SPI master.

One standard I2S interfaces (multiplexed with SPI2) is available. It can operate in master or slave mode, and can be configured to operate with a 16-/32-bit resolution as input or output channels. Audio sampling frequencies from 8 kHz up to 192 kHz are supported. When the I2S interfaces is configured in master mode, the master clock can be output to the external DAC/CODEC at 256 times the sampling frequency.

The SPIs can be served by the DMA controller.

Refer to *Table 14* for the differences between SPI1 and SPI2.

| SPI features <sup>(1)</sup> | SPI1 | SPI2 |

|-----------------------------|------|------|

| Hardware CRC calculation    | Х    | Х    |

| I2S mode                    | -    | Х    |

| TI mode                     | Х    | Х    |

Table 14. SPI/I2S implementation

1. X = supported.

# 3.18.5 Universal serial bus (USB)

The STM32L052x6/8 embed a full-speed USB device peripheral compliant with the USB specification version 2.0. The internal USB PHY supports USB FS signaling, embedded DP pull-up and also battery charging detection according to Battery Charging Specification Revision 1.2. The USB interface implements a full-speed (12 Mbit/s) function interface with added support for USB 2.0 Link Power Management. It has software-configurable endpoint setting with packet memory up to 1 KB and suspend/resume support. It requires a precise 48 MHz clock which can be generated from the internal main PLL (the clock source must use a HSE crystal oscillator) or by the internal 48 MHz oscillator in automatic trimming mode. The synchronization for this oscillator can be taken from the USB data stream itself (SOF signalization) which allows crystal-less operation.

# 3.19 Clock recovery system (CRS)

The STM32L052x6/8 embed a special block which allows automatic trimming of the internal 48 MHz oscillator to guarantee its optimal accuracy over the whole device operational range. This automatic trimming is based on the external synchronization signal, which could be either derived from USB SOF signalization, from LSE oscillator, from an external signal on CRS\_SYNC pin or generated by user software. For faster lock-in during startup it is also possible to combine automatic trimming with manual trimming action.

# 3.20 Cyclic redundancy check (CRC) calculation unit

The CRC (cyclic redundancy check) calculation unit is used to get a CRC code using a configurable generator polynomial value and size.

Among other applications, CRC-based techniques are used to verify data transmission or storage integrity. In the scope of the EN/IEC 60335-1 standard, they offer a means of verifying the Flash memory integrity. The CRC calculation unit helps compute a signature of the software during runtime, to be compared with a reference signature generated at linktime and stored at a given memory location.

# 3.21 Serial wire debug port (SW-DP)

An ARM SW-DP interface is provided to allow a serial wire debugging tool to be connected to the MCU.

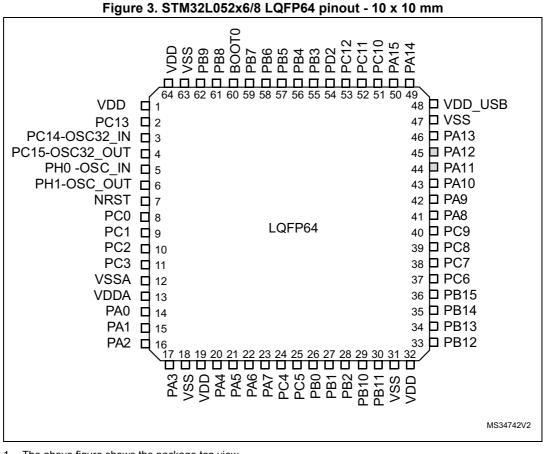

# 4 Pin descriptions

1. The above figure shows the package top view.

2. I/O pin supplied by VDD\_USB.

|        |      | AF0                                      | AF1 | AF2                                    | AF3        |

|--------|------|------------------------------------------|-----|----------------------------------------|------------|

| P      | ort  | LPUART1/LPTIM/<br>TIM21/12/<br>EVENTOUT/ |     | SPI2/I2S2/USB/<br>LPUART1/<br>EVENTOUT | TSC        |

|        | PC0  | LPTIM1_IN1                               | -   | EVENTOUT                               | TSC_G7_IO1 |

|        | PC1  | LPTIM1_OUT                               | -   | EVENTOUT                               | TSC_G7_IO2 |

|        | PC2  | LPTIM1_IN2                               | -   | SPI2_MISO/I2S2_MCK                     | TSC_G7_IO3 |

|        | PC3  | LPTIM1_ETR                               | -   | SPI2_MOSI/I2S2_SD                      | TSC_G7_IO4 |

|        | PC4  | EVENTOUT                                 | -   | LPUART1_TX                             | -          |

|        | PC5  | -                                        | -   | LPUART1_RX                             | TSC_G3_IO1 |

|        | PC6  | TIM22_CH1                                | -   | -                                      | TSC_G8_IO1 |

| Port C | PC7  | TIM22_CH2                                | -   | -                                      | TSC_G8_IO2 |

| FULC   | PC8  | TIM22_ETR                                | -   | -                                      | TSC_G8_IO3 |

|        | PC9  | TIM21_ETR                                | -   | USB_NOE                                | TSC_G8_IO4 |

|        | PC10 | LPUART1_TX                               | -   | -                                      | -          |

|        | PC11 | LPUART1_RX                               | -   | -                                      | -          |

|        | PC12 | -                                        | -   | -                                      | -          |

|        | PC13 | -                                        | -   | -                                      | -          |

|        | PC14 | -                                        | -   | -                                      | -          |

|        | PC15 | -                                        | -   | -                                      | -          |

STM32L052x6 STM32L052x8

Pin descriptions

5

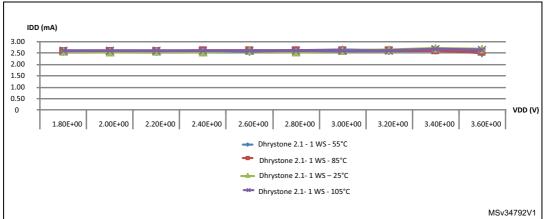

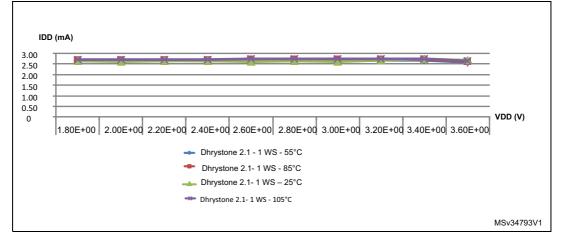

Figure 15.  $I_{DD}$  vs  $V_{DD}$ , at T<sub>A</sub>= 25/55/85/105 °C, Run mode, code running from Flash memory, Range 2, HSI16, 1WS

# 6.3.7 Internal clock source characteristics

The parameters given in *Table 46* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 25*.

### High-speed internal 16 MHz (HSI16) RC oscillator

| Symbol                                | Parameter                                           | Conditions                                                            | Min               | Тур  | Max              | Unit |

|---------------------------------------|-----------------------------------------------------|-----------------------------------------------------------------------|-------------------|------|------------------|------|

| f <sub>HSI16</sub>                    | Frequency                                           | V <sub>DD</sub> = 3.0 V                                               | -                 | 16   | -                | MHz  |

| TRIM <sup>(1)(2)</sup>                | HSI16 user-                                         | Trimming code is not a multiple of 16                                 | -                 | ±0.4 | 0.7              | %    |

| TRIM                                  | trimmed resolution                                  | Trimming code is a multiple of 16                                     | -                 | -    | ±1.5             | %    |

|                                       |                                                     | V <sub>DDA</sub> = 3.0 V, T <sub>A</sub> = 25 °C                      | -1 <sup>(3)</sup> | -    | 1 <sup>(3)</sup> | %    |

|                                       | Accuracy of the factory-calibrated HSI16 oscillator | $V_{DDA}$ = 3.0 V, $T_A$ = 0 to 55 °C                                 | -1.5              | -    | 1.5              | %    |

| ACC                                   |                                                     | $V_{DDA}$ = 3.0 V, $T_A$ = -10 to 70 °C                               | -2                | -    | 2                | %    |

| ACC <sub>HSI16</sub>                  |                                                     | $V_{DDA}$ = 3.0 V, $T_A$ = -10 to 85 °C                               | -2.5              | -    | 2                | %    |

|                                       |                                                     | V <sub>DDA</sub> = 3.0 V, T <sub>A</sub> = -10 to 105 °C              | -4                | -    | 2                | %    |

|                                       |                                                     | V <sub>DDA</sub> = 1.65 V to 3.6 V<br>T <sub>A</sub> = - 40 to 125 °C | -5.45             | -    | 3.25             | %    |

| t <sub>SU(HSI16)</sub> <sup>(2)</sup> | HSI16 oscillator<br>startup time                    | -                                                                     | -                 | 3.7  | 6                | μs   |

| I <sub>DD(HSI16)</sub> <sup>(2)</sup> | HSI16 oscillator<br>power consumption               | -                                                                     | -                 | 100  | 140              | μA   |

1. The trimming step differs depending on the trimming code. It is usually negative on the codes which are multiples of 16 (0x00, 0x10, 0x20, 0x30...0xE0).

2. Guaranteed by characterization results.

3. Guaranteed by test in production.

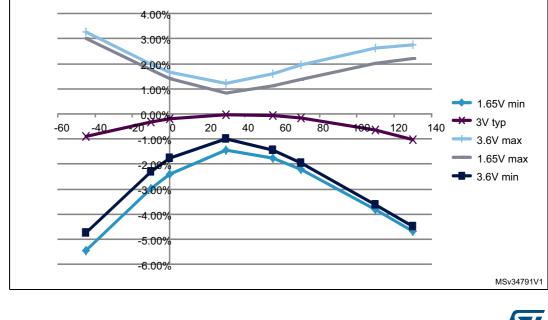

### Figure 23. HSI16 minimum and maximum value versus temperature

# 6.3.9 Memory characteristics

## **RAM** memory

| Symbol | Parameter                          | Conditions           | Min  | Тур | Max | Unit |

|--------|------------------------------------|----------------------|------|-----|-----|------|

| VRM    | Data retention mode <sup>(1)</sup> | STOP mode (or RESET) | 1.65 | -   | -   | V    |

Table 51. RAM and hardware registers

1. Minimum supply voltage without losing data stored in RAM (in Stop mode or under Reset) or in hardware registers (only in Stop mode).

## Flash memory and data EEPROM

| Symbol          | Parameter                                                                      | Conditions                                      | Min  | Тур  | Max <sup>(1)</sup> | Unit |

|-----------------|--------------------------------------------------------------------------------|-------------------------------------------------|------|------|--------------------|------|

| V <sub>DD</sub> | Operating voltage<br>Read / Write / Erase                                      | -                                               | 1.65 | -    | 3.6                | V    |

|                 | Programming time for                                                           | Erasing                                         | -    | 3.28 | 3.94               | me   |

|                 | word or half-page                                                              | Programming                                     | -    | 3.28 | 3.94               | ms   |

| I <sub>DD</sub> | Average current during<br>the whole programming /<br>erase operation           | T <sub>A</sub> = 25 °C, V <sub>DD</sub> = 3.6 V | -    | 500  | 700                | μA   |

|                 | Maximum current (peak)<br>during the whole<br>programming / erase<br>operation |                                                 | -    | 1.5  | 2.5                | mA   |

# Table 52. Flash memory and data EEPROM characteristics

1. Guaranteed by design.

| Table 53. Flash memory        | and data EEPROM endurance and retent | ion |

|-------------------------------|--------------------------------------|-----|

| 14010 001 1 14011 111011101 9 |                                      |     |

| Symbol                          | Parameter                                     | Conditions                       | Value              | Unit    |

|---------------------------------|-----------------------------------------------|----------------------------------|--------------------|---------|

|                                 | Falameter                                     | Conditions                       | Min <sup>(1)</sup> | Onit    |

|                                 | Cycling (erase / write)<br>Program memory     | T 40%0 to 405 %0                 | 10                 |         |

| N <sub>CYC</sub> <sup>(2)</sup> | Cycling (erase / write)<br>EEPROM data memory | T <sub>A</sub> = -40°C to 105 °C | 100                | kcycles |

|                                 | Cycling (erase / write)<br>Program memory     | T 40°C to 125 °C                 | 0.2                | REYCIES |

|                                 | Cycling (erase / write)<br>EEPROM data memory | T <sub>A</sub> = -40°C to 125 °C | 2                  |         |

| Symbol                          | Parameter                                                                      | Conditions                  | Value              | Unit  |  |

|---------------------------------|--------------------------------------------------------------------------------|-----------------------------|--------------------|-------|--|

| Symbol                          | Farameter                                                                      | Conditions                  | Min <sup>(1)</sup> | Unit  |  |

|                                 | Data retention (program memory) after<br>10 kcycles at T <sub>A</sub> = 85 °C  | T                           | 30                 |       |  |

|                                 | Data retention (EEPROM data memory) after 100 kcycles at $T_A = 85 \text{ °C}$ | T <sub>RET</sub> = +85 °C   | 30                 |       |  |

| t <sub>RET</sub> <sup>(2)</sup> | Data retention (program memory) after<br>10 kcycles at T <sub>A</sub> = 105 °C | T = +105 °C                 | - 10               | years |  |

| 'RET`                           | Data retention (EEPROM data memory) after 100 kcycles at $T_A = 105$ °C        | T <sub>RET</sub> = +105 °C  |                    |       |  |

|                                 | Data retention (program memory) after 200 cycles at $T_A$ = 125 °C             | -Т <sub>ВЕТ</sub> = +125 °С |                    |       |  |

|                                 | Data retention (EEPROM data memory) after 2 kcycles at $T_A$ = 125 °C          | TRET - TIZO O               |                    |       |  |

Table 53. Flash memory and data EEPROM endurance and retention (continued)

1. Guaranteed by characterization results.

2. Characterization is done according to JEDEC JESD22-A117.

# 6.3.10 EMC characteristics

Susceptibility tests are performed on a sample basis during device characterization.

### Functional EMS (electromagnetic susceptibility)

While a simple application is executed on the device (toggling 2 LEDs through I/O ports). the device is stressed by two electromagnetic events until a failure occurs. The failure is indicated by the LEDs:

- Electrostatic discharge (ESD) (positive and negative) is applied to all device pins until a functional disturbance occurs. This test is compliant with the IEC 61000-4-2 standard.

- FTB: A Burst of Fast Transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100 pF capacitor, until a functional disturbance occurs. This test is compliant with the IEC 61000-4-4 standard.

A device reset allows normal operations to be resumed.

The test results are given in *Table 54*. They are based on the EMS levels and classes defined in application note AN1709.

| Symbol            | Parameter                                                                                                                         | Conditions                                                                                                                                | Level/<br>Class |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| V <sub>FESD</sub> | Voltage limits to be applied on any I/O pin to induce a functional disturbance                                                    | $V_{DD}$ = 3.3 V, LQFP64, T <sub>A</sub> = +25 °C,<br>f <sub>HCLK</sub> = 32 MHz<br>conforms to IEC 61000-4-2                             | 3B              |

| V <sub>EFTB</sub> | Fast transient voltage burst limits to be applied through 100 pF on $V_{DD}$ and $V_{SS}$ pins to induce a functional disturbance | $V_{DD} = 3.3 \text{ V}, \text{LQFP64}, \text{T}_{\text{A}} = +25 \text{ °C},$<br>f <sub>HCLK</sub> = 32 MHz<br>conforms to IEC 61000-4-4 | 4A              |

### Table 54. EMS characteristics

# 6.3.12 I/O current injection characteristics

As a general rule, current injection to the I/O pins, due to external voltage below  $V_{SS}$  or above  $V_{DD}$  (for standard pins) should be avoided during normal product operation. However, in order to give an indication of the robustness of the microcontroller in cases when abnormal injection accidentally happens, susceptibility tests are performed on a sample basis during device characterization.

### Functional susceptibility to I/O current injection

While a simple application is executed on the device, the device is stressed by injecting current into the I/O pins programmed in floating input mode. While current is injected into the I/O pin, one at a time, the device is checked for functional failures.

The failure is indicated by an out of range parameter: ADC error above a certain limit (higher than 5 LSB TUE), out of conventional limits of induced leakage current on adjacent pins (out of  $-5 \mu A/+0 \mu A$  range), or other functional failure (for example reset occurrence oscillator frequency deviation).

The test results are given in the Table 58.

|                  |                                                                     | Functional s       |                    |      |

|------------------|---------------------------------------------------------------------|--------------------|--------------------|------|

| Symbol           | Description                                                         | Negative injection | Positive injection | Unit |

|                  | Injected current on BOOT0                                           | -0                 | NA                 |      |

| I <sub>INJ</sub> | Injected current on PA0, PA4, PA5, PA11,<br>PA12, PC15, PH0 and PH1 | -5                 | 0                  | mA   |

|                  | Injected current on any other FT, FTf pins                          | -5 <sup>(1)</sup>  | NA                 |      |

|                  | Injected current on any other pins                                  | -5 <sup>(1)</sup>  | +5                 |      |

### Table 58. I/O current injection susceptibility

1. It is recommended to add a Schottky diode (pin to ground) to analog pins which may potentially inject negative currents.

### STM32L052x6 STM32L052x8

| Symbol                                | Parameter                          | Conditions                                      | Min                                                                        | Тур | Max                                               | Unit                       |

|---------------------------------------|------------------------------------|-------------------------------------------------|----------------------------------------------------------------------------|-----|---------------------------------------------------|----------------------------|

| R <sub>ADC</sub> <sup>(3)(4)</sup>    | Sampling switch resistance         | -                                               | -                                                                          | -   | 1                                                 | kΩ                         |

| C <sub>ADC</sub> <sup>(3)</sup>       | Internal sample and hold capacitor | -                                               | -                                                                          | -   | 8                                                 | pF                         |

| ↓ (3)(5)                              | Calibration time                   | f <sub>ADC</sub> = 16 MHz                       |                                                                            | 5.2 |                                                   | μs                         |

| t <sub>CAL</sub> <sup>(3)(5)</sup>    |                                    | -                                               |                                                                            | 83  |                                                   | 1/f <sub>ADC</sub>         |

|                                       |                                    | ADC clock = HSI16                               | 1.5 ADC<br>cycles + 2<br>f <sub>PCLK</sub> cycles                          | -   | 1.5 ADC<br>cycles + 3<br>f <sub>PCLK</sub> cycles | -                          |

| W <sub>LATENCY</sub> <sup>(6)</sup>   | ADC_DR register write<br>latency   | ADC clock = PCLK/2                              | -                                                                          | 4.5 | -                                                 | f <sub>PCLK</sub><br>cycle |

|                                       |                                    | ADC clock = PCLK/4                              | -                                                                          | 8.5 | -                                                 | f <sub>PCLK</sub><br>cycle |

|                                       |                                    | $f_{ADC} = f_{PCLK}/2 = 16 \text{ MHz}$         | 0.266                                                                      |     |                                                   | μs                         |

|                                       | Trigger conversion latency         | $f_{ADC} = f_{PCLK}/2$                          | 8.5                                                                        |     |                                                   | 1/f <sub>PCLK</sub>        |

| t <sub>latr</sub> (3)                 |                                    | f <sub>ADC</sub> = f <sub>PCLK</sub> /4 = 8 MHz | 0.516                                                                      |     |                                                   | μs                         |

|                                       |                                    | f <sub>ADC</sub> = f <sub>PCLK</sub> /4         | 16.5                                                                       |     |                                                   | 1/f <sub>PCLK</sub>        |

|                                       |                                    | f <sub>ADC</sub> = f <sub>HSI16</sub> = 16 MHz  | 0.252                                                                      | -   | 0.260                                             | μs                         |

| Jitter <sub>ADC</sub>                 | ADC jitter on trigger conversion   | f <sub>ADC</sub> = f <sub>HSI16</sub>           | -                                                                          | 1   | -                                                 | 1/f <sub>HSI16</sub>       |

| ts <sup>(3)</sup>                     |                                    | f <sub>ADC</sub> = 16 MHz                       | 0.093                                                                      | -   | 10.03                                             | μs                         |

| ts <sup>(e)</sup>                     | Sampling time                      | -                                               | 1.5                                                                        | -   | 160.5                                             | 1/f <sub>ADC</sub>         |

| t <sub>UP_LDO</sub> <sup>(3)(5)</sup> | Internal LDO power-up time         | -                                               | -                                                                          | -   | 10                                                | μs                         |

| t <sub>STAB</sub> <sup>(3)(5)</sup>   | ADC stabilization time             | -                                               | 14                                                                         |     | 1/f <sub>ADC</sub>                                |                            |

| + (3)                                 | Total conversion time              | f <sub>ADC</sub> = 16 MHz,<br>12-bit resolution | 0.875                                                                      | -   | 10.81                                             | μs                         |

| t <sub>ConV</sub> <sup>(3)</sup>      | (including sampling time)          | 12-bit resolution                               | 14 to 173 (t <sub>S</sub> for sampling +12.5 for successive approximation) |     | 1/f <sub>ADC</sub>                                |                            |

Table 63. ADC characteristics (continued)

1. V<sub>DDA</sub> minimum value can be decreased in specific temperature conditions. Refer to Table 64: RAIN max for fADC = 16 MHz.

2. A current consumption proportional to the APB clock frequency has to be added (see *Table 39: Peripheral current consumption in Run or Sleep mode*).

3. Guaranteed by design.

Standard channels have an extra protection resistance which depends on supply voltage. Refer to Table 64: RAIN max for fADC = 16 MHz.

5. This parameter only includes the ADC timing. It does not take into account register access latency.

6. This parameter specifies the latency to transfer the conversion result into the ADC\_DR register. EOC bit is set to indicate the conversion is complete and has the same latency.

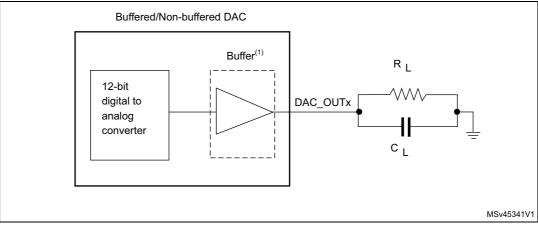

| Symbol              | Parameter                                                                                                                                                 | Conditions                                                 | Min | Тур | Мах | Unit |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|-----|-----|-----|------|

| tsettling           | Settling time (full scale: for a<br>12-bit code transition between<br>the lowest and the highest<br>input codes till DAC_OUT<br>reaches final value ±1LSB | $C_L \le 50 \text{ pF, } R_L \ge 5 \text{ k}\Omega$        | -   | 7   | 12  | μs   |

| Update rate         | Max frequency for a correct<br>DAC_OUT change (95% of<br>final value) with 1 LSB<br>variation in the input code                                           | $C_L \le 50 \text{ pF, } R_L \ge 5 \text{ k}\Omega$        | -   | -   | 1   | Msps |

| t <sub>WAKEUP</sub> | Wakeup time from off state<br>(setting the ENx bit in the DAC<br>Control register) <sup>(9)</sup>                                                         | $C_L \le 50 \text{ pF}, R_L \ge 5 \text{ k}\Omega$         | -   | 9   | 15  | μs   |

| PSRR+               | V <sub>DDA</sub> supply rejection ratio<br>(static DC measurement)                                                                                        | $C_L \le 50 \text{ pF}, \text{ R}_L \ge 5 \text{ k}\Omega$ | -   | -60 | -35 | dB   |

Table 66. DAC characteristics (continued)

1. Guaranteed by characterization results.

2. Guaranteed by design, not tested in production.

3. Connected between DAC\_OUT and V<sub>SSA</sub>.

4. Difference between two consecutive codes - 1 LSB.

5. Difference between measured value at Code i and the value at Code i on a line drawn between Code 0 and last Code 4095.

6. Difference between the value measured at Code (0x800) and the ideal value =  $V_{REF+}/2$ .

7. Difference between the value measured at Code (0x001) and the ideal value.

- 8. Difference between ideal slope of the transfer function and measured slope computed from code 0x000 and 0xFFF when buffer is OFF, and from code giving 0.2 V and ( $V_{DDA} 0.2$ ) V when buffer is ON.

- 9. In buffered mode, the output can overshoot above the final value for low input code (starting from min value).

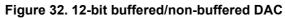

1. The DAC integrates an output buffer that can be used to reduce the output impedance and to drive external loads directly without the use of an external operational amplifier. The buffer can be bypassed by configuring the BOFFx bit in the DAC\_CR register.

# 6.3.17 Temperature sensor characteristics

| Calibration value name | Description                                                               | Memory address            |  |  |  |  |

|------------------------|---------------------------------------------------------------------------|---------------------------|--|--|--|--|

| TS_CAL1                | TS ADC raw data acquired at temperature of 30 °C, V <sub>DDA</sub> = 3 V  | 0x1FF8 007A - 0x1FF8 007B |  |  |  |  |

| TS_CAL2                | TS ADC raw data acquired at temperature of 130 °C, V <sub>DDA</sub> = 3 V | 0x1FF8 007E - 0x1FF8 007F |  |  |  |  |

Table 67. Temperature sensor calibration values

Table 68. Temperature sensor characteristics

| Symbol                                | Parameter                                           | Min  | Тур  | Max  | Unit  |

|---------------------------------------|-----------------------------------------------------|------|------|------|-------|

| T <sub>L</sub> <sup>(1)</sup>         | V <sub>SENSE</sub> linearity with temperature       | -    | ±1   | ±2   | °C    |

| Avg_Slope <sup>(1)</sup>              | Average slope                                       | 1.48 | 1.61 | 1.75 | mV/°C |

| V <sub>130</sub>                      | Voltage at 130°C ±5°C <sup>(2)</sup>                |      | 670  | 700  | mV    |

| I <sub>DDA(TEMP)</sub> <sup>(3)</sup> | Current consumption                                 |      | 3.4  | 6    | μA    |

| t <sub>START</sub> <sup>(3)</sup>     | Startup time                                        |      | -    | 10   | 110   |

| T <sub>S_temp</sub> <sup>(4)(3)</sup> | ADC sampling time when reading the temperature 10 - |      |      | -    | μs    |

1. Guaranteed by characterization results.

2. Measured at V\_{DD} = 3 V  $\pm$ 10 mV. V130 ADC conversion result is stored in the TS\_CAL2 byte.

3. Guaranteed by design.

4. Shortest sampling time can be determined in the application by multiple iterations.

# 6.3.18 Comparators

| Symbol                   | Parameter                                                      | Conditions | Min <sup>(1)</sup> | Тур | Max <sup>(1)</sup> | Unit      |  |

|--------------------------|----------------------------------------------------------------|------------|--------------------|-----|--------------------|-----------|--|

| Gymbol                   | i arameter                                                     | Conditions |                    | чур | Max                | Onit      |  |

| $V_{DDA}$                | Analog supply voltage                                          | -          | 1.65               |     | 3.6                | V         |  |

| R <sub>400K</sub>        | R <sub>400K</sub> value                                        | -          | -                  | 400 | -                  | kΩ        |  |

| R <sub>10K</sub>         | R <sub>10K</sub> value                                         | -          | -                  | 10  | -                  | - K22     |  |

| V <sub>IN</sub>          | Comparator 1 input voltage range                               | -          | 0.6                | -   | V <sub>DDA</sub>   | V         |  |

| t <sub>START</sub>       | Comparator startup time                                        | -          | -                  | 7   | 10                 | 110       |  |

| td                       | Propagation delay <sup>(2)</sup>                               | -          | -                  | 3   | 10                 | μs        |  |

| Voffset                  | Comparator offset                                              | -          | -                  | ±3  | ±10                | mV        |  |

| d <sub>Voffset</sub> /dt | Comparator offset variation in worst voltage stress conditions |            | 0                  | 1.5 | 10                 | mV/1000 h |  |

| I <sub>COMP1</sub>       | Current consumption <sup>(3)</sup>                             | -          | -                  | 160 | 260                | nA        |  |

### Table 69. Comparator 1 characteristics

1. Guaranteed by characterization.

2. The delay is characterized for 100 mV input step with 10 mV overdrive on the inverting input, the non-inverting input set to the reference.

3. Comparator consumption only. Internal reference voltage not included.

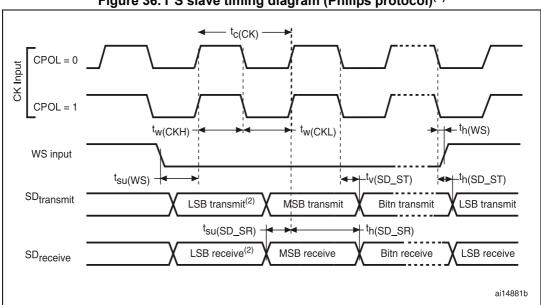

Figure 36. I<sup>2</sup>S slave timing diagram (Philips protocol)<sup>(1)</sup>

- 1. Measurement points are done at CMOS levels:  $0.3 \times V_{DD}$  and  $0.7 \times V_{DD}$ .

- 2. LSB transmit/receive of the previously transmitted byte. No LSB transmit/receive is sent before the first byte.

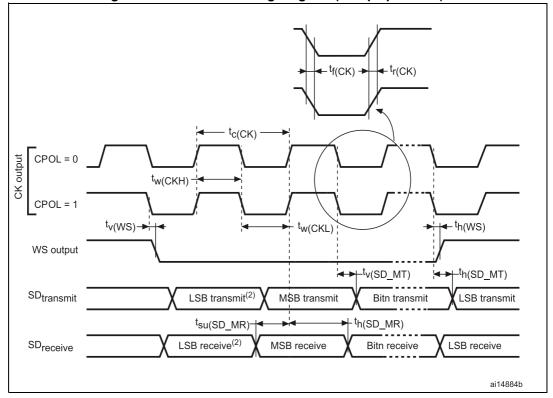

Figure 37. I<sup>2</sup>S master timing diagram (Philips protocol)<sup>(1)</sup>

- 1. Guaranteed by characterization results.

- 2. LSB transmit/receive of the previously transmitted byte. No LSB transmit/receive is sent before the first byte.

# 7.4 Standard WLCSP36 package information

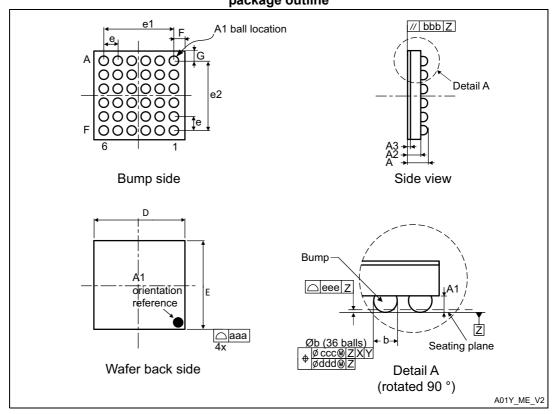

Figure 48. Standard WLCSP36 - 2.61 x 2.88 mm, 0.4 mm pitch wafer level chip scale package outline

1. Drawing is not to scale.

2. b dimensions is measured at the maximum bump diameter parallel to primary datum Z  $\,$

| mechanical data |      |                      |      |       |                       |       |

|-----------------|------|----------------------|------|-------|-----------------------|-------|

| Symbol          |      | millimeters          |      |       | inches <sup>(1)</sup> |       |

| Symbol          | Min  | Тур                  | Мах  | Min   | Тур                   | Max   |

| А               | -    | -                    | 0.59 | -     | -                     | 0.023 |

| A1              | -    | 0.18                 | -    | -     | 0.007                 | -     |

| A2              | -    | 0.38                 | -    | -     | 0.015                 | -     |

| A3              | -    | 0.025 <sup>(2)</sup> | -    | -     | 0.001                 | -     |

| b               | 0.22 | 0.25                 | 0.28 | 0.009 | 0.010                 | 0.011 |

| D               | 2.59 | 2.61                 | 2.63 | 0.102 | 0.103                 | 0.104 |

| E               | 2.86 | 2.88                 | 2.90 | 0.112 | 0.113                 | 0.114 |

| е               | -    | 0.40                 | -    | -     | 0.016                 | -     |

| e1              | -    | 2.00                 | -    | -     | 0.079                 | -     |

| e2              | -    | 2.00                 | -    | -     | 0.079                 | -     |

| Table 85. Standard WLCSP36 - 2.61 x 2.88 mm, 0.4 mm pitch wafer level chip scale |

|----------------------------------------------------------------------------------|

| mechanical data                                                                  |

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11-Mar-2016 | 6        | Updated number of SPIs on cover page and in <i>Table 2: Ultra-low-power</i><br><i>STM32L052x6/x8 device features and peripheral counts.</i><br>Changed minimum comparator supply voltage to 1.65 V on cover page.<br>Added number of fast and standard channels in <i>Section 3.11: Analog-to-digital converter (ADC).</i><br>Updated Section <i>3.18.2: Universal synchronous/asynchronous receiver</i><br><i>transmitter (USART)</i> and <i>Section 3.18.4: Serial peripheral interface</i><br>( <i>SPI)/Inter-integrated sound (I2S)</i> to mention the fact that USARTs with<br>synchronous mode feature can be used as SPI master interfaces.<br>Added baudrate allowing to wake up the MCU from Stop mode in<br><i>Section 3.18.2: Universal synchronous/asynchronous receiver</i><br><i>transmitter (USART)</i> and <i>Section 3.18.3: Low-power universal</i><br><i>asynchronous receiver transmitter (LPUART).</i><br>In <i>Section 6: Electrical characteristics</i> , updated notes related to values<br>guaranteed by characterization.<br>Updated <i>Table 58: I/O current injection susceptibility.</i><br>Updated <i>Table 55: EMI characteristics.</i><br>Changed temperature condition in <i>Table 8: Internal</i> voltage reference<br><i>measured</i> values and <i>Table 27: Embedded internal</i> voltage reference<br><i>measured</i> values.<br><i>Section 6.3.15: 12-bit ADC characteristics:</i><br>- <i>Table 63: ADC characteristics:</i><br>Distinction made between V <sub>DDA</sub> for fast and standard channels;<br>added note 1<br>Added note 4 related to R <sub>ADC</sub> .<br>Updated T <sub>RIG</sub> .<br>Updated T <sub>RIG</sub> .<br>Updated T <sub>RIG</sub> .<br>Updated R <sub>Q</sub> and added Note 2 in <i>Table 66: DAC characteristics.</i><br>Added Table <i>64: RAIN</i> max for <i>fADC = 16</i> MHz for f <sub>ADC</sub> = 16 MHz<br>and distinction made between fast and standard channels.<br>Updated R <sub>Q</sub> and added Note 2 in <i>Table 66: DAC characteristics.</i><br>Added Table <i>73: USART/LPUART characteristics.</i><br>Updated Figure <i>47: LQFP48</i> marking example (package top view). |

#### IMPORTANT NOTICE - PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2017 STMicroelectronics – All rights reserved