#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                      |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 32MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART, USB                          |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                            |

| Number of I/O              | 27                                                                    |

| Program Memory Size        | 32KB (32K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | 2K x 8                                                                |

| RAM Size                   | 8K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 3.6V                                                          |

| Data Converters            | A/D 10x12b; D/A 1x12b                                                 |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 32-LQFP                                                               |

| Supplier Device Package    | 32-LQFP (7x7)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l052k6t6 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                                                | Functionalities depending on the operating power supply range                       |                                     |                            |                           |  |  |

|------------------------------------------------|-------------------------------------------------------------------------------------|-------------------------------------|----------------------------|---------------------------|--|--|

| Operating power<br>supply range                | DAC and ADC operation                                                               | Dynamic<br>voltage scaling<br>range | I/O operation              | USB                       |  |  |

| V <sub>DD</sub> = 1.65 to 1.71 V               | 5 to 1.71 V ADC only,<br>conversion time<br>up to 570 ksps Range 2 or<br>range 3    |                                     | Degraded speed performance | Not functional            |  |  |

| V <sub>DD</sub> = 1.71 to 1.8 V <sup>(1)</sup> | 71 to 1.8 V <sup>(1)</sup> ADC only,<br>conversion time<br>up to 1.14 Msps          |                                     | Degraded speed performance | Functional <sup>(2)</sup> |  |  |

| $V_{DD}$ = 1.8 to 2.0 V <sup>(1)</sup>         | ,                                                                                   |                                     | Degraded speed performance | Functional <sup>(2)</sup> |  |  |

| V <sub>DD</sub> = 2.0 to 2.4 V                 | E 2.0 to 2.4 V Conversion time<br>up to<br>1.14 Msps Range 1, range 2<br>or range 3 |                                     | Full speed operation       | Functional <sup>(2)</sup> |  |  |

| V <sub>DD</sub> = 2.4 to 3.6 V                 | Conversion time<br>up to<br>1.14 Msps                                               | Range 1, range 2<br>or range 3      | Full speed operation       | Functional <sup>(2)</sup> |  |  |

| Table 0 Friedlandlities  |              |                 |                    |

|--------------------------|--------------|-----------------|--------------------|

| Table 3. Functionalities | aepenaing or | 1 the operating | power supply range |

CPU frequency changes from initial to final must respect "fcpu initial <4\*fcpu final". It must also respect 5

µs delay between two changes. For example to switch from 4.2 MHz to 32 MHz, you can switch from 4.2

MHz to 16 MHz, wait 5 µs, then switch from 16 MHz to 32 MHz.</li>

2. To be USB compliant from the I/O voltage standpoint, the minimum  $V_{\text{DD\_USB}}$  is 3.0 V.

#### Table 4. CPU frequency range depending on dynamic voltage scaling

| CPU frequency range                              | Dynamic voltage scaling range |

|--------------------------------------------------|-------------------------------|

| 16 MHz to 32 MHz (1ws)<br>32 kHz to 16 MHz (0ws) | Range 1                       |

| 8 MHz to 16 MHz (1ws)<br>32 kHz to 8 MHz (0ws)   | Range 2                       |

| 32 kHz to 4.2 MHz (0ws)                          | Range 3                       |

#### • Startup clock

After reset, the microcontroller restarts by default with an internal 2 MHz clock (MSI). The prescaler ratio and clock source can be changed by the application program as soon as the code execution starts.

#### • Clock security system (CSS)

This feature can be enabled by software. If an HSE clock failure occurs, the master clock is automatically switched to HSI and a software interrupt is generated if enabled.

Another clock security system can be enabled, in case of failure of the LSE it provides an interrupt or wakeup event which is generated if enabled.

#### • Clock-out capability (MCO: microcontroller clock output)

It outputs one of the internal clocks for external use by the application.

Several prescalers allow the configuration of the AHB frequency, each APB (APB1 and APB2) domains. The maximum frequency of the AHB and the APB domains is 32 MHz. See *Figure 2* for details on the clock tree.

|        |         | Pin Nı                 | umber  |        |         |                                       |          |               |       |                                                                                                 |                         |

|--------|---------|------------------------|--------|--------|---------|---------------------------------------|----------|---------------|-------|-------------------------------------------------------------------------------------------------|-------------------------|

| LQFP32 | UFQFN32 | WLCSP36 <sup>(1)</sup> | LQFP48 | LQFP64 | TFBGA64 | Pin name<br>(function after<br>reset) | Pin type | I/O structure | Notes | Alternate functions                                                                             | Additional<br>functions |

| -      | -       | E2                     | 21     | 29     | G7      | PB10                                  | I/O      | FT            | -     | TIM2_CH3,<br>TSC_SYNC,<br>LPUART1_TX,<br>SPI2_SCK,<br>I2C2_SCL                                  | -                       |

| -      | -       | D2                     | 22     | 30     | H7      | PB11                                  | I/O      | FT            | -     | EVENTOUT,<br>TIM2_CH4,<br>TSC_G6_IO1,<br>LPUART1_RX,<br>I2C2_SDA                                | -                       |

| 16     | -       | -                      | 23     | 31     | D6      | VSS                                   | S        | -             | -     | -                                                                                               | -                       |

| 17     | 17      | F1                     | 24     | 32     | E5      | VDD                                   | S        | -             | -     | -                                                                                               | -                       |

| -      | -       | -                      | 25     | 33     | H8      | PB12                                  | I/O      | FT            | -     | SPI2_NSS/I2S2_WS,<br>LPUART1_RTS_DE,<br>TSC_G6_IO2,<br>I2C2_SMBA,<br>EVENTOUT                   | -                       |

| -      | -       | -                      | 26     | 34     | G8      | PB13                                  | I/O      | FTf           | -     | SPI2_SCK/I2S2_CK,<br>TSC_G6_IO3,<br>LPUART1_CTS,<br>I2C2_SCL,<br>TIM21_CH1                      | -                       |

| -      | -       | -                      | 27     | 35     | F8      | PB14                                  | I/O      | FTf           | -     | SPI2_MISO/I<br>2S2_MCK,<br>RTC_OUT,<br>TSC_G6_IO4,<br>LPUART1_RTS_DE,<br>I2C2_SDA,<br>TIM21_CH2 | -                       |

| -      | -       | -                      | 28     | 36     | F7      | PB15                                  | I/O      | FT            | -     | SPI2_MOSI/I2S2_SD,<br>RTC_REFIN                                                                 | -                       |

| -      | -       | -                      | -      | 37     | F6      | PC6                                   | I/O      | FT            | -     | TIM22_CH1,<br>TSC_G8_IO1                                                                        | -                       |

| -      | -       | -                      | -      | 38     | E7      | PC7                                   | I/O      | FT            | -     | TIM22_CH2,<br>TSC_G8_IO2                                                                        | -                       |

| -      | -       | -                      | -      | 39     | E8      | PC8                                   | I/O      | FT            | -     | TIM22_ETR,<br>TSC_G8_IO3                                                                        | -                       |

Table 16. STM32L052x6/8 pin definitions (continued)

| ה | Table 20. Alternate function port D |       |                |  |  |  |

|---|-------------------------------------|-------|----------------|--|--|--|

|   | Po                                  |       | AF0            |  |  |  |

|   | PC                                  | Jri - | LPUART1        |  |  |  |

|   | Port D PD2                          |       | LPUART1_RTS_DE |  |  |  |

| Table 21. A | Alternate | function | port H |

|-------------|-----------|----------|--------|

|-------------|-----------|----------|--------|

| Port   |     | AF0          |

|--------|-----|--------------|

|        |     | USB          |

| Port H | PH0 | USB_CRS_SYNC |

| roitti | PH1 | -            |

| Symbol                      | Parameter                   | Conditions             | Тур  | Max <sup>(1)</sup> | Unit |  |  |  |

|-----------------------------|-----------------------------|------------------------|------|--------------------|------|--|--|--|

| I <sub>DD</sub> (Stop) Supp |                             | $T_A = -40$ to 25°C    | 0.41 | 1                  |      |  |  |  |

|                             |                             | T <sub>A</sub> = 55°C  | 0.63 | 2.1                |      |  |  |  |

|                             | Supply current in Stop mode | T <sub>A</sub> = 85°C  | 1.7  | 4.5                | μA   |  |  |  |

|                             |                             | T <sub>A</sub> = 105°C | 4    | 9.6                |      |  |  |  |

|                             |                             | T <sub>A</sub> = 125°C | 11   | 24 <sup>(2)</sup>  |      |  |  |  |

Table 36. Typical and maximum current consumptions in Stop mode

1. Guaranteed by characterization results at 125  $^\circ\text{C},$  unless otherwise specified.

2. Guaranteed by test in production.

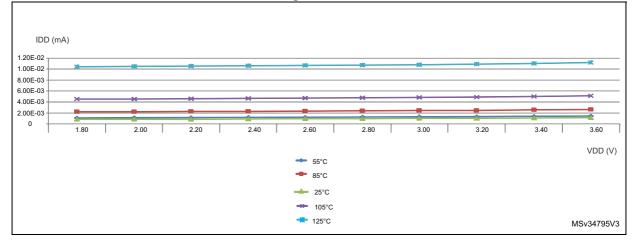

Figure 17. I<sub>DD</sub> vs V<sub>DD</sub>, at T<sub>A</sub>= 25/55/ 85/105/125 °C, Stop mode with RTC enabled and running on LSE Low drive

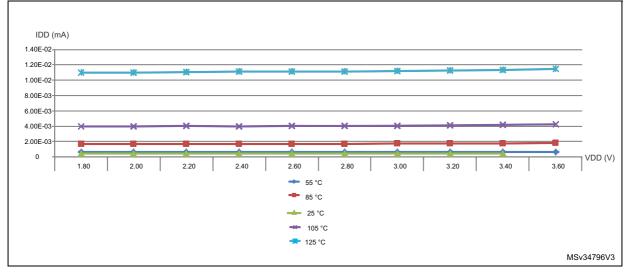

Figure 18.  $I_{DD}$  vs  $V_{DD}$ , at  $T_A$ = 25/55/85/105/125 °C, Stop mode with RTC disabled, all clocks OFF

| Symbol                     | Poriphoral                   | Typical consumption, T <sub>A</sub> = 25 °C |                        |        |

|----------------------------|------------------------------|---------------------------------------------|------------------------|--------|

| Symbol                     | Fenpheral                    | V <sub>DD</sub> =1.8 V                      | V <sub>DD</sub> =3.0 V | – Unit |

| I <sub>DD(PVD / BOR)</sub> | -                            | 0.7                                         | 1.2                    |        |

| I <sub>REFINT</sub>        | -                            | -                                           | 1.4                    |        |

| -                          | LSE Low drive <sup>(2)</sup> | 0,1                                         | 0,1                    |        |

| -                          | LPTIM1, Input 100 Hz         | 0,01                                        | 0,01                   | μΑ     |

| -                          | LPTIM1, Input 1 MHz          | 6                                           | 6                      |        |

| -                          | LPUART1                      | 0,2                                         | 0,2                    |        |

| -                          | RTC                          | 0,3                                         | 0,48                   | 1      |

1. LPTIM peripheral cannot operate in Standby mode.

2. LSE Low drive consumption is the difference between an external clock on OSC32\_IN and a quartz between OSC32\_IN and OSC32\_OUT.-

## 6.3.5 Wakeup time from low-power mode

The wakeup times given in the following table are measured with the MSI or HSI16 RC oscillator. The clock source used to wake up the device depends on the current operating mode:

- Sleep mode: the clock source is the clock that was set before entering Sleep mode

- Stop mode: the clock source is either the MSI oscillator in the range configured before entering Stop mode, the HSI16 or HSI16/4.

- Standby mode: the clock source is the MSI oscillator running at 2.1 MHz

All timings are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 25*.

| Symbol               | Parameter                                                        | Conditions                                               | Тур | Max | Unit               |

|----------------------|------------------------------------------------------------------|----------------------------------------------------------|-----|-----|--------------------|

| t <sub>WUSLEEP</sub> | Wakeup from Sleep mode                                           | f <sub>HCLK</sub> = 32 MHz                               | 7   | 8   |                    |

| twusleep_lp          | Wakeup from Low-power sleep mode,<br>f <sub>HCLK</sub> = 262 kHz | f <sub>HCLK</sub> = 262 kHz<br>Flash memory enabled      | 7   | 8   | Number<br>of clock |

|                      |                                                                  | f <sub>HCLK</sub> = 262 kHz<br>Flash memory switched OFF | 9   | 10  | cycles             |

| Table 41. Low-power mode wakeup timings | Table 41. | Low-power | mode | wakeup | timings |

|-----------------------------------------|-----------|-----------|------|--------|---------|

|-----------------------------------------|-----------|-----------|------|--------|---------|

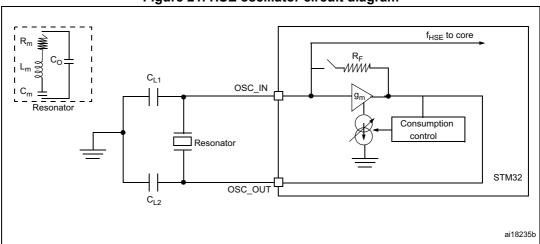

#### High-speed external clock generated from a crystal/ceramic resonator

The high-speed external (HSE) clock can be supplied with a 1 to 25 MHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on characterization results obtained with typical external components specified in *Table 44*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

| Symbol               | Parameter                                 | Conditions                    | Min | Тур | Max | Unit     |  |  |

|----------------------|-------------------------------------------|-------------------------------|-----|-----|-----|----------|--|--|

| f <sub>OSC_IN</sub>  | Oscillator frequency                      | -                             | 1   |     | 25  | MHz      |  |  |

| R <sub>F</sub>       | Feedback resistor                         | -                             | -   | 200 | -   | kΩ       |  |  |

| G <sub>m</sub>       | Maximum critical crystal transconductance | Startup                       | -   | -   | 700 | μΑ<br>/V |  |  |

| t <sub>SU(HSE)</sub> | Startup time                              | $V_{\text{DD}}$ is stabilized | -   | 2   | _   | ms       |  |  |

Table 44. HSE oscillator characteristics<sup>(1)</sup>

1. Guaranteed by design.

Guaranteed by characterization results. t<sub>SU(HSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 8 MHz oscillation is reached. This value is measured for a standard crystal resonator and it can vary significantly with the crystal manufacturer.

For  $C_{L1}$  and  $C_{L2}$ , it is recommended to use high-quality external ceramic capacitors in the 5 pF to 25 pF range (typ.), designed for high-frequency applications, and selected to match the requirements of the crystal or resonator (see *Figure 21*).  $C_{L1}$  and  $C_{L2}$  are usually the same size. The crystal manufacturer typically specifies a load capacitance which is the series combination of  $C_{L1}$  and  $C_{L2}$ . PCB and MCU pin capacitance must be included (10 pF can be used as a rough estimate of the combined pin and board capacitance) when sizing  $C_{L1}$  and  $C_{L2}$ . Refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website *www.st.com*.

Figure 21. HSE oscillator circuit diagram

# 6.3.9 Memory characteristics

## **RAM** memory

| Symbol | Parameter                          | Conditions           | Min  | Тур | Max | Unit |

|--------|------------------------------------|----------------------|------|-----|-----|------|

| VRM    | Data retention mode <sup>(1)</sup> | STOP mode (or RESET) | 1.65 | -   | -   | V    |

Table 51. RAM and hardware registers

1. Minimum supply voltage without losing data stored in RAM (in Stop mode or under Reset) or in hardware registers (only in Stop mode).

## Flash memory and data EEPROM

| Symbol                  | Parameter                                                                      | Conditions                                      | Min  | Тур  | Max <sup>(1)</sup> | Unit |  |

|-------------------------|--------------------------------------------------------------------------------|-------------------------------------------------|------|------|--------------------|------|--|

| V <sub>DD</sub>         | Operating voltage<br>Read / Write / Erase                                      | -                                               | 1.65 | -    | 3.6                | V    |  |

| +                       | Programming time for                                                           | Erasing                                         | -    | 3.28 | 3.94               | me   |  |

| tprog word or half-page |                                                                                | Programming                                     | -    | 3.28 | 3.94               | ms   |  |

|                         | Average current during<br>the whole programming /<br>erase operation           |                                                 | -    | 500  | 700                | μA   |  |

| I <sub>DD</sub>         | Maximum current (peak)<br>during the whole<br>programming / erase<br>operation | T <sub>A</sub> = 25 °C, V <sub>DD</sub> = 3.6 V | -    | 1.5  | 2.5                | mA   |  |

# Table 52. Flash memory and data EEPROM characteristics

1. Guaranteed by design.

| Table 53. Flash memory        | and data EEPROM endurance and retent | ion |

|-------------------------------|--------------------------------------|-----|

| 14010 001 1 14011 111011101 9 |                                      |     |

| Symbol                          | Parameter                                     | Conditions                       | Value              | Unit    |  |

|---------------------------------|-----------------------------------------------|----------------------------------|--------------------|---------|--|

| Symbol                          | Falameter                                     | Conditions                       | Min <sup>(1)</sup> | Unit    |  |

|                                 | Cycling (erase / write)<br>Program memory     | T - 40°C to 105 °C               | 10                 |         |  |

| N <sub>CYC</sub> <sup>(2)</sup> | Cycling (erase / write)<br>EEPROM data memory | T <sub>A</sub> = -40°C to 105 °C | 100                | kcycles |  |

|                                 | Cycling (erase / write)<br>Program memory     | $T = 40^{\circ}$ C to 125 °C     | 0.2                |         |  |

|                                 | Cycling (erase / write)<br>EEPROM data memory | T <sub>A</sub> = -40°C to 125 °C | 2                  |         |  |

# 6.3.11 Electrical sensitivity characteristics

Based on three different tests (ESD, LU) using specific measurement methods, the device is stressed in order to determine its performance in terms of electrical sensitivity.

#### Electrostatic discharge (ESD)

Electrostatic discharges (a positive then a negative pulse separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts  $\times$  (n+1) supply pins). This test conforms to the ANSI/JEDEC standard.

| Symbol                | Ratings                                                     | Conditions                                                    | Class | Maximum<br>value <sup>(1)</sup> | Unit |

|-----------------------|-------------------------------------------------------------|---------------------------------------------------------------|-------|---------------------------------|------|

| V <sub>ESD(HBM)</sub> | Electrostatic discharge voltage (human body model)          | $T_A = +25 \text{ °C},$<br>conforming to<br>ANSI/JEDEC JS-001 | 2     | 2000                            | V    |

| V <sub>ESD(CDM)</sub> | Electrostatic discharge<br>voltage (charge device<br>model) | $T_A = +25 °C,$<br>conforming to<br>ANSI/ESD STM5.3.1.        | C4    | 500                             | v    |

| Table 56. ESD absolute maximum | ratings |

|--------------------------------|---------|

|--------------------------------|---------|

1. Guaranteed by characterization results.

#### Static latch-up

Two complementary static tests are required on six parts to assess the latch-up performance:

- A supply overvoltage is applied to each power supply pin

- A current injection is applied to each input, output and configurable I/O pin

These tests are compliant with EIA/JESD 78A IC latch-up standard.

#### Table 57. Electrical sensitivities

| Symbol | Parameter             | Conditions                            | Class      |

|--------|-----------------------|---------------------------------------|------------|

| LU     | Static latch-up class | $T_A = +125$ °C conforming to JESD78A | II level A |

# 6.3.13 I/O port characteristics

### General input/output characteristics

Unless otherwise specified, the parameters given in *Table 59* are derived from tests performed under the conditions summarized in *Table 25*. All I/Os are CMOS and TTL compliant.

| Symbol           | Parameter                                         | Conditions                                                                                                    | Min                 | Тур                                | Мах                                | Unit |

|------------------|---------------------------------------------------|---------------------------------------------------------------------------------------------------------------|---------------------|------------------------------------|------------------------------------|------|

| V <sub>IL</sub>  | Input low level voltage                           | TC, FT, FTf, RST<br>I/Os                                                                                      | -                   | -                                  | 0.3V <sub>DD</sub>                 |      |

|                  |                                                   | BOOT0 pin                                                                                                     | -                   | -                                  | 0.14V <sub>DD</sub> <sup>(1)</sup> |      |

| $V_{\text{IH}}$  | Input high level voltage                          | All I/Os                                                                                                      | 0.7 V <sub>DD</sub> | -                                  | -                                  | V    |

| V                | I/O Schmitt trigger voltage hysteresis            | Standard I/Os                                                                                                 | -                   | 10% V <sub>DD</sub> <sup>(3)</sup> | -                                  |      |

| V <sub>hys</sub> | (2)                                               | BOOT0 pin                                                                                                     | -                   | 0.01                               | -                                  |      |

|                  |                                                   | V <sub>SS</sub> ≤V <sub>IN</sub> ≤V <sub>DD</sub><br>All I/Os except for<br>PA11, PA12, BOOT0<br>and FTf I/Os | -                   | -                                  | ±50                                |      |

|                  |                                                   | V <sub>SS</sub> ≤V <sub>IN</sub> ≤V <sub>DD</sub> ,<br>PA11 and PA12 I/Os                                     | -                   | -                                  | -50/+250                           | nA   |

|                  |                                                   | V <sub>SS</sub> ≤V <sub>IN</sub> ≤V <sub>DD</sub><br>FTf I/Os                                                 | -                   | -                                  | ±100                               |      |

| I <sub>lkg</sub> | Input leakage current <sup>(4)</sup>              | V <sub>DD</sub> ≤V <sub>IN</sub> ≤5 V<br>All I/Os except for<br>PA11, PA12, BOOT0<br>and FTf I/Os             | -                   | -                                  | 200                                | nA   |

|                  |                                                   | V <sub>DD</sub> ≤V <sub>IN</sub> ≤5 V<br>FTf I/Os                                                             | -                   | -                                  | 500                                |      |

|                  |                                                   | V <sub>DD</sub> ⊴V <sub>IN</sub> ⊴5 V<br>PA11, PA12 and<br>BOOT0                                              | -                   | -                                  | 10                                 | μΑ   |

| R <sub>PU</sub>  | Weak pull-up equivalent resistor <sup>(5)</sup>   | $V_{IN} = V_{SS}$                                                                                             | 30                  | 45                                 | 60                                 | kΩ   |

| R <sub>PD</sub>  | Weak pull-down equivalent resistor <sup>(5)</sup> | $V_{IN} = V_{DD}$                                                                                             | 30                  | 45                                 | 60                                 | kΩ   |

| C <sub>IO</sub>  | I/O pin capacitance                               | -                                                                                                             | -                   | 5                                  | -                                  | pF   |

| Table 59. I/O static characteristics | Table 59. I/O sta | atic characteristics |

|--------------------------------------|-------------------|----------------------|

|--------------------------------------|-------------------|----------------------|

1. Guaranteed by characterization.

2. Hysteresis voltage between Schmitt trigger switching levels. Guaranteed by characterization results.

3. With a minimum of 200 mV. Guaranteed by characterization results.

4. The max. value may be exceeded if negative current is injected on adjacent pins.

Pull-up and pull-down resistors are designed with a true resistance in series with a switchable PMOS/NMOS. This MOS/NMOS contribution to the series resistance is minimum (~10% order).

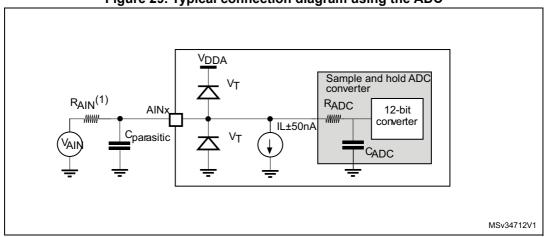

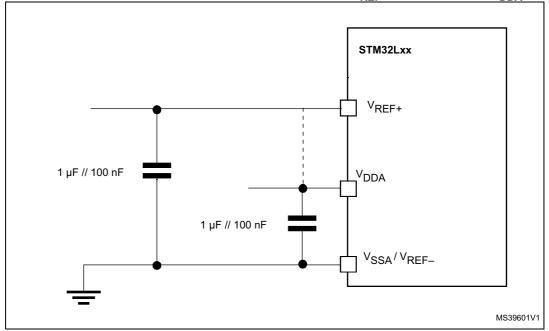

Figure 29. Typical connection diagram using the ADC

- 1. Refer to Table 63: ADC characteristics for the values of RAIN, RADC and CADC.

- C<sub>parasitic</sub> represents the capacitance of the PCB (dependent on soldering and PCB layout quality) plus the pad capacitance (roughly 7 pF). A high C<sub>parasitic</sub> value will downgrade conversion accuracy. To remedy this, f<sub>ADC</sub> should be reduced.

## **General PCB design guidelines**

Power supply decoupling should be performed as shown in *Figure 30* or *Figure 31*, depending on whether  $V_{REF+}$  is connected to  $V_{DDA}$  or not. The 10 nF capacitors should be ceramic (good quality). They should be placed as close as possible to the chip.

Figure 30. Power supply and reference decoupling (V<sub>REF+</sub> not connected to V<sub>DDA</sub>)

The analog spike filter is compliant with  $I^2C$  timings requirements only for the following voltage ranges:

- Fast mode Plus: 2.7 V  $\leq$ V<sub>DD</sub>  $\leq$ 3.6 V and voltage scaling Range 1

- Fast mode:

- 2 V  $\leq$ V<sub>DD</sub>  $\leq$ 3.6 V and voltage scaling Range 1 or Range 2.

- V<sub>DD</sub> < 2 V, voltage scaling Range 1 or Range 2, C<sub>load</sub> < 200 pF.

In other ranges, the analog filter should be disabled. The digital filter can be used instead.

Note: In Standard mode, no spike filter is required.

| Table 72. I | 2C analog | filter chara | cteristics <sup>(1)</sup> |

|-------------|-----------|--------------|---------------------------|

|-------------|-----------|--------------|---------------------------|

| Symbol          | Parameter                                                              | Conditions | Min               | Мах                | Unit |

|-----------------|------------------------------------------------------------------------|------------|-------------------|--------------------|------|

|                 |                                                                        | Range 1    |                   | 260 <sup>(3)</sup> |      |

| t <sub>AF</sub> | Maximum pulse width of spikes that are suppressed by the analog filter | Range 2    | 50 <sup>(2)</sup> | -                  | ns   |

|                 |                                                                        | Range 3    |                   | -                  |      |

- 1. Guaranteed by characterization results.

- 2. Spikes with widths below  $t_{\mbox{\scriptsize AF}(\mbox{min})}$  are filtered.

- 3. Spikes with widths above  $t_{AF(max)}$  are not filtered

### **USART/LPUART** characteristics

The parameters given in the following table are guaranteed by design.

| Symbol               | Parameter                                                                                                                                                      | Conditions                                                    | Тур | Max  | Unit |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|-----|------|------|

|                      |                                                                                                                                                                | Stop mode with main regulator in<br>Run mode, Range 2 or 3    | -   | 8.7  |      |

| <sup>t</sup> wuusart | Wakeup time needed to<br>calculate the maximum<br>USART/LPUART baudrate<br>allowing to wake up from<br>Stop mode when the<br>USART/LPUART is clocked<br>by HSI | Stop mode with main regulator in<br>Run mode, Range 1         | -   | 8.1  | μs   |

|                      |                                                                                                                                                                | Stop mode with main regulator in low-power mode, Range 2 or 3 | -   | 12   |      |

|                      |                                                                                                                                                                | Stop mode with main regulator in low-power mode, Range 1      | -   | 11.4 |      |

#### Table 73. USART/LPUART characteristics

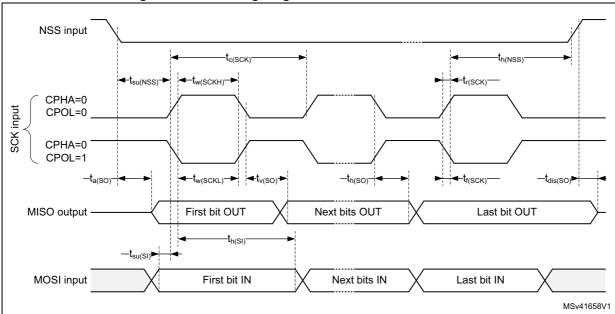

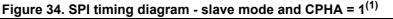

Figure 33. SPI timing diagram - slave mode and CPHA = 0

1. Measurement points are done at CMOS levels:  $0.3V_{\text{DD}}$  and  $0.7V_{\text{DD}.}$

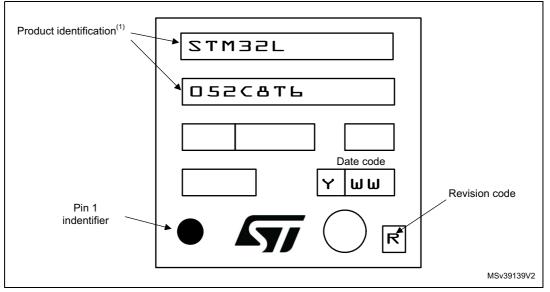

#### **Device marking for LQFP48**

The following figure gives an example of topside marking versus pin 1 position identifier location.

Other optional marking or inset/upset marks, which depend on supply chain operations, are not indicated below.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

| Dimension      | Recommended values                            |  |  |  |  |

|----------------|-----------------------------------------------|--|--|--|--|

| Pitch          | 0.4 mm                                        |  |  |  |  |

| Dpad           | 260 μm max. (circular)<br>220 μm recommended  |  |  |  |  |

| Dsm            | 300 μm min. (for 260 μm diameter pad)         |  |  |  |  |

| PCB pad design | Non-solder mask defined via underbump allowed |  |  |  |  |

Table 88. WLCSP36 recommended PCB design rules

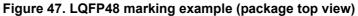

# 7.6 LQFP32 package information

1. Drawing is not to scale.

| Symbol | millimeters |       |       | inches <sup>(1)</sup> |        |        |  |

|--------|-------------|-------|-------|-----------------------|--------|--------|--|

| Symbol | Min         | Тур   | Max   | Min                   | Тур    | Мах    |  |

| А      | -           | -     | 1.600 | -                     | -      | 0.0630 |  |

| A1     | 0.050       | -     | 0.150 | 0.0020                | -      | 0.0059 |  |

| A2     | 1.350       | 1.400 | 1.450 | 0.0531                | 0.0551 | 0.0571 |  |

| b      | 0.300       | 0.370 | 0.450 | 0.0118                | 0.0146 | 0.0177 |  |

| С      | 0.090       | -     | 0.200 | 0.0035                | -      | 0.0079 |  |

| D      | 8.800       | 9.000 | 9.200 | 0.3465                | 0.3543 | 0.3622 |  |

| D1     | 6.800       | 7.000 | 7.200 | 0.2677                | 0.2756 | 0.2835 |  |

| D3     | -           | 5.600 | -     | -                     | 0.2205 | -      |  |

| E      | 8.800       | 9.000 | 9.200 | 0.3465                | 0.3543 | 0.3622 |  |

| E1     | 6.800       | 7.000 | 7.200 | 0.2677                | 0.2756 | 0.2835 |  |

| E3     | -           | 5.600 | -     | -                     | 0.2205 | -      |  |

| е      | -           | 0.800 | -     | -                     | 0.0315 | -      |  |

| L      | 0.450       | 0.600 | 0.750 | 0.0177                | 0.0236 | 0.0295 |  |

| L1     | -           | 1.000 | -     | -                     | 0.0394 | -      |  |

| k      | 0°          | 3.5°  | 7°    | 0°                    | 3.5°   | 7°     |  |

| CCC    | -           | -     | 0.100 | -                     | -      | 0.0039 |  |

Table 89. LQFP32 - 32-pin, 7 x 7 mm low-profile quad flat package mechanical data

1. Values in inches are converted from mm and rounded to 4 decimal digits.

1. Dimensions are expressed in millimeters.

|        |       | puona       | je mechanic | 4. 4444 |                       |        |

|--------|-------|-------------|-------------|---------|-----------------------|--------|

| Symbol |       | millimeters |             |         | inches <sup>(1)</sup> |        |

|        | Min   | Тур         | Max         | Min     | Тур                   | Мах    |

| А      | 0.500 | 0.550       | 0.600       | 0.0197  | 0.0217                | 0.0236 |

| A1     | 0.000 | 0.020       | 0.050       | 0.0000  | 0.0008                | 0.0020 |

| A3     | -     | 0.152       | -           | -       | 0.0060                | -      |

| b      | 0.180 | 0.230       | 0.280       | 0.0071  | 0.0091                | 0.0110 |

| D      | 4.900 | 5.000       | 5.100       | 0.1929  | 0.1969                | 0.2008 |

| D1     | 3.400 | 3.500       | 3.600       | 0.1339  | 0.1378                | 0.1417 |

| D2     | 3.400 | 3.500       | 3.600       | 0.1339  | 0.1378                | 0.1417 |

| E      | 4.900 | 5.000       | 5.100       | 0.1929  | 0.1969                | 0.2008 |

| E1     | 3.400 | 3.500       | 3.600       | 0.1339  | 0.1378                | 0.1417 |

| E2     | 3.400 | 3.500       | 3.600       | 0.1339  | 0.1378                | 0.1417 |

| е      | -     | 0.500       | -           | -       | 0.0197                | -      |

| L      | 0.300 | 0.400       | 0.500       | 0.0118  | 0.0157                | 0.0197 |

| ddd    | -     | -           | 0.080       | -       | -                     | 0.0031 |

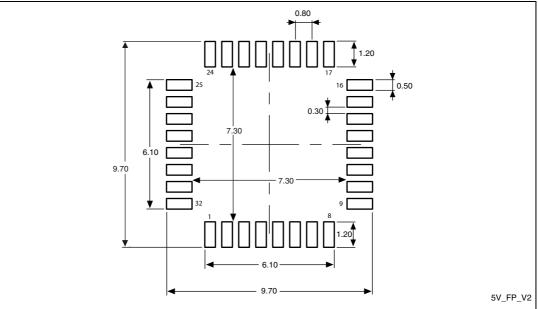

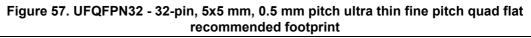

# Table 90. UFQFPN32 - 32-pin, 5x5 mm, 0.5 mm pitch ultra thin fine pitch quad flatpackage mechanical data

1. Values in inches are converted from mm and rounded to 4 decimal digits.

1. Dimensions are expressed in millimeters.

# 9 Revision history

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 27-Feb-2014 | 1        | Initial release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 29-Apr-2014 | 2        | Added WLCSP36 package.<br>Updated Table 2: Ultra-low-power STM32L052x6/x8 device features<br>and peripheral counts<br>Updated Figure 4: STM32L052x6/8 TFBGA64 ballout - 5x 5 mm.<br>Updated Table 5: Functionalities depending on the working mode (from<br>Run/active down to standby). Added Section 3.2: Interconnect matrix.<br>Replaced Ta I/O structure by TC, updated PA0/4/5, PC5/14, BOOTO<br>and NRST I/O structure, and added note 3 in Table 16:<br>STM32L052x6/8 pin definitions.<br>Updated Table 25: General operating conditions, Table 22: Voltage<br>characteristics and Table 23: Current characteristics.<br>Modified conditions in Table 28: Embedded internal reference voltage.<br>Updated Table 29: Current consumption in Run mode, code with data<br>processing running from Flash, Table 31: Current consumption in Run<br>mode, code with data processing running from RAM, Table 33: Current<br>consumption in Sleep mode, Table 34: Current consumption in Low-<br>power run mode, Table 35: Current consumption in Low-power sleep<br>mode, and Table 36: Typical and maximum current consumptions in<br>Standby mode. Added Figure 14: IDD vs VDD, at TA= 25/55/85/105 °C,<br>Run mode, code running from Flash memory, Range 2, HSE, 1WS,<br>Figure 15: IDD vs VDD, at TA= 25/55/85/105 °C, Run mode, code<br>running from Flash memory, Range 2, HSI16, 1WS, Figure 16: IDD vs<br>VDD, at TA= 25/55/85/105/125 °C, Low-power run mode, code running<br>from RAM, Range 3, MSI (Range 0) at 64 KHz, 0 WS, Figure 17: IDD<br>vs VDD, at TA= 25/55/85/105/125 °C, Stop mode with RTC enabled<br>and running on LSE Low drive and Figure 18: IDD vs VDD, at TA=<br>25/55/85/105/125 °C, Stop mode with RTC disabled, all clocks OFF.<br>Updated Table 46: ESD absolute maximum ratings, Table 58: I/O<br>current injection susceptibility and Table 59: I/O static characteristics,<br>and added Figure 24: VIH/VIL versus VDD (CMOS I/Os) and Figure 25:<br>VIH/VIL versus VDD (TTL I/Os). Updated Table 60: Cutput voltage<br>characteristics definition.<br>Updated Table 56: ESD absolute maximum ratings, Table 58: I/O<br>current injection susceptibility a |

### Table 93. Document revision history

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11-Mar-2016 | 6        | Updated number of SPIs on cover page and in <i>Table 2: Ultra-low-power</i><br><i>STM32L052x6X8 device features and peripheral counts.</i><br>Changed minimum comparator supply voltage to 1.65 V on cover page.<br>Added number of fast and standard channels in <i>Section 3.11: Analog-to-digital converter (ADC).</i><br>Updated Section <i>3.18.2: Universal synchronous/asynchronous receiver</i><br><i>transmitter (USART)</i> and <i>Section 3.18.4: Serial peripheral interface</i><br>( <i>SPI)/Inter-integrated sound (I2S)</i> to mention the fact that USARTs with<br>synchronous mode feature can be used as SPI master interfaces.<br>Added baudrate allowing to wake up the MCU from Stop mode in<br><i>Section 3.18.2: Universal synchronous/asynchronous receiver</i><br><i>transmitter (USART)</i> and <i>Section 3.18.3: Low-power universal</i><br><i>asynchronous receiver transmitter (LPUART).</i><br>In <i>Section 6: Electrical characteristics</i> , updated notes related to values<br>guaranteed by characterization.<br>Updated <i>Table 58: I/O current injection susceptibility.</i><br>Updated <i>Table 55: EMI characteristics.</i><br>Changed temperature condition in <i>Table 8: Internal</i> voltage reference<br><i>measured</i> values and <i>Table 27: Embedded internal</i> voltage reference<br><i>measured</i> values.<br><i>Section 6.3.15: 12-bit ADC characteristics:</i><br>- <i>Table 63: ADC characteristics:</i><br>Distinction made between V <sub>DDA</sub> for fast and standard channels;<br>added note 1<br>Added note 4 related to R <sub>ADC</sub> .<br>Updated <i>T<sub>RIG</sub>.</i><br>Updated <i>T<sub>RO</sub> and</i> added Note 2 in <i>Table 66: DAC characteristics.</i><br>Added <i>Table 64: RAIN max for fADC = 16</i> MHz for f <sub>ADC</sub> = 16 MHz<br>and distinction made between fast and standard channels.<br>Updated <i>T<sub>RO</sub></i> and added Note 2 in <i>Table 66: DAC characteristics.</i><br>Added <i>Table 73: USART/LPUART characteristics.</i><br>Updated <i>Figure 47: LQFP48 marking</i> example ( <i>package top view</i> ). |

| in Table 2: Ultra-low-power STM32L052x6/x8 device features and peripheral counts.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Added mission profile compliance with JEDEC JESD47 in Section 6.3         Absolute maximum ratings.         Added note 2. related to the position of the external capacitor below         Figure 27: Recommended NRST pin protection.         Updated R <sub>L</sub> in Table 63: ADC characteristics.         Updated Figure 32: 12-bit buffered/non-buffered DAC and added note         below figure.         07-Mar-2017         7         Updated t <sub>AF</sub> maximum value for range 1 in Table 72: I2C analog filter         characteristics.         Updated t <sub>WUUSART</sub> description in Table 73: USART/LPUART         characteristics.         NSS timing waveforms updated in Figure 33: SPI timing diagram - | 07-Mar-2017 | 7        | Updated number of 12S interfaces and removed 12S for STM32L052T8<br>in Table 2: Ultra-low-power STM32L052x6/x8 device features and<br>peripheral counts.<br>In Section 4: Pin descriptions, renamed USB_OE into USB_NOE.<br>Added mission profile compliance with JEDEC JESD47 in Section 6.2:<br>Absolute maximum ratings.<br>Added note 2. related to the position of the external capacitor below<br>Figure 27: Recommended NRST pin protection.<br>Updated R <sub>L</sub> in Table 63: ADC characteristics.<br>Updated Figure 32: 12-bit buffered/non-buffered DAC and added note<br>below figure.<br>Updated t <sub>AF</sub> maximum value for range 1 in Table 72: I2C analog filter<br>characteristics.<br>Updated t <sub>WUUSART</sub> description in Table 73: USART/LPUART<br>characteristics.<br>NSS timing waveforms updated in Figure 33: SPI timing diagram -<br>slave mode and CPHA = 0 and Figure 34: SPI timing diagram -<br>slave mode and CPHA = 1(1).<br>Previous WLCSP36 package renamed "Standard" WLCSP36; added<br>Note 2. below Figure 48: Standard WLCSP36 - 2.61 x 2.88 mm,<br>0.4 mm pitch wafer level chip scale package outline and updated<br>Table 85: Standard WLCSP36 - 2.61 x 2.88 mm, 0.4 mm pitch wafer<br>level chip scale mechanical data.<br>Added reference to optional marking or inset/upset marks in all |

| Table 93. | Document | revision | history | (continued)                   | ) |

|-----------|----------|----------|---------|-------------------------------|---|

|           |          |          |         | ( • • • • • • • • • • • • • • |   |