Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                      |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 32MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART, USB                          |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                            |

| Number of I/O              | 27                                                                    |

| Program Memory Size        | 32KB (32K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | 2K x 8                                                                |

| RAM Size                   | 8K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 3.6V                                                          |

| Data Converters            | A/D 10x12b; D/A 1x12b                                                 |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 32-UFQFN Exposed Pad                                                  |

| Supplier Device Package    | 32-UFQFPN (5x5)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l052k6u6 |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2 Description

The ultra-low-power STM32L052x6/8 microcontrollers incorporate the connectivity power of the universal serial bus (USB 2.0 crystal-less) with the high-performance ARM<sup>®</sup> Cortex<sup>®</sup>-M0+ 32-bit RISC core operating at a 32 MHz frequency, a memory protection unit (MPU), high-speed embedded memories (64 Kbytes of Flash program memory, 2 Kbytes of data EEPROM and 8 Kbytes of RAM) plus an extensive range of enhanced I/Os and peripherals.

The STM32L052x6/8 devices provide high power efficiency for a wide range of performance. It is achieved with a large choice of internal and external clock sources, an internal voltage adaptation and several low-power modes.

The STM32L052x6/8 devices offer several analog features, one 12-bit ADC with hardware oversampling, one DAC, two ultra-low-power comparators, several timers, one low-power timer (LPTIM), three general-purpose 16-bit timers and one basic timer, one RTC and one SysTick which can be used as timebases. They also feature two watchdogs, one watchdog with independent clock and window capability and one window watchdog based on bus clock.

Moreover, the STM32L052x6/8 devices embed standard and advanced communication interfaces: up to two I2C, two SPIs, one I2S, two USARTs, a low-power UART (LPUART), and a crystal-less USB. The devices offer up to 24 capacitive sensing channels to simply add touch sensing functionality to any application.

The STM32L052x6/8 also include a real-time clock and a set of backup registers that remain powered in Standby mode.

The ultra-low-power STM32L052x6/8 devices operate from a 1.8 to 3.6 V power supply (down to 1.65 V at power down) with BOR and from a 1.65 to 3.6 V power supply without BOR option. They are available in the -40 to +125 °C temperature range. A comprehensive set of power-saving modes allows the design of low-power applications.

## 2.2 Ultra-low-power device continuum

The ultra-low-power family offers a large choice of core and features, from 8-bit proprietary core up to ARM<sup>®</sup> Cortex<sup>®</sup>-M4, including ARM<sup>®</sup> Cortex<sup>®</sup>-M3 and ARM<sup>®</sup> Cortex<sup>®</sup>-M0+. The STM32Lx series are the best choice to answer your needs in terms of ultra-low-power features. The STM32 ultra-low-power series are the best solution for applications such as gaz/water meter, keyboard/mouse or fitness and healthcare application. Several built-in features like LCD drivers, dual-bank memory, low-power run mode, operational amplifiers, 128-bit AES, DAC, crystal-less USB and many other definitely help you building a highly cost optimized application by reducing BOM cost. STMicroelectronics, as a reliable and long-term manufacturer, ensures as much as possible pin-to-pin compatibility between all STM8Lx and STM32Lx on one hand, and between all STM32Lx and STM32Fx on the other hand. Thanks to this unprecedented scalability, your legacy application can be upgraded to respond to the latest market feature and efficiency requirements.

# 3.3 ARM<sup>®</sup> Cortex<sup>®</sup>-M0+ core with MPU

The Cortex-M0+ processor is an entry-level 32-bit ARM Cortex processor designed for a broad range of embedded applications. It offers significant benefits to developers, including:

- a simple architecture that is easy to learn and program

- ultra-low power, energy-efficient operation

- excellent code density

- deterministic, high-performance interrupt handling

- upward compatibility with Cortex-M processor family

- platform security robustness, with integrated Memory Protection Unit (MPU).

The Cortex-M0+ processor is built on a highly area and power optimized 32-bit processor core, with a 2-stage pipeline Von Neumann architecture. The processor delivers exceptional energy efficiency through a small but powerful instruction set and extensively optimized design, providing high-end processing hardware including a single-cycle multiplier.

The Cortex-M0+ processor provides the exceptional performance expected of a modern 32bit architecture, with a higher code density than other 8-bit and 16-bit microcontrollers.

Owing to its embedded ARM core, the STM32L052x6/8 are compatible with all ARM tools and software.

### Nested vectored interrupt controller (NVIC)

The ultra-low-power STM32L052x6/8 embed a nested vectored interrupt controller able to handle up to 32 maskable interrupt channels and 4 priority levels.

The Cortex-M0+ processor closely integrates a configurable Nested Vectored Interrupt Controller (NVIC), to deliver industry-leading interrupt performance. The NVIC:

- includes a Non-Maskable Interrupt (NMI)

- provides zero jitter interrupt option

- provides four interrupt priority levels

The tight integration of the processor core and NVIC provides fast execution of Interrupt Service Routines (ISRs), dramatically reducing the interrupt latency. This is achieved through the hardware stacking of registers, and the ability to abandon and restart load-multiple and store-multiple operations. Interrupt handlers do not require any assembler wrapper code, removing any code overhead from the ISRs. Tail-chaining optimization also significantly reduces the overhead when switching from one ISR to another.

To optimize low-power designs, the NVIC integrates with the sleep modes, that include a deep sleep function that enables the entire device to enter rapidly stop or standby mode.

This hardware block provides flexible interrupt management features with minimal interrupt latency.

## 3.10 Direct memory access (DMA)

The flexible 7-channel, general-purpose DMA is able to manage memory-to-memory, peripheral-to-memory and memory-to-peripheral transfers. The DMA controller supports circular buffer management, avoiding the generation of interrupts when the controller reaches the end of the buffer.

Each channel is connected to dedicated hardware DMA requests, with software trigger support for each channel. Configuration is done by software and transfer sizes between source and destination are independent.

The DMA can be used with the main peripherals: SPI, I<sup>2</sup>C, USART, LPUART, general-purpose timers, DAC, and ADC.

## 3.11 Analog-to-digital converter (ADC)

A native 12-bit, extended to 16-bit through hardware oversampling, analog-to-digital converter is embedded into STM32L052x6/8 device. It has up to 16 external channels and 3 internal channels (temperature sensor, voltage reference). Three channels, PA0, PA4 and PA5, are fast channels, while the others are standard channels.

The ADC performs conversions in single-shot or scan mode. In scan mode, automatic conversion is performed on a selected group of analog inputs.

The ADC frequency is independent from the CPU frequency, allowing maximum sampling rate of 1.14 MSPS even with a low CPU speed. The ADC consumption is low at all frequencies (~25  $\mu$ A at 10 kSPS, ~200  $\mu$ A at 1MSPS). An auto-shutdown function guarantees that the ADC is powered off except during the active conversion phase.

The ADC can be served by the DMA controller. It can operate from a supply voltage down to 1.65 V.

The ADC features a hardware oversampler up to 256 samples, this improves the resolution to 16 bits (see AN2668).

An analog watchdog feature allows very precise monitoring of the converted voltage of one, some or all scanned channels. An interrupt is generated when the converted voltage is outside the programmed thresholds.

The events generated by the general-purpose timers (TIMx) can be internally connected to the ADC start triggers, to allow the application to synchronize A/D conversions and timers.

## 3.12 Temperature sensor

The temperature sensor (T<sub>SENSE</sub>) generates a voltage V<sub>SENSE</sub> that varies linearly with temperature.

The temperature sensor is internally connected to the ADC\_IN18 input channel which is used to convert the sensor output voltage into a digital value.

The sensor provides good linearity but it has to be calibrated to obtain good overall accuracy of the temperature measurement. As the offset of the temperature sensor varies from chip to chip due to process variation, the uncalibrated internal temperature sensor is suitable for applications that detect temperature changes only.

DocID025936 Rev 7

### 3.17.4 SysTick timer

This timer is dedicated to the OS, but could also be used as a standard downcounter. It is based on a 24-bit downcounter with autoreload capability and a programmable clock source. It features a maskable system interrupt generation when the counter reaches '0'.

## 3.17.5 Independent watchdog (IWDG)

The independent watchdog is based on a 12-bit downcounter and 8-bit prescaler. It is clocked from an independent 37 kHz internal RC and, as it operates independently of the main clock, it can operate in Stop and Standby modes. It can be used either as a watchdog to reset the device when a problem occurs, or as a free-running timer for application timeout management. It is hardware- or software-configurable through the option bytes. The counter can be frozen in debug mode.

## 3.17.6 Window watchdog (WWDG)

The window watchdog is based on a 7-bit downcounter that can be set as free-running. It can be used as a watchdog to reset the device when a problem occurs. It is clocked from the main clock. It has an early warning interrupt capability and the counter can be frozen in debug mode.

# 3.18 Communication interfaces

## 3.18.1 I<sup>2</sup>C bus

two I<sup>2</sup>C interface (I2C1, I2C2) can operate in multimaster or slave modes.

Each I<sup>2</sup>C interface can support Standard mode (Sm, up to 100 kbit/s), Fast mode (Fm, up to 400 kbit/s) and Fast Mode Plus (Fm+, up to 1 Mbit/s) with 20 mA output drive on some I/Os.

7-bit and 10-bit addressing modes, multiple 7-bit slave addresses (2 addresses, 1 with configurable mask) are also supported as well as programmable analog and digital noise filters.

|                                     | Analog filter                                         | Digital filter                                                                                       |

|-------------------------------------|-------------------------------------------------------|------------------------------------------------------------------------------------------------------|

| Pulse width of<br>suppressed spikes | ≥ 50 ns                                               | Programmable length from 1 to 15<br>I2C peripheral clocks                                            |

| Benefits                            | Available in Stop mode                                | <ol> <li>Extra filtering capability vs.<br/>standard requirements.</li> <li>Stable length</li> </ol> |

| Drawbacks                           | Variations depending on temperature, voltage, process | Wakeup from Stop on address<br>match is not available when digital<br>filter is enabled.             |

In addition, I2C1 provides hardware support for SMBus 2.0 and PMBus 1.1: ARP capability, Host notify protocol, hardware CRC (PEC) generation/verification, timeouts verifications and ALERT protocol management. I2C1 also has a clock domain independent from the CPU clock, allowing the I2C1 to wake up the MCU from Stop mode on address match.

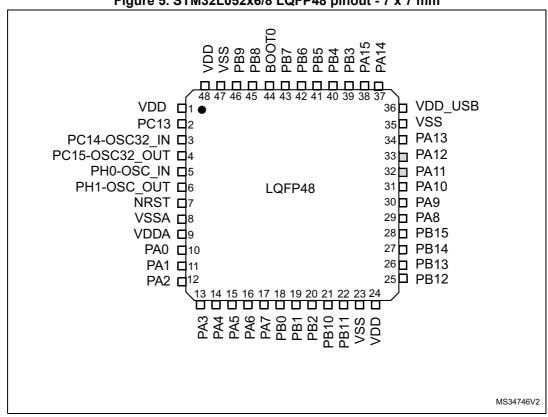

Figure 5. STM32L052x6/8 LQFP48 pinout - 7 x 7 mm

1. The above figure shows the package top view.

2. I/O pin supplied by VDD\_USB.

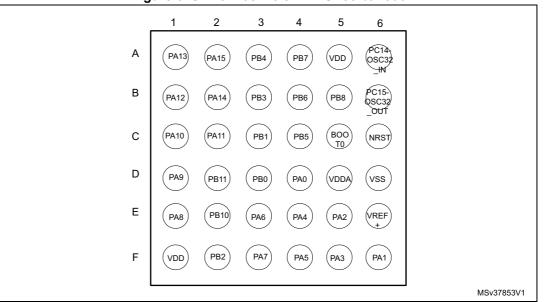

Figure 6. STM32L052x6/8 WLCSP36 ballout

1. The above figure shows the package top view.

DocID025936 Rev 7

|        |         | Pin Nu                 | ımber  |        |         |                                       | -        |               |       |                                                                       |                         |

|--------|---------|------------------------|--------|--------|---------|---------------------------------------|----------|---------------|-------|-----------------------------------------------------------------------|-------------------------|

| LQFP32 | UFQFN32 | WLCSP36 <sup>(1)</sup> | LQFP48 | LQFP64 | TFBGA64 | Pin name<br>(function after<br>reset) | Pin type | I/O structure | Notes | Alternate functions                                                   | Additional<br>functions |

| -      | -       | -                      | -      | 40     | D8      | PC9                                   | I/O      | FT            | -     | TIM21_ETR,<br>USB_NOE,<br>TSC_G8_IO4                                  | -                       |

| 18     | 18      | E1                     | 29     | 41     | D7      | PA8                                   | I/O      | FT            | -     | MCO,<br>USB_CRS_SYNC,<br>EVENTOUT,<br>USART1_CK                       | -                       |

| 19     | 19      | D1                     | 30     | 42     | C7      | PA9                                   | I/O      | FT            | -     | MCO, TSC_G4_IO1,<br>USART1_TX                                         | -                       |

| 20     | 20      | C1                     | 31     | 43     | C6      | PA10                                  | I/O      | FT            | -     | TSC_G4_IO2,<br>USART1_RX                                              | -                       |

| 21     | 21      | C2                     | 32     | 44     | C8      | PA11 <sup>(3)</sup>                   | I/O      | FT            | -     | SPI1_MISO,<br>EVENTOUT,<br>TSC_G4_IO3,<br>USART1_CTS,<br>COMP1_OUT    | USB_DM                  |

| 22     | 22      | B1                     | 33     | 45     | B8      | PA12 <sup>(3)</sup>                   | I/O      | FT            | -     | SPI1_MOSI,<br>EVENTOUT,<br>TSC_G4_IO4,<br>USART1_RTS_DE,<br>COMP2_OUT | USB_DP                  |

| 23     | 23      | A1                     | 34     | 46     | A8      | PA13                                  | I/O      | FT            | -     | SWDIO, USB_NOE                                                        | -                       |

| -      | -       | -                      | 35     | 47     | D5      | VSS                                   | S        | -             | -     | -                                                                     | -                       |

| -      | -       | -                      | 36     | 48     | E6      | VDD_USB                               | S        | -             | -     | -                                                                     | -                       |

| 24     | 24      | B2                     | 37     | 49     | A7      | PA14                                  | I/O      | FT            | -     | SWCLK, USART2_TX                                                      | -                       |

| 25     | 25      | A2                     | 38     | 50     | A6      | PA15                                  | I/O      | FT            | -     | SPI1_NSS,<br>TIM2_ETR,<br>EVENTOUT,<br>USART2_RX,<br>TIM2_CH1         | -                       |

| -      | -       | -                      | -      | 51     | B7      | PC10                                  | I/O      | FT            | -     | LPUART1_TX                                                            | -                       |

| -      | -       | -                      | -      | 52     | B6      | PC11                                  | I/O      | FT            | -     | LPUART1_RX                                                            | -                       |

| -      | -       | -                      | -      | 53     | C5      | PC12                                  | I/O      | FT            | -     | -                                                                     | -                       |

Table 16. STM32L052x6/8 pin definitions (continued)

|        |         | Pin Nu                 | ımber  |        |         |                                       |          |               |       |                                                      |                         |

|--------|---------|------------------------|--------|--------|---------|---------------------------------------|----------|---------------|-------|------------------------------------------------------|-------------------------|

| LQFP32 | UFQFN32 | WLCSP36 <sup>(1)</sup> | LQFP48 | LQFP64 | TFBGA64 | Pin name<br>(function after<br>reset) | Pin type | I/O structure | Notes | Alternate functions                                  | Additional<br>functions |

| -      | -       | -                      | -      | 54     | B5      | PD2                                   | I/O      | FT            | -     | LPUART1_RTS_DE                                       | -                       |

| 26     | 26      | В3                     | 39     | 55     | A5      | PB3                                   | I/O      | FT            | -     | SPI1_SCK,<br>TIM2_CH2,<br>TSC_G5I_O1,<br>EVENTOUT    | COMP2_INN               |

| 27     | 27      | A3                     | 40     | 56     | A4      | PB4                                   | I/O      | FT            | -     | SPI1_MISO,<br>EVENTOUT,<br>TSC_G5_IO2,<br>TIM22_CH1  | COMP2_INP               |

| 28     | 28      | C4                     | 41     | 57     | C4      | PB5                                   | I/O      | FT            | -     | SPI1_MOSI,<br>LPTIM1_IN1,<br>I2C1_SMBA,<br>TIM22_CH2 | COMP2_INP               |

| 29     | 29      | B4                     | 42     | 58     | D3      | PB6                                   | I/O      | FTf           | -     | USART1_TX,<br>I2C1_SCL,<br>LPTIM1_ETR,<br>TSC_G5_IO3 | COMP2_INP               |

| 30     | 30      | A4                     | 43     | 59     | C3      | PB7                                   | I/O      | FTf           | -     | USART1_RX,<br>I2C1_SDA,<br>LPTIM1_IN2,<br>TSC_G5_IO4 | COMP2_INP,<br>PVD_IN    |

| 31     | 31      | C5                     | 44     | 60     | B4      | BOOT0                                 | В        | -             | -     | -                                                    | -                       |

| -      | 32      | B5                     | 45     | 61     | B3      | PB8                                   | I/O      | FTf           | -     | TSC_SYNC,<br>I2C1_SCL                                | -                       |

| -      | -       | -                      | 46     | 62     | A3      | PB9                                   | I/O      | FTf           | -     | EVENTOUT,<br>I2C1_SDA,<br>SPI2_NSS/I2S2_WS           | -                       |

| 32     | -       | D6                     | 47     | 63     | D4      | VSS                                   | S        | -             | -     | -                                                    | -                       |

| 1      | 1       | A5                     | 48     | 64     | E4      | VDD                                   | S        | -             | -     | -                                                    | -                       |

Table 16. STM32L052x6/8 pin definitions (continued)

1. PB9/12/13/14/15, PH0/1 and PC13 GPIOs should be configured as output and driven Low, even if they are not available on this package.

2. PA4 offers a reduced touch sensing sensitivity. It is thus recommended to use it as sampling capacitor I/O.

3. These pins are powered by VDD\_USB. For all characteristics that refer to  $V_{DD}$ ,  $V_{DD_USB}$  must be used instead.

## 6.2 Absolute maximum ratings

Stresses above the absolute maximum ratings listed in *Table 22: Voltage characteristics*, *Table 23: Current characteristics*, and *Table 24: Thermal characteristics* may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability. Device mission profile (application conditions) is compliant with JEDEC JESD47 Qualification Standard. Extended mission profiles are available on demand.

| Symbol                              | Definition                                                                                                           | Min                  | Мах                  | Unit |

|-------------------------------------|----------------------------------------------------------------------------------------------------------------------|----------------------|----------------------|------|

| V <sub>DD</sub> -V <sub>SS</sub>    | External main supply voltage<br>(including V <sub>DDA</sub> , V <sub>DD_USB</sub> , V <sub>DD</sub> ) <sup>(1)</sup> | -0.3                 | 4.0                  |      |

|                                     | Input voltage on FT and FTf pins                                                                                     | V <sub>SS</sub> –0.3 | V <sub>DD</sub> +4.0 |      |

| V <sub>IN</sub> <sup>(2)</sup>      | Input voltage on TC pins                                                                                             | V <sub>SS</sub> –0.3 | 4.0                  | V    |

| VIN(-)                              | Input voltage on BOOT0                                                                                               | V <sub>SS</sub>      | V <sub>DD</sub> +4.0 |      |

|                                     | Input voltage on any other pin                                                                                       | V <sub>SS</sub> -0.3 | 4.0                  |      |

| $ \Delta V_{DD} $                   | Variations between different $V_{DDx}$ power pins                                                                    | -                    | 50                   |      |

| V <sub>DDA</sub> -V <sub>DDx</sub>  | DDx  Variations between any V <sub>DDx</sub> and V <sub>DDA</sub> power pins <sup>(3)</sup>                          |                      | 300                  | mV   |

| $ \Delta V_{SS} $                   | Variations between all different ground pins                                                                         | -                    | 50                   |      |

| V <sub>REF+</sub> –V <sub>DDA</sub> | Allowed voltage difference for $V_{REF^+} > V_{DDA}$                                                                 | -                    | 0.4                  | V    |

| V <sub>ESD(HBM)</sub>               | Electrostatic discharge voltage<br>(human body model)                                                                | see Sect             | ion 6.3.11           |      |

1. All main power (V<sub>DD</sub>,V<sub>DD</sub> USB, V<sub>DDA</sub>) and ground (V<sub>SS</sub>, V<sub>SSA</sub>) pins must always be connected to the external power supply, in the permitted range.

2. V<sub>IN</sub> maximum must always be respected. Refer to *Table* 23 for maximum allowed injected current values.

3. It is recommended to power V<sub>DD</sub> and V<sub>DDA</sub> from the same source. A maximum difference of 300 mV between V<sub>DD</sub> and V<sub>DDA</sub> can be tolerated during power-up and device operation. V<sub>DD\_USB</sub> is independent from V<sub>DD</sub> and V<sub>DDA</sub>: its value does not need to respect this rule.

| Symbol          | Parameter                         | Co                                                                | f <sub>HCLK</sub>                                  | Тур     | Max <sup>(1)</sup> | Unit |    |

|-----------------|-----------------------------------|-------------------------------------------------------------------|----------------------------------------------------|---------|--------------------|------|----|

|                 |                                   |                                                                   |                                                    | 1 MHz   | 165                | 230  |    |

|                 |                                   |                                                                   | Range 3, V <sub>CORE</sub> =1.2 V<br>VOS[1:0]=11   | 2 MHz   | 290                | 360  | μA |

|                 |                                   |                                                                   |                                                    | 4 MHz   | 555                | 630  |    |

|                 |                                   | f <sub>HSE</sub> = f <sub>HCLK</sub> up to                        |                                                    | 4 MHz   | 0.665              | 0.74 |    |

|                 |                                   | 16 MHz included,<br>f <sub>HSE</sub> = f <sub>HCLK</sub> /2 above | Range 2, V <sub>CORE</sub> =1.5 V,<br>VOS[1:0]=10, | 8 MHz   | 1.3                | 1.4  | μA |

| I <sub>DD</sub> | Supply<br>current in<br>Run mode, | 16 MHz (PLL ON) <sup>(2)</sup>                                    |                                                    | 16 MHz  | 2.6                | 2.8  |    |

|                 |                                   |                                                                   | Range 1, V <sub>CORE</sub> =1.8 V,<br>VOS[1:0]=01  | 8 MHz   | 1.55               | 1.7  |    |

| (Run<br>from    |                                   |                                                                   |                                                    | 16 MHz  | 3.1                | 3.4  |    |

| Flash) execute  | executed                          |                                                                   |                                                    | 32 MHz  | 6.3                | 6.8  |    |

|                 | from Flash                        |                                                                   |                                                    | 65 kHz  | 36.5               | 110  |    |

|                 |                                   |                                                                   | Range 3, V <sub>CORE</sub> =1.2 V,<br>VOS[1:0]=11  | 524 kHz | 99.5               | 190  |    |

|                 |                                   |                                                                   |                                                    | 4.2 MHz | 620                | 700  |    |

|                 |                                   |                                                                   | Range 2, V <sub>CORE</sub> =1.5 V,<br>VOS[1:0]=10, | 16 MHz  | 2.6                | 2.9  | mA |

|                 |                                   | HSI clock                                                         | Range 1, V <sub>CORE</sub> =1.8 V,<br>VOS[1:0]=01  | 32 MHz  | 6.25               | 7    | mA |

1. Guaranteed by characterization results at 125 °C, unless otherwise specified.

2. Oscillator bypassed (HSEBYP = 1 in RCC\_CR register).

| Table 30. Current consumption in Run mode vs code type, |

|---------------------------------------------------------|

| code with data processing running from Flash            |

| Symbol            | Parameter                                                           |                                                                                                                                                   | f <sub>HCLK</sub>                                    | Тур                       | Unit   |      |    |

|-------------------|---------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|---------------------------|--------|------|----|

| l <sub>DD</sub> c |                                                                     | f <sub>HSE</sub> = f <sub>HCLK</sub> up to<br>16 MHz included,<br>f <sub>HSE</sub> = f <sub>HCLK</sub> /2 above<br>16 MHz (PLL ON) <sup>(1)</sup> |                                                      | Dhrystone                 |        | 555  |    |

|                   |                                                                     |                                                                                                                                                   |                                                      | CoreMark                  |        | 585  |    |

|                   |                                                                     |                                                                                                                                                   | Range 3,<br>V <sub>CORE</sub> =1.2 V,                | Fibonacci                 | 4 MHz  | 440  | μA |

|                   | Supply<br>current in<br>Run mode,<br>code<br>executed<br>from Flash |                                                                                                                                                   | VOS[1:0]=11                                          | while(1)                  |        | 355  |    |

|                   |                                                                     |                                                                                                                                                   |                                                      | while(1), prefetch<br>OFF |        | 353  |    |

| from<br>Flash)    |                                                                     |                                                                                                                                                   | Range 1,<br>V <sub>CORE</sub> =1.8 V,<br>VOS[1:0]=01 | Dhrystone                 |        | 6.3  |    |

| F18511)           |                                                                     |                                                                                                                                                   |                                                      | CoreMark                  | 32 MHz | 6.3  | mA |

|                   |                                                                     |                                                                                                                                                   |                                                      | Fibonacci                 |        | 6.55 |    |

|                   |                                                                     |                                                                                                                                                   |                                                      | while(1)                  |        | 5.4  |    |

|                   |                                                                     |                                                                                                                                                   |                                                      | while(1), prefetch<br>OFF |        | 5.2  |    |

1. Oscillator bypassed (HSEBYP = 1 in RCC\_CR register).

| Symbol          | Parameter                 | Conditio                                | Тур                           | Max <sup>(1)</sup> | Unit |           |

|-----------------|---------------------------|-----------------------------------------|-------------------------------|--------------------|------|-----------|

|                 |                           |                                         | T <sub>A</sub> = − 40 to 25°C | 1.3                | 1.7  |           |

|                 |                           |                                         | T <sub>A</sub> = 55 °C        | -                  | 2.9  |           |

|                 |                           | Independent watchdog<br>and LSI enabled | T <sub>A</sub> = 85 °C        | -                  | 3.3  |           |

|                 |                           |                                         | T <sub>A</sub> = 105 °C       | -                  | 4.1  | - μΑ<br>- |

| I <sub>DD</sub> | Supply current in Standby |                                         | T <sub>A</sub> = 125 °C       | -                  | 8.5  |           |

| (Standby)       | mode                      | Independent watchdog<br>and LSI OFF     | T <sub>A</sub> = − 40 to 25°C | 0.29               | 0.6  |           |

|                 |                           |                                         | T <sub>A</sub> = 55 °C        | 0.32               | 0.9  |           |

|                 |                           |                                         | T <sub>A</sub> = 85 °C        | 0.5                | 2.3  |           |

|                 |                           |                                         | T <sub>A</sub> = 105 °C       | 0.94               | 3    |           |

|                 |                           |                                         | T <sub>A</sub> = 125 °C       | 2.6                | 7    |           |

#### Table 37. Typical and maximum current consumptions in Standby mode

1. Guaranteed by characterization results at 125 °C, unless otherwise specified

| Table 38. Average current c | onsumption during \ | Nakeup |

|-----------------------------|---------------------|--------|

|                             |                     |        |

| Symbol                                | parameter                                   | System frequency     | Current<br>consumption<br>during wakeup | Unit |

|---------------------------------------|---------------------------------------------|----------------------|-----------------------------------------|------|

|                                       |                                             | HSI                  | 1                                       |      |

|                                       |                                             | HSI/4                | 0,7                                     |      |

| I <sub>DD</sub> (Wakeup from<br>Stop) | Supply current during Wakeup from Stop mode | MSI clock = 4,2 MHz  | 0,7                                     | mA   |

|                                       |                                             | MSI clock = 1,05 MHz | 0,4                                     |      |

|                                       |                                             | MSI clock = 65 KHz   | 0,1                                     |      |

| I <sub>DD</sub> (Reset)               | Reset pin pulled down                       | -                    | 0,21                                    |      |

| I <sub>DD</sub> (Power-up)            | BOR ON                                      | -                    | 0,23                                    |      |

| I <sub>DD</sub> (Wakeup from          | With Fast wakeup set                        | MSI clock = 2,1 MHz  | 0,5                                     |      |

| StandBy)                              | With Fast wakeup disabled                   | MSI clock = 2,1 MHz  | 0,12                                    |      |

|                      |         | Typical          | consumption, V                                        | / <sub>DD</sub> = 3.0 V, T <sub>A</sub> = | 25 °C                         |                                |

|----------------------|---------|------------------|-------------------------------------------------------|-------------------------------------------|-------------------------------|--------------------------------|

| Per                  | ipheral |                  | Range 2,<br>V <sub>CORE</sub> =1.5 V<br>VOS[1:0] = 10 |                                           | Low-power<br>sleep and<br>run | Unit                           |

|                      | GPIOA   | 3.5              | 3                                                     | 2.5                                       | 2.5                           |                                |

| Cortex-              | GPIOB   | 3.5              | 2.5                                                   | 2                                         | 2.5                           |                                |

| M0+ core<br>I/O port | GPIOC   | 8.5              | 6.5                                                   | 5.5                                       | 7                             | µA/MHz<br>(f <sub>HCLK</sub> ) |

|                      | GPIOD   | 1                | 0.5                                                   | 0.5                                       | 0.5                           | (HCLK)                         |

|                      | GPIOH   | 1.5              | 1                                                     | 1                                         | 0.5                           |                                |

|                      | CRC     | 1.5              | 1                                                     | 1                                         | 1                             |                                |

|                      | FLASH   | 0 <sup>(3)</sup> | 0 <sup>(3)</sup>                                      | 0 <sup>(3)</sup>                          | 0 <sup>(3)</sup>              |                                |

| AHB                  | DMA1    | 10               | 8                                                     | 6.5                                       | 8.5                           | µA/MHz<br>(f <sub>HCLK</sub> ) |

|                      | RNG     | 5.5              | 1                                                     | 0.5                                       | 0.5                           | (HCLK)                         |

|                      | TSC     | 3                | 2.5                                                   | 2                                         | 3                             |                                |

| All e                | enabled | 283              | 225                                                   | 222.5                                     | 212.5                         | µA/MHz<br>(f <sub>HCLK</sub> ) |

| F                    | PWR     | 2.5              | 2                                                     | 2                                         | 1                             | µA/MHz<br>(f <sub>HCLK</sub> ) |

| Table 39. Peripheral | current consump | tion in Run or | Sleep mode <sup>(1)</sup> | (continued) |

|----------------------|-----------------|----------------|---------------------------|-------------|

|                      |                 |                |                           |             |

Data based on differential I<sub>DD</sub> measurement between all peripherals OFF an one peripheral with clock enabled, in the following conditions: f<sub>HCLK</sub> = 32 MHz (range 1), f<sub>HCLK</sub> = 16 MHz (range 2), f<sub>HCLK</sub> = 4 MHz (range 3), f<sub>HCLK</sub> = 64kHz (Low-power run/sleep), f<sub>APB1</sub> = f<sub>HCLK</sub>, f<sub>APB2</sub> = f<sub>HCLK</sub>, default prescaler value for each peripheral. The CPU is in Sleep mode in both cases. No I/O pins toggling. Not tested in production.

2. HSI oscillator is OFF for this measure.

3. Current consumption is negligible and close to 0  $\mu$ A.

| Sumbol                     | Symbol Peripheral            |                        | ption, T <sub>A</sub> = 25 °C | Unit |

|----------------------------|------------------------------|------------------------|-------------------------------|------|

| Symbol                     | Fenpheral                    | V <sub>DD</sub> =1.8 V | V <sub>DD</sub> =3.0 V        |      |

| I <sub>DD(PVD / BOR)</sub> | -                            | 0.7                    | 1.2                           |      |

| I <sub>REFINT</sub>        | -                            | -                      | 1.4                           |      |

| -                          | LSE Low drive <sup>(2)</sup> | 0,1                    | 0,1                           |      |

| -                          | LPTIM1, Input 100 Hz         | 0,01                   | 0,01                          | μΑ   |

| -                          | LPTIM1, Input 1 MHz          | 6                      | 6                             |      |

| -                          | LPUART1                      | 0,2                    | 0,2                           |      |

| -                          | RTC                          | 0,3                    | 0,48                          | 1    |

1. LPTIM peripheral cannot operate in Standby mode.

2. LSE Low drive consumption is the difference between an external clock on OSC32\_IN and a quartz between OSC32\_IN and OSC32\_OUT.-

### 6.3.5 Wakeup time from low-power mode

The wakeup times given in the following table are measured with the MSI or HSI16 RC oscillator. The clock source used to wake up the device depends on the current operating mode:

- Sleep mode: the clock source is the clock that was set before entering Sleep mode

- Stop mode: the clock source is either the MSI oscillator in the range configured before entering Stop mode, the HSI16 or HSI16/4.

- Standby mode: the clock source is the MSI oscillator running at 2.1 MHz

All timings are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 25*.

| Symbol               | Parameter                                                        | Conditions                                               | Тур | Max | Unit               |

|----------------------|------------------------------------------------------------------|----------------------------------------------------------|-----|-----|--------------------|

| t <sub>WUSLEEP</sub> | Wakeup from Sleep mode                                           | f <sub>HCLK</sub> = 32 MHz                               | 7   | 8   |                    |

| twusleep_lp          | Wakeup from Low-power sleep mode,<br>f <sub>HCLK</sub> = 262 kHz | f <sub>HCLK</sub> = 262 kHz<br>Flash memory enabled      | 7   | 8   | Number<br>of clock |

|                      |                                                                  | f <sub>HCLK</sub> = 262 kHz<br>Flash memory switched OFF | 9   | 10  | cycles             |

| Table 41. Low-power mode wakeup timings | Table 41. | Low-power | mode | wakeup | timings |

|-----------------------------------------|-----------|-----------|------|--------|---------|

|-----------------------------------------|-----------|-----------|------|--------|---------|

| Symbol   | Parameter                                                                     | Conditions                                                        | Тур | Max | Unit |

|----------|-------------------------------------------------------------------------------|-------------------------------------------------------------------|-----|-----|------|

|          |                                                                               | f <sub>HCLK</sub> = f <sub>MSI</sub> = 4.2 MHz                    | 5.0 | 8   |      |

|          | Wakeup from Stop mode, regulator in Run mode                                  | f <sub>HCLK</sub> = f <sub>HSI</sub> = 16 MHz                     | 4.9 | 7   |      |

|          |                                                                               | f <sub>HCLK</sub> = f <sub>HSI</sub> /4 = 4 MHz                   | 8.0 | 11  |      |

| twustop  |                                                                               | f <sub>HCLK</sub> = f <sub>MSI</sub> = 4.2 MHz<br>Voltage range 1 | 5.0 | 8   |      |

|          |                                                                               | f <sub>HCLK</sub> = f <sub>MSI</sub> = 4.2 MHz<br>Voltage range 2 | 5.0 | 8   |      |

|          |                                                                               | f <sub>HCLK</sub> = f <sub>MSI</sub> = 4.2 MHz<br>Voltage range 3 | 5.0 | 8   |      |

|          | Wakeup from Stop mode, regulator in low-<br>power mode                        | f <sub>HCLK</sub> = f <sub>MSI</sub> = 2.1 MHz                    | 7.3 | 13  |      |

|          |                                                                               | f <sub>HCLK</sub> = f <sub>MSI</sub> = 1.05 MHz                   | 13  | 23  | μs   |

|          |                                                                               | f <sub>HCLK</sub> = f <sub>MSI</sub> = 524 kHz                    | 28  | 38  |      |

|          |                                                                               | f <sub>HCLK</sub> = f <sub>MSI</sub> = 262 kHz                    | 51  | 65  |      |

|          |                                                                               | f <sub>HCLK</sub> = f <sub>MSI</sub> = 131 kHz                    | 100 | 120 |      |

|          |                                                                               | f <sub>HCLK</sub> = MSI = 65 kHz                                  | 190 | 260 |      |

|          |                                                                               | f <sub>HCLK</sub> = f <sub>HSI</sub> = 16 MHz                     | 4.9 | 7   |      |

|          |                                                                               | f <sub>HCLK</sub> = f <sub>HSI</sub> /4 = 4 MHz                   | 8.0 | 11  | -    |

|          |                                                                               | f <sub>HCLK</sub> = f <sub>HSI</sub> = 16 MHz                     | 4.9 | 7   |      |

|          | Wakeup from Stop mode, regulator in low-<br>power mode, code running from RAM | f <sub>HCLK</sub> = f <sub>HSI</sub> /4 = 4 MHz                   | 7.9 | 10  |      |

|          |                                                                               | f <sub>HCLK</sub> = f <sub>MSI</sub> = 4.2 MHz                    | 4.7 | 8   |      |

| +        | Wakeup from Standby mode, FWU bit = 1                                         | f <sub>HCLK</sub> = MSI = 2.1 MHz                                 | 65  | 130 | μs   |

| twustdby | Wakeup from Standby mode, FWU bit = 0                                         | f <sub>HCLK</sub> = MSI = 2.1 MHz                                 | 2.2 | 3   | ms   |

Table 41. Low-power mode wakeup timings (continued)

## 6.3.9 Memory characteristics

### **RAM** memory

| Symbol | Parameter                          | Conditions           | Min  | Тур | Max | Unit |

|--------|------------------------------------|----------------------|------|-----|-----|------|

| VRM    | Data retention mode <sup>(1)</sup> | STOP mode (or RESET) | 1.65 | -   | -   | V    |

Table 51. RAM and hardware registers

1. Minimum supply voltage without losing data stored in RAM (in Stop mode or under Reset) or in hardware registers (only in Stop mode).

### Flash memory and data EEPROM

|                   |                                                                                |                                                 |      |      | -                  |      |

|-------------------|--------------------------------------------------------------------------------|-------------------------------------------------|------|------|--------------------|------|

| Symbol            | Parameter                                                                      | Conditions                                      | Min  | Тур  | Max <sup>(1)</sup> | Unit |

| V <sub>DD</sub>   | Operating voltage<br>Read / Write / Erase                                      | -                                               | 1.65 | -    | 3.6                | V    |

| +                 | Programming time for                                                           | Erasing<br>Programming                          | -    | 3.28 | 3.94               | me   |

| t <sub>prog</sub> | word or half-page                                                              |                                                 | -    | 3.28 | 3.94               | ms   |

|                   | Average current during<br>the whole programming /<br>erase operation           | T <sub>A</sub> = 25 °C, V <sub>DD</sub> = 3.6 V | -    | 500  | 700                | μA   |

| I <sub>DD</sub>   | Maximum current (peak)<br>during the whole<br>programming / erase<br>operation |                                                 | -    | 1.5  | 2.5                | mA   |

### Table 52. Flash memory and data EEPROM characteristics

1. Guaranteed by design.

| Table 53. Flash memory | and data EEPROM endurance and retenti | on       |

|------------------------|---------------------------------------|----------|

|                        |                                       | <b>U</b> |

| Symbol                          | Parameter                                     | Conditions                                | Value              | Unit    |  |

|---------------------------------|-----------------------------------------------|-------------------------------------------|--------------------|---------|--|

| Symbol                          | Falameter                                     | Conditions                                | Min <sup>(1)</sup> | Unit    |  |

|                                 | Cycling (erase / write)<br>Program memory     | T - 40°C to 105 °C                        | 10                 |         |  |

| N <sub>CYC</sub> <sup>(2)</sup> | Cycling (erase / write)<br>EEPROM data memory | T <sub>A</sub> = -40°C to 105 °C          | 100                | kcycles |  |

| INCYC Y                         | Cycling (erase / write)<br>Program memory     | T <sub>A</sub> = -40°C to 125 °C          | 0.2                | KUYUUUS |  |

|                                 | Cycling (erase / write)<br>EEPROM data memory | $T_{A} = -40 \text{ C to } 125 \text{ C}$ | 2                  |         |  |

#### STM32L052x6 STM32L052x8

| Symbol                                | Parameter                          | Conditions                                      | Min                                                                        | Тур | Мах                                               | Unit                       |

|---------------------------------------|------------------------------------|-------------------------------------------------|----------------------------------------------------------------------------|-----|---------------------------------------------------|----------------------------|

| R <sub>ADC</sub> <sup>(3)(4)</sup>    | Sampling switch resistance         | -                                               | -                                                                          | -   | 1                                                 | kΩ                         |

| C <sub>ADC</sub> <sup>(3)</sup>       | Internal sample and hold capacitor | -                                               | -                                                                          | -   | 8                                                 | pF                         |

| ↓ (3)(5)                              | Calibration time                   | f <sub>ADC</sub> = 16 MHz                       | 5.2                                                                        |     | μs                                                |                            |

| t <sub>CAL</sub> <sup>(3)(5)</sup>    |                                    | -                                               |                                                                            | 83  |                                                   |                            |

|                                       |                                    | ADC clock = HSI16                               | 1.5 ADC<br>cycles + 2<br>f <sub>PCLK</sub> cycles                          | -   | 1.5 ADC<br>cycles + 3<br>f <sub>PCLK</sub> cycles | -                          |

| W <sub>LATENCY</sub> <sup>(6)</sup>   | ADC_DR register write<br>latency   | ADC clock = PCLK/2                              | -                                                                          | 4.5 | -                                                 | f <sub>PCLK</sub><br>cycle |

|                                       |                                    | ADC clock = PCLK/4                              | -                                                                          | 8.5 | -                                                 | f <sub>PCLK</sub><br>cycle |

|                                       | Trigger conversion latency         | $f_{ADC} = f_{PCLK}/2 = 16 \text{ MHz}$         | 0.266                                                                      |     |                                                   | μs                         |

|                                       |                                    | $f_{ADC} = f_{PCLK}/2$                          | 8.5                                                                        |     |                                                   | 1/f <sub>PCLK</sub>        |

| t <sub>latr</sub> (3)                 |                                    | f <sub>ADC</sub> = f <sub>PCLK</sub> /4 = 8 MHz | 0.516                                                                      |     |                                                   | μs                         |

|                                       |                                    | f <sub>ADC</sub> = f <sub>PCLK</sub> /4         | 16.5                                                                       |     |                                                   | 1/f <sub>PCLK</sub>        |

|                                       |                                    | f <sub>ADC</sub> = f <sub>HSI16</sub> = 16 MHz  | 0.252                                                                      | -   | 0.260                                             | μs                         |

| Jitter <sub>ADC</sub>                 | ADC jitter on trigger conversion   | f <sub>ADC</sub> = f <sub>HSI16</sub>           | -                                                                          | 1   | -                                                 | 1/f <sub>HSI16</sub>       |

| . (3)                                 | Complianting                       | f <sub>ADC</sub> = 16 MHz                       | 0.093                                                                      | -   | 10.03                                             | μs                         |

| t <sub>S</sub> <sup>(3)</sup>         | Sampling time                      | -                                               | 1.5                                                                        | -   | 160.5                                             | 1/f <sub>ADC</sub>         |

| t <sub>UP_LDO</sub> <sup>(3)(5)</sup> | Internal LDO power-up time         | -                                               | -                                                                          | -   | 10                                                | μs                         |

| t <sub>STAB</sub> <sup>(3)(5)</sup>   | ADC stabilization time             | -                                               |                                                                            | 14  | •                                                 | 1/f <sub>ADC</sub>         |

| + (3)                                 | Total conversion time              | f <sub>ADC</sub> = 16 MHz,<br>12-bit resolution | 0.875                                                                      | -   | 10.81                                             | μs                         |

| t <sub>ConV</sub> <sup>(3)</sup>      | (including sampling time)          | 12-bit resolution                               | 14 to 173 (t <sub>S</sub> for sampling +12.5 for successive approximation) |     |                                                   | 1/f <sub>ADC</sub>         |

Table 63. ADC characteristics (continued)

1. V<sub>DDA</sub> minimum value can be decreased in specific temperature conditions. Refer to Table 64: RAIN max for fADC = 16 MHz.

2. A current consumption proportional to the APB clock frequency has to be added (see *Table 39: Peripheral current consumption in Run or Sleep mode*).

3. Guaranteed by design.

Standard channels have an extra protection resistance which depends on supply voltage. Refer to Table 64: RAIN max for fADC = 16 MHz.

5. This parameter only includes the ADC timing. It does not take into account register access latency.

6. This parameter specifies the latency to transfer the conversion result into the ADC\_DR register. EOC bit is set to indicate the conversion is complete and has the same latency.

### **USB** characteristics

The USB interface is USB-IF certified (full speed).

| Table 78. USB startup time          |                              |     |      |

|-------------------------------------|------------------------------|-----|------|

| Symbol                              | Parameter                    | Мах | Unit |

| t <sub>STARTUP</sub> <sup>(1)</sup> | USB transceiver startup time | 1   | μs   |

1. Guaranteed by design.

| Table 79. USB DC electrical characteristics |

|---------------------------------------------|

|---------------------------------------------|

| Symbol                         | Parameter Conditions            |                                                            | Min. <sup>(1)</sup> | Max. <sup>(1)</sup> | Unit |

|--------------------------------|---------------------------------|------------------------------------------------------------|---------------------|---------------------|------|

| Input leve                     | Input levels                    |                                                            |                     |                     |      |

| V <sub>DD</sub>                | USB operating voltage           | -                                                          | 3.0                 | 3.6                 | V    |

| V <sub>DI</sub> <sup>(2)</sup> | Differential input sensitivity  | I(USB_DP, USB_DM)                                          | 0.2                 | -                   |      |

| V <sub>CM</sub> <sup>(2)</sup> | Differential common mode range  | Includes V <sub>DI</sub> range                             | 0.8                 | 2.5                 | V    |

| $V_{SE}^{(2)}$                 | Single ended receiver threshold | -                                                          | 1.3                 | 2.0                 |      |

| Output lev                     | vels                            |                                                            |                     |                     |      |

| V <sub>OL</sub> <sup>(3)</sup> | Static output level low         | ${\sf R}_{\sf L}$ of 1.5 k $\Omega$ to 3.6 ${\sf V}^{(4)}$ | -                   | 0.3                 | v    |

| V <sub>OH</sub> <sup>(3)</sup> | Static output level high        | $R_L$ of 15 k $\Omega$ to $V_{SS}^{(4)}$                   | 2.8                 | 3.6                 | v    |

1. All the voltages are measured from the local ground potential.

2. Guaranteed by characterization results.

3. Guaranteed by test in production.

4. R<sub>L</sub> is the load connected on the USB drivers.

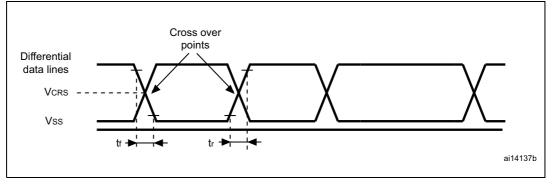

#### Figure 38. USB timings: definition of data signal rise and fall time

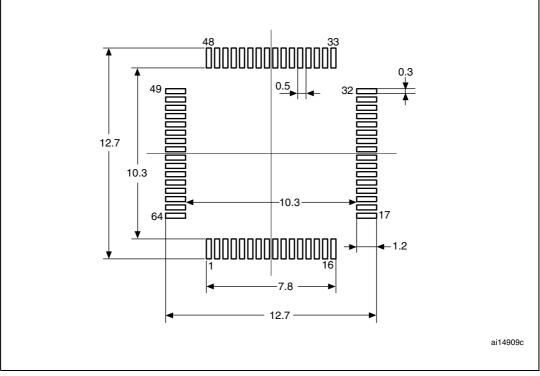

## Figure 40. LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat recommended footprint

1. Dimensions are expressed in millimeters.

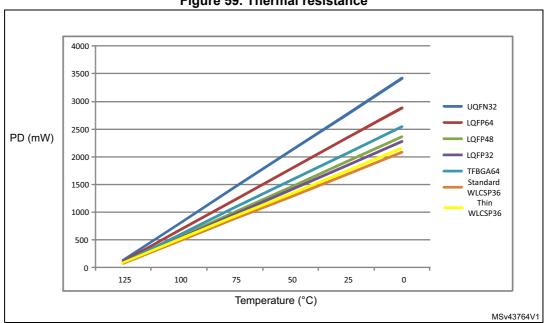

Figure 59. Thermal resistance

## 7.8.1 Reference document

JESD51-2 Integrated Circuits Thermal Test Method Environment Conditions - Natural Convection (Still Air). Available from www.jedec.org.

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 05-Sep-2014 | 4        | Extended operating temperature range to 125 °C.<br>Updated minimum ADC operating voltage to 1.65 V.<br>Changed number of I2S interface from 1 to 0 in <i>Table 2: Ultra-low-<br/>power STM32L052x6/x8 device features and peripheral counts</i> .<br>Replaced USART3 by LPUART1 in <i>Table 16: STM32L052x6/8 pin</i><br><i>definitions</i> and LPUART by LPUART1 in <i>Table 17: Alternate function</i><br><i>port A, Table 18: Alternate function port B, Table 19: Alternate function</i><br><i>port C, Table 20: Alternate function port D</i> and <i>Table 21: Alternate</i><br><i>function port H</i> . Updated PA6 in <i>Table 17: Alternate function port A</i> .<br>Updated temperature range in <i>Section 1: Description</i> , <i>Table 2: Ultra-<br/>low-power STM32L052x6/x8 device features and peripheral counts</i> .<br>Updated PD, <i>T<sub>A and</sub> T<sub>J</sub></i> to add range 3 in <i>Table 25: General operating</i><br><i>conditions</i> . Added range 3 in <i>Table 53: Flash memory</i> and data<br><i>EEPROM</i> endurance and retention, <i>Table 92: STM32L052x6/8</i><br>ordering information scheme. Update note 1 in <i>Table 29: Current</i><br><i>consumption in Run mode, code with data processing running from</i><br><i>Flash</i> , <i>Table 31: Current consumption in Rum mode, code with data</i><br><i>processing running from RAM</i> , <i>Table 33: Current consumption in Sleep</i><br><i>mode, Table 34: Current consumption in Low-power run mode,</i><br><i>Table 34: Current consumptions in Stop mode, Table 37:</i><br><i>Typical and maximum current consumptions in Stop mode, Table 37:</i><br><i>Typical and maximum current consumptions in Standby mode</i> and<br><i>Table 41: Low-power mode wakeup timings.</i> Updated <i>Figure 59:</i><br><i>Thermal resistance</i> and removed note 1. Updated <i>Figure 17: IDD</i><br>vs VDD, at <i>TA= 25/55/ 85/105/125 °C, Stop mode with RTC enabled</i><br><i>and running on LSE Low drive, Figure 18: IDD</i> vs VDD, at <i>TA=</i><br><i>25/55/85/105/125 °C, Stop mode with RTC enabled</i><br><i>and running on LSE Low drive, Figure 18: IDD</i> vs VDD, at <i>TA=</i><br><i>25/55/85/105/125 °C, Stop mode with RTC disabled, all clocks OFF.</i><br>Updated Table 43: <i>Low-speed external user clock characteristics.</i><br>Updated ACC <sub>HSI16</sub> temperature conditions in <i>Table 46: 16 MHz HSI16</i><br><i></i> |

Table 93. Document revision history (continued)