Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                        |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 32MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART, USB                            |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                              |

| Number of I/O              | 27                                                                      |

| Program Memory Size        | 32KB (32K x 8)                                                          |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 2K x 8                                                                  |

| RAM Size                   | 8K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 3.6V                                                            |

| Data Converters            | A/D 10x12b; D/A 1x12b                                                   |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

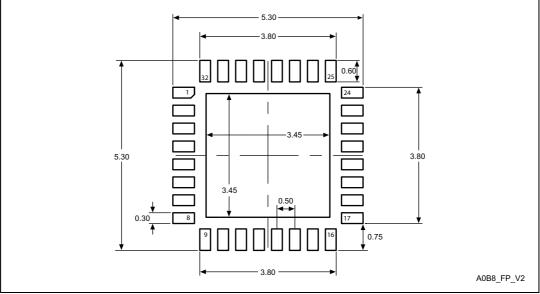

| Package / Case             | 32-UFQFN Exposed Pad                                                    |

| Supplier Device Package    | 32-UFQFPN (5x5)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l052k6u6tr |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 2 Description

The ultra-low-power STM32L052x6/8 microcontrollers incorporate the connectivity power of the universal serial bus (USB 2.0 crystal-less) with the high-performance ARM<sup>®</sup> Cortex<sup>®</sup>-M0+ 32-bit RISC core operating at a 32 MHz frequency, a memory protection unit (MPU), high-speed embedded memories (64 Kbytes of Flash program memory, 2 Kbytes of data EEPROM and 8 Kbytes of RAM) plus an extensive range of enhanced I/Os and peripherals.

The STM32L052x6/8 devices provide high power efficiency for a wide range of performance. It is achieved with a large choice of internal and external clock sources, an internal voltage adaptation and several low-power modes.

The STM32L052x6/8 devices offer several analog features, one 12-bit ADC with hardware oversampling, one DAC, two ultra-low-power comparators, several timers, one low-power timer (LPTIM), three general-purpose 16-bit timers and one basic timer, one RTC and one SysTick which can be used as timebases. They also feature two watchdogs, one watchdog with independent clock and window capability and one window watchdog based on bus clock.

Moreover, the STM32L052x6/8 devices embed standard and advanced communication interfaces: up to two I2C, two SPIs, one I2S, two USARTs, a low-power UART (LPUART), and a crystal-less USB. The devices offer up to 24 capacitive sensing channels to simply add touch sensing functionality to any application.

The STM32L052x6/8 also include a real-time clock and a set of backup registers that remain powered in Standby mode.

The ultra-low-power STM32L052x6/8 devices operate from a 1.8 to 3.6 V power supply (down to 1.65 V at power down) with BOR and from a 1.65 to 3.6 V power supply without BOR option. They are available in the -40 to +125 °C temperature range. A comprehensive set of power-saving modes allows the design of low-power applications.

| Peripheral             | STM32L0<br>52T6 | STM32<br>L052K6                                                             | STM32<br>L052C6 | STM32<br>L052R6       | STM32L<br>052T8 | STM32<br>L052K8         | STM32<br>L052C8 | STM32<br>L052R8       |

|------------------------|-----------------|-----------------------------------------------------------------------------|-----------------|-----------------------|-----------------|-------------------------|-----------------|-----------------------|

| Operating temperatures |                 | Ambient temperature: –40 to +125 °C<br>Junction temperature: –40 to +130 °C |                 |                       |                 |                         |                 |                       |

| Packages               | WLCSP<br>36     | LQFP32,<br>UFQFPN<br>32                                                     | LQFP48          | LQFP64<br>TFBGA<br>64 | WLCSP<br>36     | LQFP32,<br>UFQFPN<br>32 | LQFP48          | LQFP64<br>TFBGA<br>64 |

#### Table 2. Ultra-low-power STM32L052x6/x8 device features and peripheral counts (continued)

1. 2 SPI interfaces are USARTs operating in SPI master mode.

2. LQFP32 has two GPIOs, less than UFQFPN32 (27).

3. TFBGA64 has one GPIO, one ADC input and one capacitive sensing channel less than LQFP64.

## 3.4 Reset and supply management

#### 3.4.1 Power supply schemes

- V<sub>DD</sub> = 1.65 to 3.6 V: external power supply for I/Os and the internal regulator. Provided externally through V<sub>DD</sub> pins.

- V<sub>SSA</sub>, V<sub>DDA</sub> = 1.65 to 3.6 V: external analog power supplies for ADC, DAC, reset blocks, RCs and PLL (minimum voltage to be applied to V<sub>DDA</sub> is 1.8 V when the DAC is used). V<sub>DDA</sub> and V<sub>SSA</sub> must be connected to V<sub>DD</sub> and V<sub>SS</sub>, respectively.

- V<sub>DD\_USB</sub> = 1.65 to 3.6V: external power supply for USB transceiver, USB\_DM (PA11) and USB\_DP (PA12). To guarantee a correct voltage level for USB communication V<sub>DD\_USB</sub> must be above 3.0V. If USB is not used this pin must be tied to V<sub>DD</sub>.

#### 3.4.2 Power supply supervisor

The devices have an integrated ZEROPOWER power-on reset (POR)/power-down reset (PDR) that can be coupled with a brownout reset (BOR) circuitry.

Two versions are available:

- The version with BOR activated at power-on operates between 1.8 V and 3.6 V.

- The other version without BOR operates between 1.65 V and 3.6 V.

After the  $V_{DD}$  threshold is reached (1.65 V or 1.8 V depending on the BOR which is active or not at power-on), the option byte loading process starts, either to confirm or modify default thresholds, or to disable the BOR permanently: in this case, the VDD min value becomes 1.65 V (whatever the version, BOR active or not, at power-on).

When BOR is active at power-on, it ensures proper operation starting from 1.8 V whatever the power ramp-up phase before it reaches 1.8 V. When BOR is not active at power-up, the power ramp-up should guarantee that 1.65 V is reached on  $V_{DD}$  at least 1 ms after it exits the POR area.

Five BOR thresholds are available through option bytes, starting from 1.8 V to 3 V. To reduce the power consumption in Stop mode, it is possible to automatically switch off the internal reference voltage ( $V_{REFINT}$ ) in Stop mode. The device remains in reset mode when  $V_{DD}$  is below a specified threshold,  $V_{POR/PDR}$  or  $V_{BOR}$ , without the need for any external reset circuit.

Note: The start-up time at power-on is typically 3.3 ms when BOR is active at power-up, the startup time at power-on can be decreased down to 1 ms typically for devices with BOR inactive at power-up.

The devices feature an embedded programmable voltage detector (PVD) that monitors the  $V_{DD/VDDA}$  power supply and compares it to the  $V_{PVD}$  threshold. This PVD offers 7 different levels between 1.85 V and 3.05 V, chosen by software, with a step around 200 mV. An interrupt can be generated when  $V_{DD/VDDA}$  drops below the  $V_{PVD}$  threshold and/or when  $V_{DD/VDDA}$  is higher than the  $V_{PVD}$  threshold. The interrupt service routine can then generate a warning message and/or put the MCU into a safe state. The PVD is enabled by software.

## 3.8 Memories

The STM32L052x6/8 devices have the following features:

- 8 Kbytes of embedded SRAM accessed (read/write) at CPU clock speed with 0 wait states. With the enhanced bus matrix, operating the RAM does not lead to any performance penalty during accesses to the system bus (AHB and APB buses).

- The non-volatile memory is divided into three arrays:

- 32 or 64 Kbytes of embedded Flash program memory

- 2 Kbytes of data EEPROM

- Information block containing 32 user and factory options bytes plus 4 Kbytes of system memory

The user options bytes are used to write-protect or read-out protect the memory (with 4 Kbyte granularity) and/or readout-protect the whole memory with the following options:

- Level 0: no protection

- Level 1: memory readout protected.

The Flash memory cannot be read from or written to if either debug features are connected or boot in RAM is selected

• Level 2: chip readout protected, debug features (Cortex-M0+ serial wire) and boot in RAM selection disabled (debugline fuse)

The firewall protects parts of code/data from access by the rest of the code that is executed outside of the protected area. The granularity of the protected code segment or the non-volatile data segment is 256 bytes (Flash memory or EEPROM) against 64 bytes for the volatile data segment (RAM).

The whole non-volatile memory embeds the error correction code (ECC) feature.

## 3.9 Boot modes

At startup, BOOT0 pin and nBOOT1 option bit are used to select one of three boot options:

- Boot from Flash memory

- Boot from System memory

- Boot from embedded RAM

The boot loader is located in System memory. It is used to reprogram the Flash memory by using SPI1(PA4, PA5, PA6, PA7) or SPI2 (PB12, PB13, PB14, PB15), USART1(PA9, PA10) or USART2(PA2, PA3). See STM32<sup>™</sup> microcontroller system memory boot mode AN2606 for details.

| Group | Capacitive sensing signal name | Pin<br>name        | Group | Capacitive sensing signal name | Pin<br>name |

|-------|--------------------------------|--------------------|-------|--------------------------------|-------------|

|       | TSC_G1_IO1                     | PA0                |       | TSC_G5_IO1                     | PB3         |

| 1     | TSC_G1_IO2                     | PA1                | 5     | TSC_G5_IO2                     | PB4         |

| 1     | TSC_G1_IO3                     | PA2                | 5     | TSC_G5_IO3                     | PB6         |

|       | TSC_G1_IO4                     | PA3                |       | TSC_G5_IO4                     | PB7         |

|       | TSC_G2_IO1                     | PA4 <sup>(1)</sup> |       | TSC_G6_IO1                     | PB11        |

| 2     | TSC_G2_IO2                     | PA5                | 6     | TSC_G6_IO2                     | PB12        |

| 2     | TSC_G2_IO3                     | PA6                | 0     | TSC_G6_IO3                     | PB13        |

|       | TSC_G2_IO4                     | PA7                |       | TSC_G6_IO4                     | PB14        |

|       | TSC_G3_IO1                     | PC5                |       | TSC_G7_IO1                     | PC0         |

| 3     | TSC_G3_IO2                     | PB0                | 7     | TSC_G7_IO2                     | PC1         |

| 5     | TSC_G3_IO3                     | PB1                | '     | TSC_G7_IO3                     | PC2         |

|       | TSC_G3_IO4                     | PB2                |       | TSC_G7_IO4                     | PC3         |

|       | TSC_G4_IO1                     | PA9                |       | TSC_G8_IO1                     | PC6         |

| 4     | TSC_G4_IO2                     | PA10               | 8     | TSC_G8_IO2                     | PC7         |

| 4     | TSC_G4_IO3                     | PA11               | 0     | TSC_G8_IO3                     | PC8         |

|       | TSC_G4_IO4                     | PA12               |       | TSC_G8_IO4                     | PC9         |

Table 9. Capacitive sensing GPIOs available on STM32L052x6/8 devices

This GPIO offers a reduced touch sensing sensitivity. It is thus recommended to use it as sampling capacitor I/O.

## 3.17 Timers and watchdogs

The ultra-low-power STM32L052x6/8 devices include three general-purpose timers, one low- power timer (LPTIM), one basic timer, two watchdog timers and the SysTick timer.

*Table 10* compares the features of the general-purpose and basic timers.

| Timer           | Counter resolution | Counter type         | Prescaler factor                   | DMA<br>request<br>generation | Capture/compare<br>channels | Complementary<br>outputs |

|-----------------|--------------------|----------------------|------------------------------------|------------------------------|-----------------------------|--------------------------|

| TIM2            | 16-bit             | Up, down,<br>up/down | Any integer between<br>1 and 65536 | Yes                          | 4                           | No                       |

| TIM21,<br>TIM22 | 16-bit             | Up, down,<br>up/down | Any integer between<br>1 and 65536 | No                           | 2                           | No                       |

| TIM6            | 16-bit             | Up                   | Any integer between<br>1 and 65536 | Yes                          | 0                           | No                       |

Table 10. Timer feature comparison

Each I2C interface can be served by the DMA controller.

Refer to Table 12 for an overview of I2C interface features.

| I2C features <sup>(1)</sup>                                  | I2C1 | I2C2             |

|--------------------------------------------------------------|------|------------------|

| 7-bit addressing mode                                        | Х    | Х                |

| 10-bit addressing mode                                       | X    | Х                |

| Standard mode (up to 100 kbit/s)                             | X    | Х                |

| Fast mode (up to 400 kbit/s)                                 | X    | Х                |

| Fast Mode Plus with 20 mA output drive I/Os (up to 1 Mbit/s) | Х    | X <sup>(2)</sup> |

| Independent clock                                            | Х    | -                |

| SMBus                                                        | X    | -                |

| Wakeup from STOP                                             | Х    | -                |

| Table 12. STM32L052x6/8 I <sup>2</sup> | C implementation |

|----------------------------------------|------------------|

|----------------------------------------|------------------|

1. X = supported.

2. See for the list of I/Os that feature Fast Mode Plus capability

### 3.18.2 Universal synchronous/asynchronous receiver transmitter (USART)

The two USART interfaces (USART1, USART2) are able to communicate at speeds of up to 4 Mbit/s.

They provide hardware management of the CTS, RTS and RS485 driver enable (DE) signals, multiprocessor communication mode, master synchronous communication and single-wire half-duplex communication mode. They also support SmartCard communication (ISO 7816), IrDA SIR ENDEC, LIN Master/Slave capability, auto baud rate feature and has a clock domain independent from the CPU clock, allowing to wake up the MCU from Stop mode using baudrates up to 42 Kbaud.

All USART interfaces can be served by the DMA controller.

Table 13 for the supported modes and features of USART interfaces.

| USART modes/features <sup>(1)</sup>         | USART1 and USART2 |

|---------------------------------------------|-------------------|

| Hardware flow control for modem             | Х                 |

| Continuous communication using DMA          | X                 |

| Multiprocessor communication                | Х                 |

| Synchronous mode <sup>(2)</sup>             | Х                 |

| Smartcard mode                              | X                 |

| Single-wire half-duplex communication       | Х                 |

| IrDA SIR ENDEC block                        | Х                 |

| LIN mode                                    | Х                 |

| Dual clock domain and wakeup from Stop mode | X                 |

| Receiver timeout interrupt                  | X                 |

| Table 13 | . USART | implementation |

|----------|---------|----------------|

|----------|---------|----------------|

| Symbol               | Parameter                            | Conditions                          | Min | Max | Unit |

|----------------------|--------------------------------------|-------------------------------------|-----|-----|------|

|                      |                                      | Maximum power dissipation (range 6) | -40 | 85  |      |

| TA Temperature range | Maximum power dissipation (range 7)  |                                     | 105 |     |      |

|                      |                                      | Maximum power dissipation (range 3) | -40 | 125 | °C   |

|                      | Junction temperature range (range 6) | -40 °C ≤T <sub>A</sub> ≤85 °        | -40 | 105 |      |

| TJ                   | Junction temperature range (range 7) | -40 °C ≤T <sub>A</sub> ≤105 °C      | -40 | 125 |      |

|                      | Junction temperature range (range 3) | -40 °C ≤T <sub>A</sub> ≤125 °C      | -40 | 130 |      |

Table 25. General operating conditions (continued)

1. It is recommended to power  $V_{DD}$  and  $V_{DDA}$  from the same source. A maximum difference of 300 mV between  $V_{DD}$  and  $V_{DDA}$  can be tolerated during power-up and normal operation.

2.  $V_{DD\_USB}$  must respect the following conditions:

- When V\_{DD} is powered-on (V\_{DD} < V\_{DD\\_min}), V\_{DD\\_USB} should be always lower than V\_{DD.}

- When V\_{DD} is powered-down (V\_{DD} < V\_{DD\\_min}), V\_{DD\\_USB} should be always lower than V\_{DD}.

- In operating mode,  $V_{DD\_USB}$  could be lower or higher  $V_{DD.}$

- If the USB is not used,  $V_{DD\_USB}$  must range from  $V_{DD\_min}$  to  $V_{DD\_max}$  to be able to use PA11 and PA12 as standard I/Os.

3. To sustain a voltage higher than  $V_{DD}$ +0.3V, the internal pull-up/pull-down resistors must be disabled.

If T<sub>A</sub> is lower, higher P<sub>D</sub> values are allowed as long as T<sub>J</sub> does not exceed T<sub>J</sub> max (see Table 24: Thermal characteristics on page 56).

| Symbol                                                                                 | Parameter                      | Co                                                                | f <sub>HCLK</sub>                                  | Тур     | Max <sup>(1)</sup> | Unit |    |

|----------------------------------------------------------------------------------------|--------------------------------|-------------------------------------------------------------------|----------------------------------------------------|---------|--------------------|------|----|

|                                                                                        |                                |                                                                   |                                                    | 1 MHz   | 165                | 230  |    |

|                                                                                        |                                |                                                                   | Range 3, V <sub>CORE</sub> =1.2 V<br>VOS[1:0]=11   | 2 MHz   | 290                | 360  | μA |

|                                                                                        |                                |                                                                   |                                                    | 4 MHz   | 555                | 630  |    |

|                                                                                        |                                | f <sub>HSE</sub> = f <sub>HCLK</sub> up to                        |                                                    | 4 MHz   | 0.665              | 0.74 |    |

|                                                                                        |                                | 16 MHz included,<br>f <sub>HSE</sub> = f <sub>HCLK</sub> /2 above | Range 2, V <sub>CORE</sub> =1.5 V,<br>VOS[1:0]=10, | 8 MHz   | 1.3                | 1.4  |    |

| Supply<br>I <sub>DD</sub> current in<br>(Run Run mode,<br>from code<br>Flash) executed | 16 MHz (PLL ON) <sup>(2)</sup> |                                                                   | 16 MHz                                             | 2.6     | 2.8                | mA   |    |

|                                                                                        |                                | Range 1, V <sub>CORE</sub> =1.8 V,<br>VOS[1:0]=01                 | 8 MHz                                              | 1.55    | 1.7                |      |    |

|                                                                                        |                                |                                                                   | 16 MHz                                             | 3.1     | 3.4                |      |    |

|                                                                                        |                                |                                                                   | 32 MHz                                             | 6.3     | 6.8                |      |    |

|                                                                                        | from Flash                     |                                                                   | Range 3, V <sub>CORE</sub> =1.2 V,<br>VOS[1:0]=11  | 65 kHz  | 36.5               | 110  |    |

|                                                                                        |                                | MSI clock                                                         |                                                    | 524 kHz | 99.5               | 190  | μA |

|                                                                                        |                                |                                                                   | 4.2 MHz                                            | 620     | 700                |      |    |

|                                                                                        | HSI clock                      |                                                                   | Range 2, V <sub>CORE</sub> =1.5 V,<br>VOS[1:0]=10, | 16 MHz  | 2.6                | 2.9  | mA |

|                                                                                        |                                | Range 1, V <sub>CORE</sub> =1.8 V,<br>VOS[1:0]=01                 | 32 MHz                                             | 6.25    | 7                  | mA   |    |

1. Guaranteed by characterization results at 125 °C, unless otherwise specified.

2. Oscillator bypassed (HSEBYP = 1 in RCC\_CR register).

| Table 30. Current consumption in Run mode vs code type, |

|---------------------------------------------------------|

| code with data processing running from Flash            |

| Symbol         | Parameter                                                      | Conditions                                                     |                                       |                           | f <sub>HCLK</sub> | Тур  | Unit |

|----------------|----------------------------------------------------------------|----------------------------------------------------------------|---------------------------------------|---------------------------|-------------------|------|------|

|                |                                                                |                                                                | Dhrystone                             |                           | 555               |      |      |

|                |                                                                |                                                                | CoreMark                              |                           | 585               |      |      |

|                |                                                                |                                                                | Range 3,<br>V <sub>CORE</sub> =1.2 V, | Fibonacci                 | 4 MHz             | 440  | μA   |

|                |                                                                | VOS[1:0]=11                                                    | while(1)                              |                           | 355               | μ. τ |      |

|                | f <sub>HSE</sub> = f <sub>HCLK</sub> up to<br>16 MHz included, |                                                                | while(1), prefetch<br>OFF             |                           | 353               |      |      |

| from<br>Flash) | code<br>executed                                               | $f_{HSE} = f_{HCLK}/2$ above<br>16 MHz (PLL ON) <sup>(1)</sup> |                                       | Dhrystone                 |                   | 6.3  | mA   |

| F18511)        | from Flash                                                     | Flash                                                          |                                       | CoreMark                  | -                 | 6.3  |      |

|                |                                                                |                                                                | Range 1,<br>V <sub>CORE</sub> =1.8 V, | Fibonacci                 | 32 MHz            | 6.55 |      |

|                |                                                                | VOS[1:0]=01                                                    | while(1)                              |                           | 5.4               |      |      |

|                |                                                                |                                                                |                                       | while(1), prefetch<br>OFF |                   | 5.2  |      |

1. Oscillator bypassed (HSEBYP = 1 in RCC\_CR register).

### 6.3.12 I/O current injection characteristics

As a general rule, current injection to the I/O pins, due to external voltage below  $V_{SS}$  or above  $V_{DD}$  (for standard pins) should be avoided during normal product operation. However, in order to give an indication of the robustness of the microcontroller in cases when abnormal injection accidentally happens, susceptibility tests are performed on a sample basis during device characterization.

#### Functional susceptibility to I/O current injection

While a simple application is executed on the device, the device is stressed by injecting current into the I/O pins programmed in floating input mode. While current is injected into the I/O pin, one at a time, the device is checked for functional failures.

The failure is indicated by an out of range parameter: ADC error above a certain limit (higher than 5 LSB TUE), out of conventional limits of induced leakage current on adjacent pins (out of  $-5 \mu A/+0 \mu A$  range), or other functional failure (for example reset occurrence oscillator frequency deviation).

The test results are given in the Table 58.

|                  |                                                                     | Functional s       |                    |      |

|------------------|---------------------------------------------------------------------|--------------------|--------------------|------|

| Symbol           | Description                                                         | Negative injection | Positive injection | Unit |

| I <sub>INJ</sub> | Injected current on BOOT0                                           | -0                 | NA                 |      |

|                  | Injected current on PA0, PA4, PA5, PA11,<br>PA12, PC15, PH0 and PH1 | -5                 | 0                  | mA   |

|                  | Injected current on any other FT, FTf pins                          | -5 <sup>(1)</sup>  | NA                 |      |

|                  | Injected current on any other pins                                  | -5 <sup>(1)</sup>  | +5                 |      |

#### Table 58. I/O current injection susceptibility

1. It is recommended to add a Schottky diode (pin to ground) to analog pins which may potentially inject negative currents.

### 6.3.13 I/O port characteristics

#### General input/output characteristics

Unless otherwise specified, the parameters given in *Table 59* are derived from tests performed under the conditions summarized in *Table 25*. All I/Os are CMOS and TTL compliant.

| Symbol           | Parameter                                         | Conditions                                                                                                    | Min                 | Тур                                | Мах                                | Unit |

|------------------|---------------------------------------------------|---------------------------------------------------------------------------------------------------------------|---------------------|------------------------------------|------------------------------------|------|

| V <sub>IL</sub>  | Input low level voltage                           | TC, FT, FTf, RST<br>I/Os                                                                                      | -                   | -                                  | 0.3V <sub>DD</sub>                 |      |

|                  |                                                   | BOOT0 pin                                                                                                     | -                   | -                                  | 0.14V <sub>DD</sub> <sup>(1)</sup> |      |

| $V_{\text{IH}}$  | Input high level voltage                          | All I/Os                                                                                                      | 0.7 V <sub>DD</sub> | -                                  | -                                  | V    |

| V                | I/O Schmitt trigger voltage hysteresis            | Standard I/Os                                                                                                 | -                   | 10% V <sub>DD</sub> <sup>(3)</sup> | -                                  |      |

| V <sub>hys</sub> | (2)                                               | BOOT0 pin                                                                                                     | -                   | 0.01                               | -                                  |      |

|                  |                                                   | V <sub>SS</sub> ≤V <sub>IN</sub> ≤V <sub>DD</sub><br>All I/Os except for<br>PA11, PA12, BOOT0<br>and FTf I/Os | -                   | -                                  | ±50                                |      |

|                  | Input leakage current <sup>(4)</sup>              | V <sub>SS</sub> ≤V <sub>IN</sub> ≤V <sub>DD</sub> ,<br>PA11 and PA12 I/Os                                     | -                   | -                                  | -50/+250                           | nA   |

|                  |                                                   | V <sub>SS</sub> ≤V <sub>IN</sub> ≤V <sub>DD</sub><br>FTf I/Os                                                 | -                   | -                                  | ±100                               |      |

| I <sub>lkg</sub> |                                                   | V <sub>DD</sub> ≤V <sub>IN</sub> ≤5 V<br>All I/Os except for<br>PA11, PA12, BOOT0<br>and FTf I/Os             | -                   | -                                  | 200                                | nA   |

|                  |                                                   | V <sub>DD</sub> ≤V <sub>IN</sub> ≤5 V<br>FTf I/Os                                                             | -                   | -                                  | 500                                |      |

|                  |                                                   | V <sub>DD</sub> ⊴V <sub>IN</sub> ⊴5 V<br>PA11, PA12 and<br>BOOT0                                              | -                   | -                                  | 10                                 | μΑ   |

| R <sub>PU</sub>  | Weak pull-up equivalent resistor <sup>(5)</sup>   | $V_{IN} = V_{SS}$                                                                                             | 30                  | 45                                 | 60                                 | kΩ   |

| R <sub>PD</sub>  | Weak pull-down equivalent resistor <sup>(5)</sup> | $V_{IN} = V_{DD}$                                                                                             | 30                  | 45                                 | 60                                 | kΩ   |

| C <sub>IO</sub>  | I/O pin capacitance                               | -                                                                                                             | -                   | 5                                  | -                                  | pF   |

| Table 59. I/O static characteristics | Table 59. I/O sta | atic characteristics |

|--------------------------------------|-------------------|----------------------|

|--------------------------------------|-------------------|----------------------|

1. Guaranteed by characterization.

2. Hysteresis voltage between Schmitt trigger switching levels. Guaranteed by characterization results.

3. With a minimum of 200 mV. Guaranteed by characterization results.

4. The max. value may be exceeded if negative current is injected on adjacent pins.

Pull-up and pull-down resistors are designed with a true resistance in series with a switchable PMOS/NMOS. This MOS/NMOS contribution to the series resistance is minimum (~10% order).

| Symbol                    | Parameter                                            | Conditions                                                                                            | Min | Тур          | Мах          | Unit  |

|---------------------------|------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-----|--------------|--------------|-------|

| DNL <sup>(2)</sup>        | Differential non linearity <sup>(4)</sup>            | $C_{L} \le 50 \text{ pF}, R_{L} \ge 5 \text{ k}\Omega$<br>DAC output buffer ON                        | -   | 1.5          | 3            |       |

|                           |                                                      | No $R_{LOAD}$ , $C_{L} \le 50 \text{ pF}$<br>DAC output buffer OFF                                    | -   | 1.5          | 3            |       |

| INL <sup>(2)</sup>        | Integral non linearity <sup>(5)</sup>                | $C_L \le 50 \text{ pF}, R_L \ge 5 \text{ k}\Omega$<br>DAC output buffer ON                            | -   | 2            | 4            |       |

|                           | integral non intearity 2                             | No $R_{LOAD}$ , $C_{L} \le 50 \text{ pF}$<br>DAC output buffer OFF                                    | -   | 2            | 4            | LSB   |

| Offset <sup>(2)</sup>     | Offset error at code 0x800 <sup>(6)</sup>            | $C_L \le 50 \text{ pF}, R_L \ge 5 \text{ k}\Omega$<br>DAC output buffer ON                            | -   | ±10          | ±25          |       |

| Oliset                    |                                                      | No $R_{LOAD}$ , $C_{L} \le 50 \text{ pF}$<br>DAC output buffer OFF                                    | -   | ±5           | ±8           |       |

| Offset1 <sup>(2)</sup>    | Offset error at code 0x001 <sup>(7)</sup>            | No $R_{LOAD}$ , $C_{L} \le 50 \text{ pF}$<br>DAC output buffer OFF                                    | -   | ±1.5         | ±5           |       |

| dOffset/dT <sup>(2)</sup> | Offset error temperature<br>coefficient (code 0x800) | $V_{DDA} = 3.3V$<br>$V_{REF+} = 3.0 V$<br>$T_A = 0 \text{ to } 50 ^{\circ}C$<br>DAC output buffer OFF | -20 | -10          | 0            |       |

|                           |                                                      | $V_{DDA} = 3.3V$<br>$V_{REF+} = 3.0 V$<br>$T_A = 0 \text{ to } 50 ^{\circ} C$<br>DAC output buffer ON | 0   | 20           | 50           | μV/°C |

| Gain <sup>(2)</sup>       | Cain arrar <sup>(8)</sup>                            | $C_L \le 50 \text{ pF}, R_L \ge 5 \text{ k}\Omega$<br>DAC output buffer ON                            | -   | +0.1 / -0.2% | +0.2 / -0.5% | %     |

| Gain                      | Gain error <sup>(8)</sup>                            | No $R_{LOAD}$ , $C_{L} \le 50 \text{ pF}$<br>DAC output buffer OFF                                    | -   | +0 / -0.2%   | +0 / -0.4%   | 70    |

| dCain/dT <sup>(2)</sup>   | Gain error temperature coefficient                   | $V_{DDA} = 3.3V$<br>$V_{REF+} = 3.0 V$<br>$T_A = 0 \text{ to } 50 \degree C$<br>DAC output buffer OFF | -10 | -2           | 0            |       |

| dGain/dT <sup>(2)</sup>   |                                                      | $V_{DDA} = 3.3V$<br>$V_{REF+} = 3.0 V$<br>$T_A = 0 \text{ to } 50 \degree C$<br>DAC output buffer ON  | -40 | -8           | 0            | μV/°C |

| TUE <sup>(2)</sup>        | Tatal un adiusta d'arras                             | $C_L \le 50 \text{ pF}, R_L \ge 5 \text{ k}\Omega$<br>DAC output buffer ON                            | -   | 12           | 30           |       |

|                           | Total unadjusted error                               | No $R_{LOAD}$ , $C_{L} \le 50 \text{ pF}$<br>DAC output buffer OFF                                    | -   | 8            | 12           | LSB   |

## Table 66. DAC characteristics (continued)

### 6.3.17 Temperature sensor characteristics

| Calibration value name | Description                                                               | Memory address            |  |  |  |  |

|------------------------|---------------------------------------------------------------------------|---------------------------|--|--|--|--|

| TS_CAL1                | TS ADC raw data acquired at temperature of 30 °C, V <sub>DDA</sub> = 3 V  | 0x1FF8 007A - 0x1FF8 007B |  |  |  |  |

| TS_CAL2                | TS ADC raw data acquired at temperature of 130 °C, V <sub>DDA</sub> = 3 V | 0x1FF8 007E - 0x1FF8 007F |  |  |  |  |

Table 67. Temperature sensor calibration values

Table 68. Temperature sensor characteristics

| Symbol                                | Parameter                                      | Min  | Тур  | Max  | Unit  |

|---------------------------------------|------------------------------------------------|------|------|------|-------|

| T <sub>L</sub> <sup>(1)</sup>         | V <sub>SENSE</sub> linearity with temperature  | -    | ±1   | ±2   | °C    |

| Avg_Slope <sup>(1)</sup>              | Average slope                                  | 1.48 | 1.61 | 1.75 | mV/°C |

| V <sub>130</sub>                      | Voltage at 130°C ±5°C <sup>(2)</sup>           | 640  | 670  | 700  | mV    |

| I <sub>DDA(TEMP)</sub> <sup>(3)</sup> | Current consumption                            | -    | 3.4  | 6    | μA    |

| t <sub>START</sub> <sup>(3)</sup>     | Startup time                                   | -    | -    | 10   |       |

| T <sub>S_temp</sub> <sup>(4)(3)</sup> | ADC sampling time when reading the temperature | 10   | -    | -    | μs    |

1. Guaranteed by characterization results.

2. Measured at V\_{DD} = 3 V  $\pm$ 10 mV. V130 ADC conversion result is stored in the TS\_CAL2 byte.

3. Guaranteed by design.

4. Shortest sampling time can be determined in the application by multiple iterations.

### 6.3.18 Comparators

| Symbol Parameter Conditions Min <sup>(1)</sup> Typ Max |                                                                |                                                                                                                                                           |      |     |                  | Unit      |

|--------------------------------------------------------|----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|------------------|-----------|

| Gymbol                                                 | i arameter                                                     | Conditions                                                                                                                                                |      | чур | Max              | Onit      |

| $V_{DDA}$                                              | Analog supply voltage                                          | -                                                                                                                                                         | 1.65 |     | 3.6              | V         |

| R <sub>400K</sub>                                      | R <sub>400K</sub> value                                        | -                                                                                                                                                         | -    | 400 | -                | kΩ        |

| R <sub>10K</sub>                                       | R <sub>10K</sub> value                                         | -                                                                                                                                                         | -    | 10  | -                | 122       |

| V <sub>IN</sub>                                        | Comparator 1 input voltage range                               | -                                                                                                                                                         | 0.6  | -   | V <sub>DDA</sub> | V         |

| t <sub>START</sub>                                     | Comparator startup time                                        | -                                                                                                                                                         | -    | 7   | 10               | 110       |

| td                                                     | Propagation delay <sup>(2)</sup>                               | -                                                                                                                                                         | -    | 3   | 10               | μs        |

| Voffset                                                | Comparator offset                                              | -                                                                                                                                                         | -    | ±3  | ±10              | mV        |

| d <sub>Voffset</sub> /dt                               | Comparator offset variation in worst voltage stress conditions | $\label{eq:VDDA} \begin{split} V_{DDA} &= 3.6 \text{ V},  V_{IN+} = 0 \text{ V}, \\ V_{IN-} &= V_{REFINT},  T_A \text{ = } 25 ^\circ\text{C} \end{split}$ | 0    | 1.5 | 10               | mV/1000 h |

| I <sub>COMP1</sub>                                     | Current consumption <sup>(3)</sup>                             | -                                                                                                                                                         | -    | 160 | 260              | nA        |

#### Table 69. Comparator 1 characteristics

1. Guaranteed by characterization.

2. The delay is characterized for 100 mV input step with 10 mV overdrive on the inverting input, the non-inverting input set to the reference.

3. Comparator consumption only. Internal reference voltage not included.

| Symbol              | Parameter                                     | Conditions                                                                                                                                                                                                                                             | Min  | Тур | Max <sup>(1)</sup> | Unit       |

|---------------------|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|--------------------|------------|

| V <sub>DDA</sub>    | Analog supply voltage                         | -                                                                                                                                                                                                                                                      | 1.65 | -   | 3.6                | V          |

| V <sub>IN</sub>     | Comparator 2 input voltage range              | -                                                                                                                                                                                                                                                      | 0    | -   | V <sub>DDA</sub>   | V          |

| +                   | Comparator startup time                       | Fast mode                                                                                                                                                                                                                                              | -    | 15  | 20                 |            |

| t <sub>START</sub>  |                                               | Slow mode                                                                                                                                                                                                                                              | -    | 20  | 25                 |            |

| +                   | Propagation delay <sup>(2)</sup> in slow mode | 1.65 V ≤V <sub>DDA</sub> ≤2.7 V                                                                                                                                                                                                                        | -    | 1.8 | 3.5                |            |

| t <sub>d slow</sub> | Propagation delay/ In slow mode               | 2.7 V ≤V <sub>DDA</sub> ≤3.6 V                                                                                                                                                                                                                         | -    | 2.5 | 6                  | μs         |

| +                   | Propagation delay <sup>(2)</sup> in fast mode | 1.65 V ≤V <sub>DDA</sub> ≤2.7 V                                                                                                                                                                                                                        | -    | 0.8 | 2                  |            |

| t <sub>d fast</sub> | riopagation delay fin last mode               | 2.7 V ≤V <sub>DDA</sub> ≤3.6 V                                                                                                                                                                                                                         | -    | 1.2 | 4                  |            |

| V <sub>offset</sub> | Comparator offset error                       |                                                                                                                                                                                                                                                        | -    | ±4  | <u>+</u> 20        | mV         |

| dThreshold/<br>dt   | Threshold voltage temperature coefficient     | $\label{eq:VDDA} \begin{split} &V_{DDA} = 3.3 \text{V},  \text{T}_{\text{A}} = 0 \text{ to } 50 \ ^{\circ}\text{C}, \\ &V- = V_{\text{REFINT}}, \\ &3/4 \ &V_{\text{REFINT}}, \\ &1/2 \ &V_{\text{REFINT}}, \\ &1/4 \ &V_{\text{REFINT}}. \end{split}$ | -    | 15  | 30                 | ppm<br>/°C |

|                     | Current consumption <sup>(3)</sup>            | Fast mode                                                                                                                                                                                                                                              | -    | 3.5 | 5                  |            |

| I <sub>COMP2</sub>  |                                               | Slow mode                                                                                                                                                                                                                                              | -    | 0.5 | 2                  | μA         |

Table 70. Comparator 2 characteristics

1. Guaranteed by characterization results.

2. The delay is characterized for 100 mV input step with 10 mV overdrive on the inverting input, the non-inverting input set to the reference.

3. Comparator consumption only. Internal reference voltage (required for comparator operation) is not included.

The analog spike filter is compliant with  $I^2C$  timings requirements only for the following voltage ranges:

- Fast mode Plus: 2.7 V  $\leq$ V<sub>DD</sub>  $\leq$ 3.6 V and voltage scaling Range 1

- Fast mode:

- 2 V  $\leq$ V<sub>DD</sub>  $\leq$ 3.6 V and voltage scaling Range 1 or Range 2.

- V<sub>DD</sub> < 2 V, voltage scaling Range 1 or Range 2, C<sub>load</sub> < 200 pF.

In other ranges, the analog filter should be disabled. The digital filter can be used instead.

Note: In Standard mode, no spike filter is required.

| Table 72. I | 2C analog | filter chara | cteristics <sup>(1)</sup> |

|-------------|-----------|--------------|---------------------------|

|-------------|-----------|--------------|---------------------------|

| Symbol          | Parameter                                                              | Conditions | Min               | Мах                | Unit |

|-----------------|------------------------------------------------------------------------|------------|-------------------|--------------------|------|

|                 |                                                                        | Range 1    |                   | 260 <sup>(3)</sup> |      |

| t <sub>AF</sub> | Maximum pulse width of spikes that are suppressed by the analog filter | Range 2    | 50 <sup>(2)</sup> | -                  | ns   |

|                 | are suppressed by the analog inter                                     | Range 3    |                   | -                  |      |

- 1. Guaranteed by characterization results.

- 2. Spikes with widths below  $t_{\mbox{\scriptsize AF}(\mbox{min})}$  are filtered.

- 3. Spikes with widths above  $t_{AF(max)}$  are not filtered

#### **USART/LPUART** characteristics

The parameters given in the following table are guaranteed by design.

| Symbol               | Parameter                                                                                                                                                      | Conditions                                                    | Тур  | Max  | Unit |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|------|------|------|

| <sup>t</sup> wuusart | Wakeup time needed to<br>calculate the maximum<br>USART/LPUART baudrate<br>allowing to wake up from<br>Stop mode when the<br>USART/LPUART is clocked<br>by HSI | Stop mode with main regulator in<br>Run mode, Range 2 or 3    | -    | 8.7  |      |

|                      |                                                                                                                                                                | Stop mode with main regulator in<br>Run mode, Range 1         | - 81 |      | μs   |

|                      |                                                                                                                                                                | Stop mode with main regulator in low-power mode, Range 2 or 3 | -    | 12   |      |

|                      |                                                                                                                                                                | Stop mode with main regulator in low-power mode, Range 1      | -    | 11.4 |      |

#### Table 73. USART/LPUART characteristics

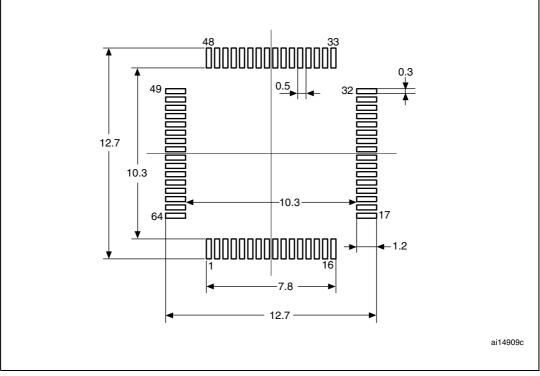

### Figure 40. LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat recommended footprint

1. Dimensions are expressed in millimeters.

# Table 82. TFBGA64 – 64-ball, 5 x 5 mm, 0.5 mm pitch, thin profile fine pitch ballgrid array package mechanical data (continued)

| Symbol | millimeters |     |       | inches <sup>(1)</sup> |     |        |

|--------|-------------|-----|-------|-----------------------|-----|--------|

|        | Min         | Тур | Мах   | Min                   | Тур | Мах    |

| ddd    | -           | -   | 0.080 | -                     | -   | 0.0031 |

| eee    | -           | -   | 0.150 | -                     | -   | 0.0059 |

| fff    | -           | -   | 0.050 | -                     | -   | 0.0020 |

1. Values in inches are converted from mm and rounded to 4 decimal digits.

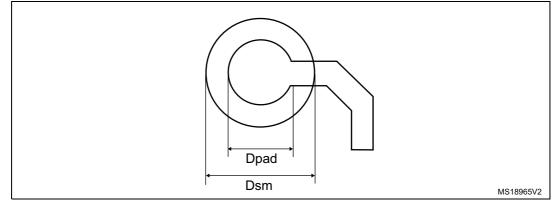

# Figure 43. TFBGA64 – 64-ball, 5 x 5 mm, 0.5 mm pitch, thin profile fine pitch ball ,grid array recommended footprint

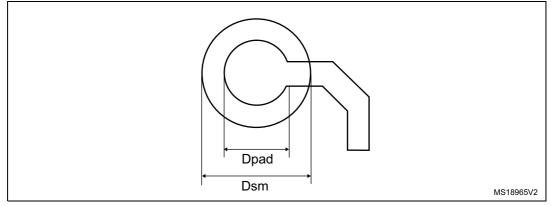

#### Table 83. TFBGA64 recommended PCB design rules (0.5 mm pitch BGA)

| Dimension    | Recommended values                                              |  |  |

|--------------|-----------------------------------------------------------------|--|--|

| Pitch        | 0.5                                                             |  |  |

| Dpad         | 0.27 mm                                                         |  |  |

| Dsm          | 0.35 mm typ. (depends on the soldermask registration tolerance) |  |  |

| Solder paste | 0.27 mm aperture diameter.                                      |  |  |

Note:Non solder mask defined (NSMD) pads are recommended.4 to 6 mils solder paste screen printing process.

| Symbol | millimeters |       |       | inches <sup>(1)</sup> |        |        |  |

|--------|-------------|-------|-------|-----------------------|--------|--------|--|

|        | Min         | Тур   | Мах   | Min                   | Тур    | Мах    |  |

| А      | -           | -     | 1.600 | -                     | -      | 0.0630 |  |

| A1     | 0.050       | -     | 0.150 | 0.0020                | -      | 0.0059 |  |

| A2     | 1.350       | 1.400 | 1.450 | 0.0531                | 0.0551 | 0.0571 |  |

| b      | 0.170       | 0.220 | 0.270 | 0.0067                | 0.0087 | 0.0106 |  |

| С      | 0.090       | -     | 0.200 | 0.0035                | -      | 0.0079 |  |

| D      | 8.800       | 9.000 | 9.200 | 0.3465                | 0.3543 | 0.3622 |  |

| D1     | 6.800       | 7.000 | 7.200 | 0.2677                | 0.2756 | 0.2835 |  |

| D3     | -           | 5.500 | -     | -                     | 0.2165 | -      |  |

| Е      | 8.800       | 9.000 | 9.200 | 0.3465                | 0.3543 | 0.3622 |  |

| E1     | 6.800       | 7.000 | 7.200 | 0.2677                | 0.2756 | 0.2835 |  |

| E3     | -           | 5.500 | -     | -                     | 0.2165 | -      |  |

| е      | -           | 0.500 | -     | -                     | 0.0197 | -      |  |

| L      | 0.450       | 0.600 | 0.750 | 0.0177                | 0.0236 | 0.0295 |  |

| L1     | -           | 1.000 | -     | -                     | 0.0394 | -      |  |

| k      | 0°          | 3.5°  | 7°    | 0°                    | 3.5°   | 7°     |  |

| CCC    | -           | -     | 0.080 | -                     | -      | 0.0031 |  |

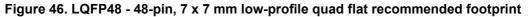

Table 84. LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package mechanical data

1. Values in inches are converted from mm and rounded to 4 decimal digits.

1. Dimensions are expressed in millimeters.

DocID025936 Rev 7

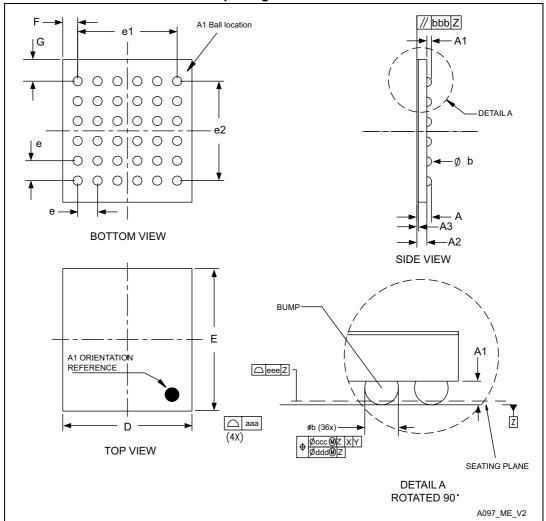

## 7.5 Thin WLCSP36 package information

# Figure 51. Thin WLCSP36 - 2.61 x 2.88 mm, 0.4 mm pitch wafer level chip scale package outline

1. Drawing is not to scale.

2. b dimensions is measured at the maximum bump diameter parallel to primary datum Z.

3. Primary datum Z and seating plane are defined by the spherical crowns of the bump.

4. Bump position designation per JESD 95-1, SPP-010.

| Symbol | millimeters |                      |      | inches <sup>(1)</sup> |       |       |

|--------|-------------|----------------------|------|-----------------------|-------|-------|

|        | Min         | Тур                  | Max  | Min                   | Тур   | Max   |

| А      | -           | -                    | 0.33 | -                     | -     | 0.013 |

| A1     | -           | 0.10                 | -    | -                     | 0.004 | -     |

| A2     | -           | 0.20                 | -    | -                     | 0.008 | -     |

| A3     | -           | 0.025 <sup>(2)</sup> | -    | -                     | 0.001 | -     |

| b      | 0.16        | 0.19                 | 0.22 | 0.006                 | 0.007 | 0.009 |

| D      | 2.59        | 2.61                 | 2.63 | 0.102                 | 0.103 | 0.104 |

| E      | 2.86        | 2.88                 | 2.90 | 0.112                 | 0.113 | 0.114 |

| е      | -           | 0.40                 | -    | -                     | 0.016 | -     |

| e1     | -           | 2.00                 | -    | -                     | 0.079 | -     |

| e2     | -           | 2.00                 | -    | -                     | 0.079 | -     |

| F      | -           | 0.305 <sup>(3)</sup> | -    | -                     | 0.012 | -     |

| G      | -           | 0.440 <sup>(3)</sup> | -    | -                     | 0.017 | -     |

| aaa    | -           | -                    | 0.10 | -                     | -     | 0.004 |

| bbb    | -           | -                    | 0.10 | -                     | -     | 0.004 |

| CCC    | -           | -                    | 0.10 | -                     | -     | 0.004 |

| ddd    | -           | -                    | 0.05 | -                     | -     | 0.002 |

| eee    | -           | -                    | 0.05 | -                     | -     | 0.002 |

# Table 87. Thin WLCSP36 - 2.61 x 2.88 mm, 0.4 mm pitch wafer level chip scale package mechanical data

1. Values in inches are converted from mm and rounded to the 3rd decimal place.

2. Back side coating. Nominal dimension rounded to the 3rd decimal place results from process capability.

3. Calculated dimensions are rounded to 3rd decimal place.

# Figure 52. Thin WLCSP36 - 2.61 x 2.88 mm, 0.4 mm pitch wafer level chip scale package recommended footprint

| package mechanical data |             |       |       |                       |        |        |  |

|-------------------------|-------------|-------|-------|-----------------------|--------|--------|--|

| Symbol                  | millimeters |       |       | inches <sup>(1)</sup> |        |        |  |

|                         | Min         | Тур   | Max   | Min                   | Тур    | Мах    |  |

| А                       | 0.500       | 0.550 | 0.600 | 0.0197                | 0.0217 | 0.0236 |  |

| A1                      | 0.000       | 0.020 | 0.050 | 0.0000                | 0.0008 | 0.0020 |  |

| A3                      | -           | 0.152 | -     | -                     | 0.0060 | -      |  |

| b                       | 0.180       | 0.230 | 0.280 | 0.0071                | 0.0091 | 0.0110 |  |

| D                       | 4.900       | 5.000 | 5.100 | 0.1929                | 0.1969 | 0.2008 |  |

| D1                      | 3.400       | 3.500 | 3.600 | 0.1339                | 0.1378 | 0.1417 |  |

| D2                      | 3.400       | 3.500 | 3.600 | 0.1339                | 0.1378 | 0.1417 |  |

| E                       | 4.900       | 5.000 | 5.100 | 0.1929                | 0.1969 | 0.2008 |  |

| E1                      | 3.400       | 3.500 | 3.600 | 0.1339                | 0.1378 | 0.1417 |  |

| E2                      | 3.400       | 3.500 | 3.600 | 0.1339                | 0.1378 | 0.1417 |  |

| е                       | -           | 0.500 | -     | -                     | 0.0197 | -      |  |

| L                       | 0.300       | 0.400 | 0.500 | 0.0118                | 0.0157 | 0.0197 |  |

| ddd                     | -           | -     | 0.080 | -                     | -      | 0.0031 |  |

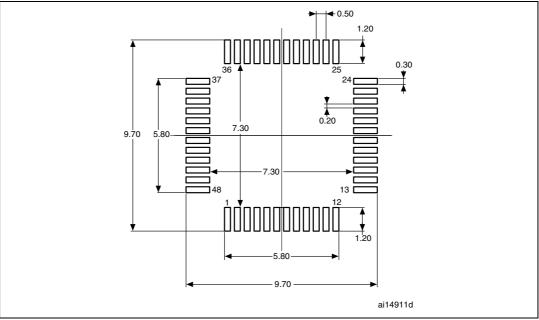

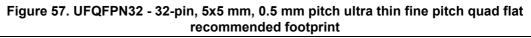

# Table 90. UFQFPN32 - 32-pin, 5x5 mm, 0.5 mm pitch ultra thin fine pitch quad flatpackage mechanical data

1. Values in inches are converted from mm and rounded to 4 decimal digits.

1. Dimensions are expressed in millimeters.