Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                      |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 32MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART, USB                          |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                            |

| Number of I/O              | 27                                                                    |

| Program Memory Size        | 64KB (64K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | 2K x 8                                                                |

| RAM Size                   | 8K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 3.6V                                                          |

| Data Converters            | A/D 10x12b; D/A 1x12b                                                 |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 32-UFQFN Exposed Pad                                                  |

| Supplier Device Package    | 32-UFQFPN (5x5)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l052k8u6 |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|   |       | 3.17.5       | Independent watchdog (IWDG) 34                                    |

|---|-------|--------------|-------------------------------------------------------------------|

|   |       | 3.17.6       | Window watchdog (WWDG) 34                                         |

|   | 3.18  | Comm         | unication interfaces                                              |

|   |       | 3.18.1       | I2C bus                                                           |

|   |       | 3.18.2       | Universal synchronous/asynchronous receiver transmitter (USART)35 |

|   |       | 3.18.3       | Low-power universal asynchronous receiver transmitter (LPUART) 36 |

|   |       | 3.18.4       | Serial peripheral interface (SPI)/Inter-integrated sound (I2S)    |

|   |       | 3.18.5       | Universal serial bus (USB)                                        |

|   | 3.19  | Clock r      | ecovery system (CRS)                                              |

|   | 3.20  | Cyclic       | redundancy check (CRC) calculation unit                           |

|   | 3.21  | Serial       | wire debug port (SW-DP) 37                                        |

| 4 | Pin d | lescript     | ions                                                              |

| 5 | Mom   | 0 M ( 100 0) |                                                                   |

| Ð | wiem  | ory ma       | pping                                                             |

| 6 | Elect | trical ch    | aracteristics                                                     |

|   | 6.1   | Param        | eter conditions                                                   |

|   |       | 6.1.1        | Minimum and maximum values53                                      |

|   |       | 6.1.2        | Typical values                                                    |

|   |       | 6.1.3        | Typical curves                                                    |

|   |       | 6.1.4        | Loading capacitor                                                 |

|   |       | 6.1.5        | Pin input voltage                                                 |

|   |       | 6.1.6        | Power supply scheme                                               |

|   |       | 6.1.7        | Current consumption measurement                                   |

|   | 6.2   | Absolu       | te maximum ratings 55                                             |

|   | 6.3   | Operat       | ing conditions                                                    |

|   |       | 6.3.1        | General operating conditions                                      |

|   |       | 6.3.2        | Embedded reset and power control block characteristics            |

|   |       | 6.3.3        | Embedded internal reference voltage60                             |

|   |       | 6.3.4        | Supply current characteristics61                                  |

|   |       | 6.3.5        | Wakeup time from low-power mode72                                 |

|   |       | 6.3.6        | External clock source characteristics                             |

|   |       | 6.3.7        | Internal clock source characteristics                             |

|   |       | 6.3.8        | PLL characteristics                                               |

|   |       | 6.3.9        | Memory characteristics                                            |

|   |       | 6.3.10       | EMC characteristics                                               |

|   |       |              |                                                                   |

# 2.1 Device overview

| Table 2 Illtra-low- | power STM32L052x6/x   | 8 dovico fosturos and | norinhoral counts  |

|---------------------|-----------------------|-----------------------|--------------------|

|                     | DOMEL OLIMISTEDSTVOLV | o device realures and | periprierar counts |

| Peripheral                                       |                             | STM32L0<br>52T6        | STM32<br>L052K6        | STM32<br>L052C6        | STM32<br>L052R6            | STM32L<br>052T8 | STM32<br>L052K8       | STM32<br>L052C8 | STM32<br>L052R8        |

|--------------------------------------------------|-----------------------------|------------------------|------------------------|------------------------|----------------------------|-----------------|-----------------------|-----------------|------------------------|

| Flash (Kbyte                                     | es)                         |                        | 32                     | 2                      |                            |                 | 6                     | 4               |                        |

| Data EEPRC                                       | M (Kbytes)                  |                        | 2                      |                        |                            |                 |                       | 2               |                        |

| RAM (Kbyte                                       | s)                          |                        | 8                      |                        |                            |                 | 8                     | 3               |                        |

|                                                  | General-<br>purpose         |                        | 3                      |                        |                            |                 | 3                     | 3               |                        |

| Timers                                           | Basic                       |                        | 1                      |                        |                            |                 |                       | 1               |                        |

|                                                  | LPTIMER                     |                        | 1                      |                        |                            |                 | ŕ                     | 1               |                        |

|                                                  | ICK/IWDG/<br>VDG            |                        | 1/1/                   | 1/1                    |                            |                 | 1/1/                  | /1/1            |                        |

|                                                  | SPI/I2S                     | 3(2) <sup>(1)</sup> /0 | 3(2) <sup>(1)</sup> /0 | 4(2) <sup>(1)</sup> /1 | 3(2) <sup>(1)</sup> /0     | 3(2)            | <sup>(1)</sup> /0     | 4(2)            | <sup>(1)</sup> /1      |

|                                                  | l <sup>2</sup> C            | 2                      | 1                      |                        | 2                          | 2               | 1                     | :               | 2                      |

| Communic ation                                   | USART                       |                        | 2                      |                        |                            |                 | 2                     |                 |                        |

| interfaces                                       | LPUART                      | 1                      | 0                      | 1                      |                            | 1 0             |                       | 1               |                        |

|                                                  | USB/<br>(VDD_USB)           | 1/                     | (0)                    | 1/(1)                  |                            | 1/(0)           |                       | 1/(1)           |                        |

| GPIOs                                            |                             | 29                     | 27 <sup>(2)</sup>      | 37                     | 51 <sup>(3)</sup>          | 29              | 27 <sup>(2)</sup>     | 37              | 51 <sup>(3)</sup>      |

| Clocks:<br>HSE/LSE/HS                            | SI/MSI/LSI                  | 0/1/1/1/1              | 0/1/1/1/1              | 1/1/1/1/1              | 1/1/1/1/1                  | 0/1/1/1/1       | 0/1/1/1/1             | 1/1/1/1/1       | 1/1/1/1/1              |

| 12-bit synchronized<br>ADC<br>Number of channels |                             | 1<br>10                | 1<br>10                | 1<br>10                | 1<br>16 <sup>(3)</sup>     | 1<br>10         | 1<br>10               | 1<br>10         | 1<br>16 <sup>(3)</sup> |

| 12-bit DAC<br>Number of channels                 |                             |                        | 1                      |                        |                            | 1               |                       |                 |                        |

| Comparators                                      |                             |                        |                        |                        | 2                          | 2               |                       |                 |                        |

| Capacitive s channels                            | Capacitive sensing channels |                        | 4                      | 17                     | 24 <sup>(3)</sup>          | 14              |                       | 17              | 24 <sup>(3)</sup>      |

| Max. CPU fr                                      | equency                     | 32 MHz                 |                        |                        |                            |                 |                       |                 |                        |

| Operating v                                      | oltage                      |                        | 1.8 V to 3.            |                        | to 1.65 V a<br>to 3.6 V wi |                 | wn) with BC<br>option | OR option       |                        |

### • Stop mode without RTC

The Stop mode achieves the lowest power consumption while retaining the RAM and register contents. All clocks are stopped, the PLL, MSI RC, HSI and LSI RC, HSE and LSE crystal oscillators are disabled.

Some peripherals featuring wakeup capability can enable the HSI RC during Stop mode to detect their wakeup condition.

The voltage regulator is in the low-power mode. The device can be woken up from Stop mode by any of the EXTI line, in 3.5  $\mu$ s, the processor can serve the interrupt or resume the code. The EXTI line source can be any GPIO. It can be the PVD output, the comparator 1 event or comparator 2 event (if internal reference voltage is on). It can also be wakened by the USB/USART/I2C/LPUART/LPTIMER wakeup events.

### • Standby mode with RTC

The Standby mode is used to achieve the lowest power consumption and real time clock. The internal voltage regulator is switched off so that the entire  $V_{CORE}$  domain is powered off. The PLL, MSI RC, HSE crystal and HSI RC oscillators are also switched off. The LSE or LSI is still running. After entering Standby mode, the RAM and register contents are lost except for registers in the Standby circuitry (wakeup logic, IWDG, RTC, LSI, LSE Crystal 32 KHz oscillator, RCC\_CSR register).

The device exits Standby mode in 60 µs when an external reset (NRST pin), an IWDG reset, a rising edge on one of the three WKUP pins, RTC alarm (Alarm A or Alarm B), RTC tamper event, RTC timestamp event or RTC Wakeup event occurs.

### Standby mode without RTC

The Standby mode is used to achieve the lowest power consumption. The internal voltage regulator is switched off so that the entire  $V_{CORE}$  domain is powered off. The PLL, MSI RC, HSI and LSI RC, HSE and LSE crystal oscillators are also switched off. After entering Standby mode, the RAM and register contents are lost except for registers in the Standby circuitry (wakeup logic, IWDG, RTC, LSI, LSE Crystal 32 KHz oscillator, RCC\_CSR register).

The device exits Standby mode in 60  $\mu$ s when an external reset (NRST pin) or a rising edge on one of the three WKUP pin occurs.

*Note:* The RTC, the IWDG, and the corresponding clock sources are not stopped automatically by entering Stop or Standby mode.

|                                                | Functionalities depending on the operating power supply range   |                                |                            |                           |  |  |  |  |

|------------------------------------------------|-----------------------------------------------------------------|--------------------------------|----------------------------|---------------------------|--|--|--|--|

| Operating power<br>supply range                | DAC and ADC<br>operation<br>Dynamic<br>voltage scaling<br>range |                                | I/O operation              | USB                       |  |  |  |  |

| V <sub>DD</sub> = 1.65 to 1.71 V               | ADC only,<br>conversion time<br>up to 570 ksps                  | Range 2 or<br>range 3          | Degraded speed performance | Not functional            |  |  |  |  |

| V <sub>DD</sub> = 1.71 to 1.8 V <sup>(1)</sup> | ADC only,<br>conversion time<br>up to 1.14 Msps                 | Range 1, range 2<br>or range 3 | Degraded speed performance | Functional <sup>(2)</sup> |  |  |  |  |

| $V_{DD}$ = 1.8 to 2.0 V <sup>(1)</sup>         | Conversion time<br>up to 1.14 Msps                              | Range1, range 2<br>or range 3  | Degraded speed performance | Functional <sup>(2)</sup> |  |  |  |  |

| V <sub>DD</sub> = 2.0 to 2.4 V                 | Conversion time<br>up to<br>1.14 Msps                           | Range 1, range 2<br>or range 3 | Full speed operation       | Functional <sup>(2)</sup> |  |  |  |  |

| V <sub>DD</sub> = 2.4 to 3.6 V                 | Conversion time<br>up to<br>1.14 Msps                           | Range 1, range 2<br>or range 3 | Full speed operation       | Functional <sup>(2)</sup> |  |  |  |  |

| Table 0 Friedlandlities  |              |                 |                    |

|--------------------------|--------------|-----------------|--------------------|

| Table 3. Functionalities | aepenaing or | 1 the operating | power supply range |

CPU frequency changes from initial to final must respect "fcpu initial <4\*fcpu final". It must also respect 5

µs delay between two changes. For example to switch from 4.2 MHz to 32 MHz, you can switch from 4.2

MHz to 16 MHz, wait 5 µs, then switch from 16 MHz to 32 MHz.</li>

2. To be USB compliant from the I/O voltage standpoint, the minimum  $V_{\text{DD\_USB}}$  is 3.0 V.

### Table 4. CPU frequency range depending on dynamic voltage scaling

| CPU frequency range                              | Dynamic voltage scaling range |

|--------------------------------------------------|-------------------------------|

| 16 MHz to 32 MHz (1ws)<br>32 kHz to 16 MHz (0ws) | Range 1                       |

| 8 MHz to 16 MHz (1ws)<br>32 kHz to 8 MHz (0ws)   | Range 2                       |

| 32 kHz to 4.2 MHz (0ws)                          | Range 3                       |

# 3.6 Low-power real-time clock and backup registers

The real time clock (RTC) and the 5 backup registers are supplied in all modes including standby mode. The backup registers are five 32-bit registers used to store 20 bytes of user application data. They are not reset by a system reset, or when the device wakes up from Standby mode.

The RTC is an independent BCD timer/counter. Its main features are the following:

- Calendar with subsecond, seconds, minutes, hours (12 or 24 format), week day, date, month, year, in BCD (binary-coded decimal) format

- Automatically correction for 28, 29 (leap year), 30, and 31 day of the month

- Two programmable alarms with wake up from Stop and Standby mode capability

- Periodic wakeup from Stop and Standby with programmable resolution and period

- On-the-fly correction from 1 to 32767 RTC clock pulses. This can be used to synchronize it with a master clock.

- Reference clock detection: a more precise second source clock (50 or 60 Hz) can be used to enhance the calendar precision.

- Digital calibration circuit with 1 ppm resolution, to compensate for quartz crystal inaccuracy

- 2 anti-tamper detection pins with programmable filter. The MCU can be woken up from Stop and Standby modes on tamper event detection.

- Timestamp feature which can be used to save the calendar content. This function can be triggered by an event on the timestamp pin, or by a tamper event. The MCU can be woken up from Stop and Standby modes on timestamp event detection.

The RTC clock sources can be:

- A 32.768 kHz external crystal

- A resonator or oscillator

- The internal low-power RC oscillator (typical frequency of 37 kHz)

- The high-speed external clock

# 3.7 General-purpose inputs/outputs (GPIOs)

Each of the GPIO pins can be configured by software as output (push-pull or open-drain), as input (with or without pull-up or pull-down) or as peripheral alternate function. Most of the GPIO pins are shared with digital or analog alternate functions, and can be individually remapped using dedicated alternate function registers. All GPIOs are high current capable. Each GPIO output, speed can be slowed (40 MHz, 10 MHz, 2 MHz, 400 kHz). The alternate function configuration of I/Os can be locked if needed following a specific sequence in order to avoid spurious writing to the I/O registers. The I/O controller is connected to a dedicated IO bus with a toggling speed of up to 32 MHz.

# Extended interrupt/event controller (EXTI)

The extended interrupt/event controller consists of 28 edge detector lines used to generate interrupt/event requests. Each line can be individually configured to select the trigger event (rising edge, falling edge, both) and can be masked independently. A pending register maintains the status of the interrupt requests. The EXTI can detect an external line with a pulse width shorter than the Internal APB2 clock period. Up to 51 GPIOs can be connected to the 16 configurable interrupt/event lines. The 12 other lines are connected to PVD, RTC, USB, USARTS, LPUART, LPTIMER or comparator events.

# 3.17.1 General-purpose timers (TIM2, TIM21 and TIM22)

There are three synchronizable general-purpose timers embedded in the STM32L052x6/8 devices (see *Table 10* for differences).

### TIM2

TIM2 is based on 16-bit auto-reload up/down counter. It includes a 16-bit prescaler. It features four independent channels each for input capture/output compare, PWM or one-pulse mode output.

The TIM2 general-purpose timers can work together or with the TIM21 and TIM22 generalpurpose timers via the Timer Link feature for synchronization or event chaining. Their counter can be frozen in debug mode. Any of the general-purpose timers can be used to generate PWM outputs.

TIM2 has independent DMA request generation.

This timer is capable of handling quadrature (incremental) encoder signals and the digital outputs from 1 to 3 hall-effect sensors.

### TIM21 and TIM22

TIM21 and TIM22 are based on a 16-bit auto-reload up/down counter. They include a 16-bit prescaler. They have two independent channels for input capture/output compare, PWM or one-pulse mode output. They can work together and be synchronized with the TIM2, full-featured general-purpose timers.

They can also be used as simple time bases and be clocked by the LSE clock source (32.768 kHz) to provide time bases independent from the main CPU clock.

# 3.17.2 Low-power Timer (LPTIM)

The low-power timer has an independent clock and is running also in Stop mode if it is clocked by LSE, LSI or an external clock. It is able to wakeup the devices from Stop mode.

This low-power timer supports the following features:

- 16-bit up counter with 16-bit autoreload register

- 16-bit compare register

- Configurable output: pulse, PWM

- Continuous / one shot mode

- Selectable software / hardware input trigger

- Selectable clock source

- Internal clock source: LSE, LSI, HSI or APB clock

- External clock source over LPTIM input (working even with no internal clock source running, used by the Pulse Counter Application)

- Programmable digital glitch filter

- Encoder mode

## 3.17.3 Basic timer (TIM6)

This timer can be used as a generic 16-bit timebase. It is mainly used for DAC trigger generation.

| Pin Number |         |                        |        |        |         |                                       |          |               |       |                                                                                   |                                                        |

|------------|---------|------------------------|--------|--------|---------|---------------------------------------|----------|---------------|-------|-----------------------------------------------------------------------------------|--------------------------------------------------------|

| LQFP32     | UFQFN32 | WLCSP36 <sup>(1)</sup> | LQFP48 | LQFP64 | TFBGA64 | Pin name<br>(function after<br>reset) | Pin type | I/O structure | Notes | Alternate functions                                                               | Additional<br>functions                                |

| 9          | 9       | F5                     | 13     | 17     | G3      | PA3                                   | I/O      | FT            | -     | TIM21_CH2,<br>TIM2_CH4,<br>TSC_G1_IO4,<br>USART2_RX                               | COMP2_INP,<br>ADC_IN3                                  |

| -          | -       | -                      | -      | 18     | C2      | VSS                                   | S        | -             | -     | -                                                                                 | -                                                      |

| -          | -       | -                      | -      | 19     | D2      | VDD                                   | S        | -             | -     | -                                                                                 | -                                                      |

| 10         | 10      | E4                     | 14     | 20     | H3      | PA4                                   | I/O      | тс            | (2)   | SPI1_NSS,<br>TSC_G2_IO1,<br>USART2_CK,<br>TIM22_ETR                               | COMP1_INM4<br>,<br>COMP2_INM4<br>, ADC_IN4,<br>DAC_OUT |

| 11         | 11      | F4                     | 15     | 21     | F4      | PA5                                   | I/O      | тс            | -     | SPI1_SCK,<br>TIM2_ETR,<br>TSC_G2_IO2,<br>TIM2_CH1                                 | COMP1_INM5<br>,<br>COMP2_INM5<br>, ADC_IN5             |

| 12         | 12      | E3                     | 16     | 22     | G4      | PA6                                   | I/O      | FT            | -     | SPI1_MISO,<br>TSC_G2_IO3,<br>LPUART1_CTS,<br>TIM22_CH1,<br>EVENTOUT,<br>COMP1_OUT | ADC_IN6                                                |

| 13         | 13      | F3                     | 17     | 23     | H4      | PA7                                   | I/O      | FT            | -     | SPI1_MOSI,<br>TSC_G2_IO4,<br>TIM22_CH2,<br>EVENTOUT,<br>COMP2_OUT                 | ADC_IN7                                                |

| -          | -       | -                      | -      | 24     | H5      | PC4                                   | I/O      | FT            | -     | EVENTOUT,<br>LPUART1_TX                                                           | ADC_IN14                                               |

| -          | -       | -                      | -      | 25     | H6      | PC5                                   | I/O      | FT            | -     | LPUART1_RX,<br>TSC_G3_IO1                                                         | ADC_IN15                                               |

| 14         | 14      | D3                     | 18     | 26     | F5      | PB0                                   | I/O      | FT            | -     | EVENTOUT,<br>TSC_G3_IO2                                                           | ADC_IN8,<br>VREF_OUT                                   |

| 15         | 15      | C3                     | 19     | 27     | G5      | PB1                                   | I/O      | FT            | -     | TSC_G3_IO3,<br>LPUART1_RTS_DE                                                     | ADC_IN9,<br>VREF_OUT                                   |

| -          | 16      | F2                     | 20     | 28     | G6      | PB2                                   | I/O      | FT            | -     | LPTIM1_OUT,<br>TSC_G3_IO4                                                         | -                                                      |

Table 16. STM32L052x6/8 pin definitions (continued)

|        |         | Pin Nı                 | umber  |        |         |                                       |          |               |       |                                                                                                 |                         |

|--------|---------|------------------------|--------|--------|---------|---------------------------------------|----------|---------------|-------|-------------------------------------------------------------------------------------------------|-------------------------|

| LQFP32 | UFQFN32 | WLCSP36 <sup>(1)</sup> | LQFP48 | LQFP64 | TFBGA64 | Pin name<br>(function after<br>reset) | Pin type | I/O structure | Notes | Alternate functions                                                                             | Additional<br>functions |

| -      | -       | E2                     | 21     | 29     | G7      | PB10                                  | I/O      | FT            | -     | TIM2_CH3,<br>TSC_SYNC,<br>LPUART1_TX,<br>SPI2_SCK,<br>I2C2_SCL                                  | -                       |

| -      | -       | D2                     | 22     | 30     | H7      | PB11                                  | I/O      | FT            | -     | EVENTOUT,<br>TIM2_CH4,<br>TSC_G6_IO1,<br>LPUART1_RX,<br>I2C2_SDA                                | -                       |

| 16     | -       | -                      | 23     | 31     | D6      | VSS                                   | S        | -             | -     | -                                                                                               | -                       |

| 17     | 17      | F1                     | 24     | 32     | E5      | VDD                                   | S        | -             | -     | -                                                                                               | -                       |

| -      | -       | -                      | 25     | 33     | H8      | PB12                                  | I/O      | FT            | -     | SPI2_NSS/I2S2_WS,<br>LPUART1_RTS_DE,<br>TSC_G6_IO2,<br>I2C2_SMBA,<br>EVENTOUT                   | -                       |

| -      | -       | -                      | 26     | 34     | G8      | PB13                                  | I/O      | FTf           | -     | SPI2_SCK/I2S2_CK,<br>TSC_G6_IO3,<br>LPUART1_CTS,<br>I2C2_SCL,<br>TIM21_CH1                      | -                       |

| -      | -       | -                      | 27     | 35     | F8      | PB14                                  | I/O      | FTf           | -     | SPI2_MISO/I<br>2S2_MCK,<br>RTC_OUT,<br>TSC_G6_IO4,<br>LPUART1_RTS_DE,<br>I2C2_SDA,<br>TIM21_CH2 | -                       |

| -      | -       | -                      | 28     | 36     | F7      | PB15                                  | I/O      | FT            | -     | SPI2_MOSI/I2S2_SD,<br>RTC_REFIN                                                                 | -                       |

| -      | -       | -                      | -      | 37     | F6      | PC6                                   | I/O      | FT            | -     | TIM22_CH1,<br>TSC_G8_IO1                                                                        | -                       |

| -      | -       | -                      | -      | 38     | E7      | PC7                                   | I/O      | FT            | -     | TIM22_CH2,<br>TSC_G8_IO2                                                                        | -                       |

| -      | -       | -                      | -      | 39     | E8      | PC8                                   | I/O      | FT            | -     | TIM22_ETR,<br>TSC_G8_IO3                                                                        | -                       |

Table 16. STM32L052x6/8 pin definitions (continued)

| ה |        | Table 20. Alter | nate function port D |

|---|--------|-----------------|----------------------|

|   | Po     |                 | AF0                  |

|   | PC     | Jri -           | LPUART1              |

|   | Port D | PD2             | LPUART1_RTS_DE       |

| Table 21. A | Alternate | function | port H |

|-------------|-----------|----------|--------|

|-------------|-----------|----------|--------|

| В      | ort | AF0          |

|--------|-----|--------------|

| E.     |     | USB          |

| Port H | PH0 | USB_CRS_SYNC |

| roitti | PH1 | -            |

| Symbol            | Parameter                            | Conditions                                | Min  | Тур  | Max  | Unit |

|-------------------|--------------------------------------|-------------------------------------------|------|------|------|------|

| M                 | PVD threshold 6                      | Falling edge                              | 2.97 | 3.05 | 3.09 | V    |

| V <sub>PVD6</sub> |                                      | Rising edge                               | 3.08 | 3.15 | 3.20 | v    |

|                   | V <sub>hyst</sub> Hysteresis voltage | BOR0 threshold                            | -    | 40   | -    |      |

| V <sub>hyst</sub> |                                      | All BOR and PVD thresholds excepting BOR0 | -    | 100  | -    | mV   |

Table 26. Embedded reset and power control block characteristics (continued)

1. Guaranteed by characterization results.

2. Valid for device version without BOR at power up. Please see option "D" in Ordering information scheme for more details.

# 6.3.3 Embedded internal reference voltage

The parameters given in *Table 28* are based on characterization results, unless otherwise specified.

| Table 27. Embedde | d internal reference voltage calibration valu | ies |

|-------------------|-----------------------------------------------|-----|

|                   |                                               |     |

| Calibration value name | Description                                                            | Memory address            |

|------------------------|------------------------------------------------------------------------|---------------------------|

| VREFINT_CAL            | Raw data acquired at<br>temperature of 25 °C<br>V <sub>DDA</sub> = 3 V | 0x1FF8 0078 - 0x1FF8 0079 |

| Symbol                                   | Parameter                                                                                    | Conditions                                                                              | Min   | Тур   | Max   | Unit   |

|------------------------------------------|----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-------|-------|-------|--------|

| V <sub>REFINT out</sub> <sup>(2)</sup>   | Internal reference voltage                                                                   | – 40 °C < T <sub>J</sub> < +125 °C                                                      | 1.202 | 1.224 | 1.242 | V      |

| T <sub>VREFINT</sub>                     | Internal reference startup time                                                              | -                                                                                       | -     | 2     | 3     | ms     |

| V <sub>VREF_MEAS</sub>                   | V <sub>DDA</sub> and V <sub>REF+</sub> voltage during<br>V <sub>REFINT</sub> factory measure | -                                                                                       | 2.99  | 3     | 3.01  | V      |

| A <sub>VREF_MEAS</sub>                   | Accuracy of factory-measured $V_{REFINT}$ value <sup>(3)</sup>                               | Including uncertainties<br>due to ADC and<br>V <sub>DDA</sub> /V <sub>REF+</sub> values | -     | -     | ±5    | mV     |

| T <sub>Coeff</sub> <sup>(4)</sup>        | Temperature coefficient                                                                      | –40 °C < T <sub>J</sub> < +125 °C                                                       | -     | 25    | 100   | ppm/°C |

| A <sub>Coeff</sub> <sup>(4)</sup>        | Long-term stability                                                                          | 1000 hours, T= 25 °C                                                                    | -     | -     | 1000  | ppm    |

| V <sub>DDCoeff</sub> <sup>(4)</sup>      | Voltage coefficient                                                                          | 3.0 V < V <sub>DDA</sub> < 3.6 V                                                        | -     | -     | 2000  | ppm/V  |

| T <sub>S_vrefint</sub> <sup>(4)(5)</sup> | ADC sampling time when<br>reading the internal reference<br>voltage                          | -                                                                                       | 5     | 10    | -     | μs     |

| T <sub>ADC_BUF</sub> <sup>(4)</sup>      | Startup time of reference voltage buffer for ADC                                             | -                                                                                       | -     | -     | 10    | μs     |

| I <sub>BUF_ADC</sub> <sup>(4)</sup>      | Consumption of reference voltage buffer for ADC                                              | -                                                                                       | -     | 13.5  | 25    | μA     |

| I <sub>VREF_OUT</sub> <sup>(4)</sup>     | VREF_OUT output current <sup>(6)</sup>                                                       | -                                                                                       | -     | -     | 1     | μA     |

| C <sub>VREF_OUT</sub> <sup>(4)</sup>     | VREF_OUT output load                                                                         | -                                                                                       | -     | -     | 50    | pF     |

# Table 28. Embedded internal reference voltage<sup>(1)</sup>

| Symbol                 | Parameter                   | Conditions             | Тур  | Max <sup>(1)</sup> | Unit |  |  |  |

|------------------------|-----------------------------|------------------------|------|--------------------|------|--|--|--|

|                        |                             | $T_A = -40$ to 25°C    | 0.41 | 1                  |      |  |  |  |

|                        |                             | T <sub>A</sub> = 55°C  | 0.63 | 2.1                |      |  |  |  |

| I <sub>DD</sub> (Stop) | Supply current in Stop mode | T <sub>A</sub> = 85°C  | 1.7  | 4.5                | μA   |  |  |  |

|                        |                             | T <sub>A</sub> = 105°C | 4    | 9.6                |      |  |  |  |

|                        |                             | T <sub>A</sub> = 125°C | 11   | 24 <sup>(2)</sup>  |      |  |  |  |

Table 36. Typical and maximum current consumptions in Stop mode

1. Guaranteed by characterization results at 125  $^\circ\text{C},$  unless otherwise specified.

2. Guaranteed by test in production.

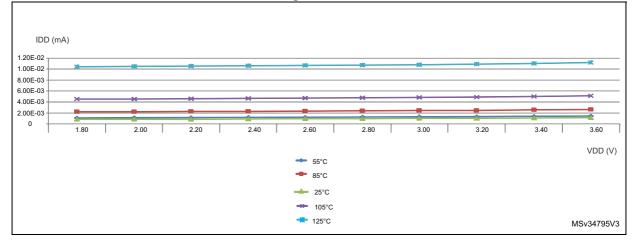

Figure 17. I<sub>DD</sub> vs V<sub>DD</sub>, at T<sub>A</sub>= 25/55/ 85/105/125 °C, Stop mode with RTC enabled and running on LSE Low drive

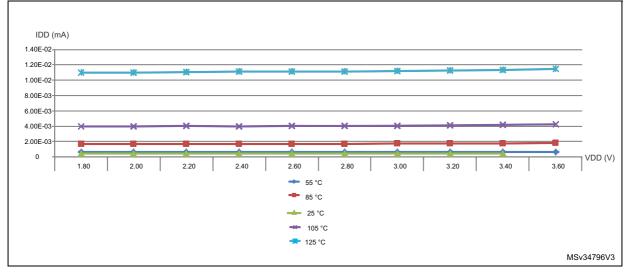

Figure 18.  $I_{DD}$  vs  $V_{DD}$ , at  $T_A$ = 25/55/85/105/125 °C, Stop mode with RTC disabled, all clocks OFF

## On-chip peripheral current consumption

The current consumption of the on-chip peripherals is given in the following tables. The MCU is placed under the following conditions:

- all I/O pins are in input mode with a static value at  $V_{DD}$  or  $V_{SS}$  (no load)

- all peripherals are disabled unless otherwise mentioned

- the given value is calculated by measuring the current consumption

- with all peripherals clocked OFF

- with only one peripheral clocked on

# Table 39. Peripheral current consumption in Run or Sleep mode<sup>(1)</sup>

|      |                     | Typical                                               | consumption, V                                        |                                                       | 25 °C                         |                      |

|------|---------------------|-------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|-------------------------------|----------------------|

| Per  | ipheral             | Range 1,<br>V <sub>CORE</sub> =1.8 V<br>VOS[1:0] = 01 | Range 2,<br>V <sub>CORE</sub> =1.5 V<br>VOS[1:0] = 10 | Range 3,<br>V <sub>CORE</sub> =1.2 V<br>VOS[1:0] = 11 | Low-power<br>sleep and<br>run | Unit                 |

|      | CRS                 | 2.5                                                   | 2                                                     | 2                                                     | 2                             |                      |

|      | DAC1                | 4                                                     | 3.5                                                   | 3                                                     | 2.5                           |                      |

|      | I2C1                | 11                                                    | 9.5                                                   | 7.5                                                   | 9                             |                      |

|      | I2C2                | 4                                                     | 3.5                                                   | 3                                                     | 2.5                           |                      |

|      | LPTIM1              | 10                                                    | 8.5                                                   | 6.5                                                   | 8                             |                      |

| APB1 | LPUART1             | 8                                                     | 6.5                                                   | 5.5                                                   | 6                             | µA/MHz               |

| AFDI | SPI2                | 9                                                     | 4.5                                                   | 3.5                                                   | 4                             | (f <sub>HCLK</sub> ) |

|      | USB                 | 8.5                                                   | 4.5                                                   | 4                                                     | 4.5                           |                      |

|      | USART2              | 14.5                                                  | 12                                                    | 9.5                                                   | 11                            |                      |

|      | TIM2                | 10.5                                                  | 8.5                                                   | 7                                                     | 9                             |                      |

|      | TIM6                | 3.5                                                   | 3                                                     | 2.5                                                   | 2                             |                      |

|      | WWDG                | 3                                                     | 2                                                     | 2                                                     | 2                             |                      |

|      | ADC1 <sup>(2)</sup> | 5.5                                                   | 5                                                     | 3.5                                                   | 4                             |                      |

|      | SPI1                | 4                                                     | 3                                                     | 3                                                     | 2.5                           |                      |

|      | USART1              | 14.5                                                  | 11.5                                                  | 9.5                                                   | 12                            |                      |

| APB2 | TIM21               | 7.5                                                   | 6                                                     | 5                                                     | 5.5                           | µA/MHz               |

| AFBZ | TIM22               | 7                                                     | 6                                                     | 5                                                     | 6                             | (f <sub>HCLK</sub> ) |

|      | FIREWALL            | 1.5                                                   | 1                                                     | 1                                                     | 0.5                           |                      |

|      | DBGMCU              | 1.5                                                   | 1                                                     | 1                                                     | 0.5                           |                      |

|      | SYSCFG              | 2.5                                                   | 2                                                     | 2                                                     | 1.5                           |                      |

| Symbol   | Parameter                                                                     | Conditions                                                        | Тур | Max | Unit |

|----------|-------------------------------------------------------------------------------|-------------------------------------------------------------------|-----|-----|------|

|          |                                                                               | f <sub>HCLK</sub> = f <sub>MSI</sub> = 4.2 MHz                    | 5.0 | 8   |      |

|          | Wakeup from Stop mode, regulator in Run mode                                  | f <sub>HCLK</sub> = f <sub>HSI</sub> = 16 MHz                     | 4.9 | 7   |      |

|          |                                                                               | f <sub>HCLK</sub> = f <sub>HSI</sub> /4 = 4 MHz                   | 8.0 | 11  |      |

| twustop  |                                                                               | f <sub>HCLK</sub> = f <sub>MSI</sub> = 4.2 MHz<br>Voltage range 1 | 5.0 | 8   |      |

|          |                                                                               | f <sub>HCLK</sub> = f <sub>MSI</sub> = 4.2 MHz<br>Voltage range 2 | 5.0 | 8   |      |

|          |                                                                               | f <sub>HCLK</sub> = f <sub>MSI</sub> = 4.2 MHz<br>Voltage range 3 | 5.0 | 8   |      |

|          | Wakeup from Stop mode, regulator in low-<br>power mode                        | f <sub>HCLK</sub> = f <sub>MSI</sub> = 2.1 MHz                    | 7.3 | 13  |      |

|          |                                                                               | f <sub>HCLK</sub> = f <sub>MSI</sub> = 1.05 MHz                   | 13  | 23  | μs   |

|          |                                                                               | f <sub>HCLK</sub> = f <sub>MSI</sub> = 524 kHz                    | 28  | 38  |      |

|          |                                                                               | f <sub>HCLK</sub> = f <sub>MSI</sub> = 262 kHz                    | 51  | 65  |      |

|          |                                                                               | f <sub>HCLK</sub> = f <sub>MSI</sub> = 131 kHz                    | 100 | 120 |      |

|          |                                                                               | f <sub>HCLK</sub> = MSI = 65 kHz                                  | 190 | 260 |      |

|          |                                                                               | f <sub>HCLK</sub> = f <sub>HSI</sub> = 16 MHz                     | 4.9 | 7   |      |

|          |                                                                               | f <sub>HCLK</sub> = f <sub>HSI</sub> /4 = 4 MHz                   | 8.0 | 11  |      |

|          |                                                                               | f <sub>HCLK</sub> = f <sub>HSI</sub> = 16 MHz                     | 4.9 | 7   |      |

|          | Wakeup from Stop mode, regulator in low-<br>power mode, code running from RAM | f <sub>HCLK</sub> = f <sub>HSI</sub> /4 = 4 MHz                   | 7.9 | 10  |      |

|          |                                                                               | f <sub>HCLK</sub> = f <sub>MSI</sub> = 4.2 MHz                    | 4.7 | 8   |      |

| +        | Wakeup from Standby mode, FWU bit = 1                                         | f <sub>HCLK</sub> = MSI = 2.1 MHz                                 | 65  | 130 | μs   |

| twustdby | Wakeup from Standby mode, FWU bit = 0                                         | f <sub>HCLK</sub> = MSI = 2.1 MHz                                 | 2.2 | 3   | ms   |

Table 41. Low-power mode wakeup timings (continued)

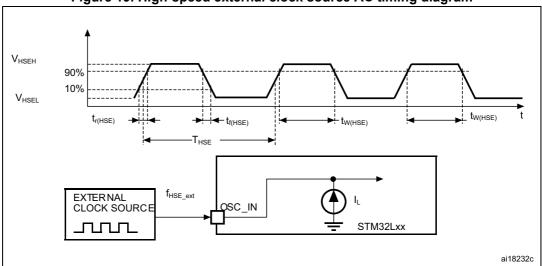

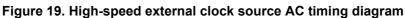

# 6.3.6 External clock source characteristics

### High-speed external user clock generated from an external source

In bypass mode the HSE oscillator is switched off and the input pin is a standard GPIO.The external clock signal has to respect the I/O characteristics in *Section 6.3.12*. However, the recommended clock input waveform is shown in *Figure 19*.

| Parameter                           | Conditions                                                                                                                                                                                                            | Min                                                                                                                                                                                                                                                         | Тур                                                                                                                                                                                                                                                                   | Мах                                                                                                                                                                                                                                                                             | Unit                                                                                                                                                                                                                                                                                  |

|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| User external clock source          | CSS is ON or<br>PLL is used                                                                                                                                                                                           | 1                                                                                                                                                                                                                                                           | 8                                                                                                                                                                                                                                                                     | 32                                                                                                                                                                                                                                                                              | MHz                                                                                                                                                                                                                                                                                   |

| frequency                           | CSS is OFF,<br>PLL not used                                                                                                                                                                                           | 0                                                                                                                                                                                                                                                           | 8                                                                                                                                                                                                                                                                     | 32                                                                                                                                                                                                                                                                              | MHz                                                                                                                                                                                                                                                                                   |

| OSC_IN input pin high level voltage |                                                                                                                                                                                                                       | $0.7V_{DD}$                                                                                                                                                                                                                                                 | -                                                                                                                                                                                                                                                                     | V <sub>DD</sub>                                                                                                                                                                                                                                                                 | V                                                                                                                                                                                                                                                                                     |

| OSC_IN input pin low level voltage  |                                                                                                                                                                                                                       | V <sub>SS</sub>                                                                                                                                                                                                                                             | -                                                                                                                                                                                                                                                                     | $0.3V_{DD}$                                                                                                                                                                                                                                                                     | v                                                                                                                                                                                                                                                                                     |

| OSC_IN high or low time             |                                                                                                                                                                                                                       | 12                                                                                                                                                                                                                                                          | -                                                                                                                                                                                                                                                                     | -                                                                                                                                                                                                                                                                               | ns                                                                                                                                                                                                                                                                                    |

| OSC_IN rise or fall time            | -                                                                                                                                                                                                                     | -                                                                                                                                                                                                                                                           | -                                                                                                                                                                                                                                                                     | 20                                                                                                                                                                                                                                                                              | 115                                                                                                                                                                                                                                                                                   |

| OSC_IN input capacitance            |                                                                                                                                                                                                                       | -                                                                                                                                                                                                                                                           | 2.6                                                                                                                                                                                                                                                                   | -                                                                                                                                                                                                                                                                               | pF                                                                                                                                                                                                                                                                                    |

| Duty cycle                          |                                                                                                                                                                                                                       | 45                                                                                                                                                                                                                                                          | -                                                                                                                                                                                                                                                                     | 55                                                                                                                                                                                                                                                                              | %                                                                                                                                                                                                                                                                                     |

| OSC_IN Input leakage current        | $V_{SS} \leq V_{IN} \leq V_{DD}$                                                                                                                                                                                      | -                                                                                                                                                                                                                                                           | -                                                                                                                                                                                                                                                                     | ±1                                                                                                                                                                                                                                                                              | μA                                                                                                                                                                                                                                                                                    |

|                                     | User external clock source<br>frequency<br>OSC_IN input pin high level voltage<br>OSC_IN input pin low level voltage<br>OSC_IN high or low time<br>OSC_IN rise or fall time<br>OSC_IN input capacitance<br>Duty cycle | User external clock source<br>frequency CSS is ON or<br>PLL is used CSS is OFF,<br>PLL not used OSC_IN input pin high level voltage OSC_IN input pin low level voltage OSC_IN high or low time OSC_IN rise or fall time OSC_IN input capacitance Duty cycle | User external clock source<br>frequencyCSS is ON or<br>PLL is used1CSS is OFF,<br>PLL not used0OSC_IN input pin high level voltage0.7V_DDOSC_IN input pin low level voltageVSSOSC_IN high or low time12OSC_IN rise or fall time-OSC_IN input capacitance-Duty cycle45 | User external clock source<br>frequencyCSS is ON or<br>PLL is used18CSS is OFF,<br>PLL not used08OSC_IN input pin high level voltage<br>OSC_IN niput pin low level voltage0.7V_DD-OSC_IN high or low time-12-OSC_IN rise or fall timeOSC_IN input capacitance-2.6Duty cycle-45- | User external clock source<br>frequencyCSS is ON or<br>PLL is used1832CSS is OFF,<br>PLL not used0832OSC_IN input pin high level voltage<br>OSC_IN input pin low level voltage0.7V_DD-V_DDOSC_IN high or low time-12-0.3V_DDOSC_IN rise or fall time20-OSC_IN input capacitance-45-55 |

| Table 42. High-speed external user clock characteristics <sup>(1)</sup> | Table 42 | . Hiah-speed | external use | r clock charac | teristics <sup>(1)</sup> |

|-------------------------------------------------------------------------|----------|--------------|--------------|----------------|--------------------------|

|-------------------------------------------------------------------------|----------|--------------|--------------|----------------|--------------------------|

1. Guaranteed by design.

### Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

Software recommendations

The software flowchart must include the management of runaway conditions such as:

- Corrupted program counter

- Unexpected reset

- Critical data corruption (control registers...)

Prequalification trials

Most of the common failures (unexpected reset and program counter corruption) can be reproduced by manually forcing a low state on the NRST pin or the oscillator pins for 1 second.

To complete these trials, ESD stress can be applied directly on the device, over the range of specification values. When unexpected behavior is detected, the software can be hardened to prevent unrecoverable errors occurring (see application note AN1015).

## **Electromagnetic Interference (EMI)**

The electromagnetic field emitted by the device are monitored while a simple application is executed (toggling 2 LEDs through the I/O ports). This emission test is compliant with IEC 61967-2 standard which specifies the test board and the pin loading.

|        |                            |                                              | Monitored                |                        | Max vs. f <sub>osc</sub> /f <sub>CPU</sub> |                  |      |     |    |

|--------|----------------------------|----------------------------------------------|--------------------------|------------------------|--------------------------------------------|------------------|------|-----|----|

| Symbol | Parameter                  | Conditions                                   | frequency band           | 8 MHz/<br>4 MHz        | 8 MHz/<br>16 MHz                           | 8 MHz/<br>32 MHz | Unit |     |    |

|        |                            | $V_{DD} = 3.6 V,$<br>T <sub>A</sub> = 25 °C. | V <sub>DD</sub> = 3.6 V, | 0.1 to 30 MHz          | -21                                        | -15              | -12  |     |    |

| 0      | Peak level                 |                                              |                          | $T_A = 25 \ ^\circ C,$ | $T_{A} = 25 \text{ °C},$                   | 30 to 130 MHz    | -14  | -12 | -1 |

| SEMI   | compliant with IEC 61967-2 | 130 MHz to 1GHz                              | -10                      | -11                    | -7                                         |                  |      |     |    |

|        |                            | EMI Level                                    | 1                        | 1                      | 1                                          | -                |      |     |    |

Table 55. EMI characteristics

### Equation 1: R<sub>AIN</sub> max formula

$$R_{AIN} < \frac{T_{S}}{f_{ADC} \times C_{ADC} \times \ln(2^{N+2})} - R_{ADC}$$

The simplified formula above (*Equation 1*) is used to determine the maximum external impedance allowed for an error below 1/4 of LSB. Here N = 12 (from 12-bit resolution).

|                            |                        | P may for                                         |                            |                            | R <sub>AIN</sub> max       | c for stand                | dard chan                   | inels (kΩ)                                                 |                                                           |

|----------------------------|------------------------|---------------------------------------------------|----------------------------|----------------------------|----------------------------|----------------------------|-----------------------------|------------------------------------------------------------|-----------------------------------------------------------|

| T <sub>s</sub><br>(cycles) | t <sub>S</sub><br>(μs) | R <sub>AIN</sub> max for<br>fast channels<br>(kΩ) | V <sub>DD</sub> ><br>2.7 V | V <sub>DD</sub> ><br>2.4 V | V <sub>DD</sub> ><br>2.0 V | V <sub>DD</sub> ><br>1.8 V | V <sub>DD</sub> ><br>1.75 V | V <sub>DD</sub> > 1.65 V<br>and<br>T <sub>A</sub> > -10 °C | V <sub>DD</sub> > 1.65 V<br>and<br>T <sub>A</sub> > 25 °C |

| 1.5                        | 0.09                   | 0.5                                               | < 0.1                      | NA                         | NA                         | NA                         | NA                          | NA                                                         | NA                                                        |

| 3.5                        | 0.22                   | 1                                                 | 0.2                        | < 0.1                      | NA                         | NA                         | NA                          | NA                                                         | NA                                                        |

| 7.5                        | 0.47                   | 2.5                                               | 1.7                        | 1.5                        | < 0.1                      | NA                         | NA                          | NA                                                         | NA                                                        |

| 12.5                       | 0.78                   | 4                                                 | 3.2                        | 3                          | 1                          | NA                         | NA                          | NA                                                         | NA                                                        |

| 19.5                       | 1.22                   | 6.5                                               | 5.7                        | 5.5                        | 3.5                        | NA                         | NA                          | NA                                                         | < 0.1                                                     |

| 39.5                       | 2.47                   | 13                                                | 12.2                       | 12                         | 10                         | NA                         | NA                          | NA                                                         | 5                                                         |

| 79.5                       | 4.97                   | 27                                                | 26.2                       | 26                         | 24                         | < 0.1                      | NA                          | NA                                                         | 19                                                        |

| 160.5                      | 10.03                  | 50                                                | 49.2                       | 49                         | 47                         | 32                         | < 0.1                       | < 0.1                                                      | 42                                                        |

Table 64.  $R_{AIN}$  max for  $f_{ADC}$  = 16 MHz<sup>(1)</sup>

1. Guaranteed by design.

# Table 65. ADC accuracy<sup>(1)(2)(3)</sup>

| Symbol | Parameter                                                                          | Conditions                                             | Min  | Тур  | Max | Unit |

|--------|------------------------------------------------------------------------------------|--------------------------------------------------------|------|------|-----|------|

| ET     | Total unadjusted error                                                             |                                                        | -    | 2    | 4   |      |

| EO     | Offset error                                                                       |                                                        | -    | 1    | 2.5 |      |

| EG     | Gain error                                                                         |                                                        | -    | 1    | 2   | LSB  |

| EL     | Integral linearity error                                                           |                                                        | -    | 1.5  | 2.5 |      |

| ED     | Differential linearity error                                                       |                                                        | -    | 1    | 1.5 |      |

|        | Effective number of bits                                                           | 1.65 V < V <sub>DDA</sub> = V <sub>REF+</sub> < 3.6 V, | 10.2 | 11   |     |      |

| ENOB   | Effective number of bits (16-bit mode oversampling with ratio =256) <sup>(4)</sup> | range 1/2/3                                            | 11.3 | 12.1 | -   | bits |

| SINAD  | Signal-to-noise distortion                                                         |                                                        | 63   | 69   | -   |      |

|        | Signal-to-noise ratio                                                              |                                                        | 63   | 69   | -   |      |

| SNR    | Signal-to-noise ratio (16-bit mode oversampling with ratio =256) <sup>(4)</sup>    |                                                        | 70   | 76   | -   | dB   |

| THD    | Total harmonic distortion                                                          |                                                        | -    | -85  | -73 |      |

# 6.3.19 Timer characteristics

### **TIM timer characteristics**

The parameters given in the Table 71 are guaranteed by design.

Refer to Section 6.3.13: I/O port characteristics for details on the input/output alternate function characteristics (output compare, input capture, external clock, PWM output).

| Symbol                 | Parameter                                                                                      | Conditions                    | Min    | Max                     | Unit                 |  |  |  |

|------------------------|------------------------------------------------------------------------------------------------|-------------------------------|--------|-------------------------|----------------------|--|--|--|

| t <sub>res(TIM)</sub>  | Timer resolution time                                                                          |                               | 1      | -                       | t <sub>TIMxCLK</sub> |  |  |  |

|                        |                                                                                                | f <sub>TIMxCLK</sub> = 32 MHz | 31.25  | -                       | ns                   |  |  |  |

| f <sub>EXT</sub>       | Timer external clock frequency on CH1 to CH4                                                   |                               | 0      | f <sub>TIMxCLK</sub> /2 | MHz                  |  |  |  |

|                        |                                                                                                | f <sub>TIMxCLK</sub> = 32 MHz | 0      | 16                      | MHz                  |  |  |  |