Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                      |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 32MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART, USB                          |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT          |

| Number of I/O              | 51                                                                    |

| Program Memory Size        | 64KB (64K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | 2K x 8                                                                |

| RAM Size                   | 8K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 3.6V                                                          |

| Data Converters            | A/D 16x12b; D/A 1x12b                                                 |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 64-LQFP                                                               |

| Supplier Device Package    | 64-LQFP (10x10)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l052r8t7 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2 Description

The ultra-low-power STM32L052x6/8 microcontrollers incorporate the connectivity power of the universal serial bus (USB 2.0 crystal-less) with the high-performance ARM<sup>®</sup> Cortex<sup>®</sup>-M0+ 32-bit RISC core operating at a 32 MHz frequency, a memory protection unit (MPU), high-speed embedded memories (64 Kbytes of Flash program memory, 2 Kbytes of data EEPROM and 8 Kbytes of RAM) plus an extensive range of enhanced I/Os and peripherals.

The STM32L052x6/8 devices provide high power efficiency for a wide range of performance. It is achieved with a large choice of internal and external clock sources, an internal voltage adaptation and several low-power modes.

The STM32L052x6/8 devices offer several analog features, one 12-bit ADC with hardware oversampling, one DAC, two ultra-low-power comparators, several timers, one low-power timer (LPTIM), three general-purpose 16-bit timers and one basic timer, one RTC and one SysTick which can be used as timebases. They also feature two watchdogs, one watchdog with independent clock and window capability and one window watchdog based on bus clock.

Moreover, the STM32L052x6/8 devices embed standard and advanced communication interfaces: up to two I2C, two SPIs, one I2S, two USARTs, a low-power UART (LPUART), and a crystal-less USB. The devices offer up to 24 capacitive sensing channels to simply add touch sensing functionality to any application.

The STM32L052x6/8 also include a real-time clock and a set of backup registers that remain powered in Standby mode.

The ultra-low-power STM32L052x6/8 devices operate from a 1.8 to 3.6 V power supply (down to 1.65 V at power down) with BOR and from a 1.65 to 3.6 V power supply without BOR option. They are available in the -40 to +125 °C temperature range. A comprehensive set of power-saving modes allows the design of low-power applications.

# 2.1 Device overview

| Table 2 Illtra-low- | power STM32L052x6/x   | 8 dovico fosturos and | norinhoral counts  |

|---------------------|-----------------------|-----------------------|--------------------|

|                     | DOMEL OLIMISTEDSTVOLV | o device realures and | periprierar counts |

| Peripheral                         |                     | STM32L0<br>52T6        | STM32<br>L052K6        | STM32<br>L052C6        | STM32<br>L052R6            | STM32L<br>052T8 | STM32<br>L052K8       | STM32<br>L052C8 | STM32<br>L052R8        |  |

|------------------------------------|---------------------|------------------------|------------------------|------------------------|----------------------------|-----------------|-----------------------|-----------------|------------------------|--|

| Flash (Kbyte                       | es)                 |                        | 32                     | 2                      |                            | 64              |                       |                 |                        |  |

| Data EEPRC                         | M (Kbytes)          |                        | 2                      |                        |                            |                 |                       | 2               |                        |  |

| RAM (Kbyte                         | s)                  |                        | 8                      |                        |                            |                 | 8                     | 3               |                        |  |

|                                    | General-<br>purpose |                        | 3                      |                        |                            |                 | 3                     | 3               |                        |  |

| Timers                             | Basic               |                        | 1                      |                        |                            |                 |                       | 1               |                        |  |

|                                    | LPTIMER             |                        | 1                      |                        |                            |                 | ŕ                     | 1               |                        |  |

|                                    | ICK/IWDG/<br>VDG    |                        | 1/1/                   | 1/1                    |                            |                 | 1/1/                  | /1/1            |                        |  |

|                                    | SPI/I2S             | 3(2) <sup>(1)</sup> /0 | 3(2) <sup>(1)</sup> /0 | 4(2) <sup>(1)</sup> /1 | 3(2) <sup>(1)</sup> /0     | 3(2)            | <sup>(1)</sup> /0     | 4(2)            | <sup>(1)</sup> /1      |  |

|                                    | l <sup>2</sup> C    | 2                      | 1                      |                        | 2                          | 2               | 1                     | :               | 2                      |  |

| Communic ation                     | USART               |                        | 2                      |                        |                            | 2               |                       |                 |                        |  |

| interfaces                         | LPUART              | 1                      | 0                      |                        | 1                          | 1 0             |                       | 1               |                        |  |

|                                    | USB/<br>(VDD_USB)   | 1/                     | (0) 1/(1)              |                        | (1)                        | 1/              | (0)                   | 1/(1)           |                        |  |

| GPIOs                              |                     | 29                     | 27 <sup>(2)</sup>      | 37                     | 51 <sup>(3)</sup>          | 29              | 27 <sup>(2)</sup>     | 37              | 51 <sup>(3)</sup>      |  |

| Clocks:<br>HSE/LSE/HS              | SI/MSI/LSI          | 0/1/1/1/1              | 0/1/1/1/1              | 1/1/1/1/1              | 1/1/1/1/1                  | 0/1/1/1/1       | 0/1/1/1/1             | 1/1/1/1/1       | 1/1/1/1/1              |  |

| 12-bit synch<br>ADC<br>Number of c |                     | 1<br>10                | 1<br>10                | 1<br>10                | 1<br>16 <sup>(3)</sup>     | 1<br>10         | 1<br>10               | 1<br>10         | 1<br>16 <sup>(3)</sup> |  |

| 12-bit DAC<br>Number of channels   |                     |                        | 1                      |                        |                            | 1<br>1          |                       |                 |                        |  |

| Comparators                        |                     |                        |                        |                        | 2                          | 2               |                       |                 |                        |  |

| Capacitive sensing channels        |                     | 1                      | 4                      | 17                     | 24 <sup>(3)</sup>          | 1               | 4                     | 17              | 24 <sup>(3)</sup>      |  |

| Max. CPU fr                        | equency             | 32 MHz                 |                        |                        |                            |                 |                       |                 |                        |  |

| Operating v                        | oltage              |                        | 1.8 V to 3.            |                        | to 1.65 V a<br>to 3.6 V wi |                 | wn) with BC<br>option | OR option       |                        |  |

## 3.2 Interconnect matrix

Several peripherals are directly interconnected. This allows autonomous communication between peripherals, thus saving CPU resources and power consumption. In addition, these hardware connections allow fast and predictable latency.

Depending on peripherals, these interconnections can operate in Run, Sleep, Low-power run, Low-power sleep and Stop modes.

|                        |                             | A32LUXX peripherals in                                                      |     | incot in |                      | -                      | 1    |

|------------------------|-----------------------------|-----------------------------------------------------------------------------|-----|----------|----------------------|------------------------|------|

| Interconnect<br>source | Interconnect<br>destination | Interconnect action                                                         | Run | Sleep    | Low-<br>power<br>run | Low-<br>power<br>sleep | Stop |

| COMPx                  | TIM2,TIM21,<br>TIM22        | Timer input channel,<br>trigger from analog<br>signals comparison           | Y   | Y        | Y                    | Y                      | -    |

| COMPX                  | LPTIM                       | Timer input channel,<br>trigger from analog<br>signals comparison           | Y   | Y        | Y                    | Y                      | Y    |

| TIMx                   | TIMx                        | Timer triggered by other timer                                              | Y   | Y        | Y                    | Y                      | -    |

| RTC                    | TIM21                       | Timer triggered by Auto<br>wake-up                                          | Y   | Y        | Y                    | Y                      | -    |

| RIC                    | LPTIM                       | Timer triggered by RTC event                                                | Y   | Y        | Y                    | Y                      | Y    |

| All clock<br>source    | TIMx                        | Clock source used as<br>input channel for RC<br>measurement and<br>trimming | Y   | Y        | Y                    | Y                      | -    |

| USB                    | CRS/HSI48                   | the clock recovery<br>system trims the HSI48<br>based on USB SOF            | Y   | Y        | -                    | -                      | -    |

|                        | TIMx                        | Timer input channel and trigger                                             | Y   | Y        | Y                    | Y                      | -    |

| GPIO                   | LPTIM                       | Timer input channel and trigger                                             | Y   | Y        | Y                    | Y                      | Y    |

|                        | ADC,DAC                     | Conversion trigger                                                          | Y   | Y        | Y                    | Y                      | -    |

Table 6. STM32L0xx peripherals interconnect matrix

#### 3.4.3 Voltage regulator

The regulator has three operation modes: main (MR), low power (LPR) and power down.

- MR is used in Run mode (nominal regulation)

- LPR is used in the Low-power run, Low-power sleep and Stop modes

- Power down is used in Standby mode. The regulator output is high impedance, the kernel circuitry is powered down, inducing zero consumption but the contents of the registers and RAM are lost except for the standby circuitry (wakeup logic, IWDG, RTC, LSI, LSE crystal 32 KHz oscillator, RCC\_CSR).

## 3.5 Clock management

The clock controller distributes the clocks coming from different oscillators to the core and the peripherals. It also manages clock gating for low-power modes and ensures clock robustness. It features:

Clock prescaler

To get the best trade-off between speed and current consumption, the clock frequency to the CPU and peripherals can be adjusted by a programmable prescaler.

#### • Safe clock switching

Clock sources can be changed safely on the fly in Run mode through a configuration register.

#### Clock management

To reduce power consumption, the clock controller can stop the clock to the core, individual peripherals or memory.

#### System clock source

Three different clock sources can be used to drive the master clock SYSCLK:

- 1-25 MHz high-speed external crystal (HSE), that can supply a PLL

- 16 MHz high-speed internal RC oscillator (HSI), trimmable by software, that can supply a PLLMultispeed internal RC oscillator (MSI), trimmable by software, able to generate 7 frequencies (65 kHz, 131 kHz, 262 kHz, 524 kHz, 1.05 MHz, 2.1 MHz, 4.2 MHz). When a 32.768 kHz clock source is available in the system (LSE), the MSI frequency can be trimmed by software down to a ±0.5% accuracy.

#### • Auxiliary clock source

Two ultra-low-power clock sources that can be used to drive the real-time clock:

- 32.768 kHz low-speed external crystal (LSE)

- 37 kHz low-speed internal RC (LSI), also used to drive the independent watchdog. The LSI clock can be measured using the high-speed internal RC oscillator for greater precision.

#### • RTC clock source

The LSI, LSE or HSE sources can be chosen to clock the RTC, whatever the system clock.

#### USB clock source

A 48 MHz clock trimmed through the USB SOF supplies the USB interface.

## 3.10 Direct memory access (DMA)

The flexible 7-channel, general-purpose DMA is able to manage memory-to-memory, peripheral-to-memory and memory-to-peripheral transfers. The DMA controller supports circular buffer management, avoiding the generation of interrupts when the controller reaches the end of the buffer.

Each channel is connected to dedicated hardware DMA requests, with software trigger support for each channel. Configuration is done by software and transfer sizes between source and destination are independent.

The DMA can be used with the main peripherals: SPI, I<sup>2</sup>C, USART, LPUART, general-purpose timers, DAC, and ADC.

# 3.11 Analog-to-digital converter (ADC)

A native 12-bit, extended to 16-bit through hardware oversampling, analog-to-digital converter is embedded into STM32L052x6/8 device. It has up to 16 external channels and 3 internal channels (temperature sensor, voltage reference). Three channels, PA0, PA4 and PA5, are fast channels, while the others are standard channels.

The ADC performs conversions in single-shot or scan mode. In scan mode, automatic conversion is performed on a selected group of analog inputs.

The ADC frequency is independent from the CPU frequency, allowing maximum sampling rate of 1.14 MSPS even with a low CPU speed. The ADC consumption is low at all frequencies (~25  $\mu$ A at 10 kSPS, ~200  $\mu$ A at 1MSPS). An auto-shutdown function guarantees that the ADC is powered off except during the active conversion phase.

The ADC can be served by the DMA controller. It can operate from a supply voltage down to 1.65 V.

The ADC features a hardware oversampler up to 256 samples, this improves the resolution to 16 bits (see AN2668).

An analog watchdog feature allows very precise monitoring of the converted voltage of one, some or all scanned channels. An interrupt is generated when the converted voltage is outside the programmed thresholds.

The events generated by the general-purpose timers (TIMx) can be internally connected to the ADC start triggers, to allow the application to synchronize A/D conversions and timers.

## 3.12 Temperature sensor

The temperature sensor (T<sub>SENSE</sub>) generates a voltage V<sub>SENSE</sub> that varies linearly with temperature.

The temperature sensor is internally connected to the ADC\_IN18 input channel which is used to convert the sensor output voltage into a digital value.

The sensor provides good linearity but it has to be calibrated to obtain good overall accuracy of the temperature measurement. As the offset of the temperature sensor varies from chip to chip due to process variation, the uncalibrated internal temperature sensor is suitable for applications that detect temperature changes only.

DocID025936 Rev 7

|        |         | Pin Nı                 | umber  |        |         |                                       |          |               |       |                                                                                                 |                         |

|--------|---------|------------------------|--------|--------|---------|---------------------------------------|----------|---------------|-------|-------------------------------------------------------------------------------------------------|-------------------------|

| LQFP32 | UFQFN32 | WLCSP36 <sup>(1)</sup> | LQFP48 | LQFP64 | TFBGA64 | Pin name<br>(function after<br>reset) | Pin type | I/O structure | Notes | Alternate functions                                                                             | Additional<br>functions |

| -      | -       | E2                     | 21     | 29     | G7      | PB10                                  | I/O      | FT            | -     | TIM2_CH3,<br>TSC_SYNC,<br>LPUART1_TX,<br>SPI2_SCK,<br>I2C2_SCL                                  | -                       |

| -      | -       | D2                     | 22     | 30     | H7      | PB11                                  | I/O      | FT            | -     | EVENTOUT,<br>TIM2_CH4,<br>TSC_G6_IO1,<br>LPUART1_RX,<br>I2C2_SDA                                | -                       |

| 16     | -       | -                      | 23     | 31     | D6      | VSS                                   | S        | -             | -     | -                                                                                               | -                       |

| 17     | 17      | F1                     | 24     | 32     | E5      | VDD                                   | S        | -             | -     | -                                                                                               | -                       |

| -      | -       | -                      | 25     | 33     | H8      | PB12                                  | I/O      | FT            | -     | SPI2_NSS/I2S2_WS,<br>LPUART1_RTS_DE,<br>TSC_G6_IO2,<br>I2C2_SMBA,<br>EVENTOUT                   | -                       |

| -      | -       | -                      | 26     | 34     | G8      | PB13                                  | I/O      | FTf           | -     | SPI2_SCK/I2S2_CK,<br>TSC_G6_IO3,<br>LPUART1_CTS,<br>I2C2_SCL,<br>TIM21_CH1                      | -                       |

| -      | -       | -                      | 27     | 35     | F8      | PB14                                  | I/O      | FTf           | -     | SPI2_MISO/I<br>2S2_MCK,<br>RTC_OUT,<br>TSC_G6_IO4,<br>LPUART1_RTS_DE,<br>I2C2_SDA,<br>TIM21_CH2 | -                       |

| -      | -       | -                      | 28     | 36     | F7      | PB15                                  | I/O      | FT            | -     | SPI2_MOSI/I2S2_SD,<br>RTC_REFIN                                                                 | -                       |

| -      | -       | -                      | -      | 37     | F6      | PC6                                   | I/O      | FT            | -     | TIM22_CH1,<br>TSC_G8_IO1                                                                        | -                       |

| -      | -       | -                      | -      | 38     | E7      | PC7                                   | I/O      | FT            | -     | TIM22_CH2,<br>TSC_G8_IO2                                                                        | -                       |

| -      | -       | -                      | -      | 39     | E8      | PC8                                   | I/O      | FT            | -     | TIM22_ETR,<br>TSC_G8_IO3                                                                        | -                       |

Table 16. STM32L052x6/8 pin definitions (continued)

|        |         | Pin Nu                 | ımber  |        |         |                                       | -        |               |       |                                                                       |                         |  |

|--------|---------|------------------------|--------|--------|---------|---------------------------------------|----------|---------------|-------|-----------------------------------------------------------------------|-------------------------|--|

| LQFP32 | UFQFN32 | WLCSP36 <sup>(1)</sup> | LQFP48 | LQFP64 | TFBGA64 | Pin name<br>(function after<br>reset) | Pin type | I/O structure | Notes | Alternate functions                                                   | Additional<br>functions |  |

| -      | -       | -                      | -      | 40     | D8      | PC9                                   | I/O      | FT            | -     | TIM21_ETR,<br>USB_NOE,<br>TSC_G8_IO4                                  | -                       |  |

| 18     | 18      | E1                     | 29     | 41     | D7      | PA8                                   | I/O      | FT            | -     | MCO,<br>USB_CRS_SYNC,<br>EVENTOUT,<br>USART1_CK                       | -                       |  |

| 19     | 19      | D1                     | 30     | 42     | C7      | PA9                                   | I/O      | FT            | -     | MCO, TSC_G4_IO1,<br>USART1_TX                                         | -                       |  |

| 20     | 20      | C1                     | 31     | 43     | C6      | PA10                                  | I/O      | FT            | -     | TSC_G4_IO2,<br>USART1_RX                                              | -                       |  |

| 21     | 21      | C2                     | 32     | 44     | C8      | PA11 <sup>(3)</sup>                   | I/O      | FT            | -     | SPI1_MISO,<br>EVENTOUT,<br>TSC_G4_IO3,<br>USART1_CTS,<br>COMP1_OUT    | USB_DM                  |  |

| 22     | 22      | B1                     | 33     | 45     | B8      | PA12 <sup>(3)</sup>                   | I/O      | FT            | -     | SPI1_MOSI,<br>EVENTOUT,<br>TSC_G4_IO4,<br>USART1_RTS_DE,<br>COMP2_OUT | USB_DP                  |  |

| 23     | 23      | A1                     | 34     | 46     | A8      | PA13                                  | I/O      | FT            | -     | SWDIO, USB_NOE                                                        | -                       |  |

| -      | -       | -                      | 35     | 47     | D5      | VSS                                   | S        | -             | -     | -                                                                     | -                       |  |

| -      | -       | -                      | 36     | 48     | E6      | VDD_USB                               | S        | -             | -     | -                                                                     | -                       |  |

| 24     | 24      | B2                     | 37     | 49     | A7      | PA14                                  | I/O      | FT            | -     | SWCLK, USART2_TX                                                      | -                       |  |

| 25     | 25      | A2                     | 38     | 50     | A6      | PA15                                  | I/O      | FT            | -     | SPI1_NSS,<br>TIM2_ETR,<br>EVENTOUT,<br>USART2_RX,<br>TIM2_CH1         | -                       |  |

| -      | -       | -                      | -      | 51     | B7      | PC10                                  | I/O      | FT            | -     | LPUART1_TX                                                            | -                       |  |

| -      | -       | -                      | -      | 52     | B6      | PC11                                  | I/O      | FT            | -     | LPUART1_RX                                                            | -                       |  |

| -      | -       | -                      | -      | 53     | C5      | PC12                                  | I/O      | FT            | -     | -                                                                     | -                       |  |

Table 16. STM32L052x6/8 pin definitions (continued)

|        |      | AF0                                     | AF1                            | AF2                | AF3        | AF4                                     | AF5                  | AF6     |

|--------|------|-----------------------------------------|--------------------------------|--------------------|------------|-----------------------------------------|----------------------|---------|

| Po     | ort  | SPI1/SPI2/I2S2/<br>USART1/<br>EVENTOUT/ | USART1/ I2C1 /TIM2/SYS_AF/ I2C |                    | I2C1/TSC   | 1/TSC EVENTOUT/ SPI2/I2S2/I2<br>LPUART1 |                      |         |

|        | PB0  | EVENTOUT                                | -                              | -                  | TSC_G3_IO2 | -                                       | -                    | -       |

|        | PB1  | -                                       | -                              | -                  | TSC_G3_IO3 | LPUART1_RTS_<br>DE                      | -                    | -       |

|        | PB2  | -                                       | -                              | LPTIM1_OUT         | TSC_G3_IO4 | -                                       | -                    | -       |

|        | PB3  | SPI1_SCK                                | -                              | TIM2_CH2           | TSC_G5I_O1 | EVENTOUT                                | -                    | -       |

|        | PB4  | SPI1_MISO                               | -                              | EVENTOUT           | TSC_G5_IO2 | TIM22_CH1                               | -                    | -       |

|        | PB5  | SPI1_MOSI                               | -                              | LPTIM1_IN1         | I2C1_SMBA  | TIM22_CH2                               | -                    | -       |

|        | PB6  | USART1_TX                               | I2C1_SCL                       | LPTIM1_ETR         | TSC_G5_IO3 | -                                       | -                    | -       |

|        | PB7  | USART1_RX                               | I2C1_SDA                       | LPTIM1_IN2         | TSC_G5_IO4 | -                                       | -                    | -       |

| Port B | PB8  | -                                       | -                              | -                  | TSC_SYNC   | I2C1_SCL                                | -                    | -       |

|        | PB9  | -                                       | -                              | EVENTOUT           | -          | I2C1_SDA                                | SPI2_NSS/I2S2_<br>WS | -       |

|        | PB10 | -                                       | -                              | TIM2_CH3           | TSC_SYNC   | LPUART1_TX                              | SPI2_SCK             | 12C2_S  |

|        | PB11 | EVENTOUT                                | -                              | TIM2_CH4           | TSC_G6_IO1 | LPUART1_RX                              |                      | 12C2_SI |

|        | PB12 | SPI2_NSS/I2S2_WS                        | -                              | LPUART1_RTS_<br>DE | TSC_G6_IO2 | -                                       | I2C2_SMBA            | EVENTC  |

|        | PB13 | SPI2_SCK/I2S2_CK                        | -                              | -                  | TSC_G6_IO3 | LPUART1_CTS                             | I2C2_SCL             | TIM21_C |

|        | PB14 | SPI2_MISO/I2S2_MCK                      | -                              | RTC_OUT            | TSC_G6_IO4 | LPUART1_RTS_<br>DE                      | I2C2_SDA             | TIM21_C |

|        | PB15 | SPI2_MOSI/I2S2_SD                       | -                              | RTC_REFIN          | -          | -                                       | -                    | -       |

49/144

STM32L052x6 STM32L052x8

Pin descriptions

# 6.2 Absolute maximum ratings

Stresses above the absolute maximum ratings listed in *Table 22: Voltage characteristics*, *Table 23: Current characteristics*, and *Table 24: Thermal characteristics* may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability. Device mission profile (application conditions) is compliant with JEDEC JESD47 Qualification Standard. Extended mission profiles are available on demand.

| Symbol                                                                      | Definition                                                                                                           | Min                  | Мах                  | Unit |

|-----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|----------------------|----------------------|------|

| V <sub>DD</sub> -V <sub>SS</sub>                                            | External main supply voltage<br>(including V <sub>DDA</sub> , V <sub>DD_USB</sub> , V <sub>DD</sub> ) <sup>(1)</sup> | -0.3                 | 4.0                  |      |

|                                                                             | Input voltage on FT and FTf pins                                                                                     | V <sub>SS</sub> –0.3 | V <sub>DD</sub> +4.0 |      |

| V <sub>IN</sub> <sup>(2)</sup>                                              | Input voltage on TC pins                                                                                             | V <sub>SS</sub> –0.3 | 4.0                  | V    |

| VIN Y                                                                       | Input voltage on BOOT0                                                                                               | V <sub>SS</sub>      | V <sub>DD</sub> +4.0 |      |

|                                                                             | Input voltage on any other pin                                                                                       | V <sub>SS</sub> -0.3 | 4.0                  |      |

| $ \Delta V_{DD} $                                                           | Variations between different $V_{DDx}$ power pins                                                                    | -                    | 50                   |      |

| V <sub>DDA</sub> -V <sub>DDx</sub>                                          | Variations between any $V_{DDx}$ and $V_{DDA}$ power $\mbox{pins}^{(3)}$                                             | -                    | 300                  | mV   |

| $ \Delta V_{SS} $                                                           | Variations between all different ground pins                                                                         | -                    | 50                   |      |

| V <sub>REF+</sub> –V <sub>DDA</sub>                                         | Allowed voltage difference for $V_{REF^+} > V_{DDA}$                                                                 | -                    | 0.4                  | V    |

| V <sub>ESD(HBM)</sub> Electrostatic discharge voltage<br>(human body model) |                                                                                                                      | see Sect             | ion 6.3.11           |      |

1. All main power (V<sub>DD</sub>,V<sub>DD</sub> USB, V<sub>DDA</sub>) and ground (V<sub>SS</sub>, V<sub>SSA</sub>) pins must always be connected to the external power supply, in the permitted range.

2. V<sub>IN</sub> maximum must always be respected. Refer to *Table* 23 for maximum allowed injected current values.

3. It is recommended to power V<sub>DD</sub> and V<sub>DDA</sub> from the same source. A maximum difference of 300 mV between V<sub>DD</sub> and V<sub>DDA</sub> can be tolerated during power-up and device operation. V<sub>DD\_USB</sub> is independent from V<sub>DD</sub> and V<sub>DDA</sub>: its value does not need to respect this rule.

| Symbol               | Parameter                                                                          | Conc                                                           | litions                                              | f <sub>HCLK</sub> | Тур  | Max <sup>(1)</sup> | Unit |

|----------------------|------------------------------------------------------------------------------------|----------------------------------------------------------------|------------------------------------------------------|-------------------|------|--------------------|------|

|                      |                                                                                    |                                                                | Range 3,                                             | 1 MHz             | 135  | 170                |      |

|                      |                                                                                    |                                                                | V <sub>CORE</sub> =1.2 V,                            | 2 MHz             | 240  | 270                | μA   |

|                      |                                                                                    |                                                                | VOS[1:0]=11                                          | 4 MHz             | 450  | 480                |      |

|                      |                                                                                    | $f_{HSE} = f_{HCLK}$ up to 16                                  | Range 2,                                             | 4 MHz             | 0.52 | 0.6                |      |

|                      |                                                                                    | MHz included,<br>f <sub>HSE</sub> = f <sub>HCLK</sub> /2 above | V <sub>CORE</sub> =1.5 ,V,                           | 8 MHz             | 1    | 1.2                |      |

|                      |                                                                                    | 16 MHz (PLL ON) <sup>(2)</sup>                                 | VOS[1:0]=10                                          | 16 MHz            | 2    | 2.3                |      |

| I <sub>DD</sub> (Run | Supply current in<br>Run mode, code<br>executed from<br>RAM, Flash<br>switched off |                                                                | Range 1,<br>V <sub>CORE</sub> =1.8 V,<br>VOS[1:0]=01 | 8 MHz             | 1.25 | 1.4                | mA   |

|                      |                                                                                    |                                                                |                                                      | 16 MHz            | 2.45 | 2.8                |      |

| from<br>RAM)         |                                                                                    |                                                                |                                                      | 32 MHz            | 5.1  | 5.4                |      |

|                      |                                                                                    |                                                                | Range 3,<br>V <sub>CORE</sub> =1.2 V,                | 65 kHz            | 34.5 | 75                 |      |

|                      |                                                                                    | MSI clock                                                      |                                                      | 524 kHz           | 83   | 120                | μA   |

|                      |                                                                                    |                                                                | VOS[1:0]=11                                          | 4.2 MHz           | 485  | 540                |      |

|                      |                                                                                    | HSI16 clock source                                             | Range 2,<br>V <sub>CORE</sub> =1.5 V,<br>VOS[1:0]=10 | 16 MHz            | 2.1  | 2.3                |      |

|                      |                                                                                    | (16 MHz)                                                       | Range 1,<br>V <sub>CORE</sub> =1.8 V,<br>VOS[1:0]=01 | 32 MHz            | 5.1  | 5.6                | mA   |

| Table 31. Current consumption in Run mode. | code with data processing running from RAM |

|--------------------------------------------|--------------------------------------------|

|                                            | coue man auta proceeding running nom roam  |

1. Guaranteed by characterization results at 125 °C, unless otherwise specified.

2. Oscillator bypassed (HSEBYP = 1 in RCC\_CR register).

| Table 32. Current consumption in Run mode vs code type,   |

|-----------------------------------------------------------|

| code with data processing running from RAM <sup>(1)</sup> |

| Symbol                                                   | Parameter                                     |                                                                                                                                                   | f <sub>HCLK</sub>                        | Тур       | Unit   |      |    |

|----------------------------------------------------------|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|-----------|--------|------|----|

|                                                          |                                               |                                                                                                                                                   |                                          | Dhrystone |        | 450  |    |

| Supply current in<br>I <sub>DD</sub> (Run Run mode, code |                                               |                                                                                                                                                   | Range 3,<br>V <sub>CORE</sub> =1.2 V,    | CoreMark  | 4 MHz  | 575  |    |

|                                                          | 6 6 A                                         | V <sub>CORE</sub> =1.2 V,<br>VOS[1:0]=11                                                                                                          | Fibonacci                                |           | 370    | μA   |    |

|                                                          | Run mode, code<br>executed from<br>RAM, Flash | f <sub>HSE</sub> = f <sub>HCLK</sub> up to<br>16 MHz included,<br>f <sub>HSE</sub> = f <sub>HCLK</sub> /2 above<br>16 MHz (PLL ON) <sup>(2)</sup> |                                          | while(1)  |        | 340  |    |

| from<br>RAM)                                             |                                               |                                                                                                                                                   |                                          | Dhrystone |        | 5.1  |    |

|                                                          | switched off                                  |                                                                                                                                                   | Range 1,                                 | CoreMark  | 32 MHz | 6.25 |    |

|                                                          |                                               |                                                                                                                                                   | V <sub>CORE</sub> =1.8 V,<br>VOS[1:0]=01 | Fibonacci |        | 4.4  | mA |

|                                                          |                                               |                                                                                                                                                   |                                          | while(1)  | 1      | 4.7  |    |

1. Guaranteed by characterization results, unless otherwise specified.

2. Oscillator bypassed (HSEBYP = 1 in RCC\_CR register).

## High-speed internal 48 MHz (HSI48) RC oscillator

| Symbol                  | Parameter                                                                          | Conditions             | Min                 | Тур  | Мах                | Unit |  |

|-------------------------|------------------------------------------------------------------------------------|------------------------|---------------------|------|--------------------|------|--|

| f <sub>HSI48</sub>      | Frequency                                                                          |                        | -                   | 48   | -                  | MHz  |  |

| TRIM                    | HSI48 user-trimming step                                                           |                        | 0.09 <sup>(2)</sup> | 0.14 | 0.2 <sup>(2)</sup> | %    |  |

| DuCy <sub>(HSI48)</sub> | Duty cycle                                                                         |                        | 45 <sup>(2)</sup>   | -    | 55 <sup>(2)</sup>  | %    |  |

| ACC <sub>HSI48</sub>    | Accuracy of the HSI48<br>oscillator (factory calibrated<br>before CRS calibration) | T <sub>A</sub> = 25 °C | -4 <sup>(3)</sup>   | -    | 4 <sup>(3)</sup>   | %    |  |

| t <sub>su(HSI48)</sub>  | HSI48 oscillator startup time                                                      |                        | -                   | -    | 6 <sup>(2)</sup>   | μs   |  |

| I <sub>DDA(HSI48)</sub> | HSI48 oscillator power<br>consumption                                              |                        | -                   | 330  | 380 <sup>(2)</sup> | μA   |  |

1.  $V_{DDA}$  = 3.3 V,  $T_A$  = -40 to 125 °C unless otherwise specified.

2. Guaranteed by design.

3. Guaranteed by characterization results.

## Low-speed internal (LSI) RC oscillator

#### Table 48. LSI oscillator characteristics

| Symbol                              | Parameter                                                               | Min | Тур | Max | Unit |

|-------------------------------------|-------------------------------------------------------------------------|-----|-----|-----|------|

| f <sub>LSI</sub> <sup>(1)</sup>     | LSI frequency                                                           | 26  | 38  | 56  | kHz  |

| D <sub>LSI</sub> <sup>(2)</sup>     | LSI oscillator frequency drift $0^{\circ}C \leq T_{A} \leq 85^{\circ}C$ | -10 | -   | 4   | %    |

| t <sub>su(LSI)</sub> <sup>(3)</sup> | LSI oscillator startup time                                             | -   | -   | 200 | μs   |

| I <sub>DD(LSI)</sub> <sup>(3)</sup> | LSI oscillator power consumption                                        | -   | 400 | 510 | nA   |

1. Guaranteed by test in production.

2. This is a deviation for an individual part, once the initial frequency has been measured.

3. Guaranteed by design.

## Multi-speed internal (MSI) RC oscillator

#### Table 49. MSI oscillator characteristics

| Symbol           | Parameter                                                                                | Condition   | Тур  | Max | Unit |

|------------------|------------------------------------------------------------------------------------------|-------------|------|-----|------|

|                  |                                                                                          | MSI range 0 | 65.5 | -   |      |

|                  |                                                                                          | MSI range 1 | 131  | -   | kHz  |

|                  | Frequency after factory calibration, done at $V_{DD}$ = 3.3 V and T <sub>A</sub> = 25 °C | MSI range 2 | 262  | -   | КПИ  |

| f <sub>MSI</sub> |                                                                                          | MSI range 3 | 524  | -   |      |

|                  |                                                                                          | MSI range 4 | 1.05 | -   |      |

|                  |                                                                                          | MSI range 5 | 2.1  | -   | MHz  |

|                  |                                                                                          | MSI range 6 | 4.2  | -   |      |

| Symbol                    | Parameter                                            | Conditions                                                                                            | Min | Тур          | Мах          | Unit  |

|---------------------------|------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-----|--------------|--------------|-------|

| DNL <sup>(2)</sup>        | Differential non linearity <sup>(4)</sup>            | $C_{L} \le 50 \text{ pF}, R_{L} \ge 5 \text{ k}\Omega$<br>DAC output buffer ON                        | -   | 1.5          | 3            |       |

|                           |                                                      | No $R_{LOAD}$ , $C_{L} \le 50 \text{ pF}$<br>DAC output buffer OFF                                    | -   | 1.5          | 3            |       |

| INL <sup>(2)</sup>        | Integral non linearity <sup>(5)</sup>                | $C_L \le 50 \text{ pF}, R_L \ge 5 \text{ k}\Omega$<br>DAC output buffer ON                            | -   | 2            | 4            |       |

|                           | integral non intearity ??                            | No $R_{LOAD}$ , $C_{L} \le 50 \text{ pF}$<br>DAC output buffer OFF                                    | -   | 2            | 4            | LSB   |

| Offset <sup>(2)</sup>     | Offset error at code 0x800 <sup>(6)</sup>            | $C_L \le 50 \text{ pF}, R_L \ge 5 \text{ k}\Omega$<br>DAC output buffer ON                            | -   | ±10          | ±25          |       |

| Oliset                    |                                                      | No $R_{LOAD}$ , $C_{L} \le 50 \text{ pF}$<br>DAC output buffer OFF                                    | -   | ±5           | ±8           |       |

| Offset1 <sup>(2)</sup>    | Offset error at code 0x001 <sup>(7)</sup>            | No $R_{LOAD}$ , $C_{L} \le 50 \text{ pF}$<br>DAC output buffer OFF                                    | -   | ±1.5         | ±5           |       |

|                           | Offset error temperature<br>coefficient (code 0x800) | $V_{DDA} = 3.3V$<br>$V_{REF+} = 3.0 V$<br>$T_A = 0 \text{ to } 50 ^{\circ}C$<br>DAC output buffer OFF | -20 | -10          | 0            |       |

| dOffset/dT <sup>(2)</sup> |                                                      | $V_{DDA} = 3.3V$<br>$V_{REF+} = 3.0 V$<br>$T_A = 0 \text{ to } 50 ^{\circ} C$<br>DAC output buffer ON | 0   | 20           | 50           | µV/°C |

| Gain <sup>(2)</sup>       | Cain arrar <sup>(8)</sup>                            | $C_L \le 50 \text{ pF}, R_L \ge 5 \text{ k}\Omega$<br>DAC output buffer ON                            | -   | +0.1 / -0.2% | +0.2 / -0.5% | %     |

| Gain                      | Gain error <sup>(8)</sup>                            | No $R_{LOAD}$ , $C_{L} \le 50 \text{ pF}$<br>DAC output buffer OFF                                    | -   | +0 / -0.2%   | +0 / -0.4%   | 70    |

| dGain/dT <sup>(2)</sup>   | Gain error temperature<br>coefficient                | $V_{DDA} = 3.3V$<br>$V_{REF+} = 3.0 V$<br>$T_A = 0 \text{ to } 50 \degree C$<br>DAC output buffer OFF | -10 | -2           | 0            |       |

| dGain/d i <sup>v=</sup>   |                                                      | $V_{DDA} = 3.3V$<br>$V_{REF+} = 3.0 V$<br>$T_A = 0 \text{ to } 50 \degree C$<br>DAC output buffer ON  | -40 | -8           | 0            | μV/°C |

| TUE <sup>(2)</sup>        | Tatal un adiusta d'arras                             | $C_L \le 50 \text{ pF}, R_L \ge 5 \text{ k}\Omega$<br>DAC output buffer ON                            | -   | 12           | 30           |       |

|                           | Total unadjusted error                               | No $R_{LOAD}$ , $C_{L} \le 50 \text{ pF}$<br>DAC output buffer OFF                                    | -   | 8            | 12           | LSB   |

## Table 66. DAC characteristics (continued)

## 6.3.17 Temperature sensor characteristics

| Calibration value name | Description                                                               | Memory address            |  |  |  |  |  |

|------------------------|---------------------------------------------------------------------------|---------------------------|--|--|--|--|--|

| TS_CAL1                | TS ADC raw data acquired at temperature of 30 °C, V <sub>DDA</sub> = 3 V  | 0x1FF8 007A - 0x1FF8 007B |  |  |  |  |  |

| TS_CAL2                | TS ADC raw data acquired at temperature of 130 °C, V <sub>DDA</sub> = 3 V | 0x1FF8 007E - 0x1FF8 007F |  |  |  |  |  |

Table 67. Temperature sensor calibration values

Table 68. Temperature sensor characteristics

| Symbol                                | Parameter                                      | Min  | Тур  | Max  | Unit  |

|---------------------------------------|------------------------------------------------|------|------|------|-------|

| T <sub>L</sub> <sup>(1)</sup>         | V <sub>SENSE</sub> linearity with temperature  | -    | ±1   | ±2   | °C    |

| Avg_Slope <sup>(1)</sup>              | Average slope                                  | 1.48 | 1.61 | 1.75 | mV/°C |

| V <sub>130</sub>                      | Voltage at 130°C ±5°C <sup>(2)</sup>           | 640  | 670  | 700  | mV    |

| I <sub>DDA(TEMP)</sub> <sup>(3)</sup> | Current consumption                            | -    | 3.4  | 6    | μA    |

| t <sub>START</sub> <sup>(3)</sup>     | Startup time                                   | -    | -    | 10   |       |

| T <sub>S_temp</sub> <sup>(4)(3)</sup> | ADC sampling time when reading the temperature | 10   | -    | -    | μs    |

1. Guaranteed by characterization results.

2. Measured at V\_{DD} = 3 V  $\pm$ 10 mV. V130 ADC conversion result is stored in the TS\_CAL2 byte.

3. Guaranteed by design.

4. Shortest sampling time can be determined in the application by multiple iterations.

## 6.3.18 Comparators

| Symbol                   | Parameter                                                      | Conditions                                                                                                                                                | Min <sup>(1)</sup> | Тур | Max <sup>(1)</sup> | Unit      |

|--------------------------|----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|--------------------|-----------|

| Gymbol                   | i arameter                                                     | Conditions                                                                                                                                                |                    | чур | Max                | Onit      |

| $V_{DDA}$                | Analog supply voltage                                          | -                                                                                                                                                         | 1.65               |     | 3.6                | V         |

| R <sub>400K</sub>        | R <sub>400K</sub> value                                        | -                                                                                                                                                         | -                  | 400 | -                  | kΩ        |

| R <sub>10K</sub>         | R <sub>10K</sub> value                                         | -                                                                                                                                                         | -                  | 10  | -                  | 122       |

| V <sub>IN</sub>          | Comparator 1 input voltage range                               | -                                                                                                                                                         | 0.6                | -   | V <sub>DDA</sub>   | V         |

| t <sub>START</sub>       | Comparator startup time                                        | -                                                                                                                                                         | -                  | 7   | 10                 | 110       |

| td                       | Propagation delay <sup>(2)</sup>                               | -                                                                                                                                                         | -                  | 3   | 10                 | μs        |

| Voffset                  | Comparator offset                                              | -                                                                                                                                                         | -                  | ±3  | ±10                | mV        |

| d <sub>Voffset</sub> /dt | Comparator offset variation in worst voltage stress conditions | $\label{eq:VDDA} \begin{split} V_{DDA} &= 3.6 \text{ V},  V_{IN+} = 0 \text{ V}, \\ V_{IN-} &= V_{REFINT},  T_A \text{ = } 25 ^\circ\text{C} \end{split}$ | 0                  | 1.5 | 10                 | mV/1000 h |

| I <sub>COMP1</sub>       | Current consumption <sup>(3)</sup>                             | -                                                                                                                                                         | -                  | 160 | 260                | nA        |

#### Table 69. Comparator 1 characteristics

1. Guaranteed by characterization.

2. The delay is characterized for 100 mV input step with 10 mV overdrive on the inverting input, the non-inverting input set to the reference.

3. Comparator consumption only. Internal reference voltage not included.

| Symbol              | Parameter                                     | Conditions                                                                                                                                                                                                                                             | Min  | Тур | Max <sup>(1)</sup> | Unit       |

|---------------------|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|--------------------|------------|

| V <sub>DDA</sub>    | Analog supply voltage                         | -                                                                                                                                                                                                                                                      | 1.65 | -   | 3.6                | V          |

| V <sub>IN</sub>     | Comparator 2 input voltage range              | -                                                                                                                                                                                                                                                      | 0    | -   | V <sub>DDA</sub>   | V          |

| +                   | Comparator startup time                       | Fast mode                                                                                                                                                                                                                                              | -    | 15  | 20                 |            |

| t <sub>START</sub>  |                                               | Slow mode                                                                                                                                                                                                                                              | -    | 20  | 25                 |            |

| +                   | Propagation delay <sup>(2)</sup> in slow mode | 1.65 V ≤V <sub>DDA</sub> ≤2.7 V                                                                                                                                                                                                                        | -    | 1.8 | 3.5                |            |

| t <sub>d slow</sub> | Propagation delay. <sup>-,</sup> in slow mode | 2.7 V ≤V <sub>DDA</sub> ≤3.6 V                                                                                                                                                                                                                         | -    | 2.5 | 6                  | μs         |

| +                   | Propagation delay <sup>(2)</sup> in fast mode | 1.65 V ≤V <sub>DDA</sub> ≤2.7 V                                                                                                                                                                                                                        | -    | 0.8 | 2                  |            |

| t <sub>d fast</sub> | riopagation delay fin last mode               | 2.7 V ≤V <sub>DDA</sub> ≤3.6 V                                                                                                                                                                                                                         | -    | 1.2 | 4                  |            |

| V <sub>offset</sub> | Comparator offset error                       |                                                                                                                                                                                                                                                        | -    | ±4  | <u>+</u> 20        | mV         |

| dThreshold/<br>dt   | Threshold voltage temperature coefficient     | $\label{eq:VDDA} \begin{split} &V_{DDA} = 3.3 \text{V},  \text{T}_{\text{A}} = 0 \text{ to } 50 \ ^{\circ}\text{C}, \\ &V- = V_{\text{REFINT}}, \\ &3/4 \ &V_{\text{REFINT}}, \\ &1/2 \ &V_{\text{REFINT}}, \\ &1/4 \ &V_{\text{REFINT}}. \end{split}$ | -    | 15  | 30                 | ppm<br>/°C |

|                     | Current consumption <sup>(3)</sup>            | Fast mode                                                                                                                                                                                                                                              | -    | 3.5 | 5                  |            |

| I <sub>COMP2</sub>  |                                               | Slow mode                                                                                                                                                                                                                                              | -    | 0.5 | 2                  | μA         |

Table 70. Comparator 2 characteristics

1. Guaranteed by characterization results.

2. The delay is characterized for 100 mV input step with 10 mV overdrive on the inverting input, the non-inverting input set to the reference.

3. Comparator consumption only. Internal reference voltage (required for comparator operation) is not included.

## 6.3.19 Timer characteristics

#### **TIM timer characteristics**

The parameters given in the Table 71 are guaranteed by design.

Refer to Section 6.3.13: I/O port characteristics for details on the input/output alternate function characteristics (output compare, input capture, external clock, PWM output).

| Symbol                 | Parameter                                               | Conditions                    | Min    | Max                     | Unit                 |  |  |  |  |

|------------------------|---------------------------------------------------------|-------------------------------|--------|-------------------------|----------------------|--|--|--|--|

| t ann                  | Timer resolution time                                   |                               | 1      | -                       | t <sub>TIMxCLK</sub> |  |  |  |  |

| <sup>t</sup> res(TIM)  |                                                         | f <sub>TIMxCLK</sub> = 32 MHz | 31.25  | -                       | ns                   |  |  |  |  |

| f <sub>EXT</sub>       | Timer external clock frequency on CH1                   |                               | 0      | f <sub>TIMxCLK</sub> /2 | MHz                  |  |  |  |  |

|                        | to CH4                                                  | f <sub>TIMxCLK</sub> = 32 MHz | 0      | 16                      | MHz                  |  |  |  |  |

| Res <sub>TIM</sub>     | Timer resolution                                        | -                             |        | 16                      | bit                  |  |  |  |  |

|                        | 16-bit counter clock period when                        | -                             | 1      | 65536                   | t <sub>TIMxCLK</sub> |  |  |  |  |

| <sup>t</sup> COUNTER   | internal clock is selected (timer's prescaler disabled) | f <sub>TIMxCLK</sub> = 32 MHz | 0.0312 | 2048                    | μs                   |  |  |  |  |

| t <sub>MAX_COUNT</sub> | Maximum possible count                                  | -                             | -      | 65536 × 65536           | t <sub>TIMxCLK</sub> |  |  |  |  |

|                        |                                                         | f <sub>TIMxCLK</sub> = 32 MHz | -      | 134.2                   | S                    |  |  |  |  |

Table 71. TIMx characteristics<sup>(1)</sup>

1. TIMx is used as a general term to refer to the TIM2, TIM6, TIM21, and TIM22 timers.

## 6.3.20 Communications interfaces

## I<sup>2</sup>C interface characteristics

The  $I^2C$  interface meets the timings requirements of the  $I^2C$ -bus specification and user manual rev. 03 for:

- Standard-mode (Sm) : with a bit rate up to 100 kbit/s

- Fast-mode (Fm) : with a bit rate up to 400 kbit/s

- Fast-mode Plus (Fm+) : with a bit rate up to 1 Mbit/s.

The I<sup>2</sup>C timing requirements are guaranteed by design when the I<sup>2</sup>C peripheral is properly configured (refer to the reference manual for details). The SDA and SCL I/O requirements are met with the following restrictions: the SDA and SCL I/O pins are not "true" open-drain. When configured as open-drain, the PMOS connected between the I/O pin and VDDIOx is disabled, but is still present. Only FTf I/O pins support Fm+ low level output current maximum requirement (refer to *Section 6.3.13: I/O port characteristics* for the I2C I/Os characteristics).

All I<sup>2</sup>C SDA and SCL I/Os embed an analog filter (see *Table 72* for the analog filter characteristics).

#### **I2S** characteristics

| Symbol                 | Parameter                      | Conditions                             | Min      | Мах                   | Unit  |

|------------------------|--------------------------------|----------------------------------------|----------|-----------------------|-------|

| f <sub>MCK</sub>       | I2S Main clock output          | -                                      | 256 x 8K | 256xFs <sup>(2)</sup> | MHz   |

| f                      | 125 alook froguopov            | Master data: 32 bits                   | -        | 64xFs                 | MHz   |

| f <sub>CK</sub>        | I2S clock frequency            | Slave data: 32 bits                    | -        | 64xFs                 | IVITZ |

| D <sub>CK</sub>        | I2S clock frequency duty cycle | Slave receiver                         | 30       | 70                    | %     |

| t <sub>v(WS)</sub>     | WS valid time                  | Master mode                            | -        | 15                    |       |

| t <sub>h(WS)</sub>     | WS hold time                   | Master mode                            | 11       | -                     |       |

| t <sub>su(WS)</sub>    | WS setup time                  | Slave mode                             | 6        | -                     |       |

| t <sub>h(WS)</sub>     | WS hold time                   | Slave mode                             | 2        | -                     |       |

| t <sub>su(SD_MR)</sub> | Data input setup time          | Master receiver                        | 0        | -                     |       |

| t <sub>su(SD_SR)</sub> | Data input setup time          | Slave receiver                         | 6.5      | -                     | ns    |

| t <sub>h(SD_MR)</sub>  | Data input hold time           | Master receiver                        | 18       | -                     | 115   |

| t <sub>h(SD_SR)</sub>  |                                | Slave receiver                         | 15.5     | -                     |       |

| t <sub>v(SD_ST)</sub>  | Data output valid time         | Slave transmitter (after enable edge)  | -        | 77                    |       |

| t <sub>v(SD_MT)</sub>  |                                | Master transmitter (after enable edge) | -        | 8                     |       |

| t <sub>h(SD_ST)</sub>  | Data output hold time          | Slave transmitter (after enable edge)  | 18       | -                     |       |

| t <sub>h(SD_MT)</sub>  | Data output hold time          | Master transmitter (after enable edge) | 1.5      | -                     |       |

#### Table 77. I2S characteristics<sup>(1)</sup>

1. Guaranteed by characterization results.

2. 256xFs maximum value is equal to the maximum clock frequency.

Note: Refer to the I2S section of the product reference manual for more details about the sampling frequency (Fs),  $f_{MCK}$ ,  $f_{CK}$  and  $D_{CK}$  values. These values reflect only the digital peripheral behavior, source clock precision might slightly change them. DCK depends mainly on the ODD bit value, digital contribution leads to a min of (I2SDIV/(2\*I2SDIV+ODD) and a max of (I2SDIV+ODD)/(2\*I2SDIV+ODD). Fs max is supported for each mode/condition.

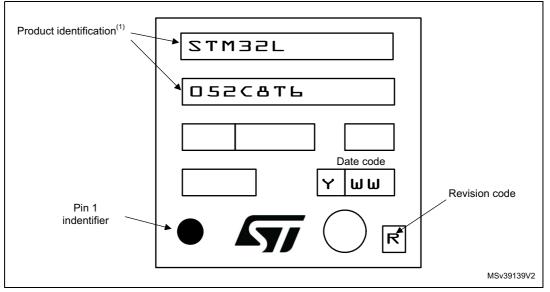

#### **Device marking for LQFP48**

The following figure gives an example of topside marking versus pin 1 position identifier location.

Other optional marking or inset/upset marks, which depend on supply chain operations, are not indicated below.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

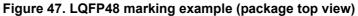

| Symbol | millimeters |       |       | inches <sup>(1)</sup> |        |        |  |  |  |

|--------|-------------|-------|-------|-----------------------|--------|--------|--|--|--|

|        | Min         | Тур   | Max   | Min                   | Тур    | Мах    |  |  |  |

| А      | 0.500       | 0.550 | 0.600 | 0.0197                | 0.0217 | 0.0236 |  |  |  |

| A1     | 0.000       | 0.020 | 0.050 | 0.0000                | 0.0008 | 0.0020 |  |  |  |

| A3     | -           | 0.152 | -     | -                     | 0.0060 | -      |  |  |  |

| b      | 0.180       | 0.230 | 0.280 | 0.0071                | 0.0091 | 0.0110 |  |  |  |

| D      | 4.900       | 5.000 | 5.100 | 0.1929                | 0.1969 | 0.2008 |  |  |  |

| D1     | 3.400       | 3.500 | 3.600 | 0.1339                | 0.1378 | 0.1417 |  |  |  |

| D2     | 3.400       | 3.500 | 3.600 | 0.1339                | 0.1378 | 0.1417 |  |  |  |

| E      | 4.900       | 5.000 | 5.100 | 0.1929                | 0.1969 | 0.2008 |  |  |  |

| E1     | 3.400       | 3.500 | 3.600 | 0.1339                | 0.1378 | 0.1417 |  |  |  |

| E2     | 3.400       | 3.500 | 3.600 | 0.1339                | 0.1378 | 0.1417 |  |  |  |

| е      | -           | 0.500 | -     | -                     | 0.0197 | -      |  |  |  |

| L      | 0.300       | 0.400 | 0.500 | 0.0118                | 0.0157 | 0.0197 |  |  |  |

| ddd    | -           | -     | 0.080 | -                     | -      | 0.0031 |  |  |  |

# Table 90. UFQFPN32 - 32-pin, 5x5 mm, 0.5 mm pitch ultra thin fine pitch quad flatpackage mechanical data

1. Values in inches are converted from mm and rounded to 4 decimal digits.

1. Dimensions are expressed in millimeters.

## 7.8 Thermal characteristics

The maximum chip-junction temperature,  $T_{\rm J}$  max, in degrees Celsius, may be calculated using the following equation:

$T_J \max = T_A \max + (P_D \max \times \Theta_{JA})$

Where:

- T<sub>A</sub> max is the maximum ambient temperature in °C,

- $\Theta_{JA}$  is the package junction-to-ambient thermal resistance, in ° C/W,

- P<sub>D</sub> max is the sum of P<sub>INT</sub> max and P<sub>I/O</sub> max (P<sub>D</sub> max = P<sub>INT</sub> max + P<sub>I/O</sub>max),

- P<sub>INT</sub> max is the product of I<sub>DD</sub> and V<sub>DD</sub>, expressed in Watts. This is the maximum chip internal power.

$P_{I/O}$  max represents the maximum power dissipation on output pins where:

$\mathsf{P}_{\mathsf{I}/\mathsf{O}} \max = \Sigma \; (\mathsf{V}_{\mathsf{OL}} \times \mathsf{I}_{\mathsf{OL}}) + \Sigma ((\mathsf{V}_{\mathsf{DD}} - \mathsf{V}_{\mathsf{OH}}) \times \mathsf{I}_{\mathsf{OH}}),$

taking into account the actual V\_{OL} / I\_{OL} and V\_{OH} / I\_{OH} of the I/Os at low and high level in the application.

| Symbol | Parameter                                                                 | Value | Unit |

|--------|---------------------------------------------------------------------------|-------|------|

| ΘjA    | Thermal resistance junction-ambient<br>TFBGA64 - 5 x 5 mm / 0.5 mm pitch  | 61    | °C/W |

|        | Thermal resistance junction-ambient<br>LQFP64 - 10 x 10 mm / 0.5 mm pitch | 45    |      |

|        | Thermal resistance junction-ambient<br>Standard WLCSP36 - 0.4 mm pitch    | 63    |      |

|        | Thermal resistance junction-ambient<br>Thin WLCSP36 - 0.4 mm pitch        | 59    |      |

|        | Thermal resistance junction-ambient<br>LQFP48 - 7 x 7 mm / 0.5 mm pitch   | 55    |      |

|        | Thermal resistance junction-ambient<br>LQFP32 - 7 x 7 mm / 0.8 mm pitch   | 57    |      |

|        | Thermal resistance junction-ambient<br>UFQFPN32 - 5 x 5 mm / 0.5 mm pitch | 38    |      |

| Table 91. Thermal characteris | stics |

|-------------------------------|-------|

|-------------------------------|-------|

#### IMPORTANT NOTICE - PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2017 STMicroelectronics – All rights reserved

DocID025936 Rev 7