Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                        |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 32MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART, USB                            |

| Peripherals                | Brown-out Detect/Reset, DMA, I2S, POR, PWM, WDT                         |

| Number of I/O              | 29                                                                      |

| Program Memory Size        | 64KB (64K x 8)                                                          |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 2K x 8                                                                  |

| RAM Size                   | 8K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 3.6V                                                            |

| Data Converters            | A/D 16x12b; D/A 1x12b                                                   |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 36-UFBGA, WLCSP                                                         |

| Supplier Device Package    | 36-WLCSP (2.61x2.88)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l052t8y7tr |

Table 5. Functionalities depending on the working mode (from Run/active down to standby) <sup>(1)</sup>

|                                           |            |       | Low-         | Low-           |                  | Stop                 | 5 | Standby           |

|-------------------------------------------|------------|-------|--------------|----------------|------------------|----------------------|---|-------------------|

| IPs                                       | Run/Active | Sleep | power<br>run | power<br>sleep |                  | Wakeup<br>capability |   | Wakeup capability |

| CPU                                       | Υ          |       | Y            |                |                  |                      |   |                   |

| Flash memory                              | 0          | 0     | 0            | 0              |                  |                      | ı |                   |

| RAM                                       | Υ          | Y     | Y            | Y              | Υ                |                      | - |                   |

| Backup registers                          | Υ          | Y     | Y            | Y              | Υ                |                      | Υ |                   |

| EEPROM                                    | 0          | 0     | 0            | 0              |                  |                      |   |                   |

| Brown-out reset (BOR)                     | 0          | 0     | 0            | 0              | 0                | 0                    | 0 | 0                 |

| DMA                                       | 0          | 0     | 0            | 0              |                  |                      | - |                   |

| Programmable<br>Voltage Detector<br>(PVD) | 0          | 0     | 0            | 0              | 0                | 0                    | - |                   |

| Power-on/down<br>reset (POR/PDR)          | Y          | Y     | Y            | Y              | Υ                | Y                    | Υ | Y                 |

| High Speed<br>Internal (HSI)              | 0          | 0     |              |                | (2)              |                      |   |                   |

| High Speed<br>External (HSE)              | 0          | 0     | 0            | 0              |                  |                      |   |                   |

| Low Speed Internal (LSI)                  | 0          | 0     | 0            | 0              | 0                |                      | 0 |                   |

| Low Speed<br>External (LSE)               | 0          | 0     | 0            | 0              | 0                |                      | 0 |                   |

| Multi-Speed<br>Internal (MSI)             | 0          | 0     | Y            | Y              |                  |                      |   |                   |

| Inter-Connect<br>Controller               | Y          | Y     | Y            | Y              | Υ                |                      |   |                   |

| RTC                                       | 0          | 0     | 0            | 0              | 0                | 0                    | 0 |                   |

| RTC Tamper                                | 0          | 0     | 0            | 0              | 0                | 0                    | 0 | 0                 |

| Auto WakeUp<br>(AWU)                      | 0          | 0     | 0            | 0              | 0                | 0                    | 0 | 0                 |

| USB                                       | 0          | 0     |              |                |                  | 0                    | 1 |                   |

| USART                                     | 0          | 0     | 0            | 0              | O <sup>(3)</sup> | 0                    | ł |                   |

| LPUART                                    | 0          | 0     | 0            | 0              | O <sup>(3)</sup> | 0                    | 1 |                   |

| SPI                                       | 0          | 0     | 0            | 0              |                  |                      | - |                   |

| I2C                                       | 0          | 0     | 0            | 0              | O <sup>(4)</sup> | 0                    | - |                   |

| ADC                                       | 0          | 0     |              |                |                  |                      | 1 |                   |

| DAC                                       | 0          | 0     | 0            | 0              | 0                |                      | - |                   |

| SPI features <sup>(1)</sup> | SPI1 | SPI2 |  |  |  |  |  |  |

|-----------------------------|------|------|--|--|--|--|--|--|

| Hardware CRC calculation    | Х    | Х    |  |  |  |  |  |  |

| I2S mode                    | -    | Х    |  |  |  |  |  |  |

| TI mode                     | Х    | Х    |  |  |  |  |  |  |

Table 14. SPI/I2S implementation

### 3.18.5 Universal serial bus (USB)

The STM32L052x6/8 embed a full-speed USB device peripheral compliant with the USB specification version 2.0. The internal USB PHY supports USB FS signaling, embedded DP pull-up and also battery charging detection according to Battery Charging Specification Revision 1.2. The USB interface implements a full-speed (12 Mbit/s) function interface with added support for USB 2.0 Link Power Management. It has software-configurable endpoint setting with packet memory up to 1 KB and suspend/resume support. It requires a precise 48 MHz clock which can be generated from the internal main PLL (the clock source must use a HSE crystal oscillator) or by the internal 48 MHz oscillator in automatic trimming mode. The synchronization for this oscillator can be taken from the USB data stream itself (SOF signalization) which allows crystal-less operation.

## 3.19 Clock recovery system (CRS)

The STM32L052x6/8 embed a special block which allows automatic trimming of the internal 48 MHz oscillator to guarantee its optimal accuracy over the whole device operational range. This automatic trimming is based on the external synchronization signal, which could be either derived from USB SOF signalization, from LSE oscillator, from an external signal on CRS\_SYNC pin or generated by user software. For faster lock-in during startup it is also possible to combine automatic trimming with manual trimming action.

# 3.20 Cyclic redundancy check (CRC) calculation unit

The CRC (cyclic redundancy check) calculation unit is used to get a CRC code using a configurable generator polynomial value and size.

Among other applications, CRC-based techniques are used to verify data transmission or storage integrity. In the scope of the EN/IEC 60335-1 standard, they offer a means of verifying the Flash memory integrity. The CRC calculation unit helps compute a signature of the software during runtime, to be compared with a reference signature generated at linktime and stored at a given memory location.

# 3.21 Serial wire debug port (SW-DP)

An ARM SW-DP interface is provided to allow a serial wire debugging tool to be connected to the MCU.

<sup>1.</sup> X = supported.

# 4 Pin descriptions

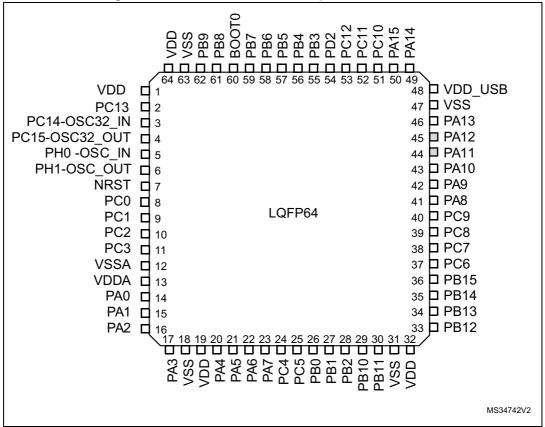

Figure 3. STM32L052x6/8 LQFP64 pinout - 10 x 10 mm

- 1. The above figure shows the package top view.

- 2. I/O pin supplied by VDD\_USB.

5//

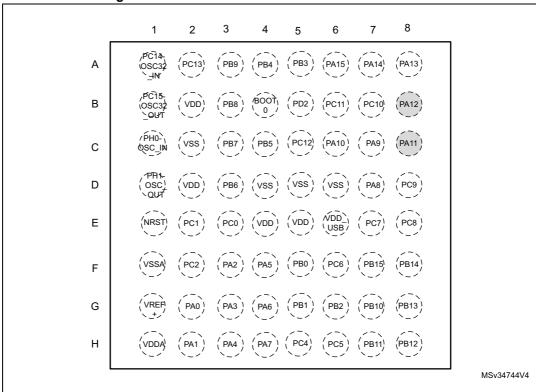

Figure 4. STM32L052x6/8 TFBGA64 ballout - 5x 5 mm

<sup>1.</sup> The above figure shows the package top view.

<sup>2.</sup> I/O pin supplied by VDD\_USB.

### 6 Electrical characteristics

### 6.1 Parameter conditions

Unless otherwise specified, all voltages are referenced to V<sub>SS</sub>.

### 6.1.1 Minimum and maximum values

Unless otherwise specified the minimum and maximum values are guaranteed in the worst conditions of ambient temperature, supply voltage and frequencies by tests in production on 100% of the devices with an ambient temperature at  $T_A = 25$  °C and  $T_A = T_A$ max (given by the selected temperature range).

Data based on characterization results, design simulation and/or technology characteristics are indicated in the table footnotes and are not tested in production. Based on characterization, the minimum and maximum values refer to sample tests and represent the mean value plus or minus three times the standard deviation (mean±3 $\sigma$ ).

### 6.1.2 Typical values

Unless otherwise specified, typical data are based on  $T_A$  = 25 °C,  $V_{DD}$  = 3.6 V (for the 1.65 V  $\leq$ V $_{DD}$   $\leq$ 3.6 V voltage range). They are given only as design guidelines and are not tested.

Typical ADC accuracy values are determined by characterization of a batch of samples from a standard diffusion lot over the full temperature range, where 95% of the devices have an error less than or equal to the value indicated (mean $\pm 2\sigma$ ).

### 6.1.3 Typical curves

Unless otherwise specified, all typical curves are given only as design guidelines and are not tested.

### 6.1.4 Loading capacitor

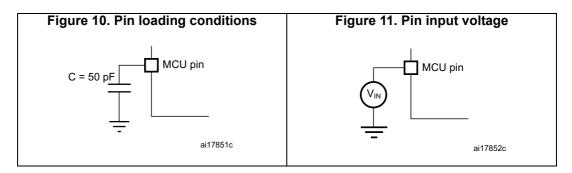

The loading conditions used for pin parameter measurement are shown in *Figure 10*.

### 6.1.5 Pin input voltage

The input voltage measurement on a pin of the device is described in Figure 11.

# 6.3 Operating conditions

## 6.3.1 General operating conditions

Table 25. General operating conditions

| Symbol             | Parameter                                                                                               | Conditions                                                 | Min  | Max                  | Unit  |  |

|--------------------|---------------------------------------------------------------------------------------------------------|------------------------------------------------------------|------|----------------------|-------|--|

| f <sub>HCLK</sub>  | Internal AHB clock frequency                                                                            | -                                                          | 0    | 32                   |       |  |

| f <sub>PCLK1</sub> | Internal APB1 clock frequency                                                                           | -                                                          | 0    | 32                   | MHz   |  |

| f <sub>PCLK2</sub> | Internal APB2 clock frequency                                                                           | -                                                          | 0    | 32                   |       |  |

|                    |                                                                                                         | BOR detector disabled                                      | 1.65 | 3.6                  |       |  |

| $V_{DD}$           | Standard operating voltage                                                                              | BOR detector enabled, at power-on                          | 1.8  | 3.6                  | V     |  |

|                    |                                                                                                         | BOR detector disabled, after power-on                      | 1.65 | 3.6                  |       |  |

| V <sub>DDA</sub>   | Analog operating voltage (DAC not used)                                                                 | Must be the same voltage as V <sub>DD</sub> <sup>(1)</sup> | 1.65 | 3.6                  | V     |  |

| $V_{DDA}$          | Analog operating voltage (all features)                                                                 | Must be the same voltage as V <sub>DD</sub> <sup>(1)</sup> | 1.8  | 3.6                  | V     |  |

| V <sub>DD_US</sub> | Standard operating voltage, USB                                                                         | USB peripheral used                                        | 3.0  | 3.6                  | V     |  |

| В                  | domain <sup>(2)</sup>                                                                                   | USB peripheral not used                                    | 1.65 | 3.6                  | ] V   |  |

|                    | Input voltage on FT, FTf and RST                                                                        | 2.0 V ≤V <sub>DD</sub> ≤3.6 V                              | -0.3 | 5.5                  |       |  |

| V                  | pins <sup>(3)</sup>                                                                                     | 1.65 V ≤V <sub>DD</sub> ≤2.0 V                             | -0.3 | 5.2                  | V     |  |

| $V_{IN}$           | Input voltage on BOOT0 pin                                                                              | -                                                          | 0    | 5.5                  | ]     |  |

|                    | Input voltage on TC pin                                                                                 | -                                                          | -0.3 | V <sub>DD</sub> +0.3 |       |  |

|                    |                                                                                                         | TFBGA64 package                                            | -    | 327                  |       |  |

|                    |                                                                                                         | LQFP64 package                                             | -    | 444                  | _     |  |

|                    |                                                                                                         | LQFP48 package                                             | -    | 363                  | 1     |  |

|                    | Power dissipation at T <sub>A</sub> = 85 °C (range 6) or T <sub>A</sub> =105 °C (rage 7) <sup>(4)</sup> | Standard WLCSP36 package                                   | -    | 318                  |       |  |

|                    |                                                                                                         | Thin WLCSP36 package                                       | -    | 338                  |       |  |

|                    |                                                                                                         | LQFP32 package                                             | -    | 351                  |       |  |

| $P_{D}$            |                                                                                                         | UFQFPN32                                                   | -    | 526                  | mW    |  |

| ' D                |                                                                                                         | TFBGA64 package                                            | -    | 81                   | 11100 |  |

|                    |                                                                                                         | LQFP64 package                                             | -    | 111                  |       |  |

|                    | D " ' " ' T 405 00                                                                                      | LQFP48 package                                             | -    | 91                   |       |  |

|                    | Power dissipation at T <sub>A</sub> = 125 °C (range 3) <sup>(4)</sup>                                   | Standard WLCSP36 package                                   | -    | 79                   |       |  |

|                    |                                                                                                         | Thin WLCSP36 package                                       | -    | 84                   |       |  |

|                    |                                                                                                         | LQFP32 package                                             | -    | 88                   | 1     |  |

|                    |                                                                                                         | UFQFPN32                                                   | -    | 132                  |       |  |

IDD (mA) 3.50E-02 3.00E-02 1.50E-02 1.00E-02 5.00E-03 VDD (V) 1.80 2.00 2.20 2.40 2.60 2.80 3.00 3.20 3.40 3.60 0 WS - 85°C 0 WS - 125°C MSv34794V3

Figure 16.  $I_{DD}$  vs  $V_{DD}$ , at  $T_A$ = 25/55/ 85/105/125 °C, Low-power run mode, code running from RAM, Range 3, MSI (Range 0) at 64 KHz, 0 WS

Table 35. Current consumption in Low-power sleep mode

| Symbol     | Parameter  | Conditions   |                                                                 |                                            | Тур                | Max <sup>(1)</sup> | Unit |

|------------|------------|--------------|-----------------------------------------------------------------|--------------------------------------------|--------------------|--------------------|------|

|            |            |              | MSI clock = 65 kHz,<br>f <sub>HCLK</sub> = 32 kHz,<br>Flash OFF | T <sub>A</sub> = -40 to 25°C               | 4.7 <sup>(2)</sup> | -                  |      |

|            |            |              |                                                                 | $T_A = -40 \text{ to } 25^{\circ}\text{C}$ | 17                 | 23                 |      |

|            |            |              | MSI clock = 65 kHz,                                             | T <sub>A</sub> = 85 °C                     | 19.5               | 63                 |      |

|            |            |              | f <sub>HCLK</sub> = 32 kHz,<br>Flash ON                         | T <sub>A</sub> = 105 °C                    | 23                 | 69                 |      |

|            |            | 1 10510.30 V |                                                                 | T <sub>A</sub> = 125 °C                    | 32.5               | 90                 |      |

|            |            |              | MSI clock =65 kHz,<br>f <sub>HCLK</sub> = 65 kHz,<br>Flash ON   | $T_A = -40 \text{ to } 25^{\circ}\text{C}$ | 17                 | 23                 |      |

| (LP Sleep) | Low-power  |              |                                                                 | T <sub>A</sub> = 85 °C                     | 20                 | 63                 | μΑ   |

|            | sleep mode |              |                                                                 | T <sub>A</sub> = 105 °C                    | 23.5               | 69                 |      |

|            |            |              |                                                                 | T <sub>A</sub> = 125 °C                    | 32.5               | 90                 |      |

|            |            |              |                                                                 | $T_A = -40 \text{ to } 25^{\circ}\text{C}$ | 19.5               | 36                 |      |

|            |            |              | MSI clock = 131 kHz,                                            | T <sub>A</sub> = 55 °C                     | 20.5               | 64                 |      |

|            |            |              | f <sub>HCLK</sub> = 131 kHz,                                    | T <sub>A</sub> = 85 °C                     | 22.5               | 66                 |      |

|            |            |              | Flash ON                                                        | T <sub>A</sub> = 105 °C                    | 26                 | 72                 |      |

|            |            |              |                                                                 | T <sub>A</sub> = 125 °C                    | 35                 | 95                 |      |

<sup>1.</sup> Guaranteed by characterization results at 125 °C, unless otherwise specified.

<sup>2.</sup> As the CPU is in Sleep mode, the difference between the current consumption with Flash ON and OFF (nearly 12  $\mu$ A) is the same whatever the clock frequency.

| Sumbal                     | Parinharal                   | Typical consum         | ption, T <sub>A</sub> = 25 °C | Unit |

|----------------------------|------------------------------|------------------------|-------------------------------|------|

| Symbol                     | Peripheral                   | V <sub>DD</sub> =1.8 V | V <sub>DD</sub> =3.0 V        |      |

| I <sub>DD(PVD / BOR)</sub> | -                            | 0.7                    | 1.2                           |      |

| I <sub>REFINT</sub>        | -                            | -                      | 1.4                           |      |

| -                          | LSE Low drive <sup>(2)</sup> | 0,1                    | 0,1                           |      |

| -                          | LPTIM1, Input 100 Hz         | 0,01                   | 0,01                          | μΑ   |

| -                          | LPTIM1, Input 1 MHz          | 6                      | 6                             |      |

| -                          | LPUART1                      | 0,2                    | 0,2                           |      |

| -                          | RTC                          | 0,3                    | 0,48                          |      |

Table 40. Peripheral current consumption in Stop and Standby mode<sup>(1)</sup>

### 6.3.5 Wakeup time from low-power mode

The wakeup times given in the following table are measured with the MSI or HSI16 RC oscillator. The clock source used to wake up the device depends on the current operating mode:

- Sleep mode: the clock source is the clock that was set before entering Sleep mode

- Stop mode: the clock source is either the MSI oscillator in the range configured before entering Stop mode, the HSI16 or HSI16/4.

- Standby mode: the clock source is the MSI oscillator running at 2.1 MHz

All timings are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 25*.

Table 41. Low-power mode wakeup timings

| Symbol                  | Parameter                                                        | Conditions                                               | Тур | Max | Unit               |

|-------------------------|------------------------------------------------------------------|----------------------------------------------------------|-----|-----|--------------------|

| t <sub>WUSLEEP</sub>    | Wakeup from Sleep mode                                           | f <sub>HCLK</sub> = 32 MHz                               | 7   | 8   |                    |

| t <sub>WUSLEEP_LP</sub> | Wakeup from Low-power sleep mode,<br>f <sub>HCLK</sub> = 262 kHz | f <sub>HCLK</sub> = 262 kHz<br>Flash memory enabled      | 7   | 8   | Number<br>of clock |

|                         |                                                                  | f <sub>HCLK</sub> = 262 kHz<br>Flash memory switched OFF | 9   | 10  | cycles             |

72/144 DocID025936 Rev 7

<sup>1.</sup> LPTIM peripheral cannot operate in Standby mode.

LSE Low drive consumption is the difference between an external clock on OSC32\_IN and a quartz between OSC32\_IN and OSC32\_OUT.-

Table 41. Low-power mode wakeup timings (continued)

| Symbol               | Parameter                                                                     | Conditions                                                        | Тур | Max | Unit |

|----------------------|-------------------------------------------------------------------------------|-------------------------------------------------------------------|-----|-----|------|

|                      |                                                                               | f <sub>HCLK</sub> = f <sub>MSI</sub> = 4.2 MHz                    | 5.0 | 8   |      |

|                      | Wakeup from Stop mode, regulator in Run mode                                  | f <sub>HCLK</sub> = f <sub>HSI</sub> = 16 MHz                     | 4.9 | 7   |      |

|                      |                                                                               | f <sub>HCLK</sub> = f <sub>HSI</sub> /4 = 4 MHz                   | 8.0 | 11  |      |

|                      |                                                                               | f <sub>HCLK</sub> = f <sub>MSI</sub> = 4.2 MHz<br>Voltage range 1 | 5.0 | 8   |      |

|                      |                                                                               | f <sub>HCLK</sub> = f <sub>MSI</sub> = 4.2 MHz<br>Voltage range 2 | 5.0 | 8   |      |

|                      | Wakeup from Stop mode, regulator in low-power mode                            | f <sub>HCLK</sub> = f <sub>MSI</sub> = 4.2 MHz<br>Voltage range 3 | 5.0 | 8   |      |

|                      |                                                                               | f <sub>HCLK</sub> = f <sub>MSI</sub> = 2.1 MHz                    | 7.3 | 13  | μs   |

| $t_{WUSTOP}$         |                                                                               | f <sub>HCLK</sub> = f <sub>MSI</sub> = 1.05 MHz                   | 13  | 23  |      |

|                      |                                                                               | f <sub>HCLK</sub> = f <sub>MSI</sub> = 524 kHz                    | 28  | 38  |      |

|                      |                                                                               | f <sub>HCLK</sub> = f <sub>MSI</sub> = 262 kHz                    | 51  | 65  |      |

|                      |                                                                               | f <sub>HCLK</sub> = f <sub>MSI</sub> = 131 kHz                    | 100 | 120 |      |

|                      |                                                                               | f <sub>HCLK</sub> = MSI = 65 kHz                                  | 190 | 260 |      |

|                      |                                                                               | f <sub>HCLK</sub> = f <sub>HSI</sub> = 16 MHz                     | 4.9 | 7   |      |

|                      |                                                                               | f <sub>HCLK</sub> = f <sub>HSI</sub> /4 = 4 MHz                   | 8.0 | 11  |      |

|                      |                                                                               | f <sub>HCLK</sub> = f <sub>HSI</sub> = 16 MHz                     | 4.9 | 7   |      |

|                      | Wakeup from Stop mode, regulator in low-<br>power mode, code running from RAM | f <sub>HCLK</sub> = f <sub>HSI</sub> /4 = 4 MHz                   | 7.9 | 10  |      |

|                      |                                                                               | f <sub>HCLK</sub> = f <sub>MSI</sub> = 4.2 MHz                    | 4.7 | 8   |      |

| t                    | Wakeup from Standby mode, FWU bit = 1                                         | f <sub>HCLK</sub> = MSI = 2.1 MHz                                 | 65  | 130 | μs   |

| <sup>t</sup> wustdby | Wakeup from Standby mode, FWU bit = 0                                         | f <sub>HCLK</sub> = MSI = 2.1 MHz                                 | 2.2 | 3   | ms   |

#### 6.3.6 **External clock source characteristics**

### High-speed external user clock generated from an external source

In bypass mode the HSE oscillator is switched off and the input pin is a standard GPIO. The external clock signal has to respect the I/O characteristics in Section 6.3.12. However, the recommended clock input waveform is shown in Figure 19.

Table 42. High-speed external user clock characteristics<sup>(1)</sup>

| Symbol                    | Parameter                           | Conditions                       | Min                | Тур | Max                | Unit |

|---------------------------|-------------------------------------|----------------------------------|--------------------|-----|--------------------|------|

| f                         | User external clock source          | CSS is ON or<br>PLL is used      | 1                  | 8   | 32                 | MHz  |

| f <sub>HSE_ext</sub>      | frequency                           | CSS is OFF,<br>PLL not used      | 0                  | 8   | 32                 | MHz  |

| V <sub>HSEH</sub>         | OSC_IN input pin high level voltage |                                  | 0.7V <sub>DD</sub> | -   | $V_{DD}$           | V    |

| V <sub>HSEL</sub>         | OSC_IN input pin low level voltage  |                                  | $V_{SS}$           | ı   | 0.3V <sub>DD</sub> | V    |

| $t_{w(HSE)} \ t_{w(HSE)}$ | OSC_IN high or low time             |                                  | 12                 | ı   | -                  | ns   |

| t <sub>r(HSE)</sub>       | OSC_IN rise or fall time            | -                                | -                  | -   | 20                 | 113  |

| C <sub>in(HSE)</sub>      | OSC_IN input capacitance            |                                  | -                  | 2.6 | -                  | pF   |

| DuCy <sub>(HSE)</sub>     | Duty cycle                          |                                  | 45                 | ı   | 55                 | %    |

| ΙL                        | OSC_IN Input leakage current        | $V_{SS} \leq V_{IN} \leq V_{DD}$ | -                  | ı   | ±1                 | μΑ   |

<sup>1.</sup> Guaranteed by design.

$V_{\mathsf{HSEH}}$ 90% 10%  $V_{HSEL}$ -T<sub>HSE</sub>  $f_{\mathsf{HSE\_ext}}$ EXTERNAL CLOCK SOURCE OSC\_IN STM32Lxx ai18232c

Figure 19. High-speed external clock source AC timing diagram

86/144

### 6.3.12 I/O current injection characteristics

As a general rule, current injection to the I/O pins, due to external voltage below  $V_{SS}$  or above  $V_{DD}$  (for standard pins) should be avoided during normal product operation. However, in order to give an indication of the robustness of the microcontroller in cases when abnormal injection accidentally happens, susceptibility tests are performed on a sample basis during device characterization.

### Functional susceptibility to I/O current injection

While a simple application is executed on the device, the device is stressed by injecting current into the I/O pins programmed in floating input mode. While current is injected into the I/O pin, one at a time, the device is checked for functional failures.

The failure is indicated by an out of range parameter: ADC error above a certain limit (higher than 5 LSB TUE), out of conventional limits of induced leakage current on adjacent pins (out of  $-5 \mu A/+0 \mu A$  range), or other functional failure (for example reset occurrence oscillator frequency deviation).

The test results are given in the Table 58.

Table 58. I/O current injection susceptibility

| Symbol           |                                                                  | Functional s       |                    |      |

|------------------|------------------------------------------------------------------|--------------------|--------------------|------|

|                  | Description                                                      | Negative injection | Positive injection | Unit |

|                  | Injected current on BOOT0                                        | -0                 | NA                 |      |

| I <sub>INJ</sub> | Injected current on PA0, PA4, PA5, PA11, PA12, PC15, PH0 and PH1 | -5                 | 0                  | mA   |

| IIVO             | Injected current on any other FT, FTf pins                       | -5 <sup>(1)</sup>  | NA                 |      |

|                  | Injected current on any other pins                               | -5 <sup>(1)</sup>  | +5                 |      |

It is recommended to add a Schottky diode (pin to ground) to analog pins which may potentially inject negative currents.

DocID025936 Rev 7

### Input/output AC characteristics

The definition and values of input/output AC characteristics are given in *Figure 26* and *Table 61*, respectively.

Unless otherwise specified, the parameters given in *Table 61* are derived from tests performed under ambient temperature and V<sub>DD</sub> supply voltage conditions summarized in *Table 25*.

Table 61. I/O AC characteristics<sup>(1)</sup>

| OSPEEDRx[1:0]<br>bit value <sup>(1)</sup> | Symbol                  | Parameter                                                       | Conditions                                                       | Min | Max <sup>(2)</sup> | Unit   |  |

|-------------------------------------------|-------------------------|-----------------------------------------------------------------|------------------------------------------------------------------|-----|--------------------|--------|--|

|                                           | f                       | Maximum frequency <sup>(3)</sup>                                | $C_L = 50 \text{ pF}, V_{DD} = 2.7 \text{ V to } 3.6 \text{ V}$  | -   | 400                | kHz    |  |

| 00                                        | f <sub>max(IO)out</sub> | waximum frequency                                               | C <sub>L</sub> = 50 pF, V <sub>DD</sub> = 1.65 V to 2.7 V        | -   | 100                | KIIZ   |  |

| 00                                        | t <sub>f(IO)out</sub>   | Output rise and fall time                                       | $C_L = 50 \text{ pF}, V_{DD} = 2.7 \text{ V to } 3.6 \text{ V}$  | -   | 125                | ns     |  |

|                                           | t <sub>r(IO)out</sub>   | Output rise and fail time                                       | $C_L = 50 \text{ pF}, V_{DD} = 1.65 \text{ V to } 2.7 \text{ V}$ | -   | 320                | 113    |  |

|                                           | f                       | Maximum frequency <sup>(3)</sup>                                | $C_L = 50 \text{ pF}, V_{DD} = 2.7 \text{ V to } 3.6 \text{ V}$  | -   | 2                  | MHz    |  |

| 01                                        | f <sub>max(IO)out</sub> | waximum nequency                                                | C <sub>L</sub> = 50 pF, V <sub>DD</sub> = 1.65 V to 2.7 V        | -   | 0.6                | IVIIIZ |  |

| 01                                        | t <sub>f(IO)out</sub>   | Output rise and fall time                                       | $C_L = 50 \text{ pF}, V_{DD} = 2.7 \text{ V to } 3.6 \text{ V}$  | -   | 30                 | ns     |  |

|                                           | t <sub>r(IO)out</sub>   | Output rise and fail time                                       | C <sub>L</sub> = 50 pF, V <sub>DD</sub> = 1.65 V to 2.7 V        | -   | 65                 | 115    |  |

|                                           | F                       | Maximum frequency <sup>(3)</sup>                                | C <sub>L</sub> = 50 pF, V <sub>DD</sub> = 2.7 V to 3.6 V         | -   | 10                 | NALI-  |  |

| 10                                        | F <sub>max(IO)out</sub> | Maximum frequency(*)                                            | C <sub>L</sub> = 50 pF, V <sub>DD</sub> = 1.65 V to 2.7 V        | -   | 2                  | - MHz  |  |

| 10                                        | t <sub>f(IO)out</sub>   | Output rise and fall time                                       | C <sub>L</sub> = 50 pF, V <sub>DD</sub> = 2.7 V to 3.6 V         | -   | 13                 | ne     |  |

|                                           | t <sub>r(IO)out</sub>   |                                                                 | C <sub>L</sub> = 50 pF, V <sub>DD</sub> = 1.65 V to 2.7 V        | -   | 28                 | ns     |  |

|                                           | Е                       | Maximum frequency <sup>(3)</sup>                                | $C_L = 30 \text{ pF}, V_{DD} = 2.7 \text{ V to } 3.6 \text{ V}$  | -   | 35                 | MHz    |  |

| 11                                        | F <sub>max(IO)out</sub> |                                                                 | C <sub>L</sub> = 50 pF, V <sub>DD</sub> = 1.65 V to 2.7 V        | -   | 10                 | IVITZ  |  |

| 11                                        | t <sub>f(IO)out</sub>   | Output rise and fall time                                       | C <sub>L</sub> = 30 pF, V <sub>DD</sub> = 2.7 V to 3.6 V         | -   | 6                  | no     |  |

|                                           | t <sub>r(IO)out</sub>   | Output rise and fail time                                       | C <sub>L</sub> = 50 pF, V <sub>DD</sub> = 1.65 V to 2.7 V        |     | 17                 | ns     |  |

|                                           | f <sub>max(IO)out</sub> | Maximum frequency <sup>(3)</sup>                                |                                                                  | -   | 1                  | MHz    |  |

|                                           | t <sub>f(IO)out</sub>   | Output fall time                                                | $C_L = 50 \text{ pF}, V_{DD} = 2.5 \text{ V to } 3.6 \text{ V}$  | -   | 10                 | no     |  |

| Fm+                                       | t <sub>r(IO)out</sub>   | Output rise time                                                |                                                                  | -   | 30                 | ns     |  |

| configuration <sup>(4)</sup>              | f <sub>max(IO)out</sub> | Maximum frequency <sup>(3)</sup>                                |                                                                  | -   | 350                | KHz    |  |

|                                           | t <sub>f(IO)out</sub>   | Output fall time                                                | C <sub>L</sub> = 50 pF, V <sub>DD</sub> = 1.65 V to 3.6 V        | -   | 15                 |        |  |

|                                           | t <sub>r(IO)out</sub>   | Output rise time                                                |                                                                  | -   | 60                 | ns     |  |

| -                                         | t <sub>EXTIpw</sub>     | Pulse width of external signals detected by the EXTI controller | -                                                                | 8   | -                  | ns     |  |

<sup>1.</sup> The I/O speed is configured using the OSPEEDRx[1:0] bits. Refer to the line reference manual for a description of GPIO Port configuration register.

90/144 DocID025936 Rev 7

<sup>2.</sup> Guaranteed by design.

<sup>3.</sup> The maximum frequency is defined in Figure 26.

<sup>4.</sup> When Fm+ configuration is set, the I/O speed control is bypassed. Refer to the line reference manual for a detailed description of Fm+ I/O configuration.

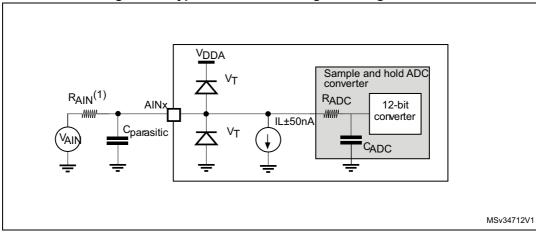

Figure 29. Typical connection diagram using the ADC

- 1. Refer to Table 63: ADC characteristics for the values of RAIN, RADC and CADC.

- $C_{parasitic}$  represents the capacitance of the PCB (dependent on soldering and PCB layout quality) plus the pad capacitance (roughly 7 pF). A high  $C_{parasitic}$  value will downgrade conversion accuracy. To remedy this,  $f_{ADC}$  should be reduced.

### General PCB design guidelines

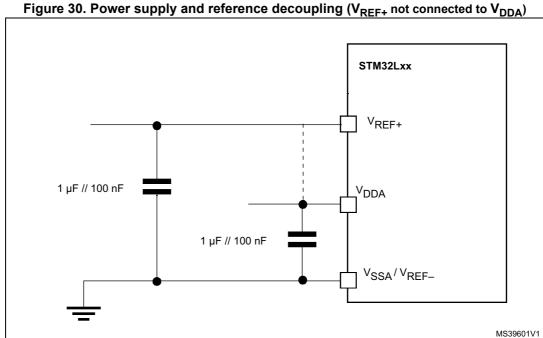

Power supply decoupling should be performed as shown in Figure 30 or Figure 31, depending on whether  $V_{\text{REF+}}$  is connected to  $V_{\text{DDA}}$  or not. The 10 nF capacitors should be ceramic (good quality). They should be placed as close as possible to the chip.

### 6.3.19 Timer characteristics

### **TIM timer characteristics**

The parameters given in the *Table 71* are guaranteed by design.

Refer to Section 6.3.13: I/O port characteristics for details on the input/output alternate function characteristics (output compare, input capture, external clock, PWM output).

| Symbol                 | Parameter                                               | Conditions                     | Min    | Max                     | Unit                 |  |  |  |  |

|------------------------|---------------------------------------------------------|--------------------------------|--------|-------------------------|----------------------|--|--|--|--|

| t                      | Timer resolution time                                   |                                | 1      | -                       | t <sub>TIMxCLK</sub> |  |  |  |  |

| <sup>t</sup> res(TIM)  | Time resolution time                                    | f <sub>TIMxCLK</sub> = 32 MHz  | 31.25  | -                       | ns                   |  |  |  |  |

| £                      | Timer external clock frequency on CH1                   |                                | 0      | f <sub>TIMxCLK</sub> /2 | MHz                  |  |  |  |  |

| f <sub>EXT</sub>       | to CH4                                                  | f <sub>TIMxCLK</sub> = 32 MHz  | 0      | 16                      | MHz                  |  |  |  |  |

| Res <sub>TIM</sub>     | Timer resolution                                        | -                              |        | 16                      | bit                  |  |  |  |  |

|                        | 16-bit counter clock period when                        | -                              | 1      | 65536                   | t <sub>TIMxCLK</sub> |  |  |  |  |

| t <sub>COUNTER</sub>   | internal clock is selected (timer's prescaler disabled) | f <sub>TIMxCLK</sub> = 32 MHz  | 0.0312 | 2048                    | μs                   |  |  |  |  |

| +                      | Maximum possible count                                  | -                              | -      | 65536 × 65536           | t <sub>TIMxCLK</sub> |  |  |  |  |

| <sup>t</sup> MAX_COUNT | Maximum possible count                                  | f <sub>TIMxCl K</sub> = 32 MHz | -      | 134.2                   | S                    |  |  |  |  |

Table 71. TIMx characteristics<sup>(1)</sup>

### 6.3.20 Communications interfaces

### I<sup>2</sup>C interface characteristics

The I<sup>2</sup>C interface meets the timings requirements of the I<sup>2</sup>C-bus specification and user manual rev. 03 for:

- Standard-mode (Sm): with a bit rate up to 100 kbit/s

- Fast-mode (Fm): with a bit rate up to 400 kbit/s

- Fast-mode Plus (Fm+): with a bit rate up to 1 Mbit/s.

The I<sup>2</sup>C timing requirements are guaranteed by design when the I<sup>2</sup>C peripheral is properly configured (refer to the reference manual for details). The SDA and SCL I/O requirements are met with the following restrictions: the SDA and SCL I/O pins are not "true" open-drain. When configured as open-drain, the PMOS connected between the I/O pin and VDDIOx is disabled, but is still present. Only FTf I/O pins support Fm+ low level output current maximum requirement (refer to Section 6.3.13: I/O port characteristics for the I2C I/Os characteristics).

All I<sup>2</sup>C SDA and SCL I/Os embed an analog filter (see *Table 72* for the analog filter characteristics).

<sup>1.</sup> TIMx is used as a general term to refer to the TIM2, TIM6, TIM21, and TIM22 timers.

### **SPI** characteristics

Unless otherwise specified, the parameters given in the following tables are derived from tests performed under ambient temperature,  $f_{PCLKx}$  frequency and  $V_{DD}$  supply voltage conditions summarized in *Table 25*.

Refer to Section 6.3.12: I/O current injection characteristics for more details on the input/output alternate function characteristics (NSS, SCK, MOSI, MISO).

Table 74. SPI characteristics in voltage Range 1 (1)

| Symbol                                    | Parameter                         | Conditions                                                  | Min     | Тур   | Max               | Unit |

|-------------------------------------------|-----------------------------------|-------------------------------------------------------------|---------|-------|-------------------|------|

| f <sub>SCK</sub><br>1/t <sub>c(SCK)</sub> |                                   | Master mode                                                 |         | -     | 16                | -    |

|                                           |                                   | Slave mode receiver                                         | -       |       | 16                |      |

|                                           | SPI clock frequency               | Slave mode<br>Transmitter<br>1.71 <v<sub>DD&lt;3.6V</v<sub> | -       | ı     | 12 <sup>(2)</sup> | MHz  |

|                                           |                                   | Slave mode<br>Transmitter<br>2.7 <v<sub>DD&lt;3.6V</v<sub>  | -       | ı     | 16 <sup>(2)</sup> |      |

| Duty <sub>(SCK)</sub>                     | Duty cycle of SPI clock frequency | Slave mode                                                  | 30      | 50    | 50 70 %           |      |

| t <sub>su(NSS)</sub>                      | NSS setup time                    | Slave mode, SPI<br>presc = 2                                | 4*Tpclk | -     | -                 |      |

| t <sub>h(NSS)</sub>                       | NSS hold time                     | Slave mode, SPI<br>presc = 2                                | 2*Tpclk | -     | -                 |      |

| t <sub>w(SCKH)</sub>                      | SCK high and low time             | Master mode                                                 | Tpclk-2 | Tpclk | Tpclk+            |      |

| t <sub>su(MI)</sub>                       | Data input setup time             | Master mode                                                 | 0       | -     | -                 |      |

| t <sub>su(SI)</sub>                       | Data input setup time             | Slave mode                                                  | 3       | i     | -                 |      |

| t <sub>h(MI)</sub>                        | Data input hold time              | Master mode                                                 | 7       | ı     | -                 |      |

| t <sub>h(SI)</sub>                        | Data input floid time             | Slave mode                                                  | 3.5     | i     | -                 | ns   |

| t <sub>a(SO</sub>                         | Data output access time           | Slave mode                                                  | 15      | i     | 36                |      |

| t <sub>dis(SO)</sub>                      | Data output disable time          | Slave mode                                                  | 10      | -     | 30                |      |

| t <sub>v(SO)</sub>                        |                                   | Slave mode<br>1.65 V <v<sub>DD&lt;3.6 V</v<sub>             | -       | 18    | 41                |      |

|                                           | Data output valid time            | Slave mode<br>2.7 V <v<sub>DD&lt;3.6 V</v<sub>              | -       | 18    | 25                |      |

| t <sub>v(MO)</sub>                        |                                   | Master mode                                                 | -       | 4     | 7                 |      |

| t <sub>h(SO)</sub>                        | Data output hold time             | Slave mode                                                  | 10      | _     | -                 |      |

| t <sub>h(MO)</sub>                        | Data output noid time             | Master mode                                                 | 0       | -     | -                 |      |

<sup>1.</sup> Guaranteed by characterization results.

<sup>2.</sup> The maximum SPI clock frequency in slave transmitter mode is determined by the sum of  $t_{v(SO)}$  and  $t_{su(MI)}$  which has to fit into SCK low or high phase preceding the SCK sampling edge. This value can be achieved when the SPI communicates with a master having  $t_{su(MI)} = 0$  while  $\text{Duty}_{(SCK)} = 50\%$ .

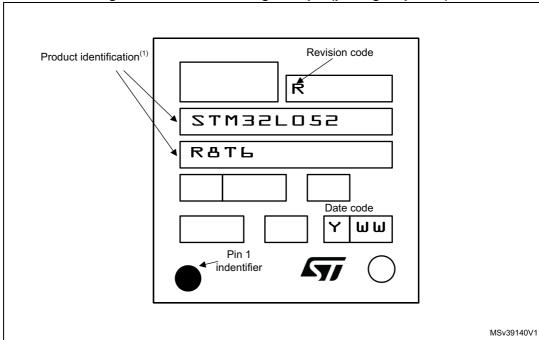

### **Device marking for LQFP64**

The following figure gives an example of topside marking versus pin 1 position identifier location.

Other optional marking or inset/upset marks, which depend on supply chain operations, are not indicated below.

Figure 41. LQFP64 marking example (package top view)

<sup>1.</sup> Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

Table 82. TFBGA64 – 64-ball, 5 x 5 mm, 0.5 mm pitch, thin profile fine pitch ball grid array package mechanical data (continued)

| Council of | millimeters |     |       | inches <sup>(1)</sup> |     |        |

|------------|-------------|-----|-------|-----------------------|-----|--------|

| Symbol     | Min         | Тур | Max   | Min                   | Тур | Max    |

| ddd        | -           | -   | 0.080 | -                     | -   | 0.0031 |

| eee        | -           | -   | 0.150 | -                     | -   | 0.0059 |

| fff        | -           | -   | 0.050 | -                     | -   | 0.0020 |

<sup>1.</sup> Values in inches are converted from mm and rounded to 4 decimal digits.

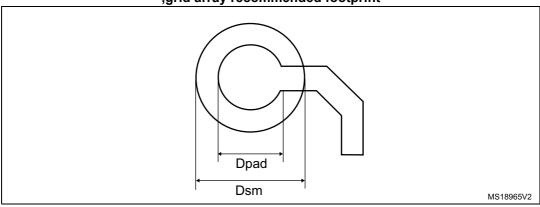

Figure 43. TFBGA64 – 64-ball, 5 x 5 mm, 0.5 mm pitch, thin profile fine pitch ball ,grid array recommended footprint

Table 83. TFBGA64 recommended PCB design rules (0.5 mm pitch BGA)

| Dimension    | Recommended values                                              |  |  |

|--------------|-----------------------------------------------------------------|--|--|

| Pitch        | 0.5                                                             |  |  |

| Dpad         | 0.27 mm                                                         |  |  |

| Dsm          | 0.35 mm typ. (depends on the soldermask registration tolerance) |  |  |

| Solder paste | 0.27 mm aperture diameter.                                      |  |  |

Note: Non solder mask defined (NSMD) pads are recommended.

4 to 6 mils solder paste screen printing process.

# 7.7 UFQFPN32 package information

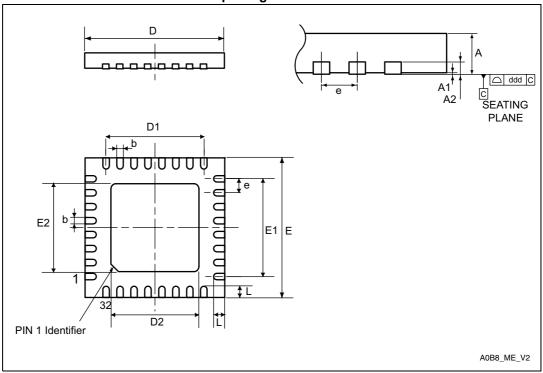

Figure 56. UFQFPN32 - 32-pin, 5x5 mm, 0.5 mm pitch ultra thin fine pitch quad flat package outline

1. Drawing is not to scale.

4

Table 93. Document revision history (continued)

| Unda                                                                                                                                                                                                                                  | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| pin/b Upda Upda Figur STM Upda devic Upda ADC in Ta Run/ Upda Adde Upda varia Rena Adde Upda oscill Adde cons 23-Jul-2015 5 Upda 1²C ir table Char into L Char meas calib Upda powe 64 K Stop Figur RTC Upda NSS Upda upda and p Upda | ated all pinout/ballout schematics except for LQFP32 to highlight all supplied through VDD_USB.  ated Table 16: STM32L052x6/8 pin definitions PC5 as FT pin.  ated Figure 5: STM32L052x6/8 LQFP48 pinout - 7 x 7 mm,  ated Figure 5: STM32L052x6/8 LQFP64 pinout - 10 x 10 mm and Figure 4:  32L052x6/8 TFBGA64 ballout - 5x 5 mm.  ated Figure 55, Figure 58, Figure 47, Figure 41 and Figure 44  be marking example.  ated current consumption in Run mode in Section : Features.  no more available in Low-power run and Low-power Sleep modes  ble 5: Functionalities depending on the working mode (from  factive down to standby).  ated ES disclaimer.  and CSP outline.  ated Table 22: Voltage characteristics adding VDDA-VDDX  tions and adding note 3.  amed BOOT1 into nBOOT1.  ated t <sub>UP_LDO</sub> in Table 63: ADC characteristics.  ated LQFP32 pinout (PC14).  ated MSI oscillator temperature frequency drift in Table MSI  lator characteristics.  and note related to Standby mode in table Peripheral current  tumption in Stop /standby.  ated Section 1: Introduction packages from 32 pins to 64 pins.  Interface characteristics: updated introduction and characteristics |

### **IMPORTANT NOTICE - PLEASE READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

144/144

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2017 STMicroelectronics - All rights reserved

DocID025936 Rev 7