# E·XFL

#### Welcome to E-XFL.COM

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                                 |

|---------------------------------|--------------------------------------------------------------------------|

| Core Processor                  | CPU32+                                                                   |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                           |

| Speed                           | 25MHz                                                                    |

| Co-Processors/DSP               | Communications; CPM                                                      |

| RAM Controllers                 | DRAM                                                                     |

| Graphics Acceleration           | No                                                                       |

| Display & Interface Controllers | · ·                                                                      |

| Ethernet                        | 10Mbps (1)                                                               |

| SATA                            | -                                                                        |

| USB                             | · ·                                                                      |

| Voltage - I/O                   | 5.0V                                                                     |

| Operating Temperature           | -40°C ~ 85°C (TC)                                                        |

| Security Features               | -                                                                        |

| Package / Case                  | 240-BFCQFP                                                               |

| Supplier Device Package         | 240-CERQUAD (31x31)                                                      |

| Purchase URL                    | https://www.e-xfl.com/product-detail/microchip-technology/ts68en360va25l |

|                                 |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

R suffix PGA 241 Ceramic Pin Grid Array Cavity Up Ceramic Leaded Chip Carrier Cavity Down

## Introduction

## QUICC Architecture Overview

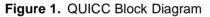

The QUICC is 32-bit controller that is an extension of other members of the TS68300 family. Like other members of the TS68300 family, the QUICC incorporates the intermodule bus (IMB). The TS68302 is an exception, having an 68000 bus on chip. The IMB provides a common interface for all modules of the TS68300 family, which allows the development of new devices more quickly by using the library of existing modules. Although the IMB definition always included an option for an on-chip 32-bit bus, the QUICC is the first device to implement this option.

The QUICC is comprised of three modules: the CPU32+ core, the SIM60, and the CPM. Each module utilizes the 32-bit IMB.

The TS68EN360 QUICC block diagram is shown in Figure 1.

| Group                | Signal Name                                                | Mnemonic            | Function                                                                                                                                                                                                                            |

|----------------------|------------------------------------------------------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bus Control          | Data and Size<br>Acknowledge                               | DSACKT - DSACKO     | Provides asynchronous data transfer acknowledgement and dynamic bus sizing (open-drain I/O but driven high before three-stated).                                                                                                    |

|                      | Address Strobe                                             | AS                  | Indicates that a valid address is on the address bus. (I/O)                                                                                                                                                                         |

|                      | Data Strobe                                                | DS                  | During a read cycle, DS indicates that an external device should place valid data on the data bus. During a write cycle, DS indicates that valid data is on the data bus. (I/O)                                                     |

|                      | Size                                                       | SIZ1-SIZ0           | Indicates the number of bytes remaining to be transferred for this cycle. (I/O)                                                                                                                                                     |

|                      | Read/Write                                                 | R/₩                 | Indicates the direction of data transfer on the bus. (I/O)                                                                                                                                                                          |

|                      | Output Enable Address<br>Multiplex                         | <del>oe</del> /amux | Active during a read cycle indicates that an external device<br>should place valid data on the data bus (O) or provides a<br>strobe for external address multiplexing in DRAM accesses<br>if internal multiplexing is not used. (O) |

| Interrupt<br>Control | Interrupt Request<br>Level 7-1                             | IRQ7-IRQ1           | Provides external interrupt requests to the CPU32+ at priority levels 7-1. (I)                                                                                                                                                      |

|                      | Autovector/Interrupt<br>Acknowledge 5                      | AVEC/IACK5          | Autovector request during an interrupt acknowledge cycle<br>(open-drain I/O) or interrupt level 5 acknowledge line. (O)                                                                                                             |

| System               | Soft Reset                                                 | RESETS              | Soft system reset. (open-drain I/O)                                                                                                                                                                                                 |

| Control              | Hard Reset                                                 | RESETH              | Hard system reset. (open-drain I/O)                                                                                                                                                                                                 |

|                      | Halt                                                       | HALT                | Suspends external bus activity. (open-drain I/O)                                                                                                                                                                                    |

|                      | Bus Error                                                  | BERR                | Indicates an erroneous bus operation is being attempted.<br>(open-drain I/O)                                                                                                                                                        |

| Clock and Test       | System Clock Out 1                                         | CLKO1               | Internal system clock output 1. (O)                                                                                                                                                                                                 |

|                      | System Clock Out 2                                         | CLKO2               | Internal system clock output 2 - normally 2x CLKO1. (O)                                                                                                                                                                             |

|                      | Crystal Oscillator                                         | EXTAL, XTAL         | Connections for an external crystal to the internal oscillator circuit. EXTAL (I), XTAL (O).                                                                                                                                        |

|                      | External Filter Capacitor                                  | XFC                 | Connection pin for an external capacitor to filter the circuit of the PLL. (I)                                                                                                                                                      |

|                      | Clock Mode Select 1-0                                      | MODCK1-MODCK0       | Selects the source of the internal system clock. (I) THESE PINS SHOULD NOT BE SET TO 00                                                                                                                                             |

|                      | Instruction Fetch/<br>Development Serial Input             | IFETCH/DSI          | Indicates when the CPU32+ is performing an instruction word prefetch (O) or input to the CPU32+ background debug mode. (I)                                                                                                          |

|                      | Instruction Pipe 0/<br>Development Serial<br>Output        | IPIPE0/DSO          | Used to track movement of words through the instruction pipeline (O) or output from the CPU32+ background debug mode. (O)                                                                                                           |

|                      | Instruction Pipe 1/Row<br>Address Select 1<br>Double-Drive | IPIPE1/RAS1DD       | Used to track movement of words through the instruction pipeline (O), or a row address select 1 "double-drive" output (O).                                                                                                          |

|                      | Breakpoint/Development<br>Serial Clock                     | BKPT/DSCLK          | Signals a hardware breakpoint to the QUICC (open-drain I/O), or clock signal for CPU32+ background debug mode (I).                                                                                                                  |

|                      | Freeze/Initial<br>Configuration 2                          | FREEZE/CONFIG2      | Indicates that the CPU32+ has acknowledged a breakpoint (O), or initial QUICC configuration select (I).                                                                                                                             |

Table 1. System Bus Signal Index (Normal Operation) (Continued)

| Group                      | Signal Name                    | Mnemonic | Function                                                                                                        |  |  |

|----------------------------|--------------------------------|----------|-----------------------------------------------------------------------------------------------------------------|--|--|

| Clock and Test<br>(Cont'd) | Three-State                    | TRIS     | Used to three-state all pins if QUICC is configured as a master. Always Sampled except during system reset. (I) |  |  |

|                            | Test Clock                     | ТСК      | Provides a clock for Scan test logic. (I)                                                                       |  |  |

|                            | Test Mode Select               | TMS      | Controls test mode operations. (I)                                                                              |  |  |

|                            | Test Data In                   | TDI      | Serial test instructions and test data signal. (I)                                                              |  |  |

|                            | Test Data Out                  | TDO      | Serial test instructions and test data signal. (O)                                                              |  |  |

|                            | Test Reset                     | TRST     | Provides an asynchronous reset to the test controller. (I)                                                      |  |  |

| Power                      | Clock Synthesizer Power        | VCCSYN   | Power supply to the PLL of the clock synthesizer.                                                               |  |  |

|                            | Clock Synthesizer Ground       | GNDSYN   | Ground supply to the PLL of the clock synthesizer.                                                              |  |  |

|                            | Clock Out Power                | VCCCLK   | Power supply to clock out pins.                                                                                 |  |  |

|                            | Clock Out Ground               | GNDCLK   | Ground supply to clock out pins.                                                                                |  |  |

|                            | Special Ground 1               | GNDS1    | Special ground for fast AC timing on certain system bus signals.                                                |  |  |

|                            | Special Ground 2               | GNDS2    | Special ground for fast AC timing on certain system bus signals.                                                |  |  |

|                            | System Power Supply and Return | VCC, GND | Power supply and return to the QUICC.                                                                           |  |  |

|                            | No Connect                     | NC4-NC1  | Four no-connect pins.                                                                                           |  |  |

Table 1. System Bus Signal Index (Normal Operation) (Continued)

Note:

1. I denotes input, O denotes output and I/O is input/output.

## Table 4. Recommended Conditions Of Use

Unless otherwise stated, all voltages are referenced to the reference terminal.

| Symbol            | Parameter                            |                      | Min.  | Тур. | Max.            | Unit |

|-------------------|--------------------------------------|----------------------|-------|------|-----------------|------|

| V <sub>cc</sub>   | Supply Voltage Range                 |                      | +4.75 |      | +5.25           | V    |

| V <sub>IL</sub>   | Logic Low Level Input Voltage Range  |                      | GND   |      | +0.8            | V    |

| V <sub>IH</sub>   | Logic High Level Input Voltage Range |                      | +2.0  |      | V <sub>cc</sub> | V    |

| T <sub>case</sub> | Operating Temperature                |                      | -55   |      | +125            | °C   |

| V <sub>OH</sub>   | High Level Output Voltage            |                      | +2.4  |      |                 | V    |

| f <sub>sys</sub>  | System Frequency                     | (For 25 MHz version) |       | 25   |                 | MHz  |

|                   |                                      | (For 33 MHz version) |       | 33   |                 | MHz  |

#### Table 5. Thermal Characteristics

| Symbol          | Parameter                                |                 | Value | Unit |

|-----------------|------------------------------------------|-----------------|-------|------|

| JC JC           | Thermal Resistance - Junction to Case    | 240-pin Cerquad | 2     | 0000 |

|                 |                                          | 241-pin PGA     | 7     | °C/W |

| L <sub>JA</sub> | Thermal Resistance - Junction to Ambient | 240-pin Cerquad | 27.4  | 0000 |

|                 |                                          | 241-pin PGA     | 22.8  | °C/W |

$T_{I} = T_{\Delta} + (P_{D} \cdot \theta_{I\Delta})$  $P_{D} = (V_{DD} \cdot I_{DD}) + P_{I/O}$ Where P<sub>I/O</sub> is the power dissipation on pins. **Power Considerations** The average chip-junction temperature, T<sub>j</sub>, in °C can be obtained from:  $\mathbf{T}_{\mathsf{J}} = \mathbf{T}_{\mathsf{A}} \div (\mathsf{P}_{\mathsf{D}} \cdot \boldsymbol{\Theta}_{\mathsf{J}\mathsf{A}})$ (1)where: T<sub>A</sub> = Ambient Temperature, °C  $\Theta_{JA}$  = Package Thermal Resistance, Junction-to-Ambient, C/W  $P_D = P_{INT} + P_{I/O}$  $P_{INT} = I_{CC} \cdot V_{CC}$ , Watts-chip Internal Power P<sub>I/O</sub> = Power Dissipation on Input and Output Pins-User Determined For most applications,  $P_{I/O} < 0.3 \cdot P_{INT}$  and can be neglected. An approximate relationship between  $P_D$  and  $T_J$  (if  $P_{I/O}$  is neglected) is:  $\mathsf{P}_\mathsf{D} = \mathsf{K} \div (\mathsf{T}_\mathsf{J} + 273^\circ \mathsf{C})$ (2)Solving Equations (1) and (2) for K gives:  $K = P_{D} \cdot (T_{A} + 273^{\circ}C) + \Theta_{JA} \cdot P_{D}^{-2}$ (3)where K is a constant pertaining to the particular part. K can be determined from Equation (3) by measuring  $P_D$  (at thermal equilibrium) for a know  $T_A$ . Using this value of K, the values of  $P_D$  and  $T_J$  can be obtained by solving Equations (1) and (2) iteratively for

any value of  $T_A$ .

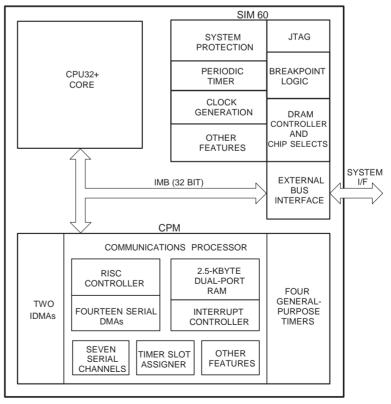

# **Bus Operation AC Timing Specifications**

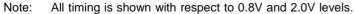

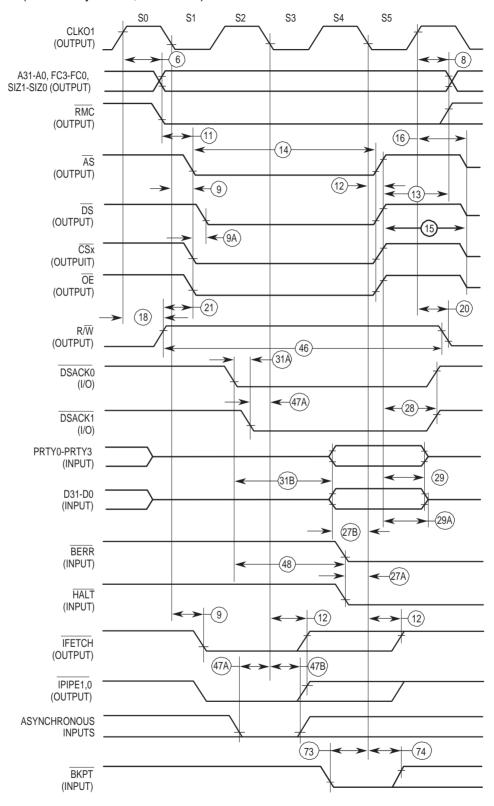

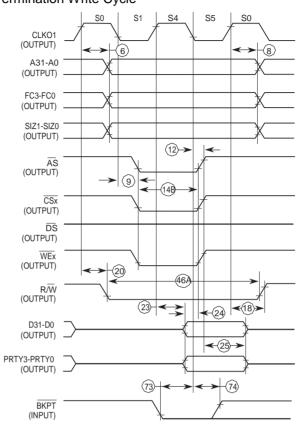

GND = 0 Vdc,  $T_c$  = -55 to +125°C. The electrical specifications in this document are preliminary (See Figure 7 to Figure 23).

|                               |                                                                                  |                    | 25  | MHz | 33.34  |       |      |

|-------------------------------|----------------------------------------------------------------------------------|--------------------|-----|-----|--------|-------|------|

| Number                        | Characteristic                                                                   | Symbol             | Min | Max | Min    | Max   | Unit |

| 6                             | CLKO1 High to Address, FC, SIZ, RMCValid                                         | t <sub>CHAV</sub>  | 0   | 15  | 0      | 12    | ns   |

| 6A                            | CLKO1 High to Address Valid (GAMX = 1)                                           | <b>E</b> HAV       | 0   | 20  | 0      | 15    | ns   |

| 7                             | CLKO1 High to Address, Data, FC, SIZ, RMCHigh<br>Impedance                       | t <sub>CHAZx</sub> | 0   | 40  | 0      | 30    | ns   |

| 8                             | CLKO1 High to Address, Data, FC, SIZ, RMC Invalid                                | t <sub>CHAZn</sub> | -2  | -   | -2     | -     | ns   |

| 9                             | CLKO1 Low to AS, DS, OE, WE, IFETCH, IPIPE, IACKx Asserted                       | t <sub>CLSA</sub>  | 3   | 20  | 3      | 15    | ns   |

| 9 <sup>(10)</sup>             | CLKO1 Low to CSXRASX Asserted                                                    | t <sub>CLSA</sub>  | 4   | 16  | 4      | 12    | ns   |

| 9B <sup>(11)</sup>            | CLKO1 High to CSX/RASX Asserted                                                  | t <sub>CHCA</sub>  | 4   | 16  | 4      | 12    | ns   |

| 9A <sup>(2)(10)</sup>         | AS to DS or CSX/RASX or OE Asserted (Read)                                       | t <sub>stsa</sub>  | -6  | 6   | -5.625 | 5.625 | ns   |

| 9C <sup>(2)(11)</sup>         | AS to CSX/RASX Asserted                                                          | t <sub>STCA</sub>  | 14  | 26  | 9      | 21    | ns   |

| 11 <sup>(10)</sup>            | Address, FC, SIZ, RMC, valid to AS, CSX/RASX,<br>OE, WE, (and DS Read) Asserted  | t <sub>AVSA</sub>  | 10  | -   | 8      | -     | ns   |

| 11A <sup>(11)</sup>           | Address, FC, SIZ, RMC, Valid to CSXRASX<br>Asserted                              | t <sub>AVCA</sub>  | 30  | -   | 22.5   | -     | ns   |

| 12                            | CLKO1 Low to AS, DS, OE, WE, IFETCH, IPIPE, IACKX Negated                        | t <sub>CLSN</sub>  | 3   | 20  | 3      | 15    | ns   |

| 12 <sup>(16)</sup>            | CLKO1 Low to CSXRASX Negated                                                     | t <sub>CLSN</sub>  | 4   | 16  | 4      | 12    | ns   |

| 12A <sup>(13)(16)</sup>       | CLKO1 High to CST/RAST Negated                                                   | t <sub>CHCN</sub>  | 4   | 16  | 4      | 12    | ns   |

| 12B                           | CS negate to WE negate (CSNTQ = 1)                                               | Atme <sub>fw</sub> | 15  | -   | 12     | -     | ns   |

| 13 <sup>(12)</sup>            | AS, DS, CSx, OE, WE, IACKx Negated to Address,<br>FC, SIZ Invalid (Address Hold) | t <sub>snai</sub>  | 10  | -   | 7.5    | -     | ns   |

| 13A <sup>(13)</sup>           | CSx Negated to Address, FC, SIZ, Invalid (Address Hold)                          | t <sub>CNAI</sub>  | 30  | -   | 22.5   | -     | ns   |

| <b>14</b> <sup>(10)(12)</sup> | AS, CSx, OE, WE (and DS Read) Width Asserted                                     | <b>t</b> swa       | 75  | -   | 56.25  | -     | ns   |

| 14C <sup>(11)(13)</sup>       | CSx Width Asserted                                                               | t <sub>cwa</sub>   | 35  | -   | 26.25  | -     | ns   |

| 14A                           | DS Width Asserted (Write)                                                        | t <sub>swaw</sub>  | 35  | -   | 26.25  | -     | ns   |

| 14B                           | AS, CSx, OE, WE, IACKx, (and DS Read) Width<br>Asserted (Fast Termination Cycle) | t <sub>SWDW</sub>  | 35  | -   | 26.25  | -     | ns   |

| 14D <sup>(13)</sup>           | CSx Width Asserted (Fast Termination Cycle)                                      | ŧwow               | 15  | -   | 10     | -     | ns   |

| 15 <sup>(3)(10)(12)</sup>     | AS, DS, CSx, OE, WE Width Negated                                                | t <sub>sn</sub>    | 35  | -   | 26.25  | -     | ns   |

| 16                            | CLKO1 High to AS, DS, R/₩ High Impedance                                         | t <sub>chsz</sub>  | -   | 40  | -      | 30    | ns   |

| 17 <sup>(12)</sup>            | AS, DS, CSx, WE Negated to R/W High                                              | t <sub>SNRN</sub>  | 10  | -   | 7.5    | -     | ns   |

| 17A <sup>(13)</sup>           | CSx Negated to R/₩ High                                                          | t <sub>cnrn</sub>  | 30  | -   | 22.5   | -     | ns   |

| 18                            | CLKO1 High to R/W High                                                           | t <sub>chrh</sub>  | 0   | 20  | 0      | 15    | ns   |

## **Bus Operation AC Timing Specifications (Continued)**

GND = 0 Vdc,  $T_c$  = -55 to +125°C. The electrical specifications in this document are preliminary (See Figure 7 to Figure 23).

|                        |                                                                                        |                    | 25  | MHz | 33.34 MHz |      |      |

|------------------------|----------------------------------------------------------------------------------------|--------------------|-----|-----|-----------|------|------|

| Number                 | Characteristic                                                                         | Symbol             | Min | Max | Min       | Max  | Unit |

| 20                     | CLKO1 High to R/₩ Low                                                                  | t <sub>CHRL</sub>  | 3   | 20  | 3         | 15   | ns   |

| 21 <sup>(10)</sup>     | R/₩ High to AS, CSx, OE Asserted                                                       | t <sub>RAAA</sub>  | 10  | -   | 7.5       | -    | ns   |

| 21A <sup>(11)</sup>    | R/₩ High to CSx Asserted                                                               | t <sub>RACA</sub>  | 30  | -   |           | -    | ns   |

| 22                     | R/₩ Low to DS Asserted (Write)                                                         | t <sub>RASA</sub>  | 47  | -   | 36        | -    | ns   |

| 23                     | CLKO1 High to Data-Out                                                                 | t <sub>chdo</sub>  | -   | 23  | -         | 18   | ns   |

| 23A                    | CLKO1 High to Parity Valid                                                             | t<br>CHPV          | -   | 25  | -         | 20   | ns   |

| 23B                    | Parity Valid to CAS Low                                                                | t <sub>PVCL</sub>  | 3   | -   | 3         | -    | ns   |

| 24 <sup>(12)</sup>     | Data-Out, Parity-Out Valid to Negating Edge of AS<br>CSx, ₩E, (Fast Termination Write) | t <sub>DVASN</sub> | 10  | -   | 7.5       | -    | ns   |

| 25 <sup>(12)</sup>     | DS, CSX, WE Negated to Data-Out, Parity-Out<br>Invalid (Data-Out, Parity-Out Hold)     | t <sub>sndoi</sub> | 10  | -   | 7.5       | -    | ns   |

| 25A <sup>(13)</sup>    | CSx Negated to Data-Out, Parity-Out Invalid (Data-<br>Out, Parity-Out Hold)            | t <sub>CNDOI</sub> | 35  | -   | 25        | -    | ns   |

| 26                     | Data-Out, Parity-Out Valid to DSAsserted (Write)                                       | t <sub>DVSA</sub>  | 10  | -   | 7.5       | -    | ns   |

| 27 <sup>(15)</sup>     | Data-In, Parity-In to CLKO1 Low (Data-Setup)                                           | <b>b</b> ICL       | 1   | -   | 1         | -    | ns   |

| 27B <sup>(14)</sup>    | Data-In, Parity-In Valid to CLKO1 Low (Data-Setup)                                     | <b>b</b> ICL       | 20  | -   | 15        | -    | ns   |

| 27A                    | Late BERR, HALT, BKPT Asserted to CLKO1 Low (Setup Time)                               | t <sub>BELCL</sub> | 10  | -   | 7.5       | -    | ns   |

| 28 <sup>(18)</sup>     | AS, DS Negated to DSACKx, BERR, HALT<br>Negated                                        | t <sub>SNDN</sub>  | 0   | 50  | 0         | 37.5 | ns   |

| 29 <sup>(4)</sup>      | DS, CSx, OE, Negated to Data-In Parity-In Invalid<br>(Data-In, Parity-In Hold)         | t <sub>SNDI</sub>  | 0   | -   | 0         | -    | ns   |

| 29A <sup>(4)</sup>     | DS, CSx, OE Negated to Data-In High Impedance                                          | ŧны                | -   | 40  | -         | 30   | ns   |

| 30 <sup>(4)</sup>      | CLKO1 Low to Data-In, Parity-In Invalid (Fast Termination Hold)                        | t <sub>CLDI</sub>  | 10  | -   | 7.5       | -    | ns   |

| 30A <sup>(4)</sup>     | CLKO1 Low to Data-In High Impedance                                                    | ŧldh               | -   | 60  | -         | 45   | ns   |

| 31 <sup>(5)(15)</sup>  | DSACKx Asserted to Data-in, Parity-In Valid                                            | <b>b</b> adi       | -   | 32  | -         | 24   | ns   |

| 31A                    | DSACKx Asserted to DSACKx Valid (Skew)                                                 | t <sub>DADV</sub>  | -   | 10  | -         | 7.5  | ns   |

| 31B <sup>(5)(14)</sup> | DSACKx Asserted to Data-in, Parity-In Valid                                            | <b>b</b> adi       | -   | 35  | -         | 26   | ns   |

| 32                     | HALT an RESET Input Transition Time                                                    | t <sub>HRrf</sub>  | -   | 140 | -         |      | ns   |

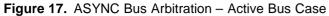

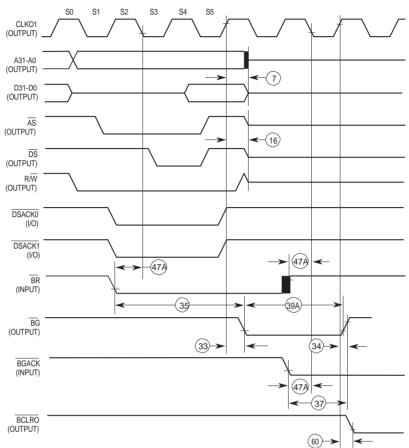

| 33                     | CLKO1 High to BG Asserted                                                              | t <sub>CLBA</sub>  | -   | 20  | -         | 15   | ns   |

| 34                     | CLKO1 High to BG Negated                                                               | t <sub>CLBN</sub>  | -   | 20  | 22.5      | 15   | ns   |

| 35 <sup>(6)</sup>      | BR Asserted to BG Asserted (RMC Not Asserted)                                          | t <sub>BRAGA</sub> | 1   | -   | 1         | -    | CLKO |

| 37                     | BGACK Asserted to BG Negated                                                           | t <sub>GAGN</sub>  | 1   | 2.5 | 1         | 2.5  | CLKO |

| 39                     | BG Width Negated                                                                       | t <sub>GH</sub>    | 2   | -   | 2         | -    | CLKO |

| 39A                    | BG Width Asserted                                                                      | t <sub>GA</sub>    | 1   | -   | 1         | -    | CLKO |

Figure 7. Read Cycle

**TS68EN360**

Figure 9. Read Cycle (With Parity Check, PBEE = 1)

Note: All timing is shown with respect to 0.8V and 2.0V levels.

Figure 13. Fast Termination Write Cycle

Figure 14. SRAM: Fast Termination Write Cycle (CSNTQ = 1)

## **Bus Operation - DRAM Accesses AC Timing Specification**

GND = 0 Vdc,  $T_c$  = -55 to +125°C. The electrical specifications in this document are preliminary (See Figure 24 to Figure 28).

|                  |                                                                  | 25.0 | MHz | 33.34 | MHz | Unit |  |

|------------------|------------------------------------------------------------------|------|-----|-------|-----|------|--|

| Number           | Characteristic                                                   | Min  | Max | Min   | Max |      |  |

| 100              | RASx Asserted to Row Address Invalid                             | 15   |     | 11.25 |     | ns   |  |

| 101              | RASx Asserted to column Address Valid                            | 20   |     | 15    |     | ns   |  |

| 102              | RASx Width Asserted                                              | 75   |     | 56.25 |     | ns   |  |

| 103A             | RASx width Negated (Back to back Cycle) Non page mode @ WBTQ = 0 | 75   |     | 56.25 |     | ns   |  |

| 103B             | RASx width Negated (Back to back Cycle) Page mode @ WBTQ = 0     | 55   |     | 41.25 |     | ns   |  |

| 103C             | RASx width Negated (Back to back Cycle) Non page mode @ WBTQ = 1 | 115  |     | 86.25 |     | ns   |  |

| 103D             | RASx width Negated (Back to back Cycle) Page mode @ WBTQ = 1     | 95   |     | 69.23 |     | ns   |  |

| 104              | RASx Asserted to CASx Asserted                                   | 35   |     | 26.25 |     | ns   |  |

| 105              | CLKO1 Low to CAST Asserted                                       | 3    | 13  | 2     | 10  | ns   |  |

| 105A             | CLKO1 High to CASx Asserted (Refresh Cycle)                      | 3    | 13  | 2     | 10  | ns   |  |

| 106              | CLKO1 High to CASx Negated                                       | 3    | 13  | 2     | 10  | ns   |  |

| 107              | Column Address Valid to CASx Asserted                            | 15   |     | 11.25 |     | ns   |  |

| 108              | CASx Asserted to Column Address Negated                          | 40   |     | 30    |     | ns   |  |

| 109              | CASx Asserted to RASx Negated                                    | 35   |     | 27    |     | ns   |  |

| 110              | CASx Width Asserted                                              | 50   |     | 37.5  |     | ns   |  |

| 111 <sup>1</sup> | CASx Width Negated (Back to Back Cycles)                         | 95   |     | 71.25 |     | ns   |  |

| 111A             | CASx Width Negated (Page Mode)                                   | 20   |     | 15    |     | ns   |  |

| 113              | WE Low to CASX Asserted                                          | 35   |     | 27    |     | ns   |  |

| 114              | CASx Asserted to WE Negated                                      | 35   |     | 27    |     | ns   |  |

| 115              | R/W Low to CASx Asserted (Write)                                 | 52.5 |     | 40    |     | ns   |  |

| 116              | CASx Asserted to R/W High (Write)                                | 55   |     | 41.25 |     | ns   |  |

| 117              | Data-Out, Parity-Out Valid to CASx Asserted                      | 10   |     | 7.5   |     | ns   |  |

| 119              | CLKO1 High to AMUX Negated                                       | 3    | 16  | 2     | 12  | ns   |  |

| 120              | CLKO1 High to AMUX Asserted                                      | 3    | 16  | 2     | 12  | ns   |  |

| 121              | AMUX High to RASx Asserted                                       | 15   |     | 11.25 |     | ns   |  |

| 122              | RASx Asserted to AMUX Low                                        | 15   |     | 11.25 |     | ns   |  |

| 123              | AMUX Low to CASx Asserted                                        | 15   |     | 11.25 |     | ns   |  |

| 124              | CASx Asserted to AMUX High                                       | 55   |     | 41.25 |     | ns   |  |

| 125              | RAS/CASx Negated to R/W change                                   | 0    |     | 0     |     | ns   |  |

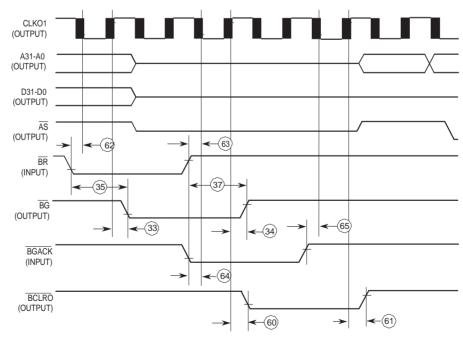

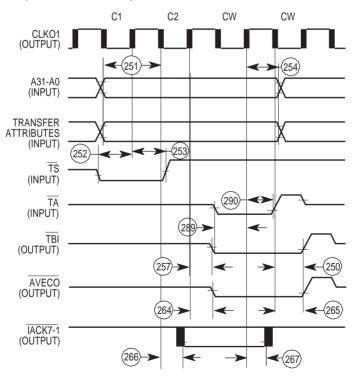

Figure 32. TS68040 IACK Cycles (Vector Driven)

Notes: 1. TS68040 Transfer Attribute Signals = SIZx, TTx, TMx, RW LOCK.

2. Up to two wait states may be inserted for internal peripheral.

Figure 33. TS68040 IACK Cycles (No Vector Driven)

Note: TS68040 Transfer Attribute Signals = SIZx, TTx, TMx,  $R\overline{W}$  LOCK.

# 42 **TS68EN360**

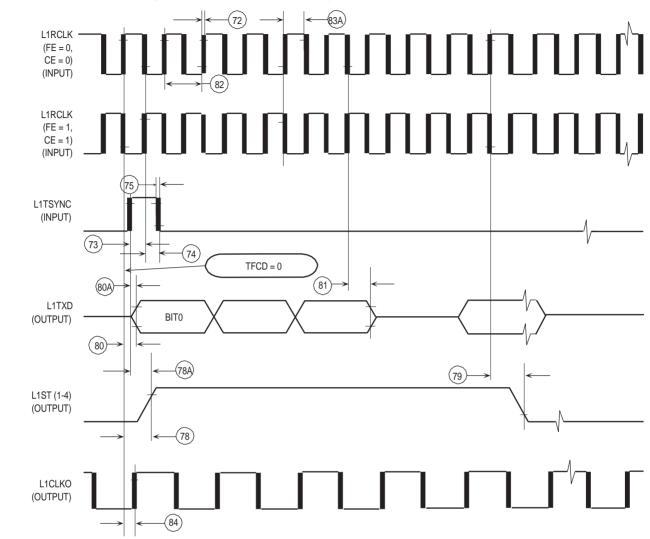

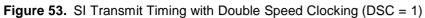

Figure 54. IDL Timing SI Transmit Timing with Double Speed Clocking (DSC = 1)

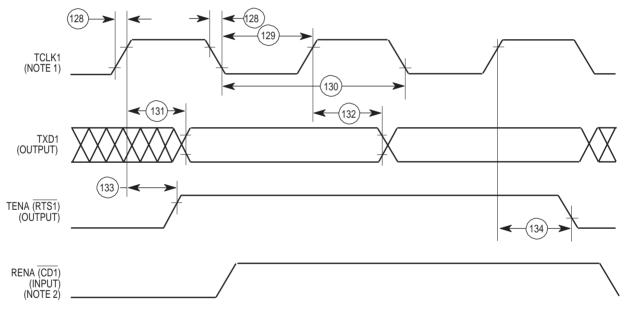

## SCC in NMSI Mode-external Clock Electrical Specifications

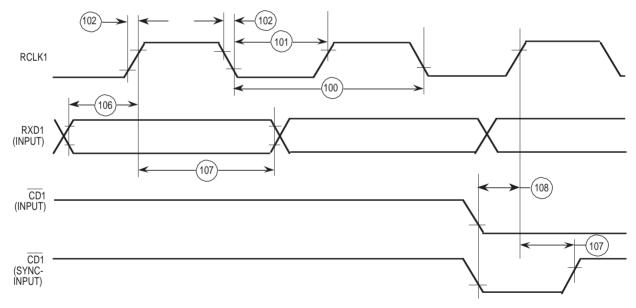

GND = 0  $V_{DC}$ ,  $T_{C}$  = -55 to +125°C. The electrical specifications in this document are preliminary (See Figure 55 to Figure 57).

|                    |                                                      | 25.0 MHz        |     | 33.34           | MHz |      |  |

|--------------------|------------------------------------------------------|-----------------|-----|-----------------|-----|------|--|

| Number             | Characteristic                                       | Min             | Max | Min             | Max | Unit |  |

| 100 <sup>(1)</sup> | RCLK1 and TCLK1 Width High                           | CLKO1           | -   | CLKO1           | -   |      |  |

| 101                | RCLK1 and TCLK1 Width Low                            | CLKO1 +<br>5 ns | -   | CLKO1 +<br>5 ns | -   |      |  |

| 102                | RCLK1 and TCLK1 Rise/Fall Time                       | -               | 15  | -               | 15  | ns   |  |

| 103                | TXD1 Active Delay (From TCLK1 Falling Edge)          | 0               | 50  | 0               | 50  | ns   |  |

| 104                | RTS1 Active/Inactive Delay (From TCLK1 Falling Edge) | 0               | 50  | 0               | 50  | ns   |  |

| 105                | CTS1 Setup Time to TCLK1 Rising Edge                 | 40              | -   | 40              | -   | ns   |  |

| 106                | RXD1 Setup Time to RCLK1 Rising Edge                 | 40              | -   | 40              | -   | ns   |  |

| 107 <sup>(2)</sup> | RXD1 Hold Time from RCLK1 Rising Edge                | 0               | -   | 0               | -   | ns   |  |

| 108                | CD1 Setup Time to RCLK1 Rising Edge                  | 40              | -   | 40              | -   | ns   |  |

Notes: 1. The ratio SyncCLK/RCLK1 and SyncCLK/TCLK1 must be greater or equal to 2.25/1.

2. Also applies to  $\overline{\text{CD}}$  and  $\overline{\text{CTS}}$  hold time when they are used as external sync signals.

## SCC in NMSI Mode-internal Clock Electrical Specifications

GND = 0  $V_{dc}$ ,  $T_C$  = -55 to +125°C. The electrical specifications in this document are preliminary (See Figure 55 to Figure 57).

|                    |                                                      | 25.0 MHz |     | 33.34 MHz |     |      |

|--------------------|------------------------------------------------------|----------|-----|-----------|-----|------|

| Number             | Characteristic                                       | Min      | Max | Min       | Max | Unit |

| 100 <sup>(1)</sup> | RCLK1 and TCLK1 Frequency                            | 0        | 8.3 | 0         | 11  | MHz  |

| 102                | RCLK1 and TCLK1 Rise/Fall Time                       | -        | -   | -         | -   | ns   |

| 103                | TXD1 Active Delay (From TCLK1 Falling Edge)          | 0        | 30  | 0         | 30  | ns   |

| 104                | RTS1 Active/Inactive Delay (From TCLK1 Falling Edge) | 0        | 30  | 40        | -   | ns   |

| 105                | CTS1 Setup Time to TCLK1 Rising Edge                 | 40       | -   | 40        | -   | ns   |

| 106                | RXD1 Setup Time to RCLK1 Rising Edge                 | 40       | -   | 0         | -   | ns   |

| 107 <sup>(2)</sup> | RXD1 Hold Time from RCLK1 Rising Edge                | 0        | -   | 40        | -   | ns   |

| 108                | CD1 Setup Time to RCLK1 Rising Edge                  | 40       | -   | 0         | 30  | ns   |

Notes: 1. The ratio SyncCLK/RCLK1 and SyncCLK/TCLK1 must be greater or equal to 3/1.

2. Also applies to CD and CTS hold time when they are used as external sync signals.

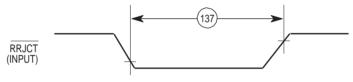

## Figure 55. SCC NMSI Receive

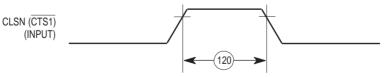

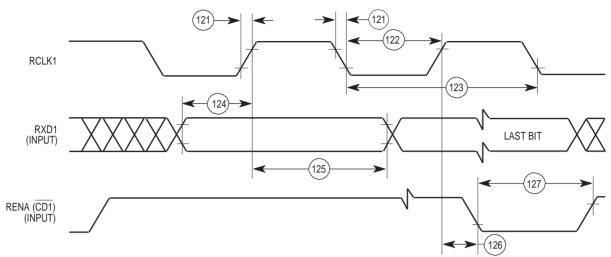

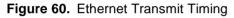

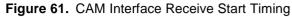

## **Ethernet Electrical Specifications**

GND = 0  $V_{dc}$ ,  $T_C$  = -55 to +125°C. The electrical specifications in this document are preliminary (See Figure 58 to Figure 63).

|                    | Characteristic                                                  | 25.0            | MHz | 33.34           |     |       |

|--------------------|-----------------------------------------------------------------|-----------------|-----|-----------------|-----|-------|

| Number             |                                                                 | Min             | Max | Min             | Max | Unit  |

| 120                | CLSN Width High                                                 | 40              | -   | 40              | -   | ns    |

| 121                | RCLK1 Rise/Fall Time                                            | -               | 15  | -               | 15  | ns    |

| 122                | RCLK1 Width Low                                                 | CLKO1 +<br>5 ns | -   | CLKO1 +<br>5 ns | -   |       |

| 123 <sup>(1)</sup> | RCLK1 Width High                                                | CLKO1           | -   | CLKO1           | -   |       |

| 124                | RXD1 Setup Time                                                 | 20              | -   | 20              | -   | ns    |

| 125                | RXD1 Hold Time                                                  | 5               | -   | 5               | -   | ns    |

| 126                | RENA Active Delay (from RCLK1 rising edge of the last data bit) | 10              | -   | 10              | -   | ns    |

| 127                | RENA Width Low                                                  | 100             | -   | 100             | -   | ns    |

| 128                | TCLK1 Rise/Fall Time                                            | -               | 15  | -               | 15  | ns    |

| 129                | TCLK1 Width Low                                                 | CLKO1 +<br>5 ns | -   | CLKO1 +<br>5 ns | -   |       |

| 130 <sup>(1)</sup> | TCLK1 Width High                                                | CLKO1           | -   | CLKO1           | -   |       |

| 131                | TXD1 Active Delay (from TCLK1 rising edge)                      | 10              | 50  | 10              | 50  | ns    |

| 132                | TXD1 Inactive Delay (from TCLK1 rising edge)                    | 10              | 50  | 10              | 50  | ns    |

| 133                | TENA Active Delay (from TCLK1 rising edge)                      | 10              | 50  | 10              | 50  | ns    |

| 134                | TENA Inactive Delay (from TCLK1 rising edge)                    | 10              | 50  | 10              | 50  | ns    |

| 135                | RSTRT Active Delay (from TCLK1 falling edge)                    | 10              | 50  | 10              | 50  | ns    |

| 136                | RSTRT Inactive Delay (from TCLK1 falling edge)                  | 10              | 50  | 10              | 50  | ns    |

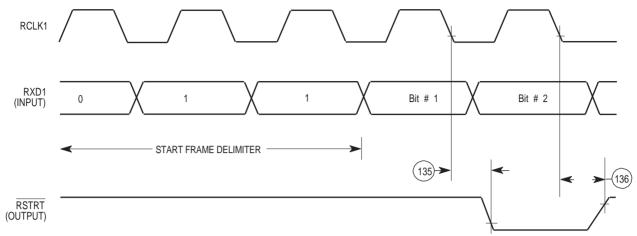

| 137                | RRJCT Width Low                                                 | 1               | -   | 1               | -   | CLKO1 |

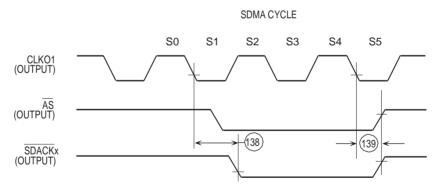

| 138 <sup>(2)</sup> | CLKO1 Low to SDACK Asserted                                     | -               | 20  | -               | 20  | ns    |

| 139 <sup>(2)</sup> | CLKO1 Low to SDACK Negated                                      | -               | 20  | -               | 20  | ns    |

Notes:

SyncCLK/RCLK1 and SyncCLK/TCLK1 must be greater or equal to 2.25/1

SDACK is asserted whenever the SDMA writes the incoming frame DA into memory.

Figure 58. Ethernet Collision Timing

## Figure 59. Ethernet Receive Timing

- Notes: 1. Transmit clock invert (TCI) bit in GSMR is set.

- 2. If RENA is deasserted before TENA, or RENA is not asserted at all during transit, then CSL bit is set in the buffer descripto at the end of frame transmission.

Note: Valid for the ethernet protocol only.

## Figure 62. CAM Interface Reject Timing

Note: Valid for the ethernet protocol only.

Figure 63. SDACK Timing Diagram

Note: SDACKx is asserted when the SDMA writes the received Ethernet frame into memory.

## **SMC Transparent Mode Electrical Specifications**

GND = 0  $V_{DC}$ ,  $T_{C}$  = -55 to +125°C. The electrical specifications in this document are preliminary (See Figure 64).

|                    |                    | 25.0 MHz |     | 33.34 |     |      |

|--------------------|--------------------|----------|-----|-------|-----|------|

| Number             | Characteristic     | Min      | Max | Min   | Max | Unit |

| 150 <sup>(1)</sup> | SMCLK Clock Period | 100      | -   | 100   | -   | ns   |

| 151                | SMCLK Width Low    | 50       | -   | 50    | -   | ns   |

| 151A               | SMCLK Width High   | 50       | -   | 50    | -   | ns   |

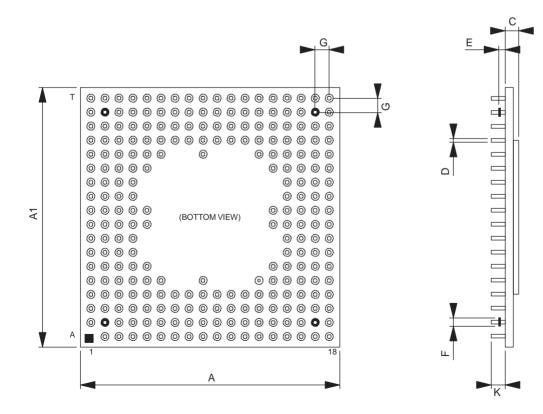

# Package Mechanical Data

## 241-pin – PGA

|     | Inches      |       | Millimeters |       |

|-----|-------------|-------|-------------|-------|

| Dim | Min         | Max   | Min         | Max   |

| А   | 1.840       | 1.880 | 46.74       | 47.75 |

| С   | 0.110       | 0.140 | 2.79        | 3.56  |

| D   | 0.016       | 0.020 | 0.41        | 0.51  |

| Е   | 0.045       | 0.055 | 1.143       | 1.4   |

| F   | 0.045       | 0.055 | 1.143       | 1.4   |

| G   | 0.100 BASIC |       | 2.54 BASIC  |       |

| К   | 0.150       | 0.170 | 3.81        | 4.32  |

## **Atmel Headquarters**

*Corporate Headquarters* 2325 Orchard Parkway San Jose, CA 95131 TEL 1(408) 441-0311 FAX 1(408) 487-2600

Europe

Atmel SarL Route des Arsenaux 41 Casa Postale 80 CH-1705 Fribourg Switzerland TEL (41) 26-426-5555 FAX (41) 26-426-5500

#### Asia

Atmel Asia, Ltd. Room 1219 Chinachem Golden Plaza 77 Mody Road Tsimhatsui East Kowloon Hong Kong TEL (852) 2721-9778 FAX (852) 2722-1369

#### Japan

Atmel Japan K.K. 9F, Tonetsu Shinkawa Bldg. 1-24-8 Shinkawa Chuo-ku, Tokyo 104-0033 Japan TEL (81) 3-3523-3551 FAX (81) 3-3523-7581

## **Atmel Operations**

*Memory* Atmel Corporate 2325 Orchard Parkway San Jose, CA 95131 TEL 1(408) 436-4270 FAX 1(408) 436-4314

Microcontrollers Atmel Corporate 2325 Orchard Parkway San Jose, CA 95131 TEL 1(408) 436-4270 FAX 1(408) 436-4314

Atmel Nantes La Chantrerie BP 70602 44306 Nantes Cedex 3, France TEL (33) 2-40-18-18-18 FAX (33) 2-40-18-19-60

ASIC/ASSP/Smart Cards Atmel Rousset Zone Industrielle 13106 Rousset Cedex, France TEL (33) 4-42-53-60-00 FAX (33) 4-42-53-60-01

Atmel Colorado Springs 1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906 TEL 1(719) 576-3300 FAX 1(719) 540-1759

Atmel Smart Card ICs Scottish Enterprise Technology Park Maxwell Building East Kilbride G75 0QR, Scotland TEL (44) 1355-803-000 FAX (44) 1355-242-743 **RF**/Automotive

Atmel Heilbronn Theresienstrasse 2 Postfach 3535 74025 Heilbronn, Germany TEL (49) 71-31-67-0 FAX (49) 71-31-67-2340

Atmel Colorado Springs 1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906 TEL 1(719) 576-3300 FAX 1(719) 540-1759

Biometrics/Imaging/Hi-Rel MPU/ High Speed Converters/RF Datacom Atmel Grenoble Avenue de Rochepleine BP 123 38521 Saint-Egreve Cedex, France TEL (33) 4-76-58-30-00 FAX (33) 4-76-58-34-80

*e-mail* literature@atmel.com

Web Site http://www.atmel.com

#### © Atmel Corporation 2002.

Atmel Corporation makes no warranty for the use of its products other than those expressly contained in the Company's standard warranty which is detailed in Atmel's Terms and Conditions located on the Company's web site. The Company assumes no responsibility for any errors which may appear in this document, reserves the right to change devices or specifications detailed herein at any time without notice, and does not make any commitment to update the information contained herein. No licenses to patents or other intellectual property of Atmel are granted by the Company in connection with the sale of Atmel products, expessly or by implication. Atmel's products are not authorized for use as critical components in life support devices or systems.

ATMEL® is the registered trademarks of Atmel.

Other terms and product names may be the trademarks of others.