Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 40MHz                                                                      |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 48KB (24K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 1K x 8                                                                     |

| RAM Size                   | 3.25K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                                |

| Data Converters            | A/D 8x10b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 28-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f2585t-i-so |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| File Name | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | Value on POR, BOR | Details<br>on page: |

|-----------|---------|---------|---------|---------|---------|---------|---------|---------|-------------------|---------------------|

| TXB1SIDL  | SID2    | SID1    | SID0    | _       | EXIDE   | _       | EID17   | EID16   | xxx- x-xx         | 54, 283             |

| TXB1SIDH  | SID10   | SID9    | SID8    | SID7    | SID6    | SID5    | SID4    | SID3    | XXXX XXXX         | 54, 283             |

| TXB1CON   | TXBIF   | TXABT   | TXLARB  | TXERR   | TXREQ   | -       | TXPRI1  | TXPRI0  | 0000 0-00         | 54, 282             |

| TXB2D7    | TXB2D77 | TXB2D76 | TXB2D75 | TXB2D74 | TXB2D73 | TXB2D72 | TXB2D71 | TXB2D70 | XXXX XXXX         | 54, 284             |

| TXB2D6    | TXB2D67 | TXB2D66 | TXB2D65 | TXB2D64 | TXB2D63 | TXB2D62 | TXB2D61 | TXB2D60 | XXXX XXXX         | 54, 284             |

| TXB2D5    | TXB2D57 | TXB2D56 | TXB2D55 | TXB2D54 | TXB2D53 | TXB2D52 | TXB2D51 | TXB2D50 | XXXX XXXX         | 54, 284             |

| TXB2D4    | TXB2D47 | TXB2D46 | TXB2D45 | TXB2D44 | TXB2D43 | TXB2D42 | TXB2D41 | TXB2D40 | XXXX XXXX         | 54, 284             |

| TXB2D3    | TXB2D37 | TXB2D36 | TXB2D35 | TXB2D34 | TXB2D33 | TXB2D32 | TXB2D31 | TXB2D30 | xxxx xxxx         | 54, 284             |

| TXB2D2    | TXB2D27 | TXB2D26 | TXB2D25 | TXB2D24 | TXB2D23 | TXB2D22 | TXB2D21 | TXB2D20 | XXXX XXXX         | 54, 284             |

| TXB2D1    | TXB2D17 | TXB2D16 | TXB2D15 | TXB2D14 | TXB2D13 | TXB2D12 | TXB2D11 | TXB2D10 | XXXX XXXX         | 55, 284             |

| TXB2D0    | TXB2D07 | TXB2D06 | TXB2D05 | TXB2D04 | TXB2D03 | TXB2D02 | TXB2D01 | TXB2D00 | XXXX XXXX         | 55, 284             |

| TXB2DLC   | _       | TXRTR   | —       | —       | DLC3    | DLC2    | DLC1    | DLC0    | -x xxxx           | 55, 285             |

| TXB2EIDL  | EID7    | EID6    | EID5    | EID4    | EID3    | EID2    | EID1    | EID0    | xxxx xxxx         | 55, 284             |

| TXB2EIDH  | EID15   | EID14   | EID13   | EID12   | EID11   | EID10   | EID9    | EID8    | xxxx xxxx         | 55, 283             |

| TXB2SIDL  | SID2    | SID1    | SID0    | _       | EXIDE   | _       | EID17   | EID16   | xxxx x-xx         | 55, 283             |

| TXB2SIDH  | SID10   | SID9    | SID8    | SID7    | SID6    | SID5    | SID4    | SID3    | xxx- x-xx         | 55, 283             |

| TXB2CON   | TXBIF   | TXABT   | TXLARB  | TXERR   | TXREQ   | _       | TXPRI1  | TXPRI0  | 0000 0-00         | 55, 282             |

| RXM1EIDL  | EID7    | EID6    | EID5    | EID4    | EID3    | EID2    | EID1    | EID0    | xxxx xxxx         | 55, 304             |

| RXM1EIDH  | EID15   | EID14   | EID13   | EID12   | EID11   | EID10   | EID9    | EID8    | xxxx xxxx         | 55, 304             |

| RXM1SIDL  | SID2    | SID1    | SID0    | _       | EXIDEN  | _       | EID17   | EID16   | xxx- x-xx         | 55, 304             |

| RXM1SIDH  | SID10   | SID9    | SID8    | SID7    | SID6    | SID5    | SID4    | SID3    | xxxx xxxx         | 55, 304             |

| RXM0EIDL  | EID7    | EID6    | EID5    | EID4    | EID3    | EID2    | EID1    | EID0    | xxxx xxxx         | 55, 304             |

| RXM0EIDH  | EID15   | EID14   | EID13   | EID12   | EID11   | EID10   | EID9    | EID8    | xxxx xxxx         | 55, 304             |

| RXM0SIDL  | SID2    | SID1    | SID0    | _       | EXIDEN  | _       | EID17   | EID16   | xxx- x-xx         | 55, 304             |

| RXM0SIDH  | SID10   | SID9    | SID8    | SID7    | SID6    | SID5    | SID4    | SID3    | xxxx xxxx         | 55, 303             |

| RXF5EIDL  | EID7    | EID6    | EID5    | EID4    | EID3    | EID2    | EID1    | EID0    | xxxx xxxx         | 55, 303             |

| RXF5EIDH  | EID15   | EID14   | EID13   | EID12   | EID11   | EID10   | EID9    | EID8    | xxxx xxxx         | 55, 303             |

| RXF5SIDL  | SID2    | SID1    | SID0    | _       | EXIDEN  | _       | EID17   | EID16   | xxx- x-xx         | 55, 302             |

| RXF5SIDH  | SID10   | SID9    | SID8    | SID7    | SID6    | SID5    | SID4    | SID3    | xxxx xxxx         | 55, 302             |

| RXF4EIDL  | EID7    | EID6    | EID5    | EID4    | EID3    | EID2    | EID1    | EID0    | xxxx xxxx         | 55, 303             |

| RXF4EIDH  | EID15   | EID14   | EID13   | EID12   | EID11   | EID10   | EID9    | EID8    | xxxx xxxx         | 55, 303             |

| RXF4SIDL  | SID2    | SID1    | SID0    | —       | EXIDEN  | —       | EID17   | EID16   | xxx- x-xx         | 55, 302             |

| RXF4SIDH  | SID10   | SID9    | SID8    | SID7    | SID6    | SID5    | SID4    | SID3    | xxxx xxxx         | 55, 302             |

| RXF3EIDL  | EID7    | EID6    | EID5    | EID4    | EID3    | EID2    | EID1    | EID0    | xxxx xxxx         | 55, 303             |

| RXF3EIDH  | EID15   | EID14   | EID13   | EID12   | EID11   | EID10   | EID9    | EID8    | xxxx xxxx         | 55, 303             |

| RXF3SIDL  | SID2    | SID1    | SID0    | —       | EXIDEN  | _       | EID17   | EID16   | xxx- x-xx         | 55, 302             |

| RXF3SIDH  | SID10   | SID9    | SID8    | SID7    | SID6    | SID5    | SID4    | SID3    | xxxx xxxx         | 55, 302             |

| RXF2EIDL  | EID7    | EID6    | EID5    | EID4    | EID3    | EID2    | EID1    | EID0    | xxxx xxxx         | 55, 303             |

| RXF2EIDH  | EID15   | EID14   | EID13   | EID12   | EID11   | EID10   | EID9    | EID8    | xxxx xxxx         | 55, 303             |

| RXF2SIDL  | SID2    | SID1    | SID0    | —       | EXIDEN  | —       | EID17   | EID16   | xxx- x-xx         | 55, 302             |

| RXF2SIDH  | SID10   | SID9    | SID8    | SID7    | SID6    | SID5    | SID4    | SID3    | xxxx xxxx         | 55, 302             |

| TABLE 5-2: REGISTER FILE SUMMARY (PIC18F2585/2680/4585/4680) (CONTINUED | TABLE 5-2: | REGISTER FILE SUMMARY | (PIC18F2585/2680/4585/4680) | (CONTINUED) |

|-------------------------------------------------------------------------|------------|-----------------------|-----------------------------|-------------|

|-------------------------------------------------------------------------|------------|-----------------------|-----------------------------|-------------|

**Legend:** x = unknown, u = unchanged, - = unimplemented, q = value depends on condition **Note 1:** Bit 21 of the PC is only available in Test mode and Serial Programming modes.

2: The SBOREN bit is only available when CONFIG2L<1:0> = 01; otherwise, it is disabled and reads as '0'. See Section 4.4 "Brown-out Reset (BOR)".

3: These registers and/or bits are not implemented on PIC18F2X8X devices and are read as '0'. Reset values are shown for PIC18F4X8X devices; individual unimplemented bits should be interpreted as '---'.

4: The PLLEN bit is only available in specific oscillator configuration; otherwise, it is disabled and reads as '0'. See Section 2.6.4 "PLL in INTOSC Modes".

5: The RE3 bit is only available when Master Clear Reset is disabled (CONFIG3H<7> = 0); otherwise, RE3 reads as '0'. This bit is read-only.

**6:** RA6/RA7 and their associated latch and direction bits are individually configured as port pins based on various primary oscillator modes. When disabled, these bits read as '0'.

7: CAN bits have multiple functions depending on the selected mode of the CAN module.

8: This register reads all '0's until the ECAN<sup>™</sup> technology is set up in Mode 1 or Mode 2.

9: These registers are available on PIC18F4X8X devices only.

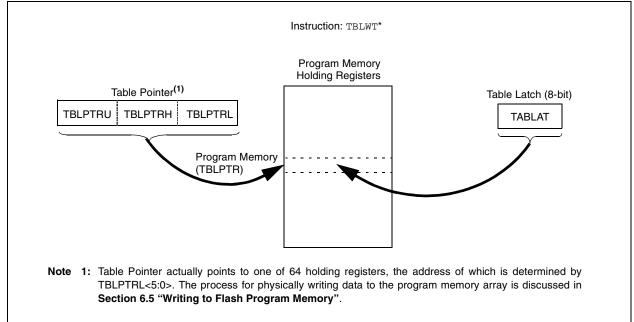

#### FIGURE 6-2: TABLE WRITE OPERATION

# 6.2 Control Registers

Several control registers are used in conjunction with the TBLRD and TBLWT instructions. These include the:

- EECON1 register

- EECON2 register

- TABLAT register

- TBLPTR registers

#### 6.2.1 EECON1 AND EECON2 REGISTERS

The EECON1 register (Register 6-1) is the control register for memory accesses. The EECON2 register is not a physical register; it is used exclusively in the memory write and erase sequences. Reading EECON2 will read all '0's.

The EEPGD control bit determines if the access will be a program or data EEPROM memory access. When clear, any subsequent operations will operate on the data EEPROM memory. When set, any subsequent operations will operate on the program memory.

The CFGS control bit determines if the access will be to the Configuration/Calibration registers or to program memory/data EEPROM memory. When set, subsequent operations will operate on Configuration registers regardless of EEPGD (see **Section 24.0 "Special Features of the CPU"**). When clear, memory selection access is determined by EEPGD. The FREE bit, when set, will allow a program memory erase operation. When FREE is set, the erase operation is initiated on the next WR command. When FREE is clear, only writes are enabled.

The WREN bit, when set, will allow a write operation. On power-up, the WREN bit is clear. The WRERR bit is set in hardware when the WREN bit is set and cleared when the internal programming timer expires and the write operation is complete.

| Note: | During normal operation, the WRERR is       |  |  |  |  |  |  |  |  |  |

|-------|---------------------------------------------|--|--|--|--|--|--|--|--|--|

|       | read as '1'. This can indicate that a write |  |  |  |  |  |  |  |  |  |

|       | operation was prematurely terminated by     |  |  |  |  |  |  |  |  |  |

|       | a Reset, or a write operation was           |  |  |  |  |  |  |  |  |  |

|       | attempted improperly.                       |  |  |  |  |  |  |  |  |  |

The WR control bit initiates write operations. The bit cannot be cleared, only set, in software; it is cleared in hardware at the completion of the write operation.

Note: The EEIF Interrupt flag bit (PIR2<4>) is set when the write is complete. It must be cleared in software.

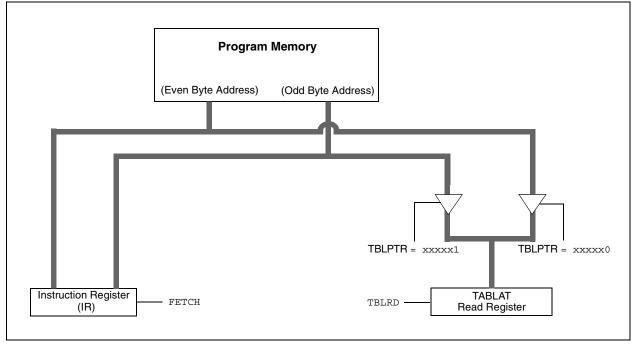

### 6.3 Reading the Flash Program Memory

The TBLRD instruction is used to retrieve data from program memory and places it into data RAM. Table reads from program memory are performed one byte at a time.

TBLPTR points to a byte address in program space. Executing TBLRD places the byte pointed to into TABLAT. In addition, TBLPTR can be modified automatically for the next table read operation.

The internal program memory is typically organized by words. The Least Significant bit of the address selects between the high and low bytes of the word. Figure 6-4 shows the interface between the internal program memory and the TABLAT.

### FIGURE 6-4: READS FROM FLASH PROGRAM MEMORY

#### EXAMPLE 6-1: READING A FLASH PROGRAM MEMORY WORD

|           | MOVLW   | CODE_ADDR_UPPER | ; | Load TBLPTR with the base      |

|-----------|---------|-----------------|---|--------------------------------|

|           | MOVWF   | TBLPTRU         | ; | address of the word            |

|           | MOVLW   | CODE_ADDR_HIGH  |   |                                |

|           | MOVWF   | TBLPTRH         |   |                                |

|           | MOVLW   | CODE_ADDR_LOW   |   |                                |

|           | MOVWF   | TBLPTRL         |   |                                |

| READ_WORD |         |                 |   |                                |

| _         | TBLRD*+ |                 | ; | read into TABLAT and increment |

|           | MOVF    | TABLAT, W       | ; | get data                       |

|           | MOVWF   | WORD EVEN       |   |                                |

|           | TBLRD*+ |                 | ; | read into TABLAT and increment |

|           | MOVF    | TABLAT, W       | ; | get data                       |

|           | MOVF    | WORD ODD        |   |                                |

|           |         | _               |   |                                |

#### EXAMPLE 6-3: WRITING TO FLASH PROGRAM MEMORY

|                     | MOVLW<br>MOVWF | D'64                | ; number of bytes in erase block       |

|---------------------|----------------|---------------------|----------------------------------------|

|                     | MOVWF          | COINTED             |                                        |

|                     |                | COUNTER             |                                        |

|                     | MOVLW          | BUFFER ADDR HIGH    | ; point to buffer                      |

|                     | MOVWF          | FSROH               |                                        |

|                     | MOVLW          | BUFFER ADDR LOW     |                                        |

|                     | MOVWF          | FSROL               |                                        |

|                     | MOVLW          | CODE_ADDR_UPPER     | ; Load TBLPTR with the base            |

|                     | MOVWF          | TBLPTRU             | ; address of the memory block          |

|                     | MOVLW          | CODE_ADDR_HIGH      |                                        |

|                     | MOVWF          | TBLPTRH             |                                        |

|                     | MOVLW          | CODE_ADDR_LOW       |                                        |

|                     | MOVWF          | TBLPTRL             |                                        |

| READ_BLOCK          |                |                     |                                        |

|                     | TBLRD*+        |                     | ; read into TABLAT, and inc            |

|                     | MOVF           | TABLAT, W           | ; get data                             |

|                     | MOVWF          | POSTINCO            | ; store data                           |

|                     | DECFSZ         | COUNTER             | ; done?                                |

|                     | BRA            | READ_BLOCK          | ; repeat                               |

| MODIFY_WORD         |                |                     |                                        |

|                     | MOVLW          | DATA_ADDR_HIGH      | ; point to buffer                      |

|                     | MOVWF          | FSROH               |                                        |

|                     | MOVLW          | DATA_ADDR_LOW       |                                        |

|                     | MOVWF          | FSROL               |                                        |

|                     | MOVLW          | NEW_DATA_LOW        | ; update buffer word                   |

|                     | MOVWF          | POSTINCO            |                                        |

|                     | MOVLW          | NEW_DATA_HIGH       |                                        |

|                     | MOVWF          | INDF0               |                                        |

| ERASE_BLOCK         |                |                     |                                        |

|                     | MOVLW          | CODE_ADDR_UPPER     | ; load TBLPTR with the base            |

|                     | MOVWF          | TBLPTRU             | ; address of the memory block          |

|                     | MOVLW          | CODE_ADDR_HIGH      |                                        |

|                     | MOVWF          | TBLPTRH             |                                        |

|                     | MOVLW          | CODE_ADDR_LOW       |                                        |

|                     | MOVWF          | TBLPTRL             |                                        |

|                     | BSF            | EECON1, EEPGD       | ; point to Flash program memory        |

|                     | BCF            | EECON1, CFGS        | ; access Flash program memory          |

|                     | BSF            | EECON1, WREN        | ; enable write to memory               |

|                     | BSF            | EECON1, FREE        | ; enable Row Erase operation           |

|                     | BCF            | INTCON, GIE         | ; disable interrupts                   |

| Pomired             | MOVLW          | 55h                 | , write EEb                            |

| Required            | MOVWF          | EECON2              | ; write 55h                            |

| Sequence            | MOVLW          | 0AAh<br>FECONO      | write Ollah                            |

|                     | MOVWF          | EECON2              | ; write OAAh                           |

|                     | BSF            | EECON1, WR          | ; start erase (CPU stall)              |

|                     | BSF            | INTCON, GIE         | ; re-enable interrupts                 |

|                     | TBLRD*-        | ייסדיי סררג משפעונס | ; dummy read decrement                 |

|                     | MOVLW          | BUFFER_ADDR_HIGH    | ; point to buffer                      |

|                     | MOVWF          | FSROH               |                                        |

|                     | MOVLW          | BUFFER_ADDR_LOW     |                                        |

| איי ההההוום החדמא   | MOVWF          | FSROL               |                                        |

| WRITE_BUFFER_BAG    |                | D' 64               | ; number of bytes in holding register  |

|                     | MOVLW<br>MOVWF | D'64<br>COUNTER     | , number of bytes in notating register |

| שפדידה פעידה יי∩ טו |                | COUNTER             |                                        |

| WRITE_BYTE_TO_H     | MOVF           | POSTINCO, W         | ; get low byte of buffer data          |

|                     | MOVF           | TABLAT              | ; present data to table latch          |

|                     | TBLWT+*        | 1111111111          | ; write data, perform a short write    |

|                     | IDUMIT.        |                     | ; to internal TBLWT holding register.  |

|                     | DECFSZ         | COUNTER             | ; loop until buffers are full          |

|                     | BRA            | WRITE BYTE TO HREGS | , roop ander parterb are rain          |

|                     | 2141           |                     |                                        |

#### **RCON Register** 9.5

The RCON register contains flag bits which are used to determine the cause of the last Reset or wake-up from Idle or Sleep modes. RCON also contains the IPEN bit which enables interrupt priorities.

| REGISTER 9-13: | RCON: RESET CONTROL REGISTER        |                                                 |               |              |          |              |       |       |  |  |  |  |

|----------------|-------------------------------------|-------------------------------------------------|---------------|--------------|----------|--------------|-------|-------|--|--|--|--|

|                | R/W-0                               | U-0                                             | U-0           | R/W-1        | R-1      | R-1          | R/W-0 | R/W-0 |  |  |  |  |

|                | IPEN                                | SBOREN                                          | _             | RI           | TO       | PD           | POR   | BOR   |  |  |  |  |

|                | bit 7 bit                           |                                                 |               |              |          |              |       |       |  |  |  |  |

|                |                                     |                                                 |               |              |          |              |       |       |  |  |  |  |

| bit 7          | IPEN: Interrupt Priority Enable bit |                                                 |               |              |          |              |       |       |  |  |  |  |

|                |                                     | e priority level                                |               |              |          |              |       |       |  |  |  |  |

|                | 0 = Disabl                          | e priority leve                                 | ls on interru | pts (PIC16C) | XX Compa | tibility moc | le)   |       |  |  |  |  |

| bit 6          | SBOREN:                             | BOR Softwar                                     | e Enable bit  |              |          |              |       |       |  |  |  |  |

|                | For details                         | of bit operation                                | on, see Regi  | ster 4-1.    |          |              |       |       |  |  |  |  |

| bit 5          | Unimplem                            | ented: Read                                     | <b>as</b> '0' |              |          |              |       |       |  |  |  |  |

| bit 4          | RI: RESET                           | Instruction FI                                  | ag bit        |              |          |              |       |       |  |  |  |  |

|                | For details                         | of bit operation                                | on, see Regi  | ster 4-1.    |          |              |       |       |  |  |  |  |

| bit 3          | TO: Watch                           | dog Time-out                                    | Flag bit      |              |          |              |       |       |  |  |  |  |

|                | For details                         | of bit operation                                | on, see Regi  | ster 4-1.    |          |              |       |       |  |  |  |  |

| bit 2          | PD: Power                           | -down Detect                                    | ion Flag bit  |              |          |              |       |       |  |  |  |  |

|                | For details                         | of bit operation                                | on, see Regi  | ster 4-1.    |          |              |       |       |  |  |  |  |

| bit 1          | POR: Pow                            | er-on Reset S                                   | Status bit    |              |          |              |       |       |  |  |  |  |

|                | For details                         | of bit operation                                | on, see Regi  | ster 4-1.    |          |              |       |       |  |  |  |  |

| bit 0          | BOR: Brow                           | vn-out Reset                                    | Status bit    |              |          |              |       |       |  |  |  |  |

|                | For details                         | For details of bit operation, see Register 4-1. |               |              |          |              |       |       |  |  |  |  |

|                |                                     |                                                 |               |              |          |              |       |       |  |  |  |  |

|                | Legend:                             |                                                 |               |              |          |              |       |       |  |  |  |  |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | l bit, read as '0' |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

# 15.0 CAPTURE/COMPARE/PWM (CCP1) MODULES

PIC18F2585/2680 devices have one CCP1 module. PIC18F4585/4680 devices have two CCP1 (Capture/Compare/PWM) modules. CCP1, discussed in this chapter, implements standard Capture, Compare and Pulse-Width Modulation (PWM) modes.

ECCP1 implements an Enhanced PWM mode. The ECCP1 implementation is discussed in Section 16.0 "Enhanced Capture/Compare/PWM (ECCP1) Module". The CCP1 module contains a 16-bit register which can operate as a 16-bit Capture register, a 16-bit Compare register or a PWM Master/Slave Duty Cycle register. For the sake of clarity, all CCP1 module operation in the following sections is described with respect to CCP1, but is equally applicable to ECCP1.

Capture and Compare operations described in this chapter apply to all standard and Enhanced CCP1 modules. The operations of PWM mode, described in **Section 15.4 "PWM Mode**", apply to ECCP1 only.

### REGISTER 15-1: CCP1CON: CAPTURE/COMPARE/PWM CONTROL REGISTER

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|-------|-------|--------|--------|--------|--------|

| —     | —   | DC1B1 | DC1B0 | CCP1M3 | CCP1M2 | CCP1M1 | CCP1M0 |

| bit 7 |     |       |       |        |        |        | bit 0  |

- bit 7-6 Unimplemented: Read as '0'

- bit 5-4 DC1B1:DC1B0: PWM Duty Cycle bit 1 and bit 0 for CCP1 Module

Capture mode: Unused. Compare mode: Unused. <u>PWM mode:</u>

These bits are the two LSbs (bit 1 and bit 0) of the 10-bit PWM duty cycle. The eight MSbs (DC19:DC12) of the duty cycle are found in ECCPR1L.

#### bit 3-0 CCP1M3:CCP1M0: CCP1 Module Mode Select bits

- 0000 = Capture/Compare/PWM disabled (resets CCP1 module)

- 0001 = Reserved

- 0010 = Compare mode, toggle output on match (CCP1IF bit is set)

- 0011 = Reserved

- 0100 = Capture mode, every falling edge or CAN message received (time-stamp)<sup>(1)</sup>

- 0101 = Capture mode, every rising edge or CAN message received (time-stamp)<sup>(1)</sup>

- 0110 = Capture mode, every 4th rising edge or every 4th CAN message received (time-stamp)<sup>(1)</sup>

- 0111 = Capture mode, every 16th rising edge or every 16th CAN message received (time-stamp)<sup>(1)</sup>

- 1000 = Compare mode: initialize CCP1 pin low; on compare match, force CCP1 pin high (CCPIF bit is set)

- 1001 = Compare mode: initialize CCP pin high; on compare match, force CCP1 pin low (CCPIF bit is set)

- 1010 = Compare mode: generate software interrupt on compare match (CCPIF bit is set, CCP1 pin reflects I/O state)

- 1011 = Compare mode: trigger special event, reset timer (TMR1 or TMR3, CCP1IF bit is set) 11xx = PWM mode

- Note 1: Selected by CANCAP (CIOCON<4>) bit; overrides the CCP1 input pin source.

| Legend:       |           |                      |                    |                  |

|---------------|-----------|----------------------|--------------------|------------------|

| R = Readabl   | e bit W = | Writable bit U = Un  | implemented bit, r | ead as '0'       |

| -n = Value at | POR '1' = | Bit is set '0' = Bit | t is cleared x =   | = Bit is unknown |

| Name                    | Bit 7                                         | Bit 6                         | Bit 5         | Bit 4         | Bit 3    | Bit 2   | Bit 1   | Bit 0   | Reset<br>Values<br>on page |  |

|-------------------------|-----------------------------------------------|-------------------------------|---------------|---------------|----------|---------|---------|---------|----------------------------|--|

| INTCON                  | GIE/GIEH                                      | PEIE/GIEL                     | TMR0IE        | INTOIE        | RBIE     | TMR0IF  | INT0IF  | RBIF    | 49                         |  |

| RCON                    | IPEN                                          | SBOREN <sup>(2)</sup>         | -             | RI            | TO       | PD      | POR     | BOR     | 50                         |  |

| PIR1                    | PSPIF                                         | ADIF                          | RCIF          | TXIF          | SSPIF    | CCP1IF  | TMR2IF  | TMR1IF  | 52                         |  |

| PIE1                    | PSPIE                                         | ADIE                          | RCIE          | TXIE          | SSPIE    | CCP1IE  | TMR2IE  | TMR1IE  | 52                         |  |

| IPR1                    | PSPIP                                         | ADIP                          | RCIP          | TXIP          | SSPIP    | CCP1IP  | TMR2IP  | TMR1IP  | 52                         |  |

| TRISB                   | PORTB Da                                      | ta Direction R                | egister       |               |          |         |         |         | 52                         |  |

| TRISC                   | PORTC Da                                      | PORTC Data Direction Register |               |               |          |         |         |         |                            |  |

| TMR2                    | Timer2 Mod                                    | lule Register                 |               |               |          |         |         |         | 50                         |  |

| PR2                     | Timer2 Mod                                    | ule Period Re                 | egister       |               |          |         |         |         | 50                         |  |

| T2CON                   | _                                             | T2OUTPS3                      | T2OUTPS2      | T2OUTPS1      | T2OUTPS0 | TMR2ON  | T2CKPS1 | T2CKPS0 | 50                         |  |

| CCPR1L <sup>(1)</sup>   | Capture/Co                                    | mpare/PWM                     | Register 1 (L | SB)           |          |         |         |         | 51                         |  |

| CCPR1H <sup>(1)</sup>   | Capture/Co                                    | mpare/PWM                     | Register 1 (N | /ISB)         |          |         |         |         | 51                         |  |

| CCP1CON                 | _                                             | _                             | DC1B1         | DC1B0         | CCP1M3   | CCP1M2  | CCP1M1  | CCP1M0  | 51                         |  |

| ECCPR1L <sup>(1)</sup>  | Enhanced Capture/Compare/PWM Register 1 (LSB) |                               |               |               |          |         |         |         |                            |  |

| ECCPR1H <sup>(1)</sup>  | Enhanced (                                    | Capture/Comp                  | are/PWM R     | egister 1 (MS | SB)      |         |         |         | 51                         |  |

| ECCP1CON <sup>(1)</sup> | EPWM1M1                                       | EPWM1M0                       | EDC1B1        | EDC1B0        | ECCP1M3  | ECCP1M2 | ECCP1M1 | ECCP1M0 | 51                         |  |

#### TABLE 15-5: REGISTERS ASSOCIATED WITH PWM AND TIMER2

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by PWM or Timer2.

Note 1: These registers are unimplemented on PIC18F2X8X devices.

**2:** The SBOREN bit is only available when CONFIG2L<1:0> = 01; otherwise, it is disabled and reads as '0'.

In addition to the expanded range of modes available through the CCP1CON register, the ECCP1 module has two additional registers associated with Enhanced PWM operation and auto-shutdown features. They are:

- ECCP1DEL (Dead-band delay)

- ECCP1AS (Auto-shutdown configuration)

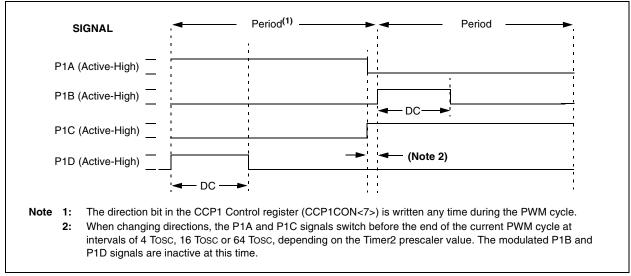

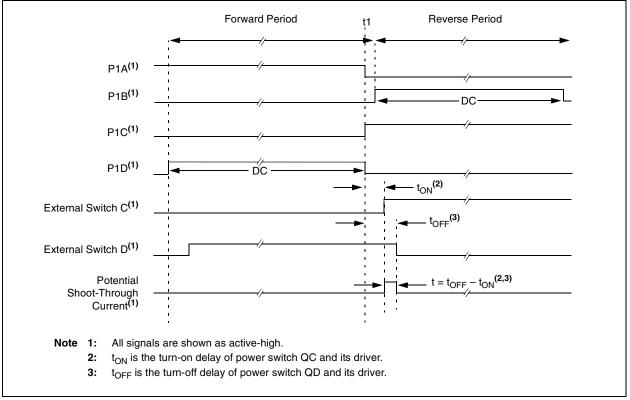

# 16.1 ECCP1 Outputs and Configuration

The Enhanced CCP1 module may have up to four PWM outputs, depending on the selected operating mode. These outputs, designated P1A through P1D, are multiplexed with I/O pins on PORTC and PORTD. The outputs that are active depend on the CCP1 operating mode selected. The pin assignments are summarized in Table 16-1.

To configure the I/O pins as PWM outputs, the proper PWM mode must be selected by setting the EPWM1M1:EPWM1M0 and CCP1M3:CCP1M0 bits. The appropriate TRISC and TRISD direction bits for the port pins must also be set as outputs.

#### 16.1.1 ECCP1 MODULES AND TIMER RESOURCES

Like the standard CCP1 modules, the ECCP1 module can utilize Timers 1, 2 or 3, depending on the mode selected. Timer1 and Timer3 are available for modules in Capture or Compare modes, while Timer2 is available for modules in PWM mode. Interactions between the standard and Enhanced CCP1 modules are identical to those described for standard CCP1 modules. Additional details on timer resources are provided in Section 15.1.1 "CCP1 Modules and Timer Resources".

# 16.2 Capture and Compare Modes

Except for the operation of the special event trigger discussed below, the Capture and Compare modes of the ECCP1 module are identical in operation to that of CCP1. These are discussed in detail in Section 15.2 "Capture Mode" and Section 15.3 "Compare Mode".

### 16.2.1 SPECIAL EVENT TRIGGER

The special event trigger output of ECCP1 resets the TMR1 or TMR3 register pair, depending on which timer resource is currently selected. This allows the ECCP1 register to effectively be a 16-bit programmable period register for Timer1 or Timer3. The special event trigger for ECCP1 can also start an A/D conversion. In order to start the conversion, the A/D converter must be previously enabled.

### 16.3 Standard PWM Mode

When configured in Single Output mode, the ECCP1 module functions identically to the standard CCP1 module in PWM mode, as described in **Section 15.4 "PWM Mode"**. This is also sometimes referred to as "Compatible CCP1" mode, as in Table 16-1.

Note: When setting up single output PWM operations, users are free to use either of the processes described in Section 15.4.4 "Setup for PWM Operation" or Section 16.4.9 "Setup for PWM Operation". The latter is more generic but will work for either single or multi-output PWM.

| ECCP1 Mode                   | CCP1CON<br>Configuration | n RD4 RD5 |          | RD6      | RD7      |  |  |  |  |  |  |

|------------------------------|--------------------------|-----------|----------|----------|----------|--|--|--|--|--|--|

| All PIC18F4585/4680 devices: |                          |           |          |          |          |  |  |  |  |  |  |

| Compatible CCP1              | 00xx 11xx                | CCP1      | RD5/PSP5 | RD6/PSP6 | RD7/PSP7 |  |  |  |  |  |  |

| Dual PWM                     | 10xx 11xx                | P1A       | P1B      | RD6/PSP6 | RD7/PSP7 |  |  |  |  |  |  |

| Quad PWM                     | x1xx 11xx                | P1A       | P1B      | P1C      | P1D      |  |  |  |  |  |  |

#### TABLE 16-1: PIN ASSIGNMENTS FOR VARIOUS ECCP1 MODES

**Legend:** x = Don't care. Shaded cells indicate pin assignments not used by ECCP1 in a given mode.

# 19.6 A/D Conversions

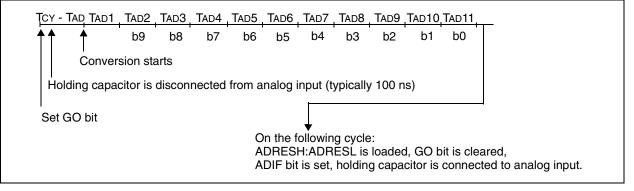

Figure 19-3 shows the operation of the A/D converter after the GO bit has been set and the ACQT2:ACQT0 bits are cleared. A conversion is started after the following instruction to allow entry into Sleep mode before the conversion begins.

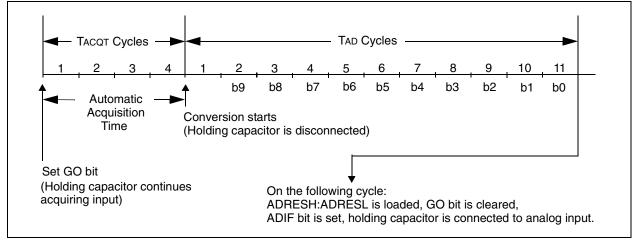

Figure 19-4 shows the operation of the A/D converter after the GO bit has been set and the ACQT2:ACQT0 bits are set to '010' and selecting a 4 TAD acquisition time before the conversion starts.

Clearing the GO/DONE bit during a conversion will abort the current conversion. The A/D Result register pair will NOT be updated with the partially completed A/D conversion sample. This means the ADRESH:ADRESL registers will continue to contain the value of the last completed conversion (or the last value written to the ADRESH:ADRESL registers).

After the A/D conversion is completed or aborted, a 2 TAD wait is required before the next acquisition can be started. After this wait, acquisition on the selected channel is automatically started.

**Note:** The GO/DONE bit should **NOT** be set in the same instruction that turns on the A/D.

### FIGURE 19-3: A/D CONVERSION TAD CYCLES (ACQT<2:0> = 000, TACQ = 0)

### FIGURE 19-4: A/D CONVERSION TAD CYCLES (ACQT<2:0> = 010, TACQ = 4 TAD)

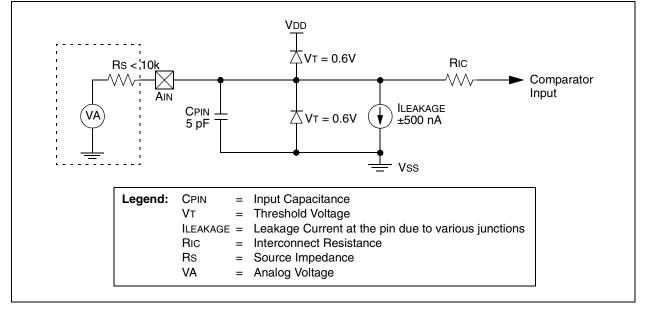

# 20.9 Analog Input Connection Considerations

A simplified circuit for an analog input is shown in Figure 20-4. Since the analog pins are connected to a digital output, they have reverse biased diodes to VDD and Vss. The analog input, therefore, must be between Vss and VDD. If the input voltage deviates from this

range by more than 0.6V in either direction, one of the diodes is forward biased and a latch-up condition may occur. A maximum source impedance of 10 k $\Omega$  is recommended for the analog sources. Any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have very little leakage current.

# FIGURE 20-4: COMPARATOR ANALOG INPUT MODEL

### TABLE 20-1: REGISTERS ASSOCIATED WITH COMPARATOR MODULE

| Name                                                                            | Bit 7                | Bit 6                | Bit 5                     | Bit 4  | Bit 3 | Bit 2  | Bit 1  | Bit 0                  | Reset<br>Values<br>on page |

|---------------------------------------------------------------------------------|----------------------|----------------------|---------------------------|--------|-------|--------|--------|------------------------|----------------------------|

| CMCON <sup>(3)</sup>                                                            | C2OUT                | C1OUT                | C2INV                     | C1INV  | CIS   | CM2    | CM1    | CM0                    | 51                         |

| CVRCON <sup>(3)</sup>                                                           | CVREN                | CVROE                | CVRR                      | CVRSS  | CVR3  | CVR2   | CVR1   | CVR0                   | 51                         |

| INTCON                                                                          | GIE/GIEH             | PEIE/GIEL            | TMR0IE                    | INT0IE | RBIE  | TMR0IF | INT0IF | RBIF                   | 52                         |

| IPR2                                                                            | OSCFIP               | CMIP <sup>(2)</sup>  | _                         | EEIP   | BCLIP | HLVDIP | TMR3IP | ECCP1IP <sup>(2)</sup> | 51                         |

| PIR2                                                                            | OSCFIF               | CMIF <sup>(2)</sup>  | —                         | EEIF   | BCLIF | HLVDIF | TMR3IF | ECCP1IF <sup>(2)</sup> | 51                         |

| PIE2                                                                            | OSCFIE               | CMIE <sup>(2)</sup>  | _                         | EEIE   | BCLIE | HLVDIE | TMR3IE | ECCP1IE <sup>(2)</sup> | 52                         |

| PORTA                                                                           | RA7 <sup>(1)</sup>   | RA6 <sup>(1)</sup>   | RA5                       | RA4    | RA3   | RA2    | RA1    | RA0                    | 52                         |

| LATA                                                                            | LATA7 <sup>(1)</sup> | LATA6 <sup>(1)</sup> | LATA Data Output Register |        |       |        |        |                        | 52                         |

| TRISA TRISA7 <sup>(1)</sup> TRISA6 <sup>(1)</sup> PORTA Data Direction Register |                      |                      |                           |        |       |        |        | 52                     |                            |

**Legend:** — = unimplemented, read as '0'. Shaded cells are unused by the comparator module.

Note 1: PORTA pins are enabled based on oscillator configuration.

2: These bits are available in PIC18F4X8X devices and reserved in PIC18F2X8X devices.

3: These registers are unimplemented on PIC18F2X8X devices.

### FIGURE 21-1: COMPARATOR VOLTAGE REFERENCE BLOCK DIAGRAM

# 21.2 Voltage Reference Accuracy/Error

The full range of voltage reference cannot be realized due to the construction of the module. The transistors on the top and bottom of the resistor ladder network (Figure 21-1) keep CVREF from approaching the reference source rails. The voltage reference is derived from the reference source; therefore, the CVREF output changes with fluctuations in that source. The tested absolute accuracy of the voltage reference can be found in **Section 27.0 "Electrical Characteristics"**.

# 21.3 Operation During Sleep

When the device wakes up from Sleep through an interrupt or a Watchdog Timer time-out, the contents of the CVRCON register are not affected. To minimize current consumption in Sleep mode, the voltage reference should be disabled.

# 21.4 Effects of a Reset

A device Reset disables the voltage reference by clearing bit CVREN (CVRCON<7>). This Reset also disconnects the reference from the RA0 pin by clearing bit CVROE (CVRCON<6>) and selects the high-voltage range by clearing bit CVRR (CVRCON<5>). The CVR value select bits are also cleared.

# 21.5 Connection Considerations

The voltage reference module operates independently of the comparator module. The output of the reference generator may be connected to the RA0 pin if the TRISA<0> bit and the CVROE bit are both set. Enabling the voltage reference output onto the RA0 pin, with an input signal present, will increase current consumption. Connecting RA0 as a digital output with CVRSS enabled will also increase current consumption.

The RA0 pin can be used as a simple D/A output with limited drive capability. Due to the limited current drive capability, a buffer must be used on the voltage reference output for external connections to VREF. Figure 21-2 shows an example buffering technique.

#### 23.15.5 BUS ACTIVITY WAKE-UP INTERRUPT

When the PIC18F2585/2680/4585/4680 devices are in Sleep mode and the bus activity wake-up interrupt is enabled, an interrupt will be generated and the WAKIF bit will be set when activity is detected on the CAN bus. This interrupt causes the PIC18F2585/2680/4585/ 4680 devices to exit Sleep mode. The interrupt is reset by the MCU, clearing the WAKIF bit.

#### 23.15.6 ERROR INTERRUPT

When the error interrupt is enabled, an interrupt is generated if an overflow condition occurs or if the error state of the transmitter or receiver has changed. The error flags in COMSTAT will indicate one of the following conditions.

#### 23.15.6.1 Receiver Overflow

An overflow condition occurs when the MAB has assembled a valid received message (the message meets the criteria of the acceptance filters) and the receive buffer associated with the filter is not available for loading of a new message. The associated RXBnOVFL bit in the COMSTAT register will be set to indicate the overflow condition. This bit must be cleared by the MCU.

#### 23.15.6.2 Receiver Warning

The receive error counter has reached the MCU warning limit of 96.

#### 23.15.6.3 Transmitter Warning

The transmit error counter has reached the MCU warning limit of 96.

#### 23.15.6.4 Receiver Bus Passive

The receive error counter has exceeded the errorpassive limit of 127 and the device has gone to error-passive state.

#### 23.15.6.5 Transmitter Bus Passive

The transmit error counter has exceeded the errorpassive limit of 127 and the device has gone to error-passive state.

#### 23.15.6.6 Bus-Off

The transmit error counter has exceeded 255 and the device has gone to bus-off state.

#### 23.15.6.7 Interrupt Acknowledge

Interrupts are directly associated with one or more status flags in the PIR register. Interrupts are pending as long as one of the flags is set. Once an interrupt flag is set by the device, the flag can not be reset by the microcontroller until the interrupt condition is removed.

# 25.0 INSTRUCTION SET SUMMARY

PIC18F2585/2680/4585/4680 devices incorporate the standard set of 75 PIC18 core instructions, as well as an extended set of 8 new instructions, for the optimization of code that is recursive or that utilizes a software stack. The extended set is discussed later in this section.

### 25.1 Standard Instruction Set

The standard PIC18 instruction set adds many enhancements to the previous PIC<sup>®</sup> MCU instruction sets, while maintaining an easy migration from these PIC MCU instruction sets. Most instructions are a single program memory word (16 bits), but there are four instructions that require two program memory locations.

Each single-word instruction is a 16-bit word divided into an opcode, which specifies the instruction type and one or more operands, which further specify the operation of the instruction.

The instruction set is highly orthogonal and is grouped into four basic categories:

- Byte-oriented operations

- Bit-oriented operations

- Literal operations

- Control operations

The PIC18 instruction set summary in Table 25-2 lists **byte-oriented**, **bit-oriented**, **literal** and **control** operations. Table 25-1 shows the opcode field descriptions.

Most byte-oriented instructions have three operands:

- 1. The file register (specified by 'f')

- 2. The destination of the result (specified by 'd')

- 3. The accessed memory (specified by 'a')

The file register designator 'f' specifies which file register is to be used by the instruction. The destination designator 'd' specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the WREG register. If 'd' is one, the result is placed in the file register specified in the instruction.

All **bit-oriented** instructions have three operands:

- 1. The file register (specified by 'f')

- 2. The bit in the file register (specified by 'b')

- 3. The accessed memory (specified by 'a')

The bit field designator 'b' selects the number of the bit affected by the operation, while the file register designator 'f' represents the number of the file in which the bit is located. The **literal** instructions may use some of the following operands:

- A literal value to be loaded into a file register (specified by 'k')

- The desired FSR register to load the literal value into (specified by 'f')

- No operand required (specified by '—')

The **control** instructions may use some of the following operands:

- A program memory address (specified by 'n')

- The mode of the CALL or RETURN instructions (specified by 's')

- The mode of the table read and table write instructions (specified by 'm')

- No operand required (specified by '—')

All instructions are a single word, except for four double-word instructions. These instructions were made double-word to contain the required information in 32 bits. In the second word, the 4 MSbs are '1's. If this second word is executed as an instruction (by itself), it will execute as a NOP.

All single-word instructions are executed in a single instruction cycle, unless a conditional test is true or the program counter is changed as a result of the instruction. In these cases, the execution takes two instruction cycles with the additional instruction cycle(s) executed as a NOP.

The double-word instructions execute in two instruction cycles.

One instruction cycle consists of four oscillator periods. Thus, for an oscillator frequency of 4 MHz, the normal instruction execution time is 1  $\mu$ s. If a conditional test is true, or the program counter is changed as a result of an instruction, the instruction execution time is 2  $\mu$ s. Two-word branch instructions (if true) would take 3  $\mu$ s.

Figure 25-1 shows the general formats that the instructions can have. All examples use the convention 'nnh' to represent a hexadecimal number.

The Instruction Set Summary, shown in Table 25-2, lists the standard instructions recognized by the Microchip MPASM<sup>™</sup> Assembler.

**Section 25.1.1 "Standard Instruction Set**" provides a description of each instruction.

| POP                                                                                                                                                                                                                                                                                                       | Рор Тор              | of Return St       | ack       |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--------------------|-----------|--|--|--|--|

| Syntax:                                                                                                                                                                                                                                                                                                   | POP                  |                    |           |  |  |  |  |

| Operands:                                                                                                                                                                                                                                                                                                 | None                 |                    |           |  |  |  |  |

| Operation:                                                                                                                                                                                                                                                                                                | $(TOS) \to b$        | it bucket          |           |  |  |  |  |

| Status Affected:                                                                                                                                                                                                                                                                                          | None                 |                    |           |  |  |  |  |

| Encoding:                                                                                                                                                                                                                                                                                                 | 0000                 | 0000 00            | 00 0110   |  |  |  |  |

| Description:<br>The TOS value is pulled off the return<br>stack and is discarded. The TOS value<br>then becomes the previous value that<br>was pushed onto the return stack.<br>This instruction is provided to enable<br>the user to properly manage the return<br>stack to incorporate a software stack |                      |                    |           |  |  |  |  |

| Words:                                                                                                                                                                                                                                                                                                    | 1                    | 1                  |           |  |  |  |  |

| Cycles:                                                                                                                                                                                                                                                                                                   | 1                    |                    |           |  |  |  |  |

| Q Cycle Activity:                                                                                                                                                                                                                                                                                         |                      |                    |           |  |  |  |  |

| Q1                                                                                                                                                                                                                                                                                                        | Q2                   | Q3                 | Q4        |  |  |  |  |

| Decode                                                                                                                                                                                                                                                                                                    | No                   | POP TOS            | No        |  |  |  |  |

|                                                                                                                                                                                                                                                                                                           | operation            | value              | operation |  |  |  |  |

| Example:                                                                                                                                                                                                                                                                                                  | POP<br>GOTO          | NEW                |           |  |  |  |  |

| Before Instru<br>TOS<br>Stack (1                                                                                                                                                                                                                                                                          | ction<br>level down) | = 0031A<br>= 01433 |           |  |  |  |  |

| After Instruct<br>TOS<br>PC                                                                                                                                                                                                                                                                               | ion                  | = 01433<br>= NEW   | 2h        |  |  |  |  |

| PUS   | н                                         | Push Top                                                     | Push Top of Return Stack                                                                                                                                                                                                                    |                |    |               |  |  |

|-------|-------------------------------------------|--------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|----|---------------|--|--|

| Synta | ax:                                       | PUSH                                                         | PUSH                                                                                                                                                                                                                                        |                |    |               |  |  |

| Oper  | ands:                                     | None                                                         |                                                                                                                                                                                                                                             |                |    |               |  |  |

| Oper  | ation:                                    | $(PC + 2) \rightarrow$                                       | TOS                                                                                                                                                                                                                                         |                |    |               |  |  |

| Statu | is Affected:                              | None                                                         |                                                                                                                                                                                                                                             |                |    |               |  |  |

| Enco  | oding:                                    | 0000                                                         | 0000                                                                                                                                                                                                                                        | 000            | 0  | 0101          |  |  |

| Desc  | ription:                                  | the return s<br>value is pus<br>This instruc<br>software sta | The PC + 2 is pushed onto the top of<br>the return stack. The previous TOS<br>value is pushed down on the stack.<br>This instruction allows implementing a<br>software stack by modifying TOS and<br>then pushing it onto the return stack. |                |    |               |  |  |

| Word  | ds:                                       | 1                                                            | 1                                                                                                                                                                                                                                           |                |    |               |  |  |

| Cycle | es:                                       | 1                                                            | 1                                                                                                                                                                                                                                           |                |    |               |  |  |

| QC    | ycle Activity:                            |                                                              |                                                                                                                                                                                                                                             |                |    |               |  |  |

|       | Q1                                        | Q2                                                           | Q3                                                                                                                                                                                                                                          |                | Q4 | Q4            |  |  |

|       | Decode                                    | PUSH<br>PC + 2 onto<br>return stack                          | N<br>opera                                                                                                                                                                                                                                  | •              | ор | No<br>eration |  |  |

| Exar  | nple:                                     | PUSH                                                         |                                                                                                                                                                                                                                             |                |    |               |  |  |

|       | Before Instruc<br>TOS<br>PC               | tion                                                         | =<br>=                                                                                                                                                                                                                                      | 345Ah<br>0124h |    |               |  |  |

|       | After Instructio<br>PC<br>TOS<br>Stack (1 | =<br>=<br>=                                                  | 0126h<br>0126h<br>345Ah                                                                                                                                                                                                                     |                |    |               |  |  |

| RRN         | ICF                                       | Ro                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Rotate Right f (No Carry)             |     |                                    |     |   |                                                                                                                                        |  |

|-------------|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-----|------------------------------------|-----|---|----------------------------------------------------------------------------------------------------------------------------------------|--|

| Synta       | ax:                                       | RR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | NCF                                   | f { | ,d {,a}}                           |     |   |                                                                                                                                        |  |

| Oper        | rands:                                    | d∈                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0 ≤ f ≤ 255<br>d ∈ [0,1]<br>a ∈ [0,1] |     |                                    |     |   |                                                                                                                                        |  |

| Oper        | ration:                                   | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ו>) → (<br>)>) → (                    |     | st <n 1<br="" –="">st&lt;7&gt;</n> | >,  |   |                                                                                                                                        |  |

| Statu       | is Affected:                              | Ν, 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Z                                     |     |                                    |     |   |                                                                                                                                        |  |

| Enco        | oding:                                    | C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0100                                  |     | 00da                               | fff | f | ffff                                                                                                                                   |  |

| Desc        | rription:                                 | The contents of register 'f' are rotated<br>one bit to the right. If 'd' is '0', the result<br>is placed in W. If 'd' is '1', the result is<br>placed back in register 'f' (default).<br>If 'a' is '0', the Access Bank will be<br>selected, overriding the BSR value. If 'a'<br>is '1', then the bank will be selected as<br>per the BSR value (default).<br>If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever $f \le 95$ (5Fh). See<br>Section 25.2.3 "Byte-Oriented and<br>Bit-Oriented Instructions in Indexed<br>Literal Offset Mode" for details. |                                       |     |                                    |     |   | the result<br>result is<br>ault).<br>ill be<br>alue. If 'a'<br>ected as<br>struction<br>operates<br>essing<br>See<br>ed and<br>Indexed |  |

| Word        | ds:                                       | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                       |     |                                    |     |   |                                                                                                                                        |  |

| Cycle       | es:                                       | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                       |     |                                    |     |   |                                                                                                                                        |  |

|             | ycle Activity:                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                       |     |                                    |     |   |                                                                                                                                        |  |

|             | Q1                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Q2                                    |     | Q3                                 |     |   | Q4                                                                                                                                     |  |

|             | Decode                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ead<br>ster 'f'                       |     | Proce<br>Data                      |     |   | /rite to<br>stination                                                                                                                  |  |

| <u>Exan</u> | nple 1:                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | NCF                                   | RI  | EG, 1,                             | , 0 |   |                                                                                                                                        |  |

|             | Before Instruc<br>REG<br>After Instructic | =                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1101                                  | 01  | 11                                 |     |   |                                                                                                                                        |  |