Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 25MHz                                                                     |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                               |

| Number of I/O              | 25                                                                        |

| Program Memory Size        | 64KB (32K x 16)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 1K x 8                                                                    |

| RAM Size                   | 3.25K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 8x10b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 28-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f2680-e-so |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin Name                                   | Pi        | n Numl          | ber               | Pin Buffer |        | Description                                                                                                   |

|--------------------------------------------|-----------|-----------------|-------------------|------------|--------|---------------------------------------------------------------------------------------------------------------|

| Pin Name                                   | PDIP      | QFN             | TQFP              | Туре       | Туре   | Description                                                                                                   |

|                                            |           |                 |                   |            |        | PORTE is a bidirectional I/O port.                                                                            |

| RE0/RD/AN5                                 | 8         | 25              | 25                |            |        |                                                                                                               |

| RE0                                        |           |                 |                   | I/O        | ST     | Digital I/O.                                                                                                  |

| RD                                         |           |                 |                   | Ι          | TTL    | Read control for Parallel Slave Port (see also $\overline{WR}$ and $\overline{CS}$ pins).                     |

| AN5                                        |           |                 |                   | I          | Analog | Analog input 5.                                                                                               |

| RE1/WR/AN6/C1OUT                           | 9         | 26              | 26                |            |        |                                                                                                               |

| RE1                                        |           |                 |                   | I/O        | ST     | Digital I/O.                                                                                                  |

| WR                                         |           |                 |                   | I          | TTL    | Write control for Parallel Slave Port (see CS and RD pins).                                                   |

| AN6                                        |           |                 |                   | I          | Analog | Analog input 6.                                                                                               |

| C1OUT                                      |           |                 |                   | 0          | TTL    | Comparator 1 output.                                                                                          |

| RE2/CS/AN7/C2OUT                           | 10        | 27              | 27                |            |        |                                                                                                               |

| RE2                                        |           |                 |                   | I/O        | ST     | Digital I/O.                                                                                                  |

| CS                                         |           |                 |                   | Ι          | TTL    | Chip select control for Parallel Slave Port (see related $\overline{\text{RD}}$ and $\overline{\text{WR}}$ ). |

| AN7                                        |           |                 |                   | I          | Analog | Analog input 7.                                                                                               |

| C2OUT                                      |           |                 |                   | 0          | TTL    | Comparator 2 output.                                                                                          |

| RE3                                        | —         | —               | —                 | —          | —      | See MCLR/VPP/RE3 pin.                                                                                         |

| Vss                                        | 12,<br>31 | 6, 30,<br>31    | 6, 29             | Р          | —      | Ground reference for logic and I/O pins.                                                                      |

| Vdd                                        | 11, 32    | 7, 8,<br>28, 29 | 7, 28             | Р          | —      | Positive supply for logic and I/O pins.                                                                       |

| NC                                         | —         | 13              | 12, 13,<br>33, 34 | —          | —      | No connect.                                                                                                   |

| Legend: TTL = TTL<br>ST = Schr<br>O = Outp | nitt Trig |                 | ut<br>It with Cl  | MOS le     |        | CMOS = CMOS compatible input or output<br>= Input<br>= Power                                                  |

| TABLE 1-3: | PIC18F4585/4680 PINOUT I/O DESCRIPTIONS (CONTINUED) |

|------------|-----------------------------------------------------|

|------------|-----------------------------------------------------|

| REGISTER 4-1: | RCON: R                                                                  | ESET CONT                       | ROL REC    | GISTER        |                       |            |                      |              |  |

|---------------|--------------------------------------------------------------------------|---------------------------------|------------|---------------|-----------------------|------------|----------------------|--------------|--|

|               | R/W-0                                                                    | R/W-1 <sup>(1)</sup>            | U-0        | R/W-1         | R-1                   | R-1        | R/W-0 <sup>(2)</sup> | R/W-0        |  |

|               | IPEN                                                                     | SBOREN                          | _          | RI            | TO                    | PD         | POR                  | BOR          |  |

|               | bit 7                                                                    |                                 |            |               |                       |            |                      | bit 0        |  |

|               |                                                                          |                                 |            |               |                       |            |                      |              |  |

| bit 7         |                                                                          | rrupt Priority E                |            |               |                       |            |                      |              |  |

|               |                                                                          | e priority levels               |            |               |                       |            |                      |              |  |

| <b>h</b> # 0  | 0 = Disable priority levels on interrupts (16CXXX Compatibility mode)    |                                 |            |               |                       |            |                      |              |  |

| bit 6         | SBOREN: BOR Software Enable bit <sup>(1)</sup><br>If BOREN1:BOREN0 = 01: |                                 |            |               |                       |            |                      |              |  |

|               | 1 = BOR is                                                               |                                 | <u>)1.</u> |               |                       |            |                      |              |  |

|               | 0 = BOR is                                                               | s disabled                      |            |               |                       |            |                      |              |  |

|               |                                                                          | <u>1:BOREN0 = 0</u>             |            | <u>1:</u>     |                       |            |                      |              |  |

|               |                                                                          | oled and read                   |            |               |                       |            |                      |              |  |

| bit 5         |                                                                          | nented: Read                    |            |               |                       |            |                      |              |  |

| bit 4         |                                                                          | Instruction Fla                 | -          |               | - <b>1</b>   <b>6</b> |            |                      |              |  |

|               |                                                                          | ESET instructi                  |            |               |                       |            | t be set in sot      | itware after |  |

|               |                                                                          | wn-out Reset                    |            |               | .9 4 401100 1         |            |                      |              |  |

| bit 3         | TO: Watch                                                                | dog Time-out                    | Flag bit   |               |                       |            |                      |              |  |

|               | -                                                                        | power-up, CL                    |            | uction or SLI | EEP instructi         | ion        |                      |              |  |

|               |                                                                          | F time-out occ                  |            |               |                       |            |                      |              |  |

| bit 2         |                                                                          | r-down Detect                   | •          |               |                       |            |                      |              |  |

|               | -                                                                        | power-up or b<br>execution of t | -          |               | on                    |            |                      |              |  |

| bit 1         |                                                                          | er-on Reset S                   |            |               |                       |            |                      |              |  |

|               |                                                                          | er-on Reset h                   |            | urred (set by | firmware or           | nly)       |                      |              |  |

|               |                                                                          | er-on Reset o                   |            |               |                       |            | on Reset oc          | curs)        |  |

| bit 0         |                                                                          | wn-out Reset                    |            |               |                       |            |                      |              |  |

|               |                                                                          | vn-out Reset h                  |            |               |                       |            |                      |              |  |

|               |                                                                          | vn-out Reset o                  | -          |               |                       |            |                      | occurs)      |  |

|               |                                                                          | If SBOREN i                     |            |               |                       |            |                      |              |  |

|               | 2:                                                                       | The actual R<br>notes follow    |            |               |                       |            |                      |              |  |

|               |                                                                          | additional inf                  |            | giotor and    |                       |            |                      |              |  |

|               |                                                                          |                                 |            |               |                       |            |                      |              |  |

|               | Legend:                                                                  |                                 |            |               |                       |            |                      |              |  |

|               | R = Reada                                                                | able bit                        | W = V      | Vritable bit  | U = Unii              | mplemented | d bit, read as       | '0'          |  |

|               | -n = Value                                                               | at POR                          | '1' = E    | Bit is set    | '0' = Bit             | is cleared | x = Bit is ι         | unknown      |  |

**Note 1:** It is recommended that the POR bit be set after a Power-on Reset has been detected so that subsequent Power-on Resets may be detected.

2: Brown-out Reset is said to have occurred when BOR is '0' and POR is '1' (assuming that POR was set to '1' by software immediately after POR).

# TABLE 5-1:SPECIAL FUNCTION REGISTER MAP FOR<br/>PIC18F2585/2680/4585/4680 DEVICES (CONTINUED)

| Address | Name                  | Address | Name                  | Address | Name                  | Address | Name                  |

|---------|-----------------------|---------|-----------------------|---------|-----------------------|---------|-----------------------|

| E7Fh    | CANCON_RO4            | E6Fh    | CANCON_RO5            | E5Fh    | CANCON_RO6            | E4Fh    | CANCON_RO7            |

| E7Eh    | CANSTAT_RO4           | E6Eh    | CANSTAT_RO5           | E5Eh    | CANSTAT_RO6           | E4Eh    | CANSTAT_RO7           |

| E7Dh    | B5D7 <sup>(2)</sup>   | E6Dh    | B4D7 <sup>(2)</sup>   | E5Dh    | B3D7 <sup>(2)</sup>   | E4Dh    | B2D7 <sup>(2)</sup>   |

| E7Ch    | B5D6 <sup>(2)</sup>   | E6Ch    | B4D6 <sup>(2)</sup>   | E5Ch    | B3D6 <sup>(2)</sup>   | E4Ch    | B2D6 <sup>(2)</sup>   |

| E7Bh    | B5D5 <sup>(2)</sup>   | E6Bh    | B4D5 <sup>(2)</sup>   | E5Bh    | B3D5 <sup>(2)</sup>   | E4Bh    | B2D5 <sup>(2)</sup>   |

| E7Ah    | B5D4 <sup>(2)</sup>   | E6Ah    | B4D4 <sup>(2)</sup>   | E5Ah    | B3D4 <sup>(2)</sup>   | E4Ah    | B2D4 <sup>(2)</sup>   |

| E79h    | B5D3 <sup>(2)</sup>   | E69h    | B4D3 <sup>(2)</sup>   | E59h    | B3D3 <sup>(2)</sup>   | E49h    | B2D3 <sup>(2)</sup>   |

| E78h    | B5D2 <sup>(2)</sup>   | E68h    | B4D2 <sup>(2)</sup>   | E58h    | B3D2 <sup>(2)</sup>   | E48h    | B2D2 <sup>(2)</sup>   |

| E77h    | B5D1 <sup>(2)</sup>   | E67h    | B4D1 <sup>(2)</sup>   | E57h    | B3D1 <sup>(2)</sup>   | E47h    | B2D1 <sup>(2)</sup>   |

| E76h    | B5D0 <sup>(2)</sup>   | E66h    | B4D0 <sup>(2)</sup>   | E56h    | B3D0 <sup>(2)</sup>   | E46h    | B2D0 <sup>(2)</sup>   |

| E75h    | B5DLC <sup>(2)</sup>  | E65h    | B4DLC <sup>(2)</sup>  | E55h    | B3DLC <sup>(2)</sup>  | E45h    | B2DLC <sup>(2)</sup>  |

| E74h    | B5EIDL <sup>(2)</sup> | E64h    | B4EIDL <sup>(2)</sup> | E54h    | B3EIDL <sup>(2)</sup> | E44h    | B2EIDL <sup>(2)</sup> |

| E73h    | B5EIDH <sup>(2)</sup> | E63h    | B4EIDH <sup>(2)</sup> | E53h    | B3EIDH <sup>(2)</sup> | E43h    | B2EIDH <sup>(2)</sup> |

| E72h    | B5SIDL <sup>(2)</sup> | E62h    | B4SIDL <sup>(2)</sup> | E52h    | B3SIDL <sup>(2)</sup> | E42h    | B2SIDL <sup>(2)</sup> |

| E71h    | B5SIDH <sup>(2)</sup> | E61h    | B4SIDH <sup>(2)</sup> | E51h    | B3SIDH <sup>(2)</sup> | E41h    | B2SIDH <sup>(2)</sup> |

| E70h    | B5CON <sup>(2)</sup>  | E60h    | B4CON <sup>(2)</sup>  | E50h    | B3CON <sup>(2)</sup>  | E40h    | B2CON <sup>(2)</sup>  |

| E3Fh    | CANCON_RO8            | E2Fh    | CANCON_RO9            | E1Fh    | —                     | E0Fh    | —                     |

| E3Eh    | CANSTAT_RO8           | E2Eh    | CANSTAT_RO9           | E1Eh    | —                     | E0Eh    | —                     |

| E3Dh    | B1D7 <sup>(2)</sup>   | E2Dh    | B0D7 <sup>(2)</sup>   | E1Dh    | —                     | E0Dh    | —                     |

| E3Ch    | B1D6 <sup>(2)</sup>   | E2Ch    | B0D6 <sup>(2)</sup>   | E1Ch    | —                     | E0Ch    | —                     |

| E3Bh    | B1D5 <sup>(2)</sup>   | E2Bh    | B0D5 <sup>(2)</sup>   | E1Bh    | —                     | E0Bh    | —                     |

| E3Ah    | B1D4 <sup>(2)</sup>   | E2Ah    | B0D4 <sup>(2)</sup>   | E1Ah    | _                     | E0Ah    | _                     |

| E39h    | B1D3 <sup>(2)</sup>   | E29h    | B0D3 <sup>(2)</sup>   | E19h    | —                     | E09h    | —                     |

| E38h    | B1D2 <sup>(2)</sup>   | E28h    | B0D2 <sup>(2)</sup>   | E18h    | —                     | E08h    | —                     |

| E37h    | B1D1 <sup>(2)</sup>   | E27h    | B0D1 <sup>(2)</sup>   | E17h    | —                     | E07h    | —                     |

| E36h    | B1D0 <sup>(2)</sup>   | E26h    | B0D0 <sup>(2)</sup>   | E16h    | —                     | E06h    | —                     |

| E35h    | B1DLC <sup>(2)</sup>  | E25h    | B0DLC <sup>(2)</sup>  | E15h    | —                     | E05h    | —                     |

| E34h    | B1EIDL <sup>(2)</sup> | E24h    | B0EIDL <sup>(2)</sup> | E14h    | _                     | E04h    | _                     |

| E33h    | B1EIDH <sup>(2)</sup> | E23h    | B0EIDH <sup>(2)</sup> | E13h    | _                     | E03h    | _                     |

| E32h    | B1SIDL <sup>(2)</sup> | E22h    | B0SIDL <sup>(2)</sup> | E12h    | _                     | E02h    | _                     |

| E31h    | B1SIDH <sup>(2)</sup> | E21h    | B0SIDH <sup>(2)</sup> | E11h    | _                     | E01h    |                       |

| E30h    | B1CON <sup>(2)</sup>  | E20h    | B0CON <sup>(2)</sup>  | E10h    | _                     | E00h    | —                     |

Note 1: Registers available only on PIC18F4X8X devices; otherwise, the registers read as '0'.

2: When any TX\_ENn bit in RX\_TX\_SELn is set, then the corresponding bit in this register has transmit properties.

3: This is not a physical register.

| File Name                              | Bit 7   | Bit 6   | Bit 5         | Bit 4   | Bit 3   | Bit 2         | Bit 1   | Bit 0   | Value on<br>POR, BOR | Details<br>on page: |

|----------------------------------------|---------|---------|---------------|---------|---------|---------------|---------|---------|----------------------|---------------------|

| B0DLC <sup>(8)</sup><br>Receive mode   | _       | RXRTR   | RB1           | RB0     | DLC3    | DLC2          | DLC1    | DLC0    | -xxx xxxx            | 56, 300             |

| B0DLC <sup>(8)</sup><br>Transmit mode  | —       | TXRTR   | -             | -       | DLC3    | DLC2          | DLC1    | DLC0    | -x xxxx              | 56, 301             |

| B0EIDL <sup>(8)</sup>                  | EID7    | EID6    | EID5          | EID4    | EID3    | EID2          | EID1    | EID0    | xxxx xxxx            | 58, 299             |

| B0EIDH <sup>(8)</sup>                  | EID15   | EID14   | EID13         | EID12   | EID11   | EID10         | EID9    | EID8    | xxxx xxxx            | 58, 298             |

| B0SIDL <sup>(8)</sup><br>Receive mode  | SID2    | SID1    | SID0          | SRR     | EXID    | _             | EID17   | EID16   | xxxx x-xx            | 56, 297             |

| B0SIDL <sup>(8)</sup><br>Transmit mode | SID2    | SID1    | SID0          |         | EXIDE   | -             | EID17   | EID16   | xxx- x-xx            | 56, 297             |

| B0SIDH <sup>(8)</sup>                  | SID10   | SID9    | SID8          | SID7    | SID6    | SID5          | SID4    | SID3    | xxxx xxxx            | 58, 296             |

| B0CON <sup>(8)</sup><br>Receive mode   | RXFUL   | RXM1    | RXRTRRO       | FILHIT4 | FILHIT3 | FILHIT2       | FILHIT1 | FILHIT0 | 0000 0000            | 58, 295             |

| B0CON <sup>(8)</sup><br>Transmit mode  | TXBIF   | TXABT   | TXLARB        | TXERR   | TXREQ   | RTREN         | TXPRI1  | TXPRI0  | 0000 0000            | 58, 295             |

| TXBIE                                  | _       | —       | —             | TXB2IE  | TXB1IE  | TXB0IE        | _       | —       | 0 00                 | 58, 318             |

| BIE0                                   | B5IE    | B4IE    | B3IE          | B2IE    | B1IE    | B0IE          | RXB1IE  | RXB0IE  | 0000 0000            | 58, 318             |

| BSEL0                                  | B5TXEN  | B4TXEN  | <b>B3TXEN</b> | B2TXEN  | B1TXEN  | <b>B0TXEN</b> | _       | _       | 0000 00              | 59, 301             |

| MSEL3                                  | FIL15_1 | FIL15_0 | FIL14_1       | FIL14_0 | FIL13_1 | FIL13_0       | FIL12_1 | FIL12_0 | 0000 0000            | 59, 310             |

| MSEL2                                  | FIL11_1 | FIL11_0 | FIL10_1       | FIL10_0 | FIL9_1  | FIL9_0        | FIL8_1  | FIL8_0  | 0000 0000            | 59, 309             |

| MSEL1                                  | FIL7_1  | FIL7_0  | FIL6_1        | FIL6_0  | FIL5_1  | FIL5_0        | FIL4_1  | FIL4_0  | 0000 0101            | 59, 308             |

| MSEL0                                  | FIL3_1  | FIL3_0  | FIL2_1        | FIL2_0  | FIL1_1  | FIL1_0        | FIL0_1  | FIL0_0  | 0101 0000            | 59, 307             |

| RXFBCON7                               | F15BP_3 | F15BP_2 | F15BP_1       | F15BP_0 | F14BP_3 | F14BP_2       | F14BP_1 | F14BP_0 | 0000 0000            | 59, 305             |

| RXFBCON6                               | F13BP_3 | F13BP_2 | F13BP_1       | F13BP_0 | F12BP_3 | F12BP_2       | F12BP_1 | F12BP_0 | 0000 0000            | 59, 305             |

| RXFBCON5                               | F11BP_3 | F11BP_2 | F11BP_1       | F11BP_0 | F10BP_3 | F10BP_2       | F10BP_1 | F10BP_0 | 0000 0000            | 59, 305             |

| RXFBCON4                               | F9BP_3  | F9BP_2  | F9BP_1        | F9BP_0  | F8BP_3  | F8BP_2        | F8BP_1  | F8BP_0  | 0000 0000            | 59, 305             |

| RXFBCON3                               | F7BP_3  | F7BP_2  | F7BP_1        | F7BP_0  | F6BP_3  | F6BP_2        | F6BP_1  | F6BP_0  | 0000 0000            | 59, 305             |

| RXFBCON2                               | F5BP_3  | F5BP_2  | F5BP_1        | F5BP_0  | F4BP_3  | F4BP_2        | F4BP_1  | F4BP_0  | 0001 0001            | 59, 305             |

| RXFBCON1                               | F3BP_3  | F3BP_2  | F3BP_1        | F3BP_0  | F2BP_3  | F2BP_2        | F2BP_1  | F2BP_0  | 0001 0001            | 59, 305             |

| RXFBCON0                               | F1BP_3  | F1BP_2  | F1BP_1        | F1BP_0  | F0BP_3  | F0BP_2        | F0BP_1  | F0BP_0  | 0000 0000            | 59, 305             |

| SDFLC                                  |         | _       | _             | FLC4    | FLC3    | FLC2          | FLC1    | FLC0    | 0 0000               | 59, 305             |

| RXFCON1                                | RXF15EN | RXF14EN | RXF13EN       | RXF12EN | RXF11EN | RXF10EN       | RXF9EN  | RXF8EN  | 0000 0000            | 59, 306             |

| RXFCON0                                | RXF7EN  | RXF6EN  | RXF5EN        | RXF4EN  | RXF3EN  | RXF2EN        | RXF1EN  | RXF0EN  | 0000 0000            | 59, 305             |

| RXF15EIDL                              | EID7    | EID6    | EID5          | EID4    | EID3    | EID2          | EID1    | EID0    | xxxx xxxx            | 59, 303             |

| RXF15EIDH                              | EID15   | EID14   | EID13         | EID12   | EID11   | EID10         | EID9    | EID8    | xxxx xxxx            | 59, 303             |

| RXF15SIDL                              | SID2    | SID1    | SID0          | _       | EXIDEN  | —             | EID17   | EID16   | xxx- x-xx            | 59, 304             |

| RXF15SIDH                              | SID10   | SID9    | SID8          | SID7    | SID6    | SID5          | SID4    | SID3    | xxxx xxxx            | 59, 303             |

| RXF14EIDL                              | EID7    | EID6    | EID5          | EID4    | EID3    | EID2          | EID1    | EID0    | xxxx xxxx            | 59, 303             |

| RXF14EIDH                              | EID15   | EID14   | EID13         | EID12   | EID11   | EID10         | EID9    | EID8    | xxxx xxxx            | 59, 303             |

| RXF14SIDL                              | SID2    | SID1    | SID0          | _       | EXIDEN  | _             | EID17   | EID16   | xxx- x-xx            | 59, 304             |

| RXF14SIDH                              | SID10   | SID9    | SID8          | SID7    | SID6    | SID5          | SID4    | SID3    | xxxx xxxx            | 59, 303             |

| RXF13EIDL                              | EID7    | EID6    | EID5          | EID4    | EID3    | EID2          | EID1    | EID0    | xxxx xxxx            | 59, 303             |

| RXF13EIDH                              | EID15   | EID14   | EID13         | EID12   | EID11   | EID10         | EID9    | EID8    | xxxx xxxx            | 59, 303             |

| <b>TABLE 5-2:</b> | REGISTER FILE SUMMARY ( | PIC18F2585/2680/4585/4680 | (CONTINUED) |

|-------------------|-------------------------|---------------------------|-------------|

|-------------------|-------------------------|---------------------------|-------------|

**Legend:** x = unknown, u = unchanged, - = unimplemented, q = value depends on condition **Note 1:** Bit 21 of the PC is only available in Test mode and Serial Programming modes.

2: The SBOREN bit is only available when CONFIG2L<1:0> = 01; otherwise, it is disabled and reads as '0'. See Section 4.4 "Brown-out Reset (BOR)".

3: These registers and/or bits are not implemented on PIC18F2X8X devices and are read as '0'. Reset values are shown for PIC18F4X8X devices; individual unimplemented bits should be interpreted as '---'.

4: The PLLEN bit is only available in specific oscillator configuration; otherwise, it is disabled and reads as '0'. See Section 2.6.4 "PLL in INTOSC Modes".

5: The RE3 bit is only available when Master Clear Reset is disabled (CONFIG3H<7> = 0); otherwise, RE3 reads as '0'. This bit is read-only.

**6:** RA6/RA7 and their associated latch and direction bits are individually configured as port pins based on various primary oscillator modes. When disabled, these bits read as '0'.

7: CAN bits have multiple functions depending on the selected mode of the CAN module.

8: This register reads all '0's until the ECAN<sup>™</sup> technology is set up in Mode 1 or Mode 2.

9: These registers are available on PIC18F4X8X devices only.

# 9.0 INTERRUPTS

The PIC18F2585/2680/4585/4680 devices have multiple interrupt sources and an interrupt priority feature that allows each interrupt source to be assigned a high priority level or a low priority level. The high priority interrupt vector is at 000008h and the low priority interrupt vector is at 000018h. High priority interrupt events will interrupt any low priority interrupts that may be in progress.

There are ten registers which are used to control interrupt operation. These registers are:

- RCON

- INTCON

- INTCON2

- INTCON3

- PIR1, PIR2, PIR3

- PIE1, PIE2, PIE3

- IPR1, IPR2, IPR3

It is recommended that the Microchip header files supplied with MPLAB<sup>®</sup> IDE be used for the symbolic bit names in these registers. This allows the assembler/ compiler to automatically take care of the placement of these bits within the specified register.

Each interrupt source has three bits to control its operation. The functions of these bits are:

- Flag bit to indicate that an interrupt event occurred

- Enable bit that allows program execution to branch to the interrupt vector address when the flag bit is set

- Priority bit to select high priority or low priority

The interrupt priority feature is enabled by setting the IPEN bit (RCON<7>). When interrupt priority is enabled, there are two bits which enable interrupts globally. Setting the GIEH bit (INTCON<7>) enables all interrupts that have the priority bit set (high priority). Setting the GIEL bit (INTCON<6>) enables all interrupts that have the priority bit cleared (low priority). When the interrupt flag, enable bit and appropriate global interrupt enable bit are set, the interrupt will vector immediately to address 000008h or 000018h, depending on the priority bit setting. Individual interrupts can be disabled through their corresponding enable bits.

When the IPEN bit is cleared (default state), the interrupt priority feature is disabled and interrupts are compatible with PIC<sup>®</sup> mid-range devices. In Compatibility mode, the interrupt priority bits for each source have no effect. INTCON<6> is the PEIE bit, which enables/ disables all peripheral interrupt sources. INTCON<7> is the GIE bit, which enables/disables all interrupt sources. All interrupts branch to address 000008h in Compatibility mode.

When an interrupt is responded to, the global interrupt enable bit is cleared to disable further interrupts. If the IPEN bit is cleared, this is the GIE bit. If interrupt priority levels are used, this will be either the GIEH or GIEL bit. High priority interrupt sources can interrupt a low priority interrupt. Low priority interrupts are not processed while high priority interrupts are in progress.

The return address is pushed onto the stack and the PC is loaded with the interrupt vector address (000008h or 000018h). Once in the Interrupt Service Routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bits must be cleared in software before re-enabling interrupts to avoid recursive interrupts.

The "return from interrupt" instruction, RETFIE, exits the interrupt routine and sets the GIE bit (GIEH or GIEL if priority levels are used), which re-enables interrupts.

For external interrupt events, such as the INT pins or the PORTB input change interrupt, the interrupt latency will be three to four instruction cycles. The exact latency is the same for one or two-cycle instructions. Individual interrupt flag bits are set, regardless of the status of their corresponding enable bit or the GIE bit.

**Note:** Do not use the MOVFF instruction to modify any of the interrupt control registers while **any** interrupt is enabled. Doing so may cause erratic microcontroller behavior.

| TABLE 10-3: PC     | ORTB I/O SUMMARY |     |      |        |                                                                                                                  |  |  |  |  |  |  |

|--------------------|------------------|-----|------|--------|------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Pin Name           | Function         | I/O | TRIS | Buffer | Description                                                                                                      |  |  |  |  |  |  |

| RB0/INT0/FLT0/AN10 | RB0              | OUT | 0    | DIG    | LATB<0> data output.                                                                                             |  |  |  |  |  |  |

|                    |                  | IN  | 1    | TTL    | PORTB<0> data input. Weak pull-up available only in this mode.                                                   |  |  |  |  |  |  |

|                    | INT0             | IN  | 1    | ST     | External interrupt 0 input.                                                                                      |  |  |  |  |  |  |

|                    | FLT0             | IN  | 1    | ST     | Enhanced PWM Fault input.                                                                                        |  |  |  |  |  |  |

|                    | AN10             | IN  | 1    | ANA    | A/D input channel 10. Enabled on POR, this analog input overrides the digital input (read as clear – low level). |  |  |  |  |  |  |

| RB1/INT1/AN8       | RB1              | OUT | 0    | DIG    | LATB<1> data output.                                                                                             |  |  |  |  |  |  |

|                    |                  | IN  | 1    | TTL    | PORTB<1> data input. Weak pull-up available only in this mode.                                                   |  |  |  |  |  |  |

|                    | INT1             | IN  | 1    | ST     | External interrupt 1 input.                                                                                      |  |  |  |  |  |  |

|                    | AN8              | IN  | 1    | ANA    | A/D input channel 8. Enabled on POR, this analog input overrides the digital input (read as clear – low level).  |  |  |  |  |  |  |

| RB2/INT2/CANTX     | RB2              | OUT | x    | DIG    | LATB<2> data output.                                                                                             |  |  |  |  |  |  |

|                    |                  | IN  | 1    | TTL    | PORTB<2> data input. Weak pull-up available only in this mode.                                                   |  |  |  |  |  |  |

|                    | INT2             | IN  | 1    | ST     | External interrupt 2 input.                                                                                      |  |  |  |  |  |  |

|                    | CANTX            | OUT | 1    | DIG    | CAN transmit signal output. The CAN interface overrides the TRIS<2> control when enabled.                        |  |  |  |  |  |  |

| RB3/CANRX          | RB3              | OUT | 0    | DIG    | LATB<3> data output.                                                                                             |  |  |  |  |  |  |

|                    |                  | IN  | 1    | TTL    | PORTB<3> data input. Weak pull-up available only in this mode.                                                   |  |  |  |  |  |  |

|                    | CANRX            | IN  | 1    | ST     | CAN receive signal input. Pin must be configured as a digital input by setting TRISB<3>.                         |  |  |  |  |  |  |

| RB4/KBI0/AN9       | RB4              | OUT | 0    | DIG    | LATB<4> data output.                                                                                             |  |  |  |  |  |  |

|                    |                  | IN  | 1    | TTL    | PORTB<4> data input. Weak pull-up available only in this mode.                                                   |  |  |  |  |  |  |

|                    | KBI0             | IN  | 1    | TTL    | Interrupt-on-pin change.                                                                                         |  |  |  |  |  |  |

|                    | AN9              | IN  | 1    | ANA    | A/D input channel 9. Enabled on POR, this analog input overrides the digital input (read as clear – low level).  |  |  |  |  |  |  |

| RB5/KBI1/PGM       | RB5              | OUT | 0    | DIG    | LATB<5> data output.                                                                                             |  |  |  |  |  |  |

|                    |                  | IN  | 1    | TTL    | PORTB<5> data input. Weak pull-up available only in this mode.                                                   |  |  |  |  |  |  |

|                    | KBI1             | IN  | 1    | TTL    | Interrupt-on-pin change.                                                                                         |  |  |  |  |  |  |

|                    | PGM              | IN  | х    | ST     | Low-Voltage Programming mode entry (ICSP™). Enabling this function overrides digital output.                     |  |  |  |  |  |  |

| RB6/KBI2/PGC       | RB6              | OUT | 0    | DIG    | LATB<6> data output.                                                                                             |  |  |  |  |  |  |

|                    |                  | IN  | 1    | TTL    | PORTB<6> data input. Weak pull-up available only in this mode.                                                   |  |  |  |  |  |  |

|                    | KBI2             | IN  | 1    | TTL    | Interrupt-on-pin change.                                                                                         |  |  |  |  |  |  |

|                    | PGC              | IN  | x    | ST     | Low-Voltage Programming mode entry (ICSP) clock input.                                                           |  |  |  |  |  |  |

| RB7/KBI3/PGD       | RB7              | OUT | 0    | DIG    | LATB<7> data output.                                                                                             |  |  |  |  |  |  |

|                    |                  | IN  | 1    | TTL    | PORTB<7> data input. Weak pull-up available only in this mode.                                                   |  |  |  |  |  |  |

|                    | KBI3             | IN  | 1    | TTL    | Interrupt-on-pin change.                                                                                         |  |  |  |  |  |  |

|                    | PGD              | OUT | x    | DIG    | Low-Voltage Programming mode entry (ICSP) clock output.                                                          |  |  |  |  |  |  |

|                    |                  | IN  | x    | ST     | Low-Voltage Programming mode entry (ICSP) clock input.                                                           |  |  |  |  |  |  |

TABLE 10-3: PORTB I/O SUMMARY

Legend: PWR = Power Supply; OUT = Output; IN = Input; ANA = Analog Signal; DIG = Digital Output; ST = Schmitt Buffer Input; TTL – TTL Buffer Input

-n = Value at POR

| ER 10-1: | I RISE RE                                                                                                                     | GISTER (I                                    |              |                  | ONLT)       |           |              |        |  |  |  |

|----------|-------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|--------------|------------------|-------------|-----------|--------------|--------|--|--|--|

|          | R-0                                                                                                                           | R-0                                          | R/W-0        | R/W-0            | U-0         | R/W-1     | R/W-1        | R/W-1  |  |  |  |

|          | IBF                                                                                                                           | OBF                                          | IBOV         | PSPMODE          | _           | TRISE2    | TRISE1       | TRISE0 |  |  |  |

|          | bit 7                                                                                                                         |                                              |              |                  |             |           |              | bit 0  |  |  |  |

|          |                                                                                                                               |                                              |              |                  |             |           |              |        |  |  |  |

| bit 7    | IBF: Input                                                                                                                    | Buffer Full S                                | Status bit   |                  |             |           |              |        |  |  |  |

|          |                                                                                                                               | l has been r<br>rd has been                  |              | l waiting to be  | read by the | e CPU     |              |        |  |  |  |

| bit 6    | <b>OBF:</b> Output Buffer Full Status bit                                                                                     |                                              |              |                  |             |           |              |        |  |  |  |

|          | <ul> <li>1 = The output buffer still holds a previously written word</li> <li>0 = The output buffer has been read</li> </ul>  |                                              |              |                  |             |           |              |        |  |  |  |

| bit 5    | IBOV: Inpu                                                                                                                    | ut Buffer Ove                                | erflow Deteo | ct bit (in Micro | processor r | node)     |              |        |  |  |  |

|          | 1 = A write occurred when a previously input word has not been read (must be cleared in software)<br>0 = No overflow occurred |                                              |              |                  |             |           |              |        |  |  |  |

| bit 4    | PSPMODE                                                                                                                       | PSPMODE: Parallel Slave Port Mode Select bit |              |                  |             |           |              |        |  |  |  |

|          |                                                                                                                               | I Slave Port                                 |              |                  |             |           |              |        |  |  |  |

|          |                                                                                                                               | al Purpose I                                 |              |                  |             |           |              |        |  |  |  |

| bit 3    | •                                                                                                                             | ented: Rea                                   |              |                  |             |           |              |        |  |  |  |

| bit 2    |                                                                                                                               | E2 Direction                                 | n Control bi | t                |             |           |              |        |  |  |  |

|          | 1 = Input<br>0 = Output                                                                                                       | :                                            |              |                  |             |           |              |        |  |  |  |

| bit 1    | TRISE1: R                                                                                                                     | E1 Direction                                 | n Control bi | t                |             |           |              |        |  |  |  |

|          | 1 = Input                                                                                                                     |                                              |              |                  |             |           |              |        |  |  |  |

|          | 0 = Output                                                                                                                    |                                              |              |                  |             |           |              |        |  |  |  |

| bit 0    | TRISE0: R                                                                                                                     | E0 Direction                                 | n Control bi | t                |             |           |              |        |  |  |  |

|          | 1 = Input<br>0 = Output                                                                                                       | :                                            |              |                  |             |           |              |        |  |  |  |

|          | Legend:                                                                                                                       |                                              |              |                  |             |           |              |        |  |  |  |

|          | R = Reada                                                                                                                     | ble bit                                      | W = V        | Vritable bit     | U = Unim    | plemented | bit, read as | '0'    |  |  |  |

|          | 1                                                                                                                             |                                              |              |                  |             |           |              |        |  |  |  |

#### REGISTER 10-1: TRISE REGISTER (PIC18F4X8X DEVICES ONLY)

'1' = Bit is set

'0' = Bit is cleared

x = Bit is unknown

|         | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                               | R/W-0                                                     | R/W-0           | R/W-0           | R/W-0          | R/W-0         | R/W-0         | R/W-0      |  |  |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|-----------------|-----------------|----------------|---------------|---------------|------------|--|--|

|         | WCOL                                                                                                                                                                                                                                                                                                                                                                                                                                | SSPOV                                                     | SSPEN           | CKP             | SSPM3          | SSPM2         | SSPM1         | SSPM0      |  |  |

|         | bit 7                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                           |                 |                 |                |               |               | bit 0      |  |  |

| bit 7   | 1 = The  S                                                                                                                                                                                                                                                                                                                                                                                                                          | rite Collision<br>SPBUF regis<br>be cleared ir<br>Ilision | ster is writter |                 | • •            | ng the prev   | ious word     |            |  |  |

| bit 6   | <ul> <li>SSPOV: Receive Overflow Indicator bit</li> <li><u>SPI Slave mode:</u></li> <li>1 = A new byte is received while the SSPBUF register is still holding the previous data. In case of overflow, the data in SSPSR is lost. Overflow can only occur in Slave mode. The user must read the SSPBUF, even if only transmitting data, to avoid setting overflow (must be cleared in software).</li> <li>0 = No overflow</li> </ul> |                                                           |                 |                 |                |               |               |            |  |  |

|         | <b>Note:</b> In Master mode, the overflow bit is not set since each new reception (and transmission) is initiated by writing to the SSPBUF register.                                                                                                                                                                                                                                                                                |                                                           |                 |                 |                |               |               |            |  |  |

| bit 5   | <b>SSPEN:</b> Synchronous Serial Port Enable bit<br>1 = Enables serial port and configures SCK, SDO, SDI and SS as serial port pins<br>0 = Disables serial port and configures these pins as I/O port pins                                                                                                                                                                                                                          |                                                           |                 |                 |                |               |               |            |  |  |

|         | Note:                                                                                                                                                                                                                                                                                                                                                                                                                               | When enab                                                 | led, these p    | ins must be     | properly cor   | nfigured as i | nput or outp  | out.       |  |  |

| bit 4   | 1 = Idle sta                                                                                                                                                                                                                                                                                                                                                                                                                        | k Polarity Se<br>ate for clock i<br>ate for clock i       | s a high leve   |                 |                |               |               |            |  |  |

| bit 3-0 |                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                           |                 |                 |                |               |               |            |  |  |

|         | Note:                                                                                                                                                                                                                                                                                                                                                                                                                               | Bit combina<br>I <sup>2</sup> C mode o                    |                 | ecifically list | ed here are    | either rese   | rved or impl  | emented in |  |  |

|         | Legend:                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                           |                 |                 |                |               |               |            |  |  |

|         | R = Reada                                                                                                                                                                                                                                                                                                                                                                                                                           | ble bit                                                   | W = Writab      | le bit          | U = Unimp      | lemented bi   | t, read as '0 | 3          |  |  |

|         | -n = Value                                                                                                                                                                                                                                                                                                                                                                                                                          | at POR                                                    | '1' = Bit is s  | set             | '0' = Bit is o | cleared       | x = Bit is u  | nknown     |  |  |

### REGISTER 17-2: SSPCON1: MSSP CONTROL REGISTER 1 (SPI MODE)

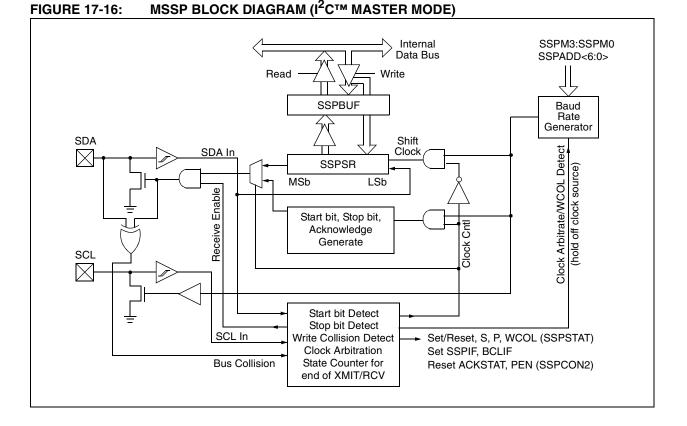

### 17.4.6 MASTER MODE

Master mode is enabled by setting and clearing the appropriate SSPM bits in SSPCON1 and by setting the SSPEN bit. In Master mode, the SCL and SDA lines are manipulated by the MSSP hardware.

Master mode of operation is supported by interrupt generation on the detection of the Start and Stop conditions. The Stop (P) and Start (S) bits are cleared from a Reset or when the MSSP module is disabled. Control of the  $I^2C$  bus may be taken when the P bit is set or the bus is Idle, with both the S and P bits clear.

In Firmware Controlled Master mode, user code conducts all  $I^2C$  bus operations based on Start and Stop bit conditions.

Once Master mode is enabled, the user has six options.

- 1. Assert a Start condition on SDA and SCL.

- 2. Assert a Repeated Start condition on SDA and SCL.

- 3. Write to the SSPBUF register initiating transmission of data/address.

- 4. Configure the I<sup>2</sup>C port to receive data.

- 5. Generate an Acknowledge condition at the end of a received byte of data.

- 6. Generate a Stop condition on SDA and SCL.

Note: The MSSP module, when configured in I<sup>2</sup>C Master mode, does not allow queueing of events. For instance, the user is not allowed to initiate a Start condition and immediately write the SSPBUF register to initiate transmission before the Start condition is complete. In this case, the SSPBUF will not be written to and the WCOL bit will be set, indicating that a write to the SSPBUF did not occur.

The following events will cause the SSP Interrupt Flag bit, SSPIF, to be set (SSP interrupt, if enabled):

- Start condition

- Stop condition

- Data transfer byte transmitted/received

- Acknowledge transmit

- Repeated Start

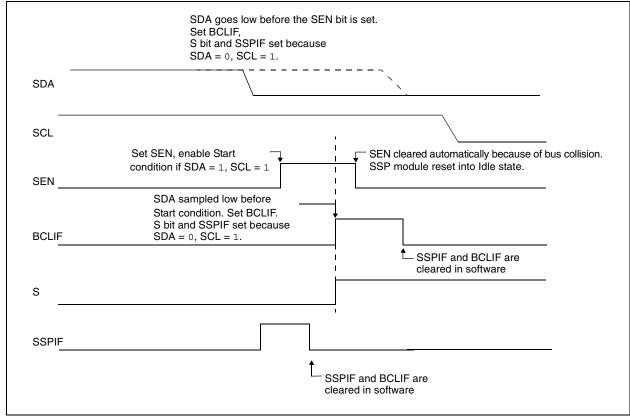

# 17.4.17.1 Bus Collision During a Start Condition

During a Start condition, a bus collision occurs if:

- a) SDA or SCL are sampled low at the beginning of the Start condition (Figure 17-26).

- b) SCL is sampled low before SDA is asserted low (Figure 17-27).

During a Start condition, both the SDA and the SCL pins are monitored.

If the SDA pin is already low, or the SCL pin is already low, then all of the following occur:

- the Start condition is aborted,

- the BCLIF flag is set; and

- the MSSP module is reset to its Idle state (Figure 17-26).

The Start condition begins with the SDA and SCL pins deasserted. When the SDA pin is sampled high, the Baud Rate Generator is loaded from SSPADD<6:0> and counts down to 0. If the SCL pin is sampled low while SDA is high, a bus collision occurs because it is assumed that another master is attempting to drive a data '1' during the Start condition.

If the SDA pin is sampled low during this count, the BRG is reset and the SDA line is asserted early (Figure 17-28). If, however, a '1' is sampled on the SDA pin, the SDA pin is asserted low at the end of the BRG count. The Baud Rate Generator is then reloaded and counts down to 0 and during this time, if the SCL pins are sampled as '0', a bus collision does not occur. At the end of the BRG count, the SCL pin is asserted low.

Note: The reason that bus collision is not a factor during a Start condition is that no two bus masters can assert a Start condition at the exact same time. Therefore, one master will always assert SDA before the other. This condition does not cause a bus collision because the two masters must be allowed to arbitrate the first address following the Start condition. If the address is the same, arbitration must be allowed to continue into the data portion, Repeated Start or Stop conditions.

### FIGURE 17-26: BUS COLLISION DURING START CONDITION (SDA ONLY)

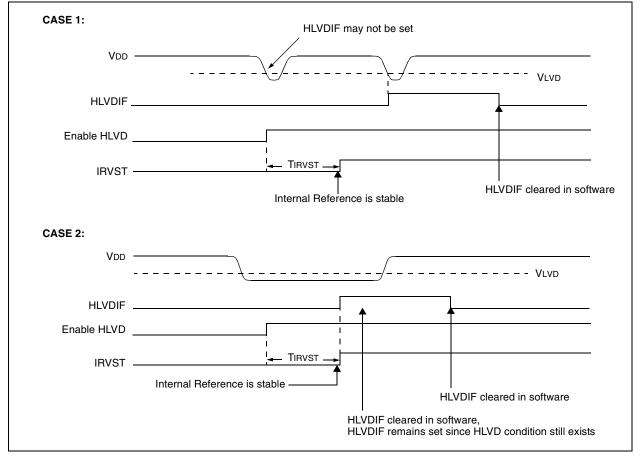

## 22.2 HLVD Setup

The following steps are needed to set up the HLVD module:

- 1. Disable the module by clearing the HLVDEN bit (HLVDCON<4>).

- 2. Write the value to the HLVDL3:HLVDL0 bits that select the desired HLVD trip point.

- Set the VDIRMAG bit to detect high voltage (VDIRMAG = 1) or low voltage (VDIRMAG = 0).

- 4. Enable the HLVD module by setting the HLVDEN bit.

- 5. Clear the HLVD interrupt flag (PIR2<2>), which may have been set from a previous interrupt.

- Enable the HLVD interrupt if interrupts are desired by setting the HLVDIE and GIE bits (PIE<2> and INTCON<7>). An interrupt will not be generated until the IRVST bit is set.

### 22.3 Current Consumption

When the module is enabled, the HLVD comparator and voltage divider are enabled and will consume static current. The total current consumption, when enabled, is specified in electrical specification parameter D022B. Depending on the application, the HLVD module does not need to be operating constantly. To decrease the current requirements, the HLVD circuitry may only need to be enabled for short periods where the voltage is checked. After doing the check, the HLVD module may be disabled.

### 22.4 HLVD Start-up Time

The internal reference voltage of the HLVD module, specified in electrical specification parameter D420, may be used by other internal circuitry, such as the Programmable Brown-out Reset. If the HLVD or other circuits using the voltage reference are disabled to lower the device's current consumption, the reference voltage circuit will require time to become stable before a low or high-voltage condition can be reliably detected. This start-up time, TIRVST, is an interval that is independent of device clock speed. It is specified in electrical specification parameter 36.

The HLVD interrupt flag is not enabled until TIRVST has expired and a stable reference voltage is reached. For this reason, brief excursions beyond the set point may not be detected during this interval. Refer to Figure 22-2 or Figure 22-3.

### 23.2.3 DEDICATED CAN RECEIVE BUFFER REGISTERS

This section shows the dedicated CAN Receive Buffer registers with their associated control registers.

| REGISTER 23-13: | RXB0CON                                                                                                                                                                                                                                                                                                                                                                                       | : RECEI\                                                                                                   | /E BUFFE    | R 0 CONT      | ROL REGIS     | STER            |                      |         |  |  |  |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|-------------|---------------|---------------|-----------------|----------------------|---------|--|--|--|

| Mada 0          | R/C-0                                                                                                                                                                                                                                                                                                                                                                                         | R/W-0                                                                                                      | R/W-0       | U-0           | R-0           | R/W-0           | R-0                  | R-0     |  |  |  |

| Mode 0          | RXFUL <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                          | RXM1                                                                                                       | RXM0        | —             | RXRTRRO       | RXB0DBEN        | JTOFF <sup>(2)</sup> | FILHIT0 |  |  |  |

| Mode 1.2        | R/C-0                                                                                                                                                                                                                                                                                                                                                                                         | R/W-0                                                                                                      | R-0         | R-0           | R-0           | R-0             | R-0                  | R-0     |  |  |  |

| Mode 1, 2       | RXFUL <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                          | RXM1                                                                                                       | RTRRO       | FILHIT4       | FILHIT3       | FILHIT2         | FILHIT1              | FILHIT0 |  |  |  |

|                 | bit 7                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                            |             |               |               |                 |                      | bit 0   |  |  |  |

| bit 7           | <b>RXFUL:</b> Receive Full Status bit <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                          |                                                                                                            |             |               |               |                 |                      |         |  |  |  |

|                 | <ul> <li>1 = Receive buffer contains a received message</li> <li>0 = Receive buffer is open to receive a new message</li> </ul>                                                                                                                                                                                                                                                               |                                                                                                            |             |               |               |                 |                      |         |  |  |  |

| bit 6           | Combines v                                                                                                                                                                                                                                                                                                                                                                                    | Mode 0:<br><b>RXM1:</b> Receive Buffer Mode bit 1<br>Combines with RXM0 to form RXM<1:0> bits (see bit 5). |             |               |               |                 |                      |         |  |  |  |

|                 | <ul> <li>11 = Receive all messages (including those with errors); filter criteria is ignored</li> <li>10 = Receive only valid messages with extended identifier; EXIDEN in RXFnSIDL must be '1'</li> <li>01 = Receive only valid messages with standard identifier; EXIDEN in RXFnSIDL must be '0'</li> <li>00 = Receive all valid messages as per EXIDEN bit in RXFnSIDL register</li> </ul> |                                                                                                            |             |               |               |                 |                      |         |  |  |  |

|                 | <u>Mode 1, 2:</u><br><b>RXM1</b> : Rec                                                                                                                                                                                                                                                                                                                                                        | eive Buffei                                                                                                | Mode bit 1  |               |               |                 |                      |         |  |  |  |

|                 | 1 = Receive<br>0 = Receive                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                            |             |               |               | ceptance filter | rs are ignore        | ∋d      |  |  |  |

| bit 5           | <u>Mode 0:</u><br><b>RXM0:</b> Rec<br>Combines v                                                                                                                                                                                                                                                                                                                                              |                                                                                                            |             |               | (see bit 6).  |                 |                      |         |  |  |  |

|                 | <u>Mode 1, 2:</u><br><b>RTRRO:</b> Re                                                                                                                                                                                                                                                                                                                                                         | emote Trar                                                                                                 | nsmission R | equest bit fo | or Received N | /lessage (read  | d-only)              |         |  |  |  |

|                 | 1 = A remot<br>0 = A remot                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                            |             |               |               |                 |                      |         |  |  |  |

| bit 4           | <u>Mode 0:</u><br>Unimpleme                                                                                                                                                                                                                                                                                                                                                                   | ented: Rea                                                                                                 | ad as '0'   |               |               |                 |                      |         |  |  |  |

|                 | <u>Mode 1, 2:</u><br>FILHIT4: Fi                                                                                                                                                                                                                                                                                                                                                              | ter Hit bit                                                                                                | 4           | o form filter | acceptance b  | oits <4:0>.     |                      |         |  |  |  |

| bit 3           | Mode 0:<br><b>RXRTRRO:</b> Remote Transmission Request bit for Received Message (read-only)<br>1 = A remote transmission request is received<br>0 = A remote transmission request is not received                                                                                                                                                                                             |                                                                                                            |             |               |               |                 |                      |         |  |  |  |

|                 | Mode 1, 2:<br>FILHIT3: Fil<br>This bit com                                                                                                                                                                                                                                                                                                                                                    |                                                                                                            | -           | o form filter | acceptance b  | oits <4:0>.     |                      |         |  |  |  |

| LII 20-40. |                                                                                                                                   | AON OLLL                        |                |             |            |        |        |        |  |  |

|------------|-----------------------------------------------------------------------------------------------------------------------------------|---------------------------------|----------------|-------------|------------|--------|--------|--------|--|--|

|            | R/W-0                                                                                                                             | R/W-1                           | R/W-0          | R/W-1       | R/W-0      | R/W-0  | R/W-0  | R/W-0  |  |  |

|            | FIL3_1                                                                                                                            | FIL3_0                          | FIL2_1         | FIL2_0      | FIL1_1     | FIL1_0 | FIL0_1 | FIL0_0 |  |  |

|            | bit 7                                                                                                                             |                                 |                |             |            |        |        | bit 0  |  |  |