Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 40MHz                                                                     |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                               |

| Number of I/O              | 25                                                                        |

| Program Memory Size        | 64KB (32K x 16)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 1K x 8                                                                    |

| RAM Size                   | 3.25K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 8x10b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 28-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f2680-i-so |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 3.2.3 RC\_RUN MODE

In RC\_RUN mode, the CPU and peripherals are clocked from the internal oscillator block using the INTOSC multiplexer; the primary clock is shut down. When using the INTRC source, this mode provides the best power conservation of all the Run modes, while still executing code. It works well for user applications which are not highly timing sensitive or do not require high-speed clocks at all times.

If the primary clock source is the internal oscillator block (either INTRC or INTOSC), there are no distinguishable differences between PRI\_RUN and RC\_RUN modes during execution. However, a clock switch delay will occur during entry to and exit from RC\_RUN mode. Therefore, if the primary clock source is the internal oscillator block, the use of RC\_RUN mode is not recommended. This mode is entered by setting SCS1 to '1'. Although it is ignored, it is recommended that SCS0 also be cleared; this is to maintain software compatibility with future devices. When the clock source is switched to the INTOSC multiplexer (see Figure 3-3), the primary oscillator is shut down and the OSTS bit is cleared. The IRCF bits may be modified at any time to immediately change the clock speed.

Note: Caution should be used when modifying a single IRCF bit. If VDD is less than 3V, it is possible to select a higher clock speed than is supported by the low VDD. Improper device operation may result if the VDD/Fosc specifications are violated.

| IABLE 4-4: |                    | IALIZ |                                    |                                                                  | DITIONS FOR ALL                 | REGISTERS |                       |

|------------|--------------------|-------|------------------------------------|------------------------------------------------------------------|---------------------------------|-----------|-----------------------|

| Register   | Applicable Devices |       | Power-on Reset,<br>Brown-out Reset | MCLR Resets,<br>WDT Reset,<br>RESET Instruction,<br>Stack Resets | Wake-up via WDT<br>or Interrupt |           |                       |

| TOSU       | 2585               | 2680  | 4585                               | 4680                                                             | 0 0000                          | 0 0000    | 0 uuuu <sup>(3)</sup> |

| TOSH       | 2585               | 2680  | 4585                               | 4680                                                             | 0000 0000                       | 0000 0000 | uuuu uuuu <b>(3)</b>  |

| TOSL       | 2585               | 2680  | 4585                               | 4680                                                             | 0000 0000                       | 0000 0000 | uuuu uuuu <b>(3)</b>  |

| STKPTR     | 2585               | 2680  | 4585                               | 4680                                                             | 00-0 0000                       | uu-0 0000 | uu-u uuuu <b>(3)</b>  |

| PCLATU     | 2585               | 2680  | 4585                               | 4680                                                             | 0 0000                          | 0 0000    | u uuuu                |

| PCLATH     | 2585               | 2680  | 4585                               | 4680                                                             | 0000 0000                       | 0000 0000 | uuuu uuuu             |

| PCL        | 2585               | 2680  | 4585                               | 4680                                                             | 0000 0000                       | 0000 0000 | PC + 2 <sup>(2)</sup> |

| TBLPTRU    | 2585               | 2680  | 4585                               | 4680                                                             | 00 0000                         | 00 0000   | uu uuuu               |

| TBLPTRH    | 2585               | 2680  | 4585                               | 4680                                                             | 0000 0000                       | 0000 0000 | uuuu uuuu             |

| TBLPTRL    | 2585               | 2680  | 4585                               | 4680                                                             | 0000 0000                       | 0000 0000 | uuuu uuuu             |

| TABLAT     | 2585               | 2680  | 4585                               | 4680                                                             | 0000 0000                       | 0000 0000 | uuuu uuuu             |

| PRODH      | 2585               | 2680  | 4585                               | 4680                                                             | xxxx xxxx                       | uuuu uuuu | uuuu uuuu             |

| PRODL      | 2585               | 2680  | 4585                               | 4680                                                             | xxxx xxxx                       | uuuu uuuu | uuuu uuuu             |

| INTCON     | 2585               | 2680  | 4585                               | 4680                                                             | 0000 000x                       | 0000 000u | uuuu uuuu <b>(1)</b>  |

| INTCON2    | 2585               | 2680  | 4585                               | 4680                                                             | 1111 -1-1                       | 1111 -1-1 | uuuu -u-u <b>(1)</b>  |

| INTCON3    | 2585               | 2680  | 4585                               | 4680                                                             | 11-0 0-00                       | 11-0 0-00 | uu-u u-uu <b>(1)</b>  |

| INDF0      | 2585               | 2680  | 4585                               | 4680                                                             | N/A                             | N/A       | N/A                   |

| POSTINC0   | 2585               | 2680  | 4585                               | 4680                                                             | N/A                             | N/A       | N/A                   |

| POSTDEC0   | 2585               | 2680  | 4585                               | 4680                                                             | N/A                             | N/A       | N/A                   |

| PREINC0    | 2585               | 2680  | 4585                               | 4680                                                             | N/A                             | N/A       | N/A                   |

| PLUSW0     | 2585               | 2680  | 4585                               | 4680                                                             | N/A                             | N/A       | N/A                   |

| FSR0H      | 2585               | 2680  | 4585                               | 4680                                                             | 0000                            | 0000      | uuuu                  |

| FSR0L      | 2585               | 2680  | 4585                               | 4680                                                             | xxxx xxxx                       | uuuu uuuu | uuuu uuuu             |

| WREG       | 2585               | 2680  | 4585                               | 4680                                                             | xxxx xxxx                       | uuuu uuuu | uuuu uuuu             |

| INDF1      | 2585               | 2680  | 4585                               | 4680                                                             | N/A                             | N/A       | N/A                   |

| POSTINC1   | 2585               | 2680  | 4585                               | 4680                                                             | N/A                             | N/A       | N/A                   |

| POSTDEC1   | 2585               | 2680  | 4585                               | 4680                                                             | N/A                             | N/A       | N/A                   |

| PREINC1    | 2585               | 2680  | 4585                               | 4680                                                             | N/A                             | N/A       | N/A                   |

| PLUSW1     | 2585               | 2680  | 4585                               | 4680                                                             | N/A                             | N/A       | N/A                   |

| FSR1H      | 2585               | 2680  | 4585                               | 4680                                                             | 0000                            | 0000      | uuuu                  |

| FSR1L      | 2585               | 2680  | 4585                               | 4680                                                             | xxxx xxxx                       | uuuu uuuu | uuuu uuuu             |

TABLE 4-4:

INITIALIZATION CONDITIONS FOR ALL REGISTERS

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition. Shaded cells indicate conditions do not apply for the designated device.

Note 1: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

**3:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

4: See Table 4-3 for Reset value for specific condition.

**5:** Bits 6 and 7 of PORTA, LATA and TRISA are enabled, depending on the oscillator mode selected. When not enabled as PORTA pins, they are disabled and read '0'.

6: This register reads all '0's until the ECAN<sup>™</sup> technology is set up in Mode 1 or Mode 2.

#### 9.1 **INTCON Registers**

The INTCON registers are readable and writable registers, which contain various enable, priority and flag bits.

Note: Interrupt flag bits are set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the global interrupt enable bit. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt. This feature allows for software polling.

#### **REGISTER 9-1:** INTCON: INTERRUPT CONTROL REGISTER

|                 |           |        |        | -     |        |        |       |

|-----------------|-----------|--------|--------|-------|--------|--------|-------|

| R/W-0           | R/W-0     | R/W-0  | R/W-0  | R/W-0 | R/W-0  | R/W-0  | R/W-x |

| <b>GIE/GIEH</b> | PEIE/GIEL | TMR0IE | INT0IE | RBIE  | TMR0IF | INT0IF | RBIF  |

| bit 7           |           |        |        |       |        |        | bit 0 |

|                 |           |        |        |       |        |        |       |

bit 7 **GIE/GIEH:** Global Interrupt Enable bit

When IPEN = 0: 1 = Enables all unmasked interrupts 0 = Disables all interrupts When IPEN = 1: 1 = Enables all high priority interrupts 0 = Disables all high priority interrupts bit 6 **PEIE/GIEL:** Peripheral Interrupt Enable bit When IPEN = 0: 1 = Enables all unmasked peripheral interrupts 0 = Disables all peripheral interrupts When IPEN = 1: 1 = Enables all low priority peripheral interrupts 0 = Disables all low priority peripheral interrupts TMR0IE: TMR0 Overflow Interrupt Enable bit bit 5 1 = Enables the TMR0 overflow interrupt 0 = Disables the TMR0 overflow interrupt bit 4 **INTOIE:** INTO External Interrupt Enable bit 1 = Enables the INT0 external interrupt 0 = Disables the INT0 external interrupt bit 3 **RBIE:** RB Port Change Interrupt Enable bit 1 = Enables the RB port change interrupt 0 = Disables the RB port change interrupt bit 2 TMR0IF: TMR0 Overflow Interrupt Flag bit 1 = TMR0 register has overflowed (must be cleared in software) 0 = TMR0 register did not overflow bit 1 INTOIF: INTO External Interrupt Flag bit

- 1 = The INT0 external interrupt occurred (must be cleared in software)

- 0 = The INT0 external interrupt did not occur

- bit 0 **RBIF:** RB Port Change Interrupt Flag bit

- 1 = At least one of the RB7:RB4 pins changed state (must be cleared in software)

- 0 = None of the RB7:RB4 pins have changed state

- Note: A mismatch condition will continue to set this bit. Reading PORTB will end the mismatch condition and allow the bit to be cleared.

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

| REGISTER 9-6: | PIR3: PERIPHERAL INTERRUPT REQUEST (FLAG) REGISTER 3 |                                                                                                                      |             |                              |                       |                       |             |            |  |  |  |  |  |  |  |

|---------------|------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|-------------|------------------------------|-----------------------|-----------------------|-------------|------------|--|--|--|--|--|--|--|

| Mode 0        | R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0            |                                                                                                                      |             |                              |                       |                       |             |            |  |  |  |  |  |  |  |

| Mode 0        | IRXIF                                                | WAKIF                                                                                                                | ERRIF       | TXB2IF                       | TXB1IF <sup>(1)</sup> | TXB0IF <sup>(1)</sup> | RXB1IF      | RXB0IF     |  |  |  |  |  |  |  |

|               | R/W-0                                                | R/W-0                                                                                                                | R/W-0       | R/W-0                        | R/W-0                 | R/W-0                 | R/W-0       | R/W-0      |  |  |  |  |  |  |  |

| Mode 1, 2     | IRXIF                                                | WAKIF                                                                                                                | ERRIF       | TXBnIF                       | TXB1IF <sup>(1)</sup> | TXB0IF <sup>(1)</sup> | RXBnIF      | FIFOWMIF   |  |  |  |  |  |  |  |

|               | bit 7                                                |                                                                                                                      |             |                              |                       | 1                     |             | bit 0      |  |  |  |  |  |  |  |

| hit 7         |                                                      |                                                                                                                      |             | aaa aa latar                 | wat Elea hit          |                       |             |            |  |  |  |  |  |  |  |

| bit 7         |                                                      | <b>RXIF:</b> CAN Invalid Received Message Interrupt Flag bit<br>L = An invalid message has occurred on the CAN bus   |             |                              |                       |                       |             |            |  |  |  |  |  |  |  |

|               |                                                      | 0 = No invalid message on CAN bus                                                                                    |             |                              |                       |                       |             |            |  |  |  |  |  |  |  |

| bit 6         |                                                      | WAKIF: CAN bus Activity Wake-up Interrupt Flag bit<br>1 = Activity on CAN bus has occurred                           |             |                              |                       |                       |             |            |  |  |  |  |  |  |  |

|               |                                                      | L = Activity on CAN bus has occurred                                                                                 |             |                              |                       |                       |             |            |  |  |  |  |  |  |  |

| bit 5         |                                                      | 0 = No activity on CAN bus<br>ERRIF: CAN bus Error Interrupt Flag bit                                                |             |                              |                       |                       |             |            |  |  |  |  |  |  |  |

| 2             |                                                      | <b>ERRIF:</b> CAN bus Error Interrupt Flag bit                                                                       |             |                              |                       |                       |             |            |  |  |  |  |  |  |  |

|               | 0 = No CAI                                           | <ul> <li>1 = An error has occurred in the CAN module (multiple sources)</li> <li>0 = No CAN module errors</li> </ul> |             |                              |                       |                       |             |            |  |  |  |  |  |  |  |

| bit 4         | When CAN                                             |                                                                                                                      |             | nterrupt Fla                 | a hit                 |                       |             |            |  |  |  |  |  |  |  |

|               |                                                      |                                                                                                                      |             |                              |                       | nessage and           | mav be rel  | oaded      |  |  |  |  |  |  |  |

|               | 0 = Transn                                           | nit Buffer 2                                                                                                         | has not co  | mpleted tra                  | nsmission of          | a message             | ,           |            |  |  |  |  |  |  |  |

|               | When CAN                                             |                                                                                                                      |             |                              |                       |                       |             |            |  |  |  |  |  |  |  |

|               |                                                      |                                                                                                                      |             | errupt Flag I<br>rs have cor |                       | smission of a         | a message   | and may be |  |  |  |  |  |  |  |

|               | reload                                               |                                                                                                                      |             |                              |                       |                       | a moodage   | and may be |  |  |  |  |  |  |  |

|               | 0 = No tran                                          |                                                                                                                      |             |                              | (1)                   |                       |             |            |  |  |  |  |  |  |  |

| bit 3         | TXB1IF: C                                            |                                                                                                                      |             |                              |                       | essage and i          | may ba rok  | adad       |  |  |  |  |  |  |  |

|               |                                                      |                                                                                                                      |             |                              | ismission of          |                       | hay be reit | Jaueu      |  |  |  |  |  |  |  |

| bit 2         | TXB0IF: C                                            |                                                                                                                      |             | -                            |                       | C C                   |             |            |  |  |  |  |  |  |  |

|               |                                                      |                                                                                                                      |             |                              |                       | essage and i          | may be relo | baded      |  |  |  |  |  |  |  |

| bit 1         | 0 = Transm<br>When CAN                               |                                                                                                                      |             | npleted trar                 | ismission of          | a message             |             |            |  |  |  |  |  |  |  |

| Dit 1         |                                                      |                                                                                                                      |             | nterrupt Fla                 | g bit                 |                       |             |            |  |  |  |  |  |  |  |

|               |                                                      |                                                                                                                      |             | d a new me                   |                       |                       |             |            |  |  |  |  |  |  |  |

|               |                                                      |                                                                                                                      |             | eived a new                  | message               |                       |             |            |  |  |  |  |  |  |  |

|               | When CAN<br>RXBnIF: A                                |                                                                                                                      |             | errupt Flag b                | oit                   |                       |             |            |  |  |  |  |  |  |  |

|               |                                                      |                                                                                                                      |             |                              | d a new mes           | sage                  |             |            |  |  |  |  |  |  |  |

| bit 0         | 0 = No rece<br>When CAN                              |                                                                                                                      |             | ed a new me                  | essage                |                       |             |            |  |  |  |  |  |  |  |

| Dit U         | RXB0IF: C                                            |                                                                                                                      |             | nterrupt Fla                 | g bit                 |                       |             |            |  |  |  |  |  |  |  |

|               | 1 = Receive                                          | e Buffer 0 h                                                                                                         | nas receive | d a new me                   | ssage                 |                       |             |            |  |  |  |  |  |  |  |

|               | 0 = Receive Buffer 0 has not received a new message  |                                                                                                                      |             |                              |                       |                       |             |            |  |  |  |  |  |  |  |

|               | When CAN<br>Unimplem                                 |                                                                                                                      |             |                              |                       |                       |             |            |  |  |  |  |  |  |  |

|               | When CAN                                             |                                                                                                                      |             |                              |                       |                       |             |            |  |  |  |  |  |  |  |

|               |                                                      |                                                                                                                      |             | errupt Flag I                | oit                   |                       |             |            |  |  |  |  |  |  |  |

|               | 1 = FIFO h<br>0 = FIFO h                             |                                                                                                                      |             |                              |                       |                       |             |            |  |  |  |  |  |  |  |

|               |                                                      | •                                                                                                                    |             |                              | forced to '0'.        |                       |             |            |  |  |  |  |  |  |  |

|               |                                                      |                                                                                                                      |             | -, 110 0110                  |                       |                       |             |            |  |  |  |  |  |  |  |

|               | Legend:                                              |                                                                                                                      |             |                              |                       |                       |             |            |  |  |  |  |  |  |  |

|               | D - Doodo                                            | hla hit                                                                                                              | M = M/ri    | tabla bit                    | 11 - 11-              | implomontor           | hit road a  | nc 'O'     |  |  |  |  |  |  |  |

| TABLE 10-3: PC     | ORTB I/O SUMMARY |     |      |        |                                                                                                                  |  |  |  |  |

|--------------------|------------------|-----|------|--------|------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Pin Name           | Function         | I/O | TRIS | Buffer | Description                                                                                                      |  |  |  |  |

| RB0/INT0/FLT0/AN10 | RB0              | OUT | 0    | DIG    | LATB<0> data output.                                                                                             |  |  |  |  |

|                    |                  | IN  | 1    | TTL    | PORTB<0> data input. Weak pull-up available only in this mode.                                                   |  |  |  |  |

|                    | INT0             | IN  | 1    | ST     | External interrupt 0 input.                                                                                      |  |  |  |  |

|                    | FLT0             | IN  | 1    | ST     | Enhanced PWM Fault input.                                                                                        |  |  |  |  |

|                    | AN10             | IN  | 1    | ANA    | A/D input channel 10. Enabled on POR, this analog input overrides the digital input (read as clear – low level). |  |  |  |  |

| RB1/INT1/AN8       | RB1              | OUT | 0    | DIG    | LATB<1> data output.                                                                                             |  |  |  |  |

|                    |                  | IN  | 1    | TTL    | PORTB<1> data input. Weak pull-up available only in this mode.                                                   |  |  |  |  |

|                    | INT1             | IN  | 1    | ST     | External interrupt 1 input.                                                                                      |  |  |  |  |

|                    | AN8              | IN  | 1    | ANA    | A/D input channel 8. Enabled on POR, this analog input overrides the digital input (read as clear – low level).  |  |  |  |  |

| RB2/INT2/CANTX     | RB2              | OUT | x    | DIG    | LATB<2> data output.                                                                                             |  |  |  |  |

|                    |                  | IN  | 1    | TTL    | PORTB<2> data input. Weak pull-up available only in this mode.                                                   |  |  |  |  |

|                    | INT2             | IN  | 1    | ST     | External interrupt 2 input.                                                                                      |  |  |  |  |

|                    | CANTX            | OUT | 1    | DIG    | CAN transmit signal output. The CAN interface overrides the TRIS<2> control when enabled.                        |  |  |  |  |

| RB3/CANRX          | RB3              | OUT | 0    | DIG    | LATB<3> data output.                                                                                             |  |  |  |  |

|                    |                  | IN  | 1    | TTL    | PORTB<3> data input. Weak pull-up available only in this mode.                                                   |  |  |  |  |

|                    | CANRX            | IN  | 1    | ST     | CAN receive signal input. Pin must be configured as a digital input by setting TRISB<3>.                         |  |  |  |  |

| RB4/KBI0/AN9       | RB4              | OUT | 0    | DIG    | LATB<4> data output.                                                                                             |  |  |  |  |

|                    |                  | IN  | 1    | TTL    | PORTB<4> data input. Weak pull-up available only in this mode.                                                   |  |  |  |  |

|                    | KBI0             | IN  | 1    | TTL    | Interrupt-on-pin change.                                                                                         |  |  |  |  |

|                    | AN9              | IN  | 1    | ANA    | A/D input channel 9. Enabled on POR, this analog input overrides the digital input (read as clear – low level).  |  |  |  |  |

| RB5/KBI1/PGM       | RB5              | OUT | 0    | DIG    | LATB<5> data output.                                                                                             |  |  |  |  |

|                    |                  | IN  | 1    | TTL    | PORTB<5> data input. Weak pull-up available only in this mode.                                                   |  |  |  |  |

|                    | KBI1             | IN  | 1    | TTL    | Interrupt-on-pin change.                                                                                         |  |  |  |  |

|                    | PGM              | IN  | х    | ST     | Low-Voltage Programming mode entry (ICSP™). Enabling this function overrides digital output.                     |  |  |  |  |

| RB6/KBI2/PGC       | RB6              | OUT | 0    | DIG    | LATB<6> data output.                                                                                             |  |  |  |  |

|                    |                  | IN  | 1    | TTL    | PORTB<6> data input. Weak pull-up available only in this mode.                                                   |  |  |  |  |

|                    | KBI2             | IN  | 1    | TTL    | Interrupt-on-pin change.                                                                                         |  |  |  |  |

|                    | PGC              | IN  | x    | ST     | Low-Voltage Programming mode entry (ICSP) clock input.                                                           |  |  |  |  |

| RB7/KBI3/PGD       | RB7              | OUT | 0    | DIG    | LATB<7> data output.                                                                                             |  |  |  |  |

|                    |                  | IN  | 1    | TTL    | PORTB<7> data input. Weak pull-up available only in this mode.                                                   |  |  |  |  |

|                    | KBI3             | IN  | 1    | TTL    | Interrupt-on-pin change.                                                                                         |  |  |  |  |

|                    | PGD              | OUT | x    | DIG    | Low-Voltage Programming mode entry (ICSP) clock output.                                                          |  |  |  |  |

|                    |                  | IN  | x    | ST     | Low-Voltage Programming mode entry (ICSP) clock input.                                                           |  |  |  |  |

TABLE 10-3: PORTB I/O SUMMARY

Legend: PWR = Power Supply; OUT = Output; IN = Input; ANA = Analog Signal; DIG = Digital Output; ST = Schmitt Buffer Input; TTL – TTL Buffer Input

| TABLE 10-4: SUMMARY OF REGISTERS ASSOCIATED WITH PORTB |

|--------------------------------------------------------|

|--------------------------------------------------------|

| Name    | Bit 7                                                    | Bit 6         | Bit 5       | Bit 4   | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |  |  |

|---------|----------------------------------------------------------|---------------|-------------|---------|--------|--------|--------|--------|----------------------------|--|--|

| PORTB   | RB7                                                      | RB6           | RB5         | RB4     | RB3    | RB2    | RB1    | RB0    | 52                         |  |  |

| LATB    | LATB Data Output Register (Read and Write to Data Latch) |               |             |         |        |        |        |        |                            |  |  |

| TRISB   | PORTB Dat                                                | a Direction C | ontrol Regi | ster    |        |        |        |        | 52                         |  |  |

| INTCON  | GIE/GIEH                                                 | PEIE/GIEL     | TMR0IE      | INT0IE  | RBIE   | TMR0IF | INT0IF | RBIF   | 49                         |  |  |

| INTCON2 | RBPU                                                     | INTEDG0       | INTEDG1     | INTEDG2 |        | TMR0IP | _      | RBIP   | 49                         |  |  |

| INTCON3 | INT2IP                                                   | INT1IP        | —           | INT2IE  | INT1IE | —      | INT2IF | INT1IF | 49                         |  |  |

| ADCON1  | _                                                        | _             | VCFG1       | VCFG0   | PCFG3  | PCFG2  | PCFG1  | PCFG0  | 50                         |  |  |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by PORTB.

#### 11.3 Prescaler

An 8-bit counter is available as a prescaler for the Timer0 module. The prescaler is not directly readable or writable; its value is set by the PSA and T0PS2:T0PS0 bits (T0CON<3:0>) which determine the prescaler assignment and prescale ratio.

Clearing the PSA bit assigns the prescaler to the Timer0 module. When it is assigned, prescale values from 1:2 through 1:256 in power-of-2 increments are selectable.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g., CLRF TMR0, MOVWF TMR0, BSF TMR0, etc.) clear the prescaler count.

| Note: | Writing to TMR0 when the prescaler is       |

|-------|---------------------------------------------|

|       | assigned to Timer0 will clear the prescaler |

|       | count but will not change the prescaler     |

|       | assignment.                                 |

#### 11.3.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control and can be changed "on-the-fly" during program execution.

### 11.4 Timer0 Interrupt

The TMR0 interrupt is generated when the TMR0 register overflows from FFh to 00h in 8-bit mode, or from FFFFh to 0000h in 16-bit mode. This overflow sets the TMR0IF flag bit. The interrupt can be masked by clearing the TMR0IE bit (INTCON<5>). Before reenabling the interrupt, the TMR0IF bit must be cleared in software by the Interrupt Service Routine.

Since Timer0 is shut down in Sleep mode, the TMR0 interrupt cannot awaken the processor from Sleep.

TABLE 11-1:

REGISTERS ASSOCIATED WITH TIMER0

| Name   | Bit 7                            | Bit 6                                             | Bit 5       | Bit 4    | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Reset<br>Values<br>on page |  |  |

|--------|----------------------------------|---------------------------------------------------|-------------|----------|-------|-------|-------|-------|----------------------------|--|--|

| TMR0L  | Timer0 Module Low Byte Register  |                                                   |             |          |       |       |       |       |                            |  |  |

| TMR0H  | Timer0 Module High Byte Register |                                                   |             |          |       |       |       |       |                            |  |  |

| INTCON | GIE/GIEH                         | H PEIE/GIEL TMROIE INTOIE RBIE TMROIF INTOIF RBIF |             |          |       |       |       |       |                            |  |  |

| T0CON  | TMR0ON                           | T08BIT T0CS T0SE PSA T0PS2 T0PS1 T0PS0            |             |          |       |       |       |       |                            |  |  |

| TRISA  | —                                | PORTA Data                                        | a Direction | Register |       |       |       |       | 52                         |  |  |

**Legend:** x = unknown, u = unchanged, — = unimplemented locations, read as '0'. Shaded cells are not used by Timer0.

#### 17.3.8 OPERATION IN POWER MANAGED MODES

In SPI Master mode, module clocks may be operating at a different speed than when in full power mode; in the case of the Sleep mode, all clocks are halted.

In most power managed modes, a clock is provided to the peripherals. That clock should be from the primary clock source, the secondary clock (Timer1 oscillator at 32.768 kHz) or the INTOSC source. See **Section 2.7 "Clock Sources and Oscillator Switching**" for additional information.

In most cases, the speed that the master clocks SPI data is not important; however, this should be evaluated for each system.

If MSSP interrupts are enabled, they can wake the controller from Sleep mode, or one of the Idle modes, when the master completes sending data. If an exit from Sleep or Idle mode is not desired, MSSP interrupts should be disabled.

If the Sleep mode is selected, all module clocks are halted and the transmission/reception will remain in that state until the devices wakes. After the device returns to Run mode, the module will resume transmitting and receiving data.

In SPI Slave mode, the SPI Transmit/Receive Shift register operates asynchronously to the device. This allows the device to be placed in any power managed mode and data to be shifted into the SPI Transmit/ Receive Shift register. When all 8 bits have been received, the MSSP interrupt flag bit will be set and if enabled, will wake the device.

#### 17.3.9 EFFECTS OF A RESET

A Reset disables the MSSP module and terminates the current transfer.

#### 17.3.10 BUS MODE COMPATIBILITY

Table 17-1 shows the compatibility between the standard SPI modes and the states of the CKP and CKE control bits.

| Standard SPI Mode | Control Bits State |     |  |  |  |

|-------------------|--------------------|-----|--|--|--|

| Terminology       | СКР                | CKE |  |  |  |

| 0, 0              | 0                  | 1   |  |  |  |

| 0, 1              | 0                  | 0   |  |  |  |

| 1, 0              | 1                  | 1   |  |  |  |

| 1, 1              | 1                  | 0   |  |  |  |

#### TABLE 17-1: SPI BUS MODES

There is also a SMP bit which controls when the data is sampled.

| Name    | Bit 7                | Bit 6         | Bit 5        | Bit 4         | Bit 3        | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

|---------|----------------------|---------------|--------------|---------------|--------------|--------|--------|--------|----------------------------|

| INTCON  | GIE/GIEH             | PEIE/GIEL     | TMR0IE       | <b>INTOIE</b> | RBIE         | TMR0IF | INT0IF | RBIF   | 49                         |

| PIR1    | PSPIF <sup>(1)</sup> | ADIF          | RCIF         | TXIF          | SSPIF        | CCP1IF | TMR2IF | TMR1IF | 52                         |

| PIE1    | PSPIE <sup>(1)</sup> | ADIE          | RCIE         | TXIE          | SSPIE        | CCP1IE | TMR2IE | TMR1IE | 52                         |

| IPR1    | PSPIP <sup>(1)</sup> | ADIP          | RCIP         | TXIP          | SSPIP        | CCP1IP | TMR2IP | TMR1IP | 52                         |

| TRISA   | PORTA Da             | ta Direction  | Register     |               |              |        |        |        | 52                         |

| TRISC   | PORTC Da             | ata Direction | Register     |               |              |        |        |        | 52                         |

| SSPBUF  | Synchrono            | us Serial Po  | rt Receive E | Buffer/Transi | mit Register |        |        |        | 50                         |

| SSPCON1 | WCOL                 | SSPOV         | SSPEN        | CKP           | SSPM3        | SSPM2  | SSPM1  | SSPM0  | 50                         |

| SSPSTAT | SMP                  | CKE           | D/A          | Р             | S            | R/W    | UA     | BF     | 50                         |

TABLE 17-2: REGISTERS ASSOCIATED WITH SPI OPERATION

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by the MSSP in SPI mode.

**Note 1:** These bits are unimplemented in PIC18F2X8X devices; always maintain these bits clear.

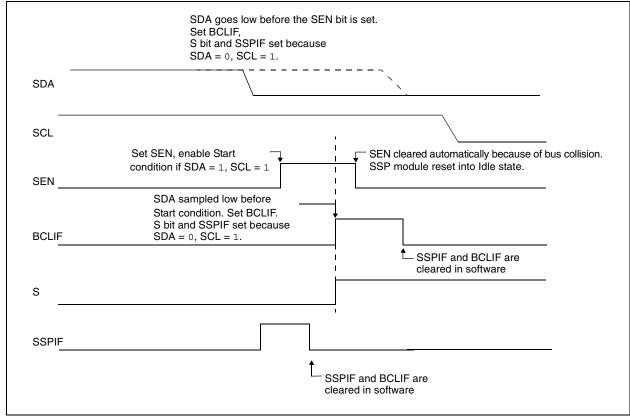

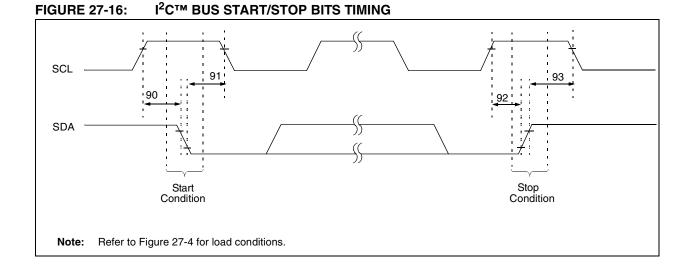

### 17.4.17.1 Bus Collision During a Start Condition

During a Start condition, a bus collision occurs if:

- a) SDA or SCL are sampled low at the beginning of the Start condition (Figure 17-26).

- b) SCL is sampled low before SDA is asserted low (Figure 17-27).

During a Start condition, both the SDA and the SCL pins are monitored.

If the SDA pin is already low, or the SCL pin is already low, then all of the following occur:

- the Start condition is aborted,

- the BCLIF flag is set; and

- the MSSP module is reset to its Idle state (Figure 17-26).

The Start condition begins with the SDA and SCL pins deasserted. When the SDA pin is sampled high, the Baud Rate Generator is loaded from SSPADD<6:0> and counts down to 0. If the SCL pin is sampled low while SDA is high, a bus collision occurs because it is assumed that another master is attempting to drive a data '1' during the Start condition.

If the SDA pin is sampled low during this count, the BRG is reset and the SDA line is asserted early (Figure 17-28). If, however, a '1' is sampled on the SDA pin, the SDA pin is asserted low at the end of the BRG count. The Baud Rate Generator is then reloaded and counts down to 0 and during this time, if the SCL pins are sampled as '0', a bus collision does not occur. At the end of the BRG count, the SCL pin is asserted low.

Note: The reason that bus collision is not a factor during a Start condition is that no two bus masters can assert a Start condition at the exact same time. Therefore, one master will always assert SDA before the other. This condition does not cause a bus collision because the two masters must be allowed to arbitrate the first address following the Start condition. If the address is the same, arbitration must be allowed to continue into the data portion, Repeated Start or Stop conditions.

#### FIGURE 17-26: BUS COLLISION DURING START CONDITION (SDA ONLY)

| TER 18-1: | TXSTA: T                                                                                                                                      | RANSMIT S                                          | STATUS A      | ND CONT      | ROL REGI  | STER       |              |       |  |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|---------------|--------------|-----------|------------|--------------|-------|--|

|           | R/W-0                                                                                                                                         | R/W-0                                              | R/W-0         | R/W-0        | R/W-0     | R/W-0      | R-1          | R/W-0 |  |

|           | CSRC                                                                                                                                          | TX9                                                | TXEN          | SYNC         | SENDB     | BRGH       | TRMT         | TX9D  |  |

|           | bit 7                                                                                                                                         |                                                    |               |              |           |            |              | bit 0 |  |

| bit 7     |                                                                                                                                               | ock Source S                                       | elect bit     |              |           |            |              |       |  |

|           | <u>Asynchron</u><br>Don't care.                                                                                                               |                                                    |               |              |           |            |              |       |  |

|           |                                                                                                                                               | <u>ous mode:</u><br>r mode (clock<br>mode (clock t |               |              | om BRG)   |            |              |       |  |

| bit 6     | <b>TX9:</b> 9-bit                                                                                                                             | Transmit Ena                                       | able bit      |              |           |            |              |       |  |

|           |                                                                                                                                               | ts 9-bit transr<br>ts 8-bit transr                 |               |              |           |            |              |       |  |

| bit 5     | TXEN: Tra                                                                                                                                     | nsmit Enable                                       | e bit         |              |           |            |              |       |  |

|           |                                                                                                                                               | mit enabled<br>mit disabled                        |               |              |           |            |              |       |  |

|           | Note:                                                                                                                                         | SREN/CRE                                           | N overrides   | TXEN in S    | ync mode. |            |              |       |  |

| bit 4     | SYNC: EU                                                                                                                                      | SART Mode                                          | Select bit    |              |           |            |              |       |  |

|           | -                                                                                                                                             | ironous mode<br>hronous mod                        |               |              |           |            |              |       |  |

| bit 3     | SENDB: S                                                                                                                                      | end Break C                                        | haracter bit  |              |           |            |              |       |  |

|           | Asynchronous mode:<br>1 = Send Sync Break on next transmission (cleared by hardware upon completion)<br>0 = Sync Break transmission completed |                                                    |               |              |           |            |              |       |  |

|           | <u>Synchrono</u><br>Don't care.                                                                                                               |                                                    |               |              |           |            |              |       |  |

| bit 2     | BRGH: Hig                                                                                                                                     | gh Baud Rate                                       | e Select bit  |              |           |            |              |       |  |

|           | Asynchronous mode:<br>1 = High speed<br>0 = Low speed                                                                                         |                                                    |               |              |           |            |              |       |  |

|           | <u>Synchrono</u><br>Unused in                                                                                                                 | ous mode:                                          |               |              |           |            |              |       |  |

| bit 1     | TRMT: Tra                                                                                                                                     | nsmit Shift R                                      | egister Stat  | us bit       |           |            |              |       |  |

|           | 1 = TSR e<br>0 = TSR fi                                                                                                                       | empty                                              | 0             |              |           |            |              |       |  |

| bit 0     | <b>TX9D:</b> 9th                                                                                                                              | bit of Transm                                      | nit Data      |              |           |            |              |       |  |

|           | Can be ad                                                                                                                                     | dress/data bi                                      | t or a parity | bit.         |           |            |              |       |  |

|           | Legend:                                                                                                                                       |                                                    |               |              |           |            |              |       |  |

|           | R = Reada                                                                                                                                     | ıble bit                                           | W = W         | /ritable bit | U = Unin  | nplemented | bit, read as | '0'   |  |

### REGISTER 18-1: TXSTA: TRANSMIT STATUS AND CONTROL REGISTER

DS39625C-page 228

-n = Value at POR

'1' = Bit is set

'0' = Bit is cleared

x = Bit is unknown

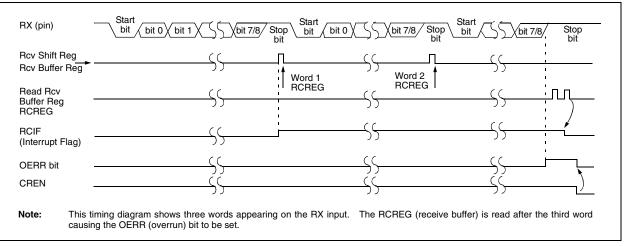

#### FIGURE 18-7: ASYNCHRONOUS RECEPTION

#### TABLE 18-6: REGISTERS ASSOCIATED WITH ASYNCHRONOUS RECEPTION

| Name                                                 | Bit 7                                              | Bit 6        | Bit 5  | Bit 4  | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

|------------------------------------------------------|----------------------------------------------------|--------------|--------|--------|-------|--------|--------|--------|----------------------------|

| INTCON                                               | GIE/GIEH                                           | PEIE/GIEL    | TMR0IE | INT0IE | RBIE  | TMR0IF | INT0IF | RBIF   | 49                         |

| PIR1                                                 | PSPIF <sup>(1)</sup>                               | ADIF         | RCIF   | TXIF   | SSPIF | CCP1IF | TMR2IF | TMR1IF | 52                         |

| PIE1                                                 | PSPIE <sup>(1)</sup>                               | ADIE         | RCIE   | TXIE   | SSPIE | CCP1IE | TMR2IE | TMR1IE | 52                         |

| IPR1                                                 | PSPIP <sup>(1)</sup>                               | ADIP         | RCIP   | TXIP   | SSPIP | CCP1IP | TMR2IP | TMR1IP | 52                         |

| RCSTA                                                | SPEN                                               | RX9          | SREN   | CREN   | ADDEN | FERR   | OERR   | RX9D   | 51                         |

| RCREG                                                | EUSART F                                           | Receive Regi | ster   |        |       |        |        |        | 51                         |

| TXSTA                                                | CSRC                                               | TX9          | TXEN   | SYNC   | SENDB | BRGH   | TRMT   | TX9D   | 51                         |

| BAUDCON                                              | ABDOVF                                             | RCIDL        |        | SCKP   | BRG16 | —      | WUE    | ABDEN  | 51                         |

| SPBRGH EUSART Baud Rate Generator Register High Byte |                                                    |              |        |        |       |        |        | 51     |                            |

| SPBRG                                                | SPBRG EUSART Baud Rate Generator Register Low Byte |              |        |        |       |        |        | 51     |                            |

|                                                      |                                                    |              |        |        |       |        |        |        |                            |

**Legend:** — = unimplemented locations read as '0'. Shaded cells are not used for asynchronous reception.

**Note 1:** Reserved in PIC18F2X8X devices; always maintain these bits clear.

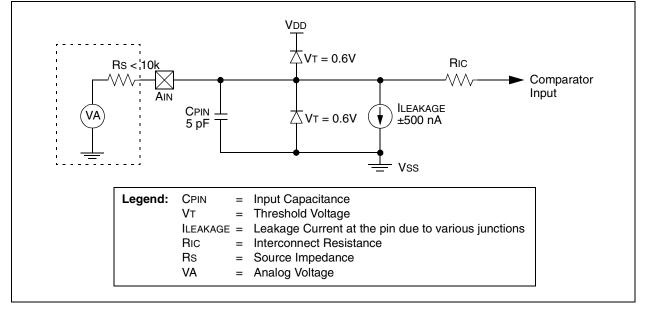

#### 20.9 Analog Input Connection Considerations

A simplified circuit for an analog input is shown in Figure 20-4. Since the analog pins are connected to a digital output, they have reverse biased diodes to VDD and Vss. The analog input, therefore, must be between Vss and VDD. If the input voltage deviates from this

range by more than 0.6V in either direction, one of the diodes is forward biased and a latch-up condition may occur. A maximum source impedance of 10 k $\Omega$  is recommended for the analog sources. Any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have very little leakage current.

#### FIGURE 20-4: COMPARATOR ANALOG INPUT MODEL

#### TABLE 20-1: REGISTERS ASSOCIATED WITH COMPARATOR MODULE

| Name                  | Bit 7                 | Bit 6                 | Bit 5                     | Bit 4        | Bit 3      | Bit 2  | Bit 1  | Bit 0                  | Reset<br>Values<br>on page |

|-----------------------|-----------------------|-----------------------|---------------------------|--------------|------------|--------|--------|------------------------|----------------------------|

| CMCON <sup>(3)</sup>  | C2OUT                 | C1OUT                 | C2INV                     | C1INV        | CIS        | CM2    | CM1    | CM0                    | 51                         |

| CVRCON <sup>(3)</sup> | CVREN                 | CVROE                 | CVRR                      | CVRSS        | CVR3       | CVR2   | CVR1   | CVR0                   | 51                         |

| INTCON                | GIE/GIEH              | PEIE/GIEL             | TMR0IE                    | INT0IE       | RBIE       | TMR0IF | INT0IF | RBIF                   | 52                         |

| IPR2                  | OSCFIP                | CMIP <sup>(2)</sup>   | _                         | EEIP         | BCLIP      | HLVDIP | TMR3IP | ECCP1IP <sup>(2)</sup> | 51                         |

| PIR2                  | OSCFIF                | CMIF <sup>(2)</sup>   | _                         | EEIF         | BCLIF      | HLVDIF | TMR3IF | ECCP1IF <sup>(2)</sup> | 51                         |

| PIE2                  | OSCFIE                | CMIE <sup>(2)</sup>   | _                         | EEIE         | BCLIE      | HLVDIE | TMR3IE | ECCP1IE <sup>(2)</sup> | 52                         |

| PORTA                 | RA7 <sup>(1)</sup>    | RA6 <sup>(1)</sup>    | RA5                       | RA4          | RA3        | RA2    | RA1    | RA0                    | 52                         |

| LATA                  | LATA7 <sup>(1)</sup>  | LATA6 <sup>(1)</sup>  | LATA Data Output Register |              |            |        |        |                        | 52                         |

| TRISA                 | TRISA7 <sup>(1)</sup> | TRISA6 <sup>(1)</sup> | PORTA Da                  | ata Directio | n Register |        |        |                        | 52                         |

Legend: — = unimplemented, read as '0'. Shaded cells are unused by the comparator module.

Note 1: PORTA pins are enabled based on oscillator configuration.

2: These bits are available in PIC18F4X8X devices and reserved in PIC18F2X8X devices.

3: These registers are unimplemented on PIC18F2X8X devices.

| 51EN 23-1. | CANCON                                                                                      |                                |                | GISIEN                                  |              |            |                |            |  |  |

|------------|---------------------------------------------------------------------------------------------|--------------------------------|----------------|-----------------------------------------|--------------|------------|----------------|------------|--|--|

| Mada 0     | R/W-1                                                                                       | R/W-0                          | R/W-0          | R/S-0                                   | R/W-0        | R/W-0      | R/W-0          | U-0        |  |  |

| Mode 0     | REQOP2                                                                                      | REQOP1                         | REQOP0         | ABAT                                    | WIN2         | WIN1       | WIN0           | —          |  |  |

|            | DAM 4                                                                                       |                                |                |                                         |              |            |                |            |  |  |

| Mode 1     | R/W-1                                                                                       | R/W-0                          | R/W-0          | R/S-0                                   | U-0          | U-0        | U-0            | U-0        |  |  |

|            | REQOP2                                                                                      | REQOP1                         | REQOP0         | ABAT                                    | _            |            |                | —          |  |  |

|            | R/W-1                                                                                       | R/W-0                          | R/W-0          | R/S-0                                   | R-0          | R-0        | R-0            | R-0        |  |  |

| Mode 2     | REQOP2                                                                                      | REQOP1                         | REQOP0         | ABAT                                    | FP3          | FP2        | FP1            | FP0        |  |  |

|            | bit 7                                                                                       | n.Edoi i                       | 1120010        | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |              |            |                | bit 0      |  |  |

|            |                                                                                             |                                |                |                                         |              |            |                |            |  |  |

| bit 7-5    | REQOP2:F                                                                                    | REQOP0: R                      | equest CAN     | Operation N                             | /lode bits   |            |                |            |  |  |

|            |                                                                                             |                                | uration mode   | -                                       |              |            |                |            |  |  |

|            |                                                                                             | uest Listen (                  |                |                                         |              |            |                |            |  |  |

|            |                                                                                             | uest Loopba                    |                |                                         |              |            |                |            |  |  |

|            |                                                                                             | uest Disable                   |                |                                         |              |            |                |            |  |  |

| L:1 4      | •                                                                                           | uest Normal                    |                |                                         |              |            |                |            |  |  |

| bit 4      |                                                                                             |                                | ng Transmiss   |                                         |              |            |                |            |  |  |

|            |                                                                                             |                                | ansmissions    |                                         | mit buffers) |            |                |            |  |  |

| bit 3-1    | Mode 0:                                                                                     |                                | securing de m  | orman                                   |              |            |                |            |  |  |

|            |                                                                                             | WIN2:WIN0: Window Address bits |                |                                         |              |            |                |            |  |  |

|            | These bits select which of the CAN buffers to switch into the access bank area. This allows |                                |                |                                         |              |            |                |            |  |  |

|            |                                                                                             |                                | gisters from a |                                         |              |            |                |            |  |  |

|            | -                                                                                           |                                | CODE0 bits     | -                                       | ied to the W | IN3:WIN0 b | ts to select t | he correct |  |  |

|            |                                                                                             | =                              | 3-2 for a code | e example.                              |              |            |                |            |  |  |

|            |                                                                                             | eive Buffer (                  |                |                                         |              |            |                |            |  |  |

|            |                                                                                             | eive Buffer (<br>eive Buffer 1 |                |                                         |              |            |                |            |  |  |

|            |                                                                                             | smit Buffer                    |                |                                         |              |            |                |            |  |  |

|            | 011 <b>= Tran</b>                                                                           | smit Buffer                    | 1              |                                         |              |            |                |            |  |  |

|            |                                                                                             | smit Buffer                    |                |                                         |              |            |                |            |  |  |

|            |                                                                                             | eive Buffer (<br>eive Buffer ( |                |                                         |              |            |                |            |  |  |

| bit 0      |                                                                                             |                                |                |                                         |              |            |                |            |  |  |

| bit 4-0    | Mode 1:                                                                                     | ented: Rea                     |                |                                         |              |            |                |            |  |  |

| Dit 4-0    |                                                                                             | ented: Rea                     | d as '∩'       |                                         |              |            |                |            |  |  |

|            | Mode 2:                                                                                     | enteu. nea                     |                |                                         |              |            |                |            |  |  |

|            |                                                                                             | FIFO Read F                    | Pointer bits   |                                         |              |            |                |            |  |  |

|            | These bits                                                                                  | point to the                   | message bu     | ffer to be re                           | ad.          |            |                |            |  |  |

|            | These bits point to the message buffer to be read.<br>0111:0000 = Message buffer to be read |                                |                |                                         |              |            |                |            |  |  |

|            | 1111:100                                                                                    | 0 = Reserve                    | ed             |                                         |              |            |                |            |  |  |

|            | Γ-                                                                                          |                                |                |                                         |              |            |                | 1          |  |  |

|            | Legend:                                                                                     |                                |                |                                         |              |            |                |            |  |  |

|            | R = Reada                                                                                   |                                | W = Writat     |                                         |              | -          | bit, read as ' |            |  |  |

|            | -n = Value                                                                                  | at POR                         | '1' = Bit is   | set                                     | '0' = Bit is | cleared    | x = Bit is u   | nknown     |  |  |

#### REGISTER 23-1: CANCON: CAN CONTROL REGISTER

| ER 23-31: |                                                                                                                                      | ASK SELE | CI REGIS     | IER 3     |            |         |         |         |  |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------|----------|--------------|-----------|------------|---------|---------|---------|--|

|           | R/W-0                                                                                                                                | R/W-0    | R/W-0        | R/W-0     | R/W-0      | R/W-0   | R/W-0   | R/W-0   |  |

|           | FIL15_1                                                                                                                              | FIL15_0  | FIL14_1      | FIL14_0   | FIL13_1    | FIL13_0 | FIL12_1 | FIL12_0 |  |

|           | bit 7                                                                                                                                |          |              |           |            |         |         | bit 0   |  |

| bit 7-6   | 11 = No mas                                                                                                                          |          | 5 Select bit | s 1 and 0 |            |         |         |         |  |

|           | 10 = Filter 15<br>01 = Acceptance Mask 1<br>00 = Acceptance Mask 0                                                                   |          |              |           |            |         |         |         |  |

| bit 5-4   | FIL14_1:FIL14_0: Filter 14 Select bits 1 and 0<br>11 = No mask<br>10 = Filter 15<br>01 = Acceptance Mask 1<br>00 = Acceptance Mask 0 |          |              |           |            |         |         |         |  |

| bit 3-2   | 11 = No mas<br>10 = Filter 1<br>01 = Accept                                                                                          | 5        | 3 Select bit | s 1 and 0 |            |         |         |         |  |

| bit 1-0   | 11 = No mas<br>10 = Filter 1<br>01 = Accept<br>00 = Accept                                                                           | 5        |              |           | nd 2 only. |         |         |         |  |

|           |                                                                                                                                      |          |              |           |            |         |         |         |  |

### REGISTER 23-51: MSEL3: MASK SELECT REGISTER 3<sup>(1)</sup>

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented b  | pit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### TABLE 23-1: CAN CONTROLLER REGISTER MAP (CONTINUED)

| Address <sup>(1)</sup> | Name      |  |  |  |  |

|------------------------|-----------|--|--|--|--|

| D7Fh                   | (4)       |  |  |  |  |

| D7Eh                   | (4)       |  |  |  |  |

| D7Dh                   | (4)       |  |  |  |  |

| D7Ch                   | (4)       |  |  |  |  |

| D7Bh                   | RXF11EIDL |  |  |  |  |