Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 25MHz                                                                     |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                               |

| Number of I/O              | 36                                                                        |

| Program Memory Size        | 48KB (24K x 16)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 1K x 8                                                                    |

| RAM Size                   | 3.25K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 11x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 44-VQFN Exposed Pad                                                       |

| Supplier Device Package    | 44-QFN (8x8)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f4585-e-ml |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 3.5.4 EXIT WITHOUT AN OSCILLATOR START-UP DELAY

Certain exits from power managed modes do not invoke the OST at all. There are two cases:

- PRI\_IDLE mode where the primary clock source is not stopped; and

- the primary clock source is not any of the LP, XT, HS or HSPLL modes.

In these instances, the primary clock source either does not require an oscillator start-up delay, since it is already running (PRI\_IDLE), or normally does not require an oscillator start-up delay (RC, EC and INTIO Oscillator modes). However, a fixed delay of interval TCSD following the wake event is still required when leaving Sleep and Idle modes to allow the CPU to prepare for execution. Instruction execution resumes on the first clock cycle following this delay.

## TABLE 3-2:EXIT DELAY ON WAKE-UP BY RESET FROM SLEEP MODE OR ANY IDLE MODE<br/>(BY CLOCK SOURCES)

| Clock Source<br>Before Wake-up          | Clock Source<br>After Wake-up | Exit Delay                            | Clock Ready Status<br>Bit (OSCCON) |

|-----------------------------------------|-------------------------------|---------------------------------------|------------------------------------|

|                                         | LP, XT, HS                    |                                       |                                    |

| Drive and Device Ole als                | HSPLL                         |                                       | OSTS                               |

| Primary Device Clock<br>(PRI_IDLE mode) | EC, RC                        | Tcsd <sup>(2)</sup>                   |                                    |

|                                         | INTRC <sup>(1)</sup>          |                                       | —                                  |

|                                         | INTOSC <sup>(3)</sup>         |                                       | IOFS                               |

|                                         | LP, XT, HS                    | Tost <sup>(4)</sup>                   |                                    |

|                                         | HSPLL                         | Tost + t <sub>rc</sub> (4)            | OSTS                               |

| T1OSC or INTRC <sup>(1)</sup>           | EC, RC                        | T <sub>CSD</sub> (2)                  |                                    |

|                                         | INTRC <sup>(1)</sup>          | 103047                                | —                                  |

|                                         | INTOSC <sup>(2)</sup>         | TIOBST <sup>(5)</sup>                 | IOFS                               |

|                                         | LP, XT, HS                    | Tost <sup>(5)</sup>                   |                                    |

|                                         | HSPLL                         | Tost + t <sub>rc</sub> (4)            | OSTS                               |

| INTOSC <sup>(3)</sup>                   | EC, RC                        | T <sub>CSD</sub> (2)                  |                                    |

|                                         | INTRC <sup>(1)</sup>          | 105047                                | —                                  |

|                                         | INTOSC <sup>(2)</sup>         | None                                  | IOFS                               |

|                                         | LP, XT, HS                    | Tost <sup>(4)</sup>                   |                                    |

|                                         | HSPLL                         | TOST + t <sub>rc</sub> <sup>(4)</sup> | OSTS                               |

| None<br>(Sleep mode)                    | EC, RC                        | TCSD(2)                               | ]                                  |

|                                         | INTRC <sup>(1)</sup>          |                                       | —                                  |

|                                         | INTOSC <sup>(2)</sup>         | TIOBST <sup>(5)</sup>                 | IOFS                               |

**Note 1:** In this instance, refers specifically to the 31 kHz INTRC clock source.

2: TCSD (parameter 38) is a required delay when waking from Sleep and all Idle modes and runs concurrently with any other required delays (see Section 3.4 "Idle Modes").

- 3: Includes both the INTOSC 8 MHz source and postscaler derived frequencies.

- 4: TOST is the Oscillator Start-up Timer (parameter 32). t<sub>rc</sub> is the PLL Lock-out Timer (parameter F12); it is also designated as TPLL.

- 5: Execution continues during TIOBST (parameter 39), the INTOSC stabilization period.

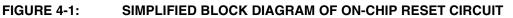

### 4.0 RESET

The PIC18F2585/2680/4585/4680 devices differentiate between various kinds of Reset:

- a) Power-on Reset (POR)

- b) MCLR Reset during normal operation

- c) MCLR Reset during power managed modes

- d) Watchdog Timer (WDT) Reset (during execution)

- e) Programmable Brown-out Reset (BOR)

- f) RESET Instruction

- g) Stack Full Reset

- h) Stack Underflow Reset

This section discusses Resets generated by MCLR, POR and BOR and covers the operation of the various start-up timers. Stack Reset events are covered in Section 5.1.2.4 "Stack Full and Underflow Resets". WDT Resets are covered in Section 24.2 "Watchdog Timer (WDT)". A simplified block diagram of the On-Chip Reset Circuit is shown in Figure 4-1.

### 4.1 RCON Register

Device Reset events are tracked through the RCON register (Register 4-1). The lower five bits of the register indicate that a specific Reset event has occurred. In most cases, these bits can only be cleared by the event and must be set by the application after the event. The state of these flag bits, taken together, can be read to indicate the type of Reset that just occurred. This is described in more detail in **Section 4.6 "Reset State of Registers"**.

The RCON register also has control bits for setting interrupt priority (IPEN) and software control of the BOR (SBOREN). Interrupt priority is discussed in Section 9.0 "Interrupts". BOR is covered in Section 4.4 "Brown-out Reset (BOR)".

| TADLE 4-4.               |      | INTIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED) |        |                                       |                      |      |                 |                                           |                                 |      |  |  |  |  |  |

|--------------------------|------|--------------------------------------------------------|--------|---------------------------------------|----------------------|------|-----------------|-------------------------------------------|---------------------------------|------|--|--|--|--|--|

| Register                 | Ар   | olicabl                                                | e Devi | ces                                   | Power-oi<br>Brown-oi | ,    | WDT<br>RESET IN | Resets,<br>Reset,<br>struction,<br>Resets | Wake-up via WDT<br>or Interrupt |      |  |  |  |  |  |

| BSEL0 <sup>(6)</sup>     | 2585 | 2680                                                   | 4585   | 4680                                  | 0000                 | 00   | 0000            | 00                                        | uuuu                            | uu   |  |  |  |  |  |

| MSEL3 <sup>(6)</sup>     | 2585 | 2680                                                   | 4585   | 4680                                  | 0000                 | 0000 | 0000            | 0000                                      | uuuu                            | uuuu |  |  |  |  |  |

| MSEL2 <sup>(6)</sup>     | 2585 | 2680                                                   | 4585   | 4680                                  | 0000                 | 0000 | 0000            | 0000                                      | uuuu                            | uuuu |  |  |  |  |  |

| MSEL1 <sup>(6)</sup>     | 2585 | 2680                                                   | 4585   | 4680                                  | 0000                 | 0101 | 0000            | 0101                                      | uuuu                            | uuuu |  |  |  |  |  |

| MSEL0 <sup>(6)</sup>     | 2585 | 2680                                                   | 4585   | 4680                                  | 0101                 | 0000 | 0101            | 0000                                      | uuuu                            | uuuu |  |  |  |  |  |

| SDFLC <sup>(6)</sup>     | 2585 | 2680                                                   | 4585   | 4680                                  | 0                    | 0000 | 0               | 0000                                      | -u                              | uuuu |  |  |  |  |  |

| RXFCON1 <sup>(6)</sup>   | 2585 | 2680                                                   | 4585   | 4680                                  | 0000                 | 0000 | 0000            | 0000                                      | uuuu                            | uuuu |  |  |  |  |  |

| RXFCON0 <sup>(6)</sup>   | 2585 | 2680                                                   | 4585   | 4680                                  | 0000                 | 0000 | 0000            | 0000                                      | uuuu                            | uuuu |  |  |  |  |  |

| RXFBCON7 <sup>(6)</sup>  | 2585 | 2680                                                   | 4585   | 4680                                  | 0000                 | 0000 | 0000            | 0000                                      | uuuu                            | uuuu |  |  |  |  |  |

| RXFBCON6 <sup>(6)</sup>  | 2585 | 2680                                                   | 4585   | 4680                                  | 0000                 | 0000 | 0000            | 0000                                      | uuuu                            | uuuu |  |  |  |  |  |

| RXFBCON5 <sup>(6)</sup>  | 2585 | 2680                                                   | 4585   | 4680                                  | 0000                 | 0000 | 0000            | 0000                                      | uuuu                            | uuuu |  |  |  |  |  |

| RXFBCON4 <sup>(6)</sup>  | 2585 | 2680                                                   | 4585   | 4680                                  | 0000                 | 0000 | 0000            | 0000                                      | uuuu                            | uuuu |  |  |  |  |  |

| RXFBCON3(6)              | 2585 | 2680                                                   | 4585   | 4680                                  | 0000                 | 0000 | 0000            | 0000                                      | uuuu                            | uuuu |  |  |  |  |  |

| RXFBCON2 <sup>(6)</sup>  | 2585 | 2680                                                   | 4585   | 4680                                  | 0001                 | 0001 | 0001            | 0001                                      | uuuu                            | uuuu |  |  |  |  |  |

| RXFBCON1 <sup>(6)</sup>  | 2585 | 2680                                                   | 4585   | 4680                                  | 0001                 | 0001 | 0001            | 0001                                      | uuuu                            | uuuu |  |  |  |  |  |

| RXFBCON0 <sup>(6)</sup>  | 2585 | 2680                                                   | 4585   | 4680                                  | 0000                 | 0000 | 0000            | 0000                                      | uuuu                            | uuuu |  |  |  |  |  |

| RXF15EIDL <sup>(6)</sup> | 2585 | 2680                                                   | 4585   | 4680                                  | xxxx                 | xxxx | uuuu            | uuuu                                      | uuuu                            | uuuu |  |  |  |  |  |

| RXF15EIDH(6)             | 2585 | 2680                                                   | 4585   | 4680                                  | xxxx                 | xxxx | uuuu            | uuuu                                      | uuuu                            | uuuu |  |  |  |  |  |

| RXF15SIDL <sup>(6)</sup> | 2585 | 2680                                                   | 4585   | 4680                                  | xxx-                 | x-xx | uuu-            | u-uu                                      | uuu-                            | u-uu |  |  |  |  |  |

| RXF15SIDH(6)             | 2585 | 2680                                                   | 4585   | 4680                                  | xxxx                 | xxxx | uuuu            | uuuu                                      | uuuu                            | uuuu |  |  |  |  |  |

| RXF14EIDL <sup>(6)</sup> | 2585 | 2680                                                   | 4585   | 4680                                  | xxxx                 | xxxx | uuuu            | uuuu                                      | uuuu                            | uuuu |  |  |  |  |  |

| RXF14EIDH <sup>(6)</sup> | 2585 | 2680                                                   | 4585   | 4680                                  | xxxx                 | xxxx | uuuu            | uuuu                                      | uuuu                            | uuuu |  |  |  |  |  |

| RXF14SIDL <sup>(6)</sup> | 2585 | 2680                                                   | 4585   | 4680                                  | xxx-                 | x-xx | uuu-            | u-uu                                      | uuu-                            | u-uu |  |  |  |  |  |

| RXF14SIDH(6)             | 2585 | 2680                                                   | 4585   | 4680                                  | xxxx                 | xxxx | uuuu            | uuuu                                      | uuuu                            | uuuu |  |  |  |  |  |

| RXF13EIDL <sup>(6)</sup> | 2585 | 2680                                                   | 4585   | 4680                                  | xxxx                 | xxxx | uuuu            | uuuu                                      | uuuu                            | uuuu |  |  |  |  |  |

| RXF13EIDH(6)             | 2585 | 2680                                                   | 4585   | 4680                                  | xxxx                 | xxxx | uuuu            | uuuu                                      | uuuu                            | uuuu |  |  |  |  |  |

| RXF13SIDL(6)             | 2585 | 2680                                                   | 4585   | 4680                                  | xxx-                 | x-xx | uuu-            | u-uu                                      | uuu-                            | u-uu |  |  |  |  |  |

| RXF13SIDH(6)             | 2585 | 2680                                                   | 4585   | 4680                                  | xxxx                 | xxxx | uuuu            | uuuu                                      | uuuu                            | uuuu |  |  |  |  |  |

| RXF12EIDL(6)             | 2585 | 2680                                                   | 4585   | 4680                                  | xxxx                 | xxxx | սսսս            | uuuu                                      | սսսս                            | uuuu |  |  |  |  |  |

| RXF12EIDH(6)             | 2585 | 2680                                                   | 4585   | 4680                                  | xxxx                 | xxxx | uuuu            | uuuu                                      | uuuu                            | uuuu |  |  |  |  |  |

| RXF12SIDL(6)             | 2585 | 2680                                                   | 4585   | 4680                                  | xxx-                 | x-xx | uuu-            | u-uu                                      | uuu-                            | u-uu |  |  |  |  |  |

|                          |      | ۱                                                      |        | · · · · · · · · · · · · · · · · · · · | t                    |      |                 |                                           |                                 |      |  |  |  |  |  |

### TABLE 4-4: INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED)

$\label{eq:logend: u = unchanged, x = unknown, - = unimplemented bit, read as `0', q = value depends on condition. Shaded cells indicate conditions do not apply for the designated device.}$

Note 1: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

- 2: When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

- **3:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

- 4: See Table 4-3 for Reset value for specific condition.

- **5:** Bits 6 and 7 of PORTA, LATA and TRISA are enabled, depending on the oscillator mode selected. When not enabled as PORTA pins, they are disabled and read '0'.

- 6: This register reads all '0's until the ECAN<sup>™</sup> technology is set up in Mode 1 or Mode 2.

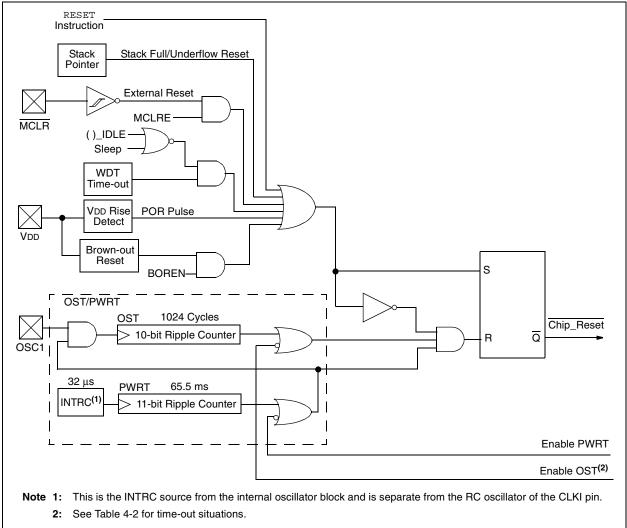

### FIGURE 5-6: USE OF THE BANK SELECT REGISTER (DIRECT ADDRESSING)

### 5.3.2 ACCESS BANK

While the use of the BSR with an embedded 8-bit address allows users to address the entire range of data memory, it also means that the user must always ensure that the correct bank is selected. Otherwise, data may be read from or written to the wrong location. This can be disastrous if a GPR is the intended target of an operation, but an SFR is written to instead. Verifying and/or changing the BSR for each read or write to data memory can become very inefficient.

To streamline access for the most commonly used data memory locations, the data memory is configured with an Access Bank, which allows users to access a mapped block of memory without specifying a BSR. The Access Bank consists of the first 128 bytes of memory (00h-7Fh) in Bank 0 and the last 128 bytes of memory (80h-FFh) in Block 15. The lower half is known as the "Access RAM" and is composed of GPRs. The upper half is also where the device's SFRs are mapped. These two areas are mapped contiguously in the Access Bank and can be addressed in a linear fashion by an 8-bit address (Figure 5-5).

The Access Bank is used by core PIC18 instructions that include the Access RAM bit (the 'a' parameter in the instruction). When 'a' is equal to '1', the instruction uses the BSR and the 8-bit address included in the opcode for the data memory address. When 'a' is '0'

however, the instruction is forced to use the Access Bank address map; the current value of the BSR is ignored entirely.

Using this "forced" addressing allows the instruction to operate on a data address in a single cycle, without updating the BSR first. For 8-bit addresses of 80h and above, this means that users can evaluate and operate on SFRs more efficiently. The Access RAM below 80h is a good place for data values that the user might need to access rapidly, such as immediate computational results or common program variables. Access RAM also allows for faster and more code efficient context saving and switching of variables.

The mapping of the Access Bank is slightly different when the extended instruction set is enabled (XINST Configuration bit = 1). This is discussed in more detail in Section 5.6.3 "Mapping the Access Bank in Indexed Literal Offset Mode".

### 5.3.3 GENERAL PURPOSE REGISTER FILE

PIC18 devices may have banked memory in the GPR area. This is data RAM, which is available for use by all instructions. GPRs start at the bottom of Bank 0 (address 000h) and grow upwards towards the bottom of the SFR area. GPRs are not initialized by a Power-on Reset and are unchanged on all other Resets.

| File Name | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | Value on POR, BOR | Details<br>on page: |

|-----------|---------|---------|---------|---------|---------|---------|---------|---------|-------------------|---------------------|

| TXB1SIDL  | SID2    | SID1    | SID0    | _       | EXIDE   | _       | EID17   | EID16   | xxx- x-xx         | 54, 283             |

| TXB1SIDH  | SID10   | SID9    | SID8    | SID7    | SID6    | SID5    | SID4    | SID3    | XXXX XXXX         | 54, 283             |

| TXB1CON   | TXBIF   | TXABT   | TXLARB  | TXERR   | TXREQ   | -       | TXPRI1  | TXPRI0  | 0000 0-00         | 54, 282             |

| TXB2D7    | TXB2D77 | TXB2D76 | TXB2D75 | TXB2D74 | TXB2D73 | TXB2D72 | TXB2D71 | TXB2D70 | XXXX XXXX         | 54, 284             |

| TXB2D6    | TXB2D67 | TXB2D66 | TXB2D65 | TXB2D64 | TXB2D63 | TXB2D62 | TXB2D61 | TXB2D60 | XXXX XXXX         | 54, 284             |

| TXB2D5    | TXB2D57 | TXB2D56 | TXB2D55 | TXB2D54 | TXB2D53 | TXB2D52 | TXB2D51 | TXB2D50 | XXXX XXXX         | 54, 284             |

| TXB2D4    | TXB2D47 | TXB2D46 | TXB2D45 | TXB2D44 | TXB2D43 | TXB2D42 | TXB2D41 | TXB2D40 | XXXX XXXX         | 54, 284             |

| TXB2D3    | TXB2D37 | TXB2D36 | TXB2D35 | TXB2D34 | TXB2D33 | TXB2D32 | TXB2D31 | TXB2D30 | xxxx xxxx         | 54, 284             |

| TXB2D2    | TXB2D27 | TXB2D26 | TXB2D25 | TXB2D24 | TXB2D23 | TXB2D22 | TXB2D21 | TXB2D20 | XXXX XXXX         | 54, 284             |

| TXB2D1    | TXB2D17 | TXB2D16 | TXB2D15 | TXB2D14 | TXB2D13 | TXB2D12 | TXB2D11 | TXB2D10 | XXXX XXXX         | 55, 284             |

| TXB2D0    | TXB2D07 | TXB2D06 | TXB2D05 | TXB2D04 | TXB2D03 | TXB2D02 | TXB2D01 | TXB2D00 | XXXX XXXX         | 55, 284             |

| TXB2DLC   | _       | TXRTR   | —       | —       | DLC3    | DLC2    | DLC1    | DLC0    | -x xxxx           | 55, 285             |

| TXB2EIDL  | EID7    | EID6    | EID5    | EID4    | EID3    | EID2    | EID1    | EID0    | xxxx xxxx         | 55, 284             |

| TXB2EIDH  | EID15   | EID14   | EID13   | EID12   | EID11   | EID10   | EID9    | EID8    | xxxx xxxx         | 55, 283             |

| TXB2SIDL  | SID2    | SID1    | SID0    | _       | EXIDE   | _       | EID17   | EID16   | xxxx x-xx         | 55, 283             |

| TXB2SIDH  | SID10   | SID9    | SID8    | SID7    | SID6    | SID5    | SID4    | SID3    | xxx- x-xx         | 55, 283             |

| TXB2CON   | TXBIF   | TXABT   | TXLARB  | TXERR   | TXREQ   | _       | TXPRI1  | TXPRI0  | 0000 0-00         | 55, 282             |

| RXM1EIDL  | EID7    | EID6    | EID5    | EID4    | EID3    | EID2    | EID1    | EID0    | xxxx xxxx         | 55, 304             |

| RXM1EIDH  | EID15   | EID14   | EID13   | EID12   | EID11   | EID10   | EID9    | EID8    | xxxx xxxx         | 55, 304             |

| RXM1SIDL  | SID2    | SID1    | SID0    | _       | EXIDEN  | _       | EID17   | EID16   | xxx- x-xx         | 55, 304             |

| RXM1SIDH  | SID10   | SID9    | SID8    | SID7    | SID6    | SID5    | SID4    | SID3    | xxxx xxxx         | 55, 304             |

| RXM0EIDL  | EID7    | EID6    | EID5    | EID4    | EID3    | EID2    | EID1    | EID0    | xxxx xxxx         | 55, 304             |

| RXM0EIDH  | EID15   | EID14   | EID13   | EID12   | EID11   | EID10   | EID9    | EID8    | xxxx xxxx         | 55, 304             |

| RXM0SIDL  | SID2    | SID1    | SID0    | _       | EXIDEN  | _       | EID17   | EID16   | xxx- x-xx         | 55, 304             |

| RXM0SIDH  | SID10   | SID9    | SID8    | SID7    | SID6    | SID5    | SID4    | SID3    | xxxx xxxx         | 55, 303             |

| RXF5EIDL  | EID7    | EID6    | EID5    | EID4    | EID3    | EID2    | EID1    | EID0    | xxxx xxxx         | 55, 303             |

| RXF5EIDH  | EID15   | EID14   | EID13   | EID12   | EID11   | EID10   | EID9    | EID8    | xxxx xxxx         | 55, 303             |

| RXF5SIDL  | SID2    | SID1    | SID0    | _       | EXIDEN  | _       | EID17   | EID16   | xxx- x-xx         | 55, 302             |

| RXF5SIDH  | SID10   | SID9    | SID8    | SID7    | SID6    | SID5    | SID4    | SID3    | xxxx xxxx         | 55, 302             |

| RXF4EIDL  | EID7    | EID6    | EID5    | EID4    | EID3    | EID2    | EID1    | EID0    | xxxx xxxx         | 55, 303             |

| RXF4EIDH  | EID15   | EID14   | EID13   | EID12   | EID11   | EID10   | EID9    | EID8    | xxxx xxxx         | 55, 303             |

| RXF4SIDL  | SID2    | SID1    | SID0    | —       | EXIDEN  | —       | EID17   | EID16   | xxx- x-xx         | 55, 302             |

| RXF4SIDH  | SID10   | SID9    | SID8    | SID7    | SID6    | SID5    | SID4    | SID3    | xxxx xxxx         | 55, 302             |

| RXF3EIDL  | EID7    | EID6    | EID5    | EID4    | EID3    | EID2    | EID1    | EID0    | xxxx xxxx         | 55, 303             |

| RXF3EIDH  | EID15   | EID14   | EID13   | EID12   | EID11   | EID10   | EID9    | EID8    | xxxx xxxx         | 55, 303             |

| RXF3SIDL  | SID2    | SID1    | SID0    | —       | EXIDEN  | _       | EID17   | EID16   | xxx- x-xx         | 55, 302             |

| RXF3SIDH  | SID10   | SID9    | SID8    | SID7    | SID6    | SID5    | SID4    | SID3    | xxxx xxxx         | 55, 302             |

| RXF2EIDL  | EID7    | EID6    | EID5    | EID4    | EID3    | EID2    | EID1    | EID0    | xxxx xxxx         | 55, 303             |

| RXF2EIDH  | EID15   | EID14   | EID13   | EID12   | EID11   | EID10   | EID9    | EID8    | xxxx xxxx         | 55, 303             |

| RXF2SIDL  | SID2    | SID1    | SID0    | —       | EXIDEN  | —       | EID17   | EID16   | xxx- x-xx         | 55, 302             |

| RXF2SIDH  | SID10   | SID9    | SID8    | SID7    | SID6    | SID5    | SID4    | SID3    | xxxx xxxx         | 55, 302             |

| TABLE 5-2: REGISTER FILE SUMMARY (PIC18F2585/2680/4585/4680) (CONTINUED | TABLE 5-2: | REGISTER FILE SUMMARY | (PIC18F2585/2680/4585/4680) | (CONTINUED) |

|-------------------------------------------------------------------------|------------|-----------------------|-----------------------------|-------------|

|-------------------------------------------------------------------------|------------|-----------------------|-----------------------------|-------------|

**Legend:** x = unknown, u = unchanged, - = unimplemented, q = value depends on condition **Note 1:** Bit 21 of the PC is only available in Test mode and Serial Programming modes.

2: The SBOREN bit is only available when CONFIG2L<1:0> = 01; otherwise, it is disabled and reads as '0'. See Section 4.4 "Brown-out Reset (BOR)".

3: These registers and/or bits are not implemented on PIC18F2X8X devices and are read as '0'. Reset values are shown for PIC18F4X8X devices; individual unimplemented bits should be interpreted as '---'.

4: The PLLEN bit is only available in specific oscillator configuration; otherwise, it is disabled and reads as '0'. See Section 2.6.4 "PLL in INTOSC Modes".

5: The RE3 bit is only available when Master Clear Reset is disabled (CONFIG3H<7> = 0); otherwise, RE3 reads as '0'. This bit is read-only.

**6:** RA6/RA7 and their associated latch and direction bits are individually configured as port pins based on various primary oscillator modes. When disabled, these bits read as '0'.

7: CAN bits have multiple functions depending on the selected mode of the CAN module.

8: This register reads all '0's until the ECAN<sup>™</sup> technology is set up in Mode 1 or Mode 2.

9: These registers are available on PIC18F4X8X devices only.

NOTES:

### 9.6 INTn Pin Interrupts

External interrupts on the RB0/INT0, RB1/INT1 and RB2/INT2 pins are edge-triggered. If the corresponding INTEDGx bit in the INTCON2 register is set (= 1), the interrupt is triggered by a rising edge; if the bit is clear, the trigger is on the falling edge. When a valid edge appears on the RBx/INTx pin, the corresponding flag bit INTxF is set. This interrupt can be disabled by clearing the corresponding enable bit INTxE. Flag bit INTxF must be cleared in software in the Interrupt.

All external interrupts (INT0, INT1 and INT2) can wake-up the processor from the power managed modes, if bit INTxE was set prior to going into power managed modes. If the Global Interrupt Enable bit, GIE, is set, the processor will branch to the interrupt vector following wake-up.

Interrupt priority for INT1 and INT2 is determined by the value contained in the interrupt priority bits, INT1IP (INTCON3<6>) and INT2IP (INTCON3<7>). There is no priority bit associated with INT0. It is always a high priority interrupt source.

### 9.7 TMR0 Interrupt

In 8-bit mode (which is the default), an overflow in the TMR0 register (FFh  $\rightarrow$  00h) will set flag bit TMR0IF. In 16-bit mode, an overflow in the TMR0H:TMR0L register pair (FFFFh  $\rightarrow$  0000h) will set TMR0IF. The interrupt can be enabled/disabled by setting/clearing enable bit TMR0IE (INTCON<5>). Interrupt priority for Timer0 is determined by the value contained in the interrupt priority bit, TMR0IP (INTCON2<2>). See Section 11.0 "Timer0 Module" for further details on the Timer0 module.

### 9.8 PORTB Interrupt-on-Change

An input change on PORTB<7:4> sets flag bit, RBIF (INTCON<0>). The interrupt can be enabled/disabled by setting/clearing enable bit, RBIE (INTCON<3>). Interrupt priority for PORTB interrupt-on-change is determined by the value contained in the interrupt priority bit, RBIP (INTCON2<0>).

### 9.9 Context Saving During Interrupts

During interrupts, the return PC address is saved on the stack. Additionally, the WREG, STATUS and BSR registers are saved on the fast return stack. If a fast return from interrupt is not used (See **Section 5.3 "Data Memory Organization**"), the user may need to save the WREG, STATUS and BSR registers on entry to the Interrupt Service Routine. Depending on the user's application, other registers may also need to be saved. Example 9-1 saves and restores the WREG, STATUS and BSR registers during an Interrupt Service Routine.

| MOVWF  | W_TEMP              | ; W_TEMP is in virtual bank    |

|--------|---------------------|--------------------------------|

| MOVFF  | STATUS, STATUS_TEMP | ; STATUS_TEMP located anywhere |

| MOVFF  | BSR, BSR_TEMP       | ; BSR_TMEP located anywhere    |

| ;      |                     |                                |

| ; USER | ISR CODE            |                                |

| ;      |                     |                                |

| MOVFF  | BSR_TEMP, BSR       | ; Restore BSR                  |

| MOVF   | W_TEMP, W           | ; Restore WREG                 |

| MOVFF  | STATUS TEMP, STATUS | ; Restore STATUS               |

EXAMPLE 9-1: SAVING STATUS, WREG AND BSR REGISTERS IN RAM

| Pin Name         | Function | I/O | TRIS | Buffer | Description                                                                                                     |

|------------------|----------|-----|------|--------|-----------------------------------------------------------------------------------------------------------------|

| RE0/RD/AN5       | RE0      | OUT | 0    | DIG    | LATE<0> data output.                                                                                            |

|                  |          | IN  | 1    | ST     | PORTE<0> data input.                                                                                            |

|                  | RD       | IN  | 1    | TTL    | PSP read enable input.                                                                                          |

|                  | AN5      | IN  | 1    | ANA    | A/D input channel 5. Enabled on POR, this analog input overrides the digital input (read as clear – low level). |

| RE1/WR/AN6/C1OUT | RE1      | OUT | 0    | DIG    | LATE<1> data output.                                                                                            |

|                  |          | IN  | 1    | ST     | PORTE<1> data input.                                                                                            |

|                  | WR       | IN  | 1    | TTL    | PSP write enable input.                                                                                         |

|                  | AN6      | IN  | 1    | ANA    | A/D input channel 6. Enabled on POR, this analog input overrides the digital input (read as clear – low level). |

|                  | C1OUT    | OUT | 0    | DIG    | Comparator 1 output.                                                                                            |

| RE2/CS/AN7/C2OUT | RE2      | OUT | 0    | DIG    | LATE<2> data output.                                                                                            |

|                  |          | IN  | 1    | ST     | PORTE<2> data input.                                                                                            |

|                  | CS       | IN  | 1    | TTL    | PSP chip select input.                                                                                          |

|                  | AN7      | IN  | 1    | ANA    | A/D input channel 7. Enabled on POR, this analog input overrides the digital input (read as clear – low level). |

|                  | C2OUT    | OUT | 0    | DIG    | Comparator 2 output.                                                                                            |

| MCLR/VPP/RE3     | MCLR     | IN  | x    | ST     | External Reset input. Disabled when MCLRE Configuration bit is '1'.                                             |

|                  | VPP      | IN  | x    | ANA    | High-voltage detection; used by ICSP™ operation.                                                                |

|                  | RE3      | IN  | 1    | ST     | PORTE<3> data input. Disabled when MCLRE Configuration bit is '0'.                                              |

### TABLE 10-9: PORTE I/O SUMMARY

Legend: PWR = Power Supply; OUT = Output; IN = Input; ANA = Analog Signal; DIG = Digital Output; ST = Schmitt Buffer Input; TTL = TTL Buffer Input

| Name                 | Bit 7 | Bit 6 | Bit 5 Bit 4 |         | Bit 3                | Bit 2               | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

|----------------------|-------|-------|-------------|---------|----------------------|---------------------|--------|--------|----------------------------|

| PORTE <sup>(3)</sup> | _     | _     |             |         | RE3 <sup>(1,2)</sup> | RE2                 | RE1    | RE0    | 52                         |

| LATE <sup>(2)</sup>  | —     | —     | —           | —       | _                    | LATE Data Output Re |        | ister  | 52                         |

| TRISE <sup>(3)</sup> | IBF   | OBF   | IBOV        | PSPMODE |                      | TRISE2              | TRISE1 | TRISE0 | 52                         |

| ADCON1               | _     | _     | VCFG1       | VCFG0   | PCFG3                | PCFG2               | PCFG1  | PCFG0  | 50                         |

| CMCON <sup>(3)</sup> | C2OUT | C10UT | C2INV       | C1INV   | CIS                  | CM2                 | CM1    | CM0    | 51                         |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by PORTE.

**Note 1:** Implemented only when Master Clear functionality is disabled (MCLRE Configuration bit = 0).

2: RE3 is the only PORTE bit implemented on both PIC18F2X8X and PIC18F4X8X devices. All other bits are implemented only when PORTE is implemented (i.e., PIC18F4X8X devices).

3: These registers are unimplemented on PIC18F2X8X devices.

### 15.4 PWM Mode

In Pulse-Width Modulation (PWM) mode, the CCP1 pin produces up to a 10-bit resolution PWM output. Since the CCP1 pin is multiplexed with a PORTB or PORTC data latch, the appropriate TRIS bit must be cleared to make the CCP1 pin an output.

| Note: | Clearing the CCP1CON register will force |

|-------|------------------------------------------|

|       | the RC2 output latch (depending on       |

|       | device configuration) to the default low |

|       | level. This is not the PORTC I/O data    |

|       | latch.                                   |

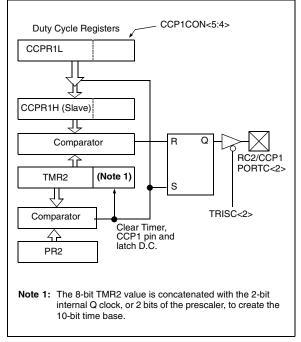

Figure 15-3 shows a simplified block diagram of the CCP1 module in PWM mode.

For a step-by-step procedure on how to set up the CCP1 module for PWM operation, see Section 15.4.4 "Setup for PWM Operation".

### FIGURE 15-3: SIMPLIFIED PWM BLOCK DIAGRAM

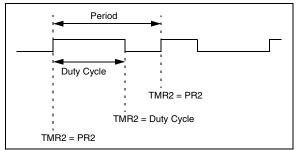

A PWM output (Figure 15-4) has a time base (period) and a time that the output stays high (duty cycle). The frequency of the PWM is the inverse of the period (1/period).

### FIGURE 15-4: PWM OUTPUT

### 15.4.1 PWM PERIOD

The PWM period is specified by writing to the PR2 (PR4) register. The PWM period can be calculated using the following formula.

### EQUATION 15-1:

$PWM Period = (PR2) + 1] \bullet 4 \bullet TOSC \bullet$ (TMR2 Prescale Value)

PWM frequency is defined as 1/[PWM period].

When TMR1 (TMR3) is equal to PR2 (PR2), the following three events occur on the next increment cycle:

- TMR2 is cleared

- The CCP1 pin is set (exception: if PWM duty cycle = 0%, the CCP1 pin will not be set)

- The PWM duty cycle is latched from ECCPR1L into ECCPR1H

### 15.4.2 PWM DUTY CYCLE

The PWM duty cycle is specified by writing to the ECCPR1L register and to the CCP1CON<5:4> bits. Up to 10-bit resolution is available. The ECCPR1L contains the eight MSbs and the CCP1CON<5:4> contains the two LSbs. This 10-bit value is represented by ECCPR1L:ECCP1CON<5:4>. The following equation is used to calculate the PWM duty cycle in time.

### **EQUATION 15-2:**

PWM Duty Cycle = (ECCPR1L:ECCP1CON<5:4>) • Tosc • (TMR2 Prescale Value)

ECCPR1L and ECCP1CON<5:4> can be written to at any time, but the duty cycle value is not latched into ECCPR1H until after a match between PR2 and TMR2 occurs (i.e., the period is complete). In PWM mode, ECCPR1H is a read-only register.

### 16.0 ENHANCED CAPTURE/COMPARE/PWM (ECCP1) MODULE

Note: The ECCP1 module is implemented only in PIC18F4X8X (40/44-pin) devices.

In PIC18F4585/4680 devices, ECCP1 is implemented as a standard CCP1 module with Enhanced PWM capabilities. These include the provision for 2 or 4 output channels, user selectable polarity, dead-band control and automatic shutdown and restart. The enhanced features are discussed in detail in **Section 16.4** "Enhanced PWM Mode". Capture, Compare and single output PWM functions of the ECCP1 module are the same as described for the standard CCP1 module.

The control register for the Enhanced CCP1 module is shown in Register 16-1. It differs from the CCP1CON register in the PIC18F2585/2680 devices in that the two Most Significant bits are implemented to control PWM functionality.

### REGISTER 16-1: ECCP1CON REGISTER (ECCP1 MODULE, PIC18F4585/4680 DEVICES)

| R/W-0   | R/W-0   | R/W-0  | R/W-0  | R/W-0   | R/W-0   | R/W-0   | R/W-0   |

|---------|---------|--------|--------|---------|---------|---------|---------|

| EPWM1M1 | EPWM1M0 | EDC1B1 | EDC1B0 | ECCP1M3 | ECCP1M2 | ECCP1M1 | ECCP1M0 |

| bit 7   | •       |        |        | •       |         |         | bit 0   |

bit 7-6 EPWM1M1:EPWM1M0: Enhanced PWM Output Configuration bits

If ECCP1M3:ECCP1M2 = 00, 01, 10:

xx = P1A assigned as Capture/Compare input/output; P1B, P1C, P1D assigned as port pins If ECCP1M3:ECCP1M2 = 11:

- 00 = Single output: P1A modulated; P1B, P1C, P1D assigned as port pins

- 01 = Full-bridge output forward: P1D modulated; P1A active; P1B, P1C inactive

- 10 = Half-bridge output: P1A, P1B modulated with dead-band control; P1C, P1D assigned as port pins

- 11 = Full-bridge output reverse: P1B modulated; P1C active; P1A, P1D inactive

- bit 5-4 EDC1B1:EDC1B0: PWM Duty Cycle bit 1 and bit 0

Capture mode:

Unused.

Compare mode:

Unused.

PWM mode:

These bits are the two LSbs of the 10-bit PWM duty cycle. The eight MSbs of the duty cycle are found in CCPR1L/ECCPR1L.

### bit 3-0 ECCP1M3:ECCP1M0: Enhanced CCP1 Mode Select bits

- 0000 = Capture/Compare/PWM off (resets ECCP1 module)

- 0001 = Reserved

- 0010 = Compare mode, toggle output on match

- OO11 = Reserved

- 0100 = Capture mode, every falling edge

- 0101 = Capture mode, every rising edge

- 0110 = Capture mode, every 4th rising edge

- 0111 = Capture mode, every 16th rising edge

- 1000 = Compare mode, initialize ECCP1 pin low, set output on compare match (set ECCP1IF)

- 1001 = Compare mode, initialize ECCP1 pin high, clear output on compare match (set ECCP1IF)

- 1010 = Compare mode, generate software interrupt only, ECCP1 pin reverts to I/O state

- 1011 = Compare mode, trigger special event (ECCP1 resets TMR1 or TMR3, sets ECCP1IF bit and starts the A/D conversion on ECCP1 match)

- 1100 = PWM mode; P1A, P1C active-high; P1B, P1D active-high

- 1101 = PWM mode; P1A, P1C active-high; P1B, P1D active-low

- 1110 = PWM mode; P1A, P1C active-low; P1B, P1D active-high

- 1111 = PWM mode; P1A, P1C active-low; P1B, P1D active-low

# Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

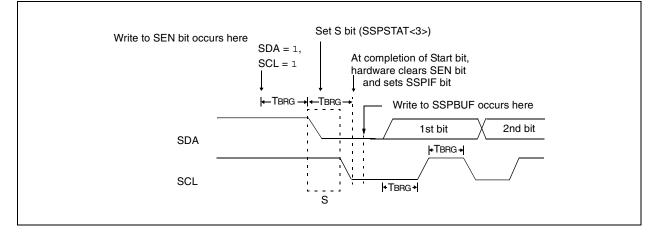

### 17.4.8 I<sup>2</sup>C MASTER MODE START CONDITION TIMING

To initiate a Start condition, the user sets the Start Enable bit, SEN (SSPCON2<0>). If the SDA and SCL pins are sampled high, the Baud Rate Generator is reloaded with the contents of SSPADD<6:0> and starts its count. If SCL and SDA are both sampled high when the Baud Rate Generator times out (TBRG), the SDA pin is driven low. The action of the SDA being driven low while SCL is high is the Start condition and causes the S bit (SSPSTAT<3>) to be set. Following this, the Baud Rate Generator is reloaded with the contents of SSPADD<6:0> and resumes its count. When the Baud Rate Generator times out (TBRG), the SEN bit (SSPCON2<0>) will be automatically cleared by hardware, the Baud Rate Generator is suspended, leaving the SDA line held low and the Start condition is complete.

Note: If at the beginning of the Start condition, the SDA and SCL pins are already sampled low, or if during the Start condition, the SCL line is sampled low before the SDA line is driven low, a bus collision occurs, the Bus Collision Interrupt Flag, BCLIF, is set, the Start condition is aborted and the l<sup>2</sup>C module is reset into its Idle state.

### 17.4.8.1 WCOL Status Flag

If the user writes the SSPBUF when a Start sequence is in progress, the WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

Note: Because queueing of events is not allowed, writing to the lower 5 bits of SSPCON2 is disabled until the Start condition is complete.

### FIGURE 17-19: FIRST START BIT TIMING

## PIC18F2585/2680/4585/4680

| ER 18-3: | BAUDCON: BAUD RATE CONTROL REGISTER                                                                                                                           |                              |                              |                         |                         |             |               |              |  |  |  |  |  |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|------------------------------|-------------------------|-------------------------|-------------|---------------|--------------|--|--|--|--|--|

|          | R/W-0                                                                                                                                                         | R-1                          | U-0                          | R/W-0                   | R/W-0                   | U-0         | R/W-0         | R/W-0        |  |  |  |  |  |

|          | ABDOVF                                                                                                                                                        | RCIDL                        |                              | SCKP                    | BRG16                   | _           | WUE           | ABDEN        |  |  |  |  |  |

|          | bit 7                                                                                                                                                         |                              |                              |                         |                         |             |               | bit 0        |  |  |  |  |  |

| bit 7    | ABDOVF: Auto-Baud Acquisition Rollover Status bit                                                                                                             |                              |                              |                         |                         |             |               |              |  |  |  |  |  |

|          | (must l                                                                                                                                                       | be cleared i                 |                              | C C                     | Baud Rate D             | etect mode  |               |              |  |  |  |  |  |

| bit 6    | RCIDL: Re                                                                                                                                                     | ceive Opera                  | ation Idle Sta               | atus bit                |                         |             |               |              |  |  |  |  |  |

|          |                                                                                                                                                               | ve operation<br>ve operation |                              |                         |                         |             |               |              |  |  |  |  |  |

| bit 5    | Unimplem                                                                                                                                                      | ented: Rea                   | <b>d as</b> '0'              |                         |                         |             |               |              |  |  |  |  |  |

| bit 4    | Unimplemented: Read as '0'<br>SCKP: Synchronous Clock Polarity Select bit                                                                                     |                              |                              |                         |                         |             |               |              |  |  |  |  |  |

|          | Asynchronous mode:<br>Unused in this mode.                                                                                                                    |                              |                              |                         |                         |             |               |              |  |  |  |  |  |

|          |                                                                                                                                                               | ate for clock                | (CK) is a hi<br>(CK) is a lo |                         |                         |             |               |              |  |  |  |  |  |

| bit 3    | <b>BRG16:</b> 16                                                                                                                                              | bit Baud R                   | ate Register                 | <sup>r</sup> Enable bit |                         |             |               |              |  |  |  |  |  |

|          |                                                                                                                                                               |                              | Generator –<br>enerator – S  |                         | nd SPBRG<br>(Compatible | e mode), SP | BRGH valu     | e ignored    |  |  |  |  |  |

| bit 2    | Unimplem                                                                                                                                                      | ented: Rea                   | <b>d as</b> '0'              |                         |                         |             |               |              |  |  |  |  |  |

| bit 1    | WUE: Wake-up Enable bit                                                                                                                                       |                              |                              |                         |                         |             |               |              |  |  |  |  |  |

|          | Asynchronous mode:                                                                                                                                            |                              |                              |                         |                         |             |               |              |  |  |  |  |  |

|          | cleared                                                                                                                                                       | d in hardwa                  | re on followi                | ng rising ed            |                         | upt generat | ted on fallir | ig edge; bit |  |  |  |  |  |

|          | <ul> <li>0 = RX pin not monitored or rising edge detected</li> <li>Synchronous mode:</li> </ul>                                                               |                              |                              |                         |                         |             |               |              |  |  |  |  |  |

|          | Unused in t                                                                                                                                                   |                              |                              |                         |                         |             |               |              |  |  |  |  |  |

| bit 0    | ABDEN: A                                                                                                                                                      | uto-Baud De                  | etect Enable                 | bit                     |                         |             |               |              |  |  |  |  |  |

|          | Asynchronous mode:                                                                                                                                            |                              |                              |                         |                         |             |               |              |  |  |  |  |  |

|          | <ul> <li>1 = Enable baud rate measurement on the next character. Requires reception of a Sync field<br/>(55h); cleared in hardware upon completion</li> </ul> |                              |                              |                         |                         |             |               |              |  |  |  |  |  |

|          |                                                                                                                                                               |                              | ement disab                  | led or comp             | leted                   |             |               |              |  |  |  |  |  |

|          | <u>Synchrono</u><br>Unused in t                                                                                                                               |                              |                              |                         |                         |             |               |              |  |  |  |  |  |

|          | Unused III I                                                                                                                                                  |                              |                              |                         |                         |             |               |              |  |  |  |  |  |

|          |                                                                                                                                                               |                              |                              |                         |                         |             |               |              |  |  |  |  |  |

### REGISTER 18-3: BAUDCON: BAUD RATE CONTROL REGISTER

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

### 22.0 HIGH/LOW-VOLTAGE DETECT (HLVD)

PIC18F2585/2680/4585/4680 devices have a High/Low-Voltage Detect module (HLVD). This is a programmable circuit that allows the user to specify both a device voltage trip point and the direction of change from that point. If the device experiences an excursion past the trip point in that direction, an interrupt flag is set. If the interrupt is enabled, the program execution will branch to the interrupt vector address and the software can then respond to the interrupt.

The High/Low-Voltage Detect Control register (Register 22-1) completely controls the operation of the HLVD module. This allows the circuitry to be "turned off" by the user under software control, which minimizes the current consumption for the device.

The block diagram for the HLVD module is shown in Figure 22-1.

### REGISTER 22-1: HLVDCON: HIGH/LOW-VOLTAGE DETECT CONTROL REGISTER

|         | R/W-0                               | U-0                       | R-0           | R/W-0           | R/W-0                 | R/W-1          | R/W-0                 | R/W-1                 |

|---------|-------------------------------------|---------------------------|---------------|-----------------|-----------------------|----------------|-----------------------|-----------------------|

|         | VDIRMAG                             | _                         | IRVST         | HLVDEN          | HLVDL3 <sup>(1)</sup> | HLVDL2(1)      | HLVDL1 <sup>(1)</sup> | HLVDL0 <sup>(1)</sup> |

|         | bit 7                               |                           |               |                 |                       |                |                       | bit 0                 |

|         |                                     |                           |               |                 |                       |                |                       |                       |

| bit 7   | VDIRMAG:                            | Voltage Dir               | ection Mag    | nitude Seleo    | ct bit                |                |                       |                       |

|         |                                     |                           |               |                 | eeds trip poir        |                |                       |                       |

| 1 0     |                                     |                           | •             | juais or fails  | below trip p          | oint (HLVDL    | 3:HLVDL0)             |                       |

| bit 6   | Unimpleme                           |                           |               |                 |                       |                |                       |                       |

| bit 5   | IRVST: Inte                         |                           | •             | -               |                       |                |                       | <b>.</b>              |

|         | 1 = Indicate                        | es that the v             | oltage dete   | ct logic will g | generate the i        | interrupt flag | at the speci          | fied voltage          |

|         | 0                                   | es that the               | voltage det   | ect logic wil   | I not generat         | te the interre | upt flag at th        | e specified           |

|         | voltage                             | range and                 | the HLVD in   | nterrupt sho    | ould not be er        | nabled         |                       |                       |

| bit 4   | HLVDEN: H                           | ligh/Low-Vo               | ltage Detec   | t Power En      | able bit              |                |                       |                       |

|         | 1 = HLVD 6                          |                           |               |                 |                       |                |                       |                       |

|         | 0 = HLVD c                          |                           | _             |                 | (1)                   |                |                       |                       |

| bit 3-0 | HLVDL3:HI                           |                           |               |                 |                       |                |                       |                       |

|         | 1111 = Extended 1110 = 4.48         |                           | g input is us | ed (input co    | omes from the         | e HLVDIN p     | in)                   |                       |

|         | 1110 = 4.40<br>1101 = 4.20          |                           |               |                 |                       |                |                       |                       |

|         | 1100 = 4.0                          | 1V-4.20V                  |               |                 |                       |                |                       |                       |

|         | 1011 = 3.8                          |                           |               |                 |                       |                |                       |                       |

|         | 1010 = 3.63                         |                           |               |                 |                       |                |                       |                       |

|         | 1001 = 3.40<br>$1000 = 3.3^{\circ}$ |                           |               |                 |                       |                |                       |                       |

|         | 0111 = 3.0                          |                           |               |                 |                       |                |                       |                       |

|         | 0110 = 2.82                         |                           |               |                 |                       |                |                       |                       |

|         | 0101 = 2.72<br>0100 = 2.54          |                           |               |                 |                       |                |                       |                       |

|         | 0100 = 2.32<br>0011 = 2.38          |                           |               |                 |                       |                |                       |                       |

|         | 0010 = 2.3                          |                           |               |                 |                       |                |                       |                       |

|         | 0001 = 2.18                         |                           |               |                 |                       |                |                       |                       |

|         | 0000 = 2.12                         |                           |               |                 |                       |                |                       |                       |

|         |                                     | HLVDL3:HL<br>of the devic |               |                 | lt in a trip poi      | nt below the   | e valid opera         | ting voltage          |

|         |                                     |                           |               |                 |                       |                |                       |                       |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

### REGISTER 23-26: BnSIDL: TX/RX BUFFER n STANDARD IDENTIFIER REGISTERS, LOW BYTE IN RECEIVE MODE $[0 \le n \le 5, TXnEN (BSEL0 < n >) = 0]^{(1)}$

|         |                                                     |               |                 | - [• •         | ·, ····        |             | / = •]      |       |  |  |

|---------|-----------------------------------------------------|---------------|-----------------|----------------|----------------|-------------|-------------|-------|--|--|

|         | R-x                                                 | R-x           | R-x             | R-x            | R-x            | U-0         | R-x         | R-x   |  |  |

|         | SID2                                                | SID1          | SID0            | SRR            | EXID           | _           | EID17       | EID16 |  |  |

|         | bit 7                                               |               |                 |                |                |             |             | bit 0 |  |  |

|         |                                                     |               |                 |                |                |             |             |       |  |  |

| bit 7-5 | SID2:SID0                                           | : Standard le | dentifier bits  | (if $EXID = 0$ | )              |             |             |       |  |  |

|         | Extended Identifier bits EID20:EID18 (if EXID = 1). |               |                 |                |                |             |             |       |  |  |

| bit 4   | SRR: Subs                                           | titute Remo   | te Transmis     | sion Reques    | st bit (only w | hen EXID =  | 1)          |       |  |  |

|         | 1 = Remote                                          | e transmissi  | on request o    | occurred       |                |             |             |       |  |  |

|         | 0 = No rem                                          | ote transmi   | ssion reques    | st occurred    |                |             |             |       |  |  |

| bit 3   | EXID: Exte                                          | nded Identif  | ier Enable b    | bit            |                |             |             |       |  |  |

|         |                                                     | 0             |                 | ded identifie  | ``             | 10:SID0 are | e EID28:EID | 18)   |  |  |

|         | 0 = Receiv                                          | ed message    | e is a standa   | rd identifier  | frame          |             |             |       |  |  |

| bit 2   | Unimplem                                            | ented: Read   | <b>d as</b> '0' |                |                |             |             |       |  |  |

| bit 1-0 | EID17:EID                                           | 16: Extende   | d Identifier k  | oits           |                |             |             |       |  |  |

|         | Note 1:                                             | These regis   | sters are ava   | ailable in Mo  | de 1 and 2 d   | only.       |             |       |  |  |

|         |                                                     |               |                 |                |                |             |             |       |  |  |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

### REGISTER 23-27: BnSIDL: TX/RX BUFFER n STANDARD IDENTIFIER REGISTERS, LOW BYTE IN TRANSMIT MODE $[0 \le n \le 5, TXnEN (BSEL0<n>) = 1]^{(1)}$

|         |                                                             |             |                 | -                              | •     | •            | <i>,</i> -  |       |  |  |

|---------|-------------------------------------------------------------|-------------|-----------------|--------------------------------|-------|--------------|-------------|-------|--|--|

|         | R/W-x                                                       | R/W-x       | R/W-x           | U-0                            | R/W-x | U-0          | R/W-x       | R/W-x |  |  |

|         | SID2                                                        | SID1        | SID0            | —                              | EXIDE | —            | EID17       | EID16 |  |  |

|         | bit 7                                                       |             |                 |                                |       |              |             | bit 0 |  |  |

| bit 7-5 |                                                             |             |                 | (if EXIDE =<br>18 (if EXIDE    | •     |              |             |       |  |  |

| bit 4   | Unimplemented: Read as '0'                                  |             |                 |                                |       |              |             |       |  |  |

| bit 3   | EXIDE: Ext                                                  | ended Iden  | tifier Enable   | bit                            |       |              |             |       |  |  |

|         |                                                             | •           |                 | ded identifie<br>rd identifier | •     | D10:SID0 are | e EID28:EID | 18)   |  |  |

| bit 2   | Unimpleme                                                   | ented: Read | <b>d as</b> '0' |                                |       |              |             |       |  |  |

| bit 1-0 | EID17:EID1                                                  | 16: Extende | d Identifier l  | oits                           |       |              |             |       |  |  |

|         | Note 1: These registers are available in Mode 1 and 2 only. |             |                 |                                |       |              |             |       |  |  |

|         | Legend:                                                     |             |                 |                                |       |              |             |       |  |  |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

© 2007 Microchip Technology Inc.

### **REGISTER 23-31:** BnEIDL: TX/RX BUFFER n EXTENDED IDENTIFIER REGISTERS, LOW BYTE IN TRANSMIT MODE $[0 \le n \le 5, TXnEN (BSEL<n>) = 1]^{(1)}$

| R/W-x |

|-------|-------|-------|-------|-------|-------|-------|-------|

| EID7  | EID6  | EID5  | EID4  | EID3  | EID2  | EID1  | EID0  |

| bit 7 |       |       |       |       |       |       | bit 0 |

bit 7-0

EID7:EID0: Extended Identifier bits

Note 1: These registers are available in Mode 1 and 2 only.

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

## REGISTER 23-32: BnDm: TX/RX BUFFER n DATA FIELD BYTE m REGISTERS IN RECEIVE MODE $[0 \le n \le 5, 0 \le m \le 7, TXnEN (BSEL<n>) = 0]^{(1)}$

| R-x   |

|-------|-------|-------|-------|-------|-------|-------|-------|

| BnDm7 | BnDm6 | BnDm5 | BnDm4 | BnDm3 | BnDm2 | BnDm1 | BnDm0 |

| bit 7 |       |       |       |       |       |       | bit 0 |

bit 7-0 **BnDm7:BnDm0:** Receive Buffer n Data Field Byte m bits (where  $0 \le n < 3$  and 0 < m < 8) Each receive buffer has an array of registers. For example, Receive Buffer 0 has 7 registers: B0D0 to B0D7.

Note 1: These registers are available in Mode 1 and 2 only.

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | l bit, read as '0' |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

## REGISTER 23-33: BnDm: TX/RX BUFFER n DATA FIELD BYTE m REGISTERS IN TRANSMIT MODE $[0 \le n \le 5, 0 \le m \le 7, TXnEN (BSEL<n>) = 1]^{(1)}$

| R/W-x |

|-------|-------|-------|-------|-------|-------|-------|-------|

| BnDm7 | BnDm6 | BnDm5 | BnDm4 | BnDm3 | BnDm2 | BnDm1 | BnDm0 |

| bit 7 |       |       |       |       |       |       | bit 0 |

bit 7-0 **BnDm7:BnDm0:** Transmit Buffer n Data Field Byte m bits (where  $0 \le n < 3$  and 0 < m < 8) Each transmit buffer has an array of registers. For example, Transmit Buffer 0 has 7 registers: TXB0D0 to TXB0D7.

**Note 1:** These registers are available in Mode 1 and 2 only.

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

| 20 04.  | Diracon                                             | IO. DAOD                                                                                                              |                   |             |            |                        |                        |                        |  |  |  |  |

|---------|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|-------------------|-------------|------------|------------------------|------------------------|------------------------|--|--|--|--|

|         | R/W-0                                               | R/W-0                                                                                                                 | U-0               | U-0         | U-0        | R/W-0                  | R/W-0                  | R/W-0                  |  |  |  |  |

|         | WAKDIS                                              | WAKFIL                                                                                                                | —                 | —           | —          | SEG2PH2 <sup>(1)</sup> | SEG2PH1 <sup>(1)</sup> | SEG2PH0 <sup>(1)</sup> |  |  |  |  |

|         | bit 7                                               |                                                                                                                       |                   |             |            |                        |                        | bit 0                  |  |  |  |  |

|         |                                                     |                                                                                                                       |                   |             |            |                        |                        |                        |  |  |  |  |

| bit 7   | WAKDIS:                                             | Wake-up [                                                                                                             | Disable bit       |             |            |                        |                        |                        |  |  |  |  |

|         |                                                     | <ul> <li>1 = Disable CAN bus activity wake-up feature</li> <li>0 = Enable CAN bus activity wake-up feature</li> </ul> |                   |             |            |                        |                        |                        |  |  |  |  |

| bit 6   | WAKFIL: Selects CAN bus Line Filter for Wake-up bit |                                                                                                                       |                   |             |            |                        |                        |                        |  |  |  |  |

|         | 1 = Use CAN bus line filter for wake-up             |                                                                                                                       |                   |             |            |                        |                        |                        |  |  |  |  |

|         | 0 = CAN k                                           | ous line filte                                                                                                        | er is not us      | ed for wake | e-up       |                        |                        |                        |  |  |  |  |

| bit 5-3 | Unimpler                                            | nented: Re                                                                                                            | ad as '0'         |             |            |                        |                        |                        |  |  |  |  |

| bit 2-0 | SEG2PH2                                             | 2:SEG2PH                                                                                                              | <b>0:</b> Phase S | egment 2    | Time Selec | t bits <sup>(1)</sup>  |                        |                        |  |  |  |  |