Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 40MHz                                                                     |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                               |

| Number of I/O              | 36                                                                        |

| Program Memory Size        | 48KB (24K x 16)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 1K x 8                                                                    |

| RAM Size                   | 3.25K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 11x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 44-VQFN Exposed Pad                                                       |

| Supplier Device Package    | 44-QFN (8x8)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f4585-i-ml |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

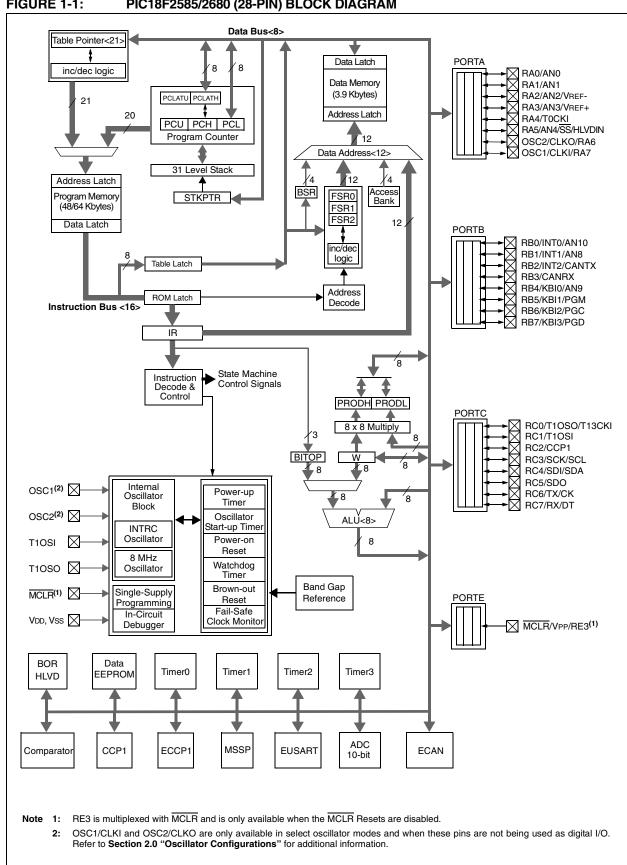

FIGURE 1-1: PIC18F2585/2680 (28-PIN) BLOCK DIAGRAM

TABLE 1-3: PIC18F4585/4680 PINOUT I/O DESCRIPTIONS (CONTINUED)

| Din Nama                                   | Pi   | n Numl | oer  | Pin             | Buffer         | De a suiviti a u                                                                                           |

|--------------------------------------------|------|--------|------|-----------------|----------------|------------------------------------------------------------------------------------------------------------|

| Pin Name                                   | PDIP | QFN    | TQFP | Туре            | Туре           | Description                                                                                                |

|                                            |      |        |      |                 |                | PORTC is a bidirectional I/O port.                                                                         |

| RC0/T10S0/T13CKI<br>RC0<br>T10S0<br>T13CKI | 15   | 34     | 32   | I/O<br>O<br>I   | ST<br>—<br>ST  | Digital I/O. Timer1 oscillator output. Timer1/Timer3 external clock input.                                 |

| RC1/T1OSI<br>RC1<br>T1OSI                  | 16   | 35     | 35   | I/O<br>I        | ST<br>CMOS     | Digital I/O.<br>Timer1 oscillator input.                                                                   |

| RC2/CCP1<br>RC2<br>CCP1                    | 17   | 36     | 36   | I/O<br>I/O      | ST<br>ST       | Digital I/O.<br>Capture1 input/Compare1 output/PWM1 output.                                                |

| RC3/SCK/SCL<br>RC3<br>SCK<br>SCL           | 18   | 37     | 37   | I/O<br>I/O      | ST<br>ST       | Digital I/O. Synchronous serial clock input/output for SPI mode. Synchronous serial clock input/output for |

| RC4/SDI/SDA<br>RC4<br>SDI<br>SDA           | 23   | 42     | 42   | I/O<br>I<br>I/O | ST<br>ST<br>ST | I <sup>2</sup> C™ mode.  Digital I/O.  SPI data in. I <sup>2</sup> C data I/O.                             |

| RC5/SDO<br>RC5<br>SDO                      | 24   | 43     | 43   | I/O<br>O        | ST<br>—        | Digital I/O.<br>SPI data out.                                                                              |

| RC6/TX/CK<br>RC6<br>TX<br>CK               | 25   | 44     | 44   | I/O<br>O<br>I/O | ST<br>—<br>ST  | Digital I/O. EUSART asynchronous transmit. EUSART synchronous clock (see related RX/DT).                   |

| RC7/RX/DT<br>RC7<br>RX<br>DT               | 26   | 1      | 1    | I/O<br>I<br>I/O | ST<br>ST<br>ST | Digital I/O. EUSART asynchronous receive. EUSART synchronous data (see related TX/CK).                     |

**Legend:** TTL = TTL compatible input

CMOS = CMOS compatible input or output

ST = Schmitt Trigger input with CMOS levels

I = Input

O = Output

P = Power

#### 9.3 PIE Registers

The PIE registers contain the individual enable bits for the peripheral interrupts. Due to the number of peripheral interrupt sources, there are two Peripheral Interrupt Enable registers (PIE1, PIE2). When IPEN = 0, the PEIE bit must be set to enable any of these peripheral interrupts.

#### REGISTER 9-7: PIE1: PERIPHERAL INTERRUPT ENABLE REGISTER 1

| R/W-0                | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0  | R/W-0  |

|----------------------|-------|-------|-------|-------|--------|--------|--------|

| PSPIE <sup>(1)</sup> | ADIE  | RCIE  | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE |

| bit 7                |       |       |       |       |        |        | bit 0  |

bit 7 **PSPIE:** Parallel Slave Port Read/Write Interrupt Enable bit<sup>(1)</sup>

1 = Enables the PSP read/write interrupt

0 = Disables the PSP read/write interrupt

Note 1: This bit is reserved on PIC18F2X8X devices; always maintain this bit clear.

bit 6 ADIE: A/D Converter Interrupt Enable bit

1 = Enables the A/D interrupt

0 = Disables the A/D interrupt

bit 5 RCIE: EUSART Receive Interrupt Enable bit

1 = Enables the EUSART receive interrupt

0 = Disables the EUSART receive interrupt

bit 4 TXIE: EUSART Transmit Interrupt Enable bit

1 = Enables the EUSART transmit interrupt

0 = Disables the EUSART transmit interrupt

bit 3 SSPIE: Master Synchronous Serial Port Interrupt Enable bit

1 = Enables the MSSP interrupt

0 = Disables the MSSP interrupt

bit 2 CCP1IE: CCP1 Interrupt Enable bit

1 = Enables the CCP1 interrupt

0 = Disables the CCP1 interrupt

bit 1 TMR2IE: TMR2 to PR2 Match Interrupt Enable bit

1 = Enables the TMR2 to PR2 match interrupt

0 = Disables the TMR2 to PR2 match interrupt

bit 0 TMR1IE: TMR1 Overflow Interrupt Enable bit

1 = Enables the TMR1 overflow interrupt

0 = Disables the TMR1 overflow interrupt

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

# 10.2 PORTB, TRISB and LATB Registers

PORTB is an 8-bit wide, bidirectional port. The corresponding data direction register is TRISB. Setting a TRISB bit (= 1) will make the corresponding PORTB pin an input (i.e., put the corresponding output driver in a high-impedance mode). Clearing a TRISB bit (= 0) will make the corresponding PORTB pin an output (i.e., put the contents of the output latch on the selected pin).

The Data Latch register (LATB) is also memory mapped. Read-modify-write operations on the LATB register read and write the latched output value for PORTB.

Pins RB2 through RB3 are multiplexed with the ECAN peripheral. Refer to **Section 23.0** "**ECAN™ Technology**" for proper settings of TRISB when CAN is enabled.

#### **EXAMPLE 10-2: INITIALIZING PORTB**

|       | LL 10 L | . INTITALIZATION          |

|-------|---------|---------------------------|

| CLRF  | PORTB   | ; Initialize PORTB by     |

|       |         | ; clearing output         |

|       |         | ; data latches            |

| CLRF  | LATB    | ; Alternate method        |

|       |         | ; to clear output         |

|       |         | ; data latches            |

| MOVLW | 0Eh     | ; Set RB<4:0> as          |

| MOVWF | ADCON1  | ; digital I/O pins        |

|       |         | ; (required if config bit |

|       |         | ; PBADEN is set)          |

| MOVLW | 0CFh    | ; Value used to           |

|       |         | ; initialize data         |

|       |         | ; direction               |

| MOVWF | TRISB   | ; Set RB<3:0> as inputs   |

|       |         | ; RB<5:4> as outputs      |

|       |         | ; RB<7:6> as inputs       |

|       |         |                           |

Each of the PORTB pins has a weak internal pull-up. A single control bit can turn on all the pull-ups. This is performed by clearing bit RBPU (INTCON2<7>). The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on all device Resets.

| Note: | On a Power-on Reset, RB4:RB0 are configured as analog inputs by default and read as '0'; RB7:RB5 are configured as digital inputs. |

|-------|------------------------------------------------------------------------------------------------------------------------------------|

|       | By programming the Configuration bit, PBADEN (CONFIG3H<1>), RB4:RB0 will alternatively be configured as digital inputs on POR.     |

Four of the PORTB pins (RB7:RB4) have an interrupt-on-change feature. Only pins configured as inputs can cause this interrupt to occur (i.e., any RB7:RB4 pin configured as an output is excluded from the interrupt-on-change comparison). The input pins (of RB7:RB4) are compared with the old value latched on the last read of PORTB. The "mismatch" outputs of RB7:RB4 are ORed together to generate the RB Port Change Interrupt with Flag bit, RBIF (INTCON<0>).

This interrupt can wake the device from Sleep. The user, in the Interrupt Service Routine, can clear the interrupt in the following manner:

- a) Any read or write of PORTB (except with the MOVFF (ANY), PORTB instruction). This will end the mismatch condition.

- b) Clear flag bit RBIF.

A mismatch condition will continue to set flag bit RBIF. Reading PORTB will end the mismatch condition and allow flag bit RBIF to be cleared.

The interrupt-on-change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt-on-change feature. Polling of PORTB is not recommended while using the interrupt-on-change feature.

NOTES:

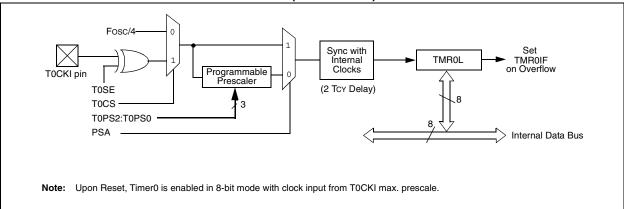

#### 11.1 Timer0 Operation

Timer0 can operate as either a timer or a counter; the mode is selected by clearing the ToCS bit (ToCON<5>). In Timer mode, the module increments on every clock by default unless a different prescaler value is selected (see **Section 11.3 "Prescaler"**). If the TMR0 register is written to, the increment is inhibited for the following two instruction cycles. The user can work around this by writing an adjusted value to the TMR0 register.

The Counter mode is selected by setting the T0CS bit (= 1). In Counter mode, Timer0 increments either on every rising or falling edge of pin RA4/T0CKI. The incrementing edge is determined by the Timer0 Source Edge Select bit, T0SE (T0CON<4>). Clearing this bit selects the rising edge. Restrictions on the external clock input are discussed below.

An external clock source can be used to drive Timer0; however, it must meet certain requirements to ensure that the external clock can be synchronized with the

internal phase clock (Tosc). There is a delay between synchronization and the onset of incrementing the timer/counter.

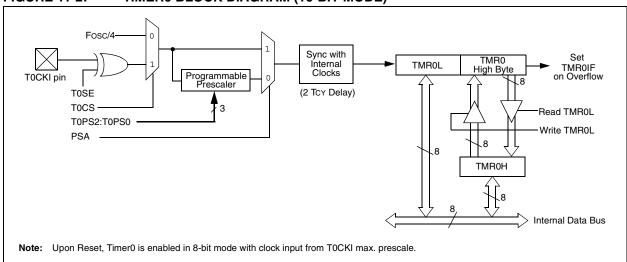

# 11.2 Timer0 Reads and Writes in 16-Bit Mode

TMR0H is not the actual high byte of Timer0 in 16-bit mode; it is actually a buffered version of the real high byte of Timer0, which is not directly readable nor writable (refer to Figure 11-2). TMR0H is updated with the contents of the high byte of Timer0 during a read of TMR0L. This provides the ability to read all 16 bits of Timer0 without having to verify that the read of the high and low byte were valid, due to a rollover between successive reads of the high and low byte.

Similarly, a write to the high byte of Timer0 must also take place through the TMR0H Buffer register. The high byte is updated with the contents of TMR0H when a write occurs to TMR0L. This allows all 16 bits of Timer0 to be updated at once.

#### FIGURE 11-1: TIMERO BLOCK DIAGRAM (8-BIT MODE)

#### FIGURE 11-2: TIMERO BLOCK DIAGRAM (16-BIT MODE)

## REGISTER 16-3: ECCP1AS: ENHANCED CAPTURE/COMPARE/PWM AUTO-SHUTDOWN CONTROL REGISTER

| R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0  | R/W-0  | R/W-0                 | R/W-0                 |

|---------|---------|---------|---------|--------|--------|-----------------------|-----------------------|

| ECCPASE | ECCPAS2 | ECCPAS1 | ECCPAS0 | PSSAC1 | PSSAC0 | PSSBD1 <sup>(1)</sup> | PSSBD0 <sup>(1)</sup> |

| bit 7   |         |         |         |        |        |                       | bit 0                 |

bit 7 ECCPASE: ECCP1 Auto-Shutdown Event Status bit

1 = A shutdown event has occurred; ECCP1 outputs are in shutdown state

0 = ECCP1 outputs are operating

bit 6-4 ECCPAS2:ECCPAS0: ECCP1 Auto-Shutdown Source Select bits

111 = RB0 or Comparator 1 or Comparator 2

110 = RB0 or Comparator 2

101 = RB0 or Comparator 1

100 = **RB0**

011 = Either Comparator 1 or 2

010 = Comparator 2 output

001 = Comparator 1 output

000 = Auto-shutdown is disabled

bit 3-2 PSSAC1:PSSAC0: Pins A and C Shutdown State Control bits

1x = Pins A and C tri-state (PIC18F4X8X devices);

01 = Drive Pins A and C to '1'

00 = Drive Pins A and C to '0'

bit 1-0 **PSSBD1:PSSBD0:** Pins B and D Shutdown State Control bits<sup>(1)</sup>

1x = Pins B and D tri-state

01 = Drive Pins B and D to '1'

00 = Drive Pins B and D to '0'

Note 1: Reserved on PIC18F2X8X devices; maintain these bits clear.

#### Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

Note:

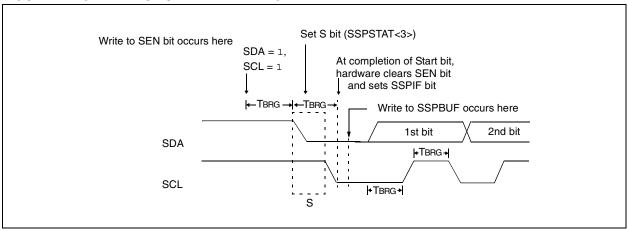

# 17.4.8 I<sup>2</sup>C MASTER MODE START CONDITION TIMING

To initiate a Start condition, the user sets the Start Enable bit, SEN (SSPCON2<0>). If the SDA and SCL pins are sampled high, the Baud Rate Generator is reloaded with the contents of SSPADD<6:0> and starts its count. If SCL and SDA are both sampled high when the Baud Rate Generator times out (TBRG), the SDA pin is driven low. The action of the SDA being driven low while SCL is high is the Start condition and causes the S bit (SSPSTAT<3>) to be set. Following this, the Baud Rate Generator is reloaded with the contents of SSPADD<6:0> and resumes its count. When the Baud Rate Generator times out (TBRG), the SEN bit (SSPCON2<0>) will be automatically cleared by hardware, the Baud Rate Generator is suspended, leaving the SDA line held low and the Start condition is complete.

If at the beginning of the Start condition, the SDA and SCL pins are already sampled low, or if during the Start condition, the SCL line is sampled low before the SDA line is driven low, a bus collision occurs, the Bus Collision Interrupt Flag, BCLIF, is set, the Start condition is aborted and the I<sup>2</sup>C module is reset into its Idle state.

#### 17.4.8.1 WCOL Status Flag

If the user writes the SSPBUF when a Start sequence is in progress, the WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

bte: Because queueing of events is not allowed, writing to the lower 5 bits of SSPCON2 is disabled until the Start condition is complete.

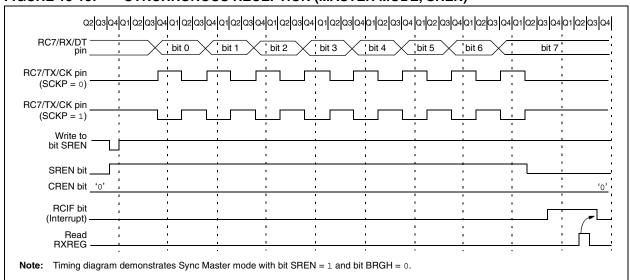

## 18.3.2 EUSART SYNCHRONOUS MASTER RECEPTION

Once Synchronous mode is selected, reception is enabled by setting either the Single Receive Enable bit, SREN (RCSTA<5>), or the Continuous Receive Enable bit, CREN (RCSTA<4>). Data is sampled on the RX pin on the falling edge of the clock.

If enable bit SREN is set, only a single word is received. If enable bit CREN is set, the reception is continuous until CREN is cleared. If both bits are set, then CREN takes precedence.

To set up a Synchronous Master Reception:

- Initialize the SPBRGH:SPBRG registers for the appropriate baud rate. Set or clear the BRG16 bit, as required, to achieve the desired baud rate.

- Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC.

- 3. Ensure bits CREN and SREN are clear.

- 4. If interrupts are desired, set enable bit RCIE.

- 5. If 9-bit reception is desired, set bit RX9.

- 6. If a single reception is required, set bit SREN. For continuous reception, set bit CREN.

- Interrupt flag bit RCIF will be set when reception is complete and an interrupt will be generated if the enable bit RCIE was set.

- Read the RCSTA register to get the 9th bit (if enabled) and determine if any error occurred during reception.

- Read the 8-bit received data by reading the RCREG register.

- If any error occurred, clear the error by clearing bit CREN.

- If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set

#### FIGURE 18-13: SYNCHRONOUS RECEPTION (MASTER MODE, SREN)

#### TABLE 18-8: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER RECEPTION

| Name    | Bit 7                                         | Bit 6         | Bit 5          | Bit 4      | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values on<br>page |

|---------|-----------------------------------------------|---------------|----------------|------------|-------|--------|--------|--------|----------------------------|

| INTCON  | GIE/GIEH                                      | PEIE/GIEL     | TMR0IE         | INT0IE     | RBIE  | TMR0IF | INT0IF | RBIF   | 49                         |

| PIR1    | PSPIF <sup>(1)</sup>                          | ADIF          | RCIF           | TXIF       | SSPIF | CCP1IF | TMR2IF | TMR1IF | 52                         |

| PIE1    | PSPIE <sup>(1)</sup>                          | ADIE          | RCIE           | TXIE       | SSPIE | CCP1IE | TMR2IE | TMR1IE | 52                         |

| IPR1    | PSPIP <sup>(1)</sup>                          | ADIP          | RCIP           | TXIP       | SSPIP | CCP1IP | TMR2IP | TMR1IP | 52                         |

| RCSTA   | SPEN                                          | RX9           | SREN           | CREN       | ADDEN | FERR   | OERR   | RX9D   | 51                         |

| RCREG   | EUSART Re                                     | ceive Registe | r              |            |       |        |        |        | 51                         |

| TXSTA   | CSRC                                          | TX9           | TXEN           | SYNC       | SENDB | BRGH   | TRMT   | TX9D   | 51                         |

| BAUDCON | ABDOVF                                        | RCIDL         | _              | SCKP       | BRG16 | _      | WUE    | ABDEN  | 51                         |

| SPBRGH  | EUSART Baud Rate Generator Register High Byte |               |                |            |       |        |        |        | 51                         |

| SPBRG   | EUSART Ba                                     | ud Rate Gene  | erator Registe | r Low Byte |       |        |        |        | 51                         |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used for synchronous master reception.

Note 1: Reserved in PIC18F2X8X devices; always maintain these bits clear.

# 18.4 EUSART Synchronous Slave Mode

Synchronous Slave mode is entered by clearing bit, CSRC (TXSTA<7>). This mode differs from the Synchronous Master mode in that the shift clock is supplied externally at the CK pin (instead of being supplied internally in Master mode). This allows the device to transfer or receive data while in any low-power mode.

## 18.4.1 EUSART SYNCHRONOUS SLAVE TRANSMIT

The operation of the Synchronous Master and Slave modes are identical, except in the case of the Sleep mode.

If two words are written to the TXREG and then the SLEEP instruction is executed, the following will occur:

- The first word will immediately transfer to the TSR register and transmit.

- The second word will remain in the TXREG register.

- c) Flag bit TXIF will not be set.

- d) When the first word has been shifted out of TSR, the TXREG register will transfer the second word to the TSR and flag bit TXIF will now be set.

- If enable bit TXIE is set, the interrupt will wake the chip from Sleep. If the global interrupt is enabled, the program will branch to the interrupt vector.

To set up a Synchronous Slave Transmission:

- Enable the synchronous slave serial port by setting bits SYNC and SPEN and clearing bit CSRC.

- 2. Clear bits CREN and SREN.

- 3. If interrupts are desired, set enable bit TXIE.

- 4. If 9-bit transmission is desired, set bit TX9.

- Enable the transmission by setting enable bit TXEN.

- If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- Start transmission by loading data to the TXREGx register.

- 8. If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

TABLE 18-9: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE TRANSMISSION

| Name    | Bit 7                                                | Bit 6        | Bit 5       | Bit 4        | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

|---------|------------------------------------------------------|--------------|-------------|--------------|-------|--------|--------|--------|----------------------------|

| INTCON  | GIE/GIEH                                             | PEIE/GIEL    | TMR0IE      | INT0IE       | RBIE  | TMR0IF | INT0IF | RBIF   | 49                         |

| PIR1    | PSPIF <sup>(1)</sup>                                 | ADIF         | RCIF        | TXIF         | SSPIF | CCP1IF | TMR2IF | TMR1IF | 52                         |

| PIE1    | PSPIE <sup>(1)</sup>                                 | ADIE         | RCIE        | TXIE         | SSPIE | CCP1IE | TMR2IE | TMR1IE | 52                         |

| IPR1    | PSPIP <sup>(1)</sup>                                 | ADIP         | RCIP        | TXIP         | SSPIP | CCP1IP | TMR2IP | TMR1IP | 52                         |

| RCSTA   | SPEN                                                 | RX9          | SREN        | CREN         | ADDEN | FERR   | OERR   | RX9D   | 51                         |

| TXREG   | EUSART T                                             | ransmit Regi | ister       |              |       |        |        |        | 51                         |

| TXSTA   | CSRC                                                 | TX9          | TXEN        | SYNC         | SENDB | BRGH   | TRMT   | TX9D   | 51                         |

| BAUDCON | ABDOVF                                               | RCIDL        | -           | SCKP         | BRG16 | _      | WUE    | ABDEN  | 51                         |

| SPBRGH  | SPBRGH EUSART Baud Rate Generator Register High Byte |              |             |              |       |        |        |        | 51                         |

| SPBRG   | EUSART B                                             | Baud Rate Ge | enerator Re | gister Low E | Byte  |        |        |        | 51                         |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used for synchronous slave transmission.

Note 1: Reserved in PIC18F2X8X devices; always maintain these bits clear.

#### 19.6 A/D Conversions

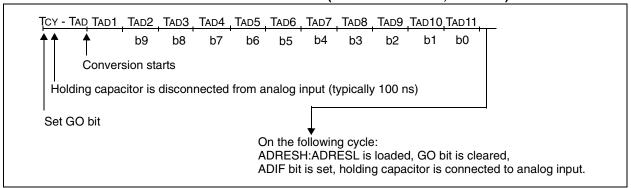

Figure 19-3 shows the operation of the A/D converter after the GO bit has been set and the ACQT2:ACQT0 bits are cleared. A conversion is started after the following instruction to allow entry into Sleep mode before the conversion begins.

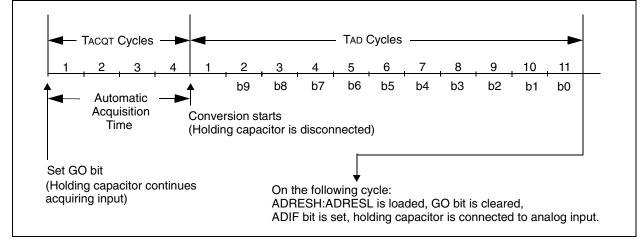

Figure 19-4 shows the operation of the A/D converter after the GO bit has been set and the ACQT2:ACQT0 bits are set to '010' and selecting a 4 TAD acquisition time before the conversion starts.

Clearing the GO/DONE bit during a conversion will abort the current conversion. The A/D Result register pair will NOT be updated with the partially completed A/D conversion sample. This means the ADRESH:ADRESL registers will continue to contain the value of the last completed conversion (or the last value written to the ADRESH:ADRESL registers).

After the A/D conversion is completed or aborted, a 2 TAD wait is required before the next acquisition can be started. After this wait, acquisition on the selected channel is automatically started.

Note: The GO/DONE bit should NOT be set in the same instruction that turns on the A/D.

#### FIGURE 19-3: A/D CONVERSION TAD CYCLES (ACQT<2:0> = 000, TACQ = 0)

#### FIGURE 19-4: A/D CONVERSION TAD CYCLES (ACQT<2:0> = 010, TACQ = 4 TAD)

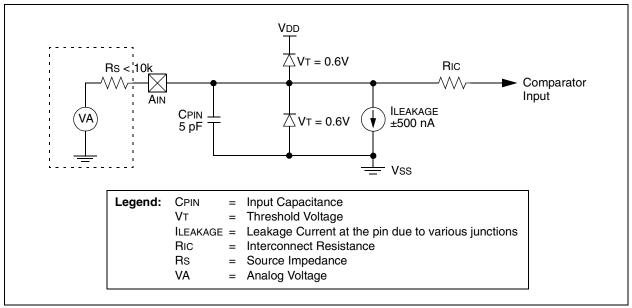

# 20.9 Analog Input Connection Considerations

A simplified circuit for an analog input is shown in Figure 20-4. Since the analog pins are connected to a digital output, they have reverse biased diodes to VDD and Vss. The analog input, therefore, must be between Vss and VDD. If the input voltage deviates from this

range by more than 0.6V in either direction, one of the diodes is forward biased and a latch-up condition may occur. A maximum source impedance of 10  $k\Omega$  is recommended for the analog sources. Any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have very little leakage current.

FIGURE 20-4: COMPARATOR ANALOG INPUT MODEL

TABLE 20-1: REGISTERS ASSOCIATED WITH COMPARATOR MODULE

| Name                  | Bit 7                 | Bit 6                 | Bit 5     | Bit 4                    | Bit 3      | Bit 2  | Bit 1  | Bit 0                  | Reset<br>Values<br>on page |  |

|-----------------------|-----------------------|-----------------------|-----------|--------------------------|------------|--------|--------|------------------------|----------------------------|--|

| CMCON(3)              | C2OUT                 | C1OUT                 | C2INV     | C1INV                    | CIS        | CM2    | CM1    | CM0                    | 51                         |  |

| CVRCON <sup>(3)</sup> | CVREN                 | CVROE                 | CVRR      | CVRSS                    | CVR3       | CVR2   | CVR1   | CVR0                   | 51                         |  |

| INTCON                | GIE/GIEH              | PEIE/GIEL             | TMR0IE    | INT0IE                   | RBIE       | TMR0IF | INT0IF | RBIF                   | 52                         |  |

| IPR2                  | OSCFIP                | CMIP <sup>(2)</sup>   |           | EEIP                     | BCLIP      | HLVDIP | TMR3IP | ECCP1IP <sup>(2)</sup> | 51                         |  |

| PIR2                  | OSCFIF                | CMIF <sup>(2)</sup>   |           | EEIF                     | BCLIF      | HLVDIF | TMR3IF | ECCP1IF <sup>(2)</sup> | 51                         |  |

| PIE2                  | OSCFIE                | CMIE <sup>(2)</sup>   |           | EEIE                     | BCLIE      | HLVDIE | TMR3IE | ECCP1IE <sup>(2)</sup> | 52                         |  |

| PORTA                 | RA7 <sup>(1)</sup>    | RA6 <sup>(1)</sup>    | RA5       | RA4                      | RA3        | RA2    | RA1    | RA0                    | 52                         |  |

| LATA                  | LATA7 <sup>(1)</sup>  | LATA6 <sup>(1)</sup>  | LATA Data | ATA Data Output Register |            |        |        |                        |                            |  |

| TRISA                 | TRISA7 <sup>(1)</sup> | TRISA6 <sup>(1)</sup> | PORTA Da  | ata Directio             | n Register |        | •      |                        | 52                         |  |

**Legend:** — = unimplemented, read as '0'. Shaded cells are unused by the comparator module.

Note 1: PORTA pins are enabled based on oscillator configuration.

2: These bits are available in PIC18F4X8X devices and reserved in PIC18F2X8X devices.

3: These registers are unimplemented on PIC18F2X8X devices.

TABLE 23-1: CAN CONTROLLER REGISTER MAP (CONTINUED)

| Address <sup>(1)</sup> | Name     | Address | Name    | Address | Name | Address | Name      |

|------------------------|----------|---------|---------|---------|------|---------|-----------|

| DFFh                   | (4)      | DDFh    | (4)     | DBFh    | (4)  | D9Fh    | (4)       |

| DFEh                   | (4)      | DDEh    | (4)     | DBEh    | (4)  | D9Eh    | (4)       |

| DFDh                   | (4)      | DDDh    | (4)     | DBDh    | (4)  | D9Dh    | (4)       |

| DFCh                   | TXBIE    | DDCh    | (4)     | DBCh    | (4)  | D9Ch    | (4)       |

| DFBh                   | (4)      | DDBh    | (4)     | DBBh    | (4)  | D9Bh    | (4)       |

| DFAh                   | BIE0     | DDAh    | (4)     | DBAh    | (4)  | D9Ah    | (4)       |

| DF9h                   | (4)      | DD9h    | (4)     | DB9h    | (4)  | D99h    | (4)       |

| DF8h                   | BSEL0    | DD8h    | SDFLC   | DB8h    | (4)  | D98h    | (4)       |

| DF7h                   | (4)      | DD7h    | (4)     | DB7h    | (4)  | D97h    | (4)       |

| DF6h                   | (4)      | DD6h    | (4)     | DB6h    | (4)  | D96h    | (4)       |

| DF5h                   | (4)      | DD5h    | RXFCON1 | DB5h    | (4)  | D95h    | (4)       |

| DF4h                   | (4)      | DD4h    | RXFCON0 | DB4h    | (4)  | D94h    | (4)       |

| DF3h                   | MSEL3    | DD3h    | (4)     | DB3h    | (4)  | D93h    | RXF15EIDL |

| DF2h                   | MSEL2    | DD2h    | (4)     | DB2h    | (4)  | D92h    | RXF15EIDH |

| DF1h                   | MSEL1    | DD1h    | (4)     | DB1h    | (4)  | D91h    | RXF15SIDL |

| DF0h                   | MSEL0    | DD0h    | (4)     | DB0h    | (4)  | D90h    | RXF15SIDH |

| DEFh                   | (4)      | DCFh    | (4)     | DAFh    | (4)  | D8Fh    | (4)       |

| DEEh                   | (4)      | DCEh    | (4)     | DAEh    | (4)  | D8Eh    | (4)       |

| DEDh                   | (4)      | DCDh    | (4)     | DADh    | (4)  | D8Dh    | (4)       |

| DECh                   | (4)      | DCCh    | (4)     | DACh    | (4)  | D8Ch    | (4)       |

| DEBh                   | (4)      | DCBh    | (4)     | DABh    | (4)  | D8Bh    | RXF14EIDL |

| DEAh                   | (4)      | DCAh    | (4)     | DAAh    | (4)  | D8Ah    | RXF14EIDH |

| DE9h                   | (4)      | DC9h    | (4)     | DA9h    | (4)  | D89h    | RXF14SIDL |

| DE8h                   | (4)      | DC8h    | (4)     | DA8h    | (4)  | D88h    | RXF14SIDH |

| DE7h                   | RXFBCON7 | DC7h    | (4)     | DA7h    | (4)  | D87h    | RXF13EIDL |

| DE6h                   | RXFBCON6 | DC6h    | (4)     | DA6h    | (4)  | D86h    | RXF13EIDH |

| DE5h                   | RXFBCON5 | DC5h    | (4)     | DA5h    | (4)  | D85h    | RXF13SIDL |

| DE4h                   | RXFBCON4 | DC4h    | (4)     | DA4h    | (4)  | D84h    | RXF13SIDH |

| DE3h                   | RXFBCON3 | DC3h    | (4)     | DA3h    | (4)  | D83h    | RXF12EIDL |

| DE2h                   | RXFBCON2 | DC2h    | (4)     | DA2h    | (4)  | D82h    | RXF12EIDH |

| DE1h                   | RXFBCON1 | DC1h    | (4)     | DA1h    | (4)  | D81h    | RXF12SIDL |

| DE0h                   | RXFBCON0 | DC0h    | (4)     | DA0h    | (4)  | D80h    | RXF12SIDH |

Note 1: Shaded registers are available in Access Bank low area, while the rest are available in Bank 15.

**<sup>2:</sup>** CANSTAT register is repeated in these locations to simplify application firmware. Unique names are given for each instance of the controller register due to the Microchip header file requirement.

<sup>3:</sup> These registers are not CAN registers.

<sup>4:</sup> Unimplemented registers are read as '0'.

#### **REGISTER 24-4:** CONFIG3H: CONFIGURATION REGISTER 3 HIGH (BYTE ADDRESS 300005h)

| R/P-1 | U-0 | U-0 | U-0 | U-0 | R/P-0   | R/P-1  | U-0   |

|-------|-----|-----|-----|-----|---------|--------|-------|

| MCLRE | _   | _   | _   | _   | LPT1OSC | PBADEN | _     |

| bit 7 |     |     |     |     |         |        | bit 0 |

bit 0

- bit 7 MCLRE: MCLR Pin Enable bit

- $1 = \overline{MCLR}$  pin enabled; RE3 input pin disabled 0 = RE3 input pin enabled; MCLR disabled

- Unimplemented: Read as '0' bit 6-3

- bit 2 LPT10SC: Low-Power Timer 1 Oscillator Enable bit

- 1 = Timer1 configured for low-power operation

- 0 = Timer1 configured for higher power operation

- bit 1 PBADEN: PORTB A/D Enable bit

(Affects ADCON1 Reset state. ADCON1 controls PORTB<4:0> pin configuration.)

- 1 = PORTB<4:0> pins are configured as analog input channels on Reset

- 0 = PORTB<4:0> pins are configured as digital I/O on Reset

- bit 0 Unimplemented: Read as '0'

#### Legend:

R = Readable bit P = Programmable bit U = Unimplemented bit, read as '0' u = Unchanged from programmed state -n = Value when device is unprogrammed

#### **REGISTER 24-5:** CONFIG4L: CONFIGURATION REGISTER 4 LOW (BYTE ADDRESS 300006h)

| R/P-1 | R/P-0 | R/P-0  | R/P-0  | U-0 | R/P-1 | U-0 | R/P-1  |

|-------|-------|--------|--------|-----|-------|-----|--------|

| DEBUG | XINST | BBSIZ1 | BBSIZ2 | _   | LVP   | _   | STVREN |

| hit 7 |       |        |        |     |       |     | hit ∩  |

- bit 7 **DEBUG:** Background Debugger Enable bit

- 1 = Background debugger disabled, RB6 and RB7 configured as general purpose I/O pins

- 0 = Background debugger enabled, RB6 and RB7 are dedicated to In-Circuit Debug

- bit 6 XINST: Extended Instruction Set Enable bit

- 1 = Instruction set extension and Indexed Addressing mode enabled

- 0 = Instruction set extension and Indexed Addressing mode disabled (Legacy mode)

- bit 5 BBSIZ1: Boot Block Size Select Bit 1

- 11 = 4K words (8 Kbytes) boot block

- 10 = 4K words (8 Kbytes) boot block

- bit 4 BBSIZ2: Boot Block Size Select Bit 0

- 01 = 2K words (4 Kbytes) boot block

- 00 = 1K words (2 Kbytes) boot block

- bit 3 Unimplemented: Read as '0'

- LVP: Single-Supply ICSP Enable bit bit 2

- 1 = Single-Supply ICSP enabled

- 0 = Single-Supply ICSP disabled

- bit 1 Unimplemented: Read as '0'

- bit 0 STVREN: Stack Full/Underflow Reset Enable bit

- 1 = Stack full/underflow will cause Reset

- 0 = Stack full/underflow will not cause Reset

#### Legend:

R = Readable bit C = Clearable bit U = Unimplemented bit, read as '0' -n = Value when device is unprogrammed u = Unchanged from programmed state

TABLE 25-2: PIC18FXXXX INSTRUCTION SET (CONTINUED)

| Mnemonic,<br>Operands |         | Description                    | Cycles     | 16-Bit Instruction Word |      |      |      | Status                 | Notes |

|-----------------------|---------|--------------------------------|------------|-------------------------|------|------|------|------------------------|-------|

|                       |         |                                |            | MSb                     |      |      | LSb  | Affected               | Notes |

| BIT-ORIEN             | TED OP  | ERATIONS                       |            |                         |      |      |      |                        |       |

| BCF                   | f, b, a | Bit Clear f                    | 1          | 1001                    | bbba | ffff | ffff | None                   | 1, 2  |

| BSF                   | f, b, a | Bit Set f                      | 1          | 1000                    | bbba | ffff | ffff | None                   | 1, 2  |

| BTFSC                 | f, b, a | Bit Test f, Skip if Clear      | 1 (2 or 3) | 1011                    | bbba | ffff | ffff | None                   | 3, 4  |

| BTFSS                 | f, b, a | Bit Test f, Skip if Set        | 1 (2 or 3) | 1010                    | bbba | ffff | ffff | None                   | 3, 4  |

| BTG                   | f, b, a | Bit Toggle f                   | 1          | 0111                    | bbba | ffff | ffff | None                   | 1, 2  |

| CONTROL               | OPERA   | TIONS                          |            | •                       |      |      |      |                        | •     |

| ВС                    | n       | Branch if Carry                | 1 (2)      | 1110                    | 0010 | nnnn | nnnn | None                   |       |

| BN                    | n       | Branch if Negative             | 1 (2)      | 1110                    | 0110 | nnnn | nnnn | None                   |       |

| BNC                   | n       | Branch if Not Carry            | 1 (2)      | 1110                    | 0011 | nnnn | nnnn | None                   |       |

| BNN                   | n       | Branch if Not Negative         | 1 (2)      | 1110                    | 0111 | nnnn | nnnn | None                   |       |

| BNOV                  | n       | Branch if Not Overflow         | 1 (2)      | 1110                    | 0101 | nnnn | nnnn | None                   |       |

| BNZ                   | n       | Branch if Not Zero             | 1 (2)      | 1110                    | 0001 | nnnn | nnnn | None                   |       |

| BOV                   | n       | Branch if Overflow             | 1 (2)      | 1110                    | 0100 | nnnn | nnnn | None                   |       |

| BRA                   | n       | Branch Unconditionally         | 2          | 1101                    | 0nnn | nnnn | nnnn | None                   |       |

| BZ                    | n       | Branch if Zero                 | 1 (2)      | 1110                    | 0000 | nnnn | nnnn | None                   |       |

| CALL                  | n, s    | Call subroutine1st word        | 2          | 1110                    | 110s | kkkk | kkkk | None                   |       |

|                       |         | 2nd word                       |            | 1111                    | kkkk | kkkk | kkkk |                        |       |

| CLRWDT                | _       | Clear Watchdog Timer           | 1          | 0000                    | 0000 | 0000 | 0100 | TO, PD                 |       |

| DAW                   | _       | Decimal Adjust WREG            | 1          | 0000                    | 0000 | 0000 | 0111 | С                      |       |

| GOTO                  | n       | Go to address 1st word         | 2          | 1110                    | 1111 | kkkk | kkkk | None                   |       |

|                       |         | 2nd word                       |            | 1111                    | kkkk | kkkk | kkkk |                        |       |

| NOP                   | _       | No Operation                   | 1          | 0000                    | 0000 | 0000 | 0000 | None                   |       |

| NOP                   | _       | No Operation                   | 1          | 1111                    | XXXX | XXXX | XXXX | None                   | 4     |

| POP                   | _       | Pop top of return stack (TOS)  | 1          | 0000                    | 0000 | 0000 | 0110 | None                   |       |

| PUSH                  | _       | Push top of return stack (TOS) | 1          | 0000                    | 0000 | 0000 | 0101 | None                   |       |

| RCALL                 | n       | Relative Call                  | 2          | 1101                    | 1nnn | nnnn | nnnn |                        |       |

| RESET                 |         | Software device Reset          | 1          | 0000                    | 0000 | 1111 | 1111 | All                    |       |

| RETFIE                | S       | Return from interrupt enable   | 2          | 0000                    | 0000 | 0001 | 000s | GIE/GIEH,<br>PEIE/GIEL |       |

| RETLW                 | k       | Return with literal in WREG    | 2          | 0000                    | 1100 | kkkk | kkkk | None                   |       |

| RETURN                | s       | Return from Subroutine         | 2          | 0000                    | 0000 | 0001 | 001s | None                   |       |

| SLEEP                 | _       | Go into Standby mode           | 1          | 0000                    |      | 0000 | 0011 | TO, PD                 |       |

Note 1: When a Port register is modified as a function of itself (e.g., MOVF PORTB, 1, 0), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

- 2: If this instruction is executed on the TMR0 register (and where applicable, 'd' = 1), the prescaler will be cleared if assigned.

- **3:** If Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

- 4: Some instructions are two-word instructions. The second word of these instructions will be executed as a NOP unless the first word of the instruction retrieves the information embedded in these 16 bits. This ensures that all program memory locations have a valid instruction.

- 5: If the table write starts the write cycle to internal memory, the write will continue until terminated.

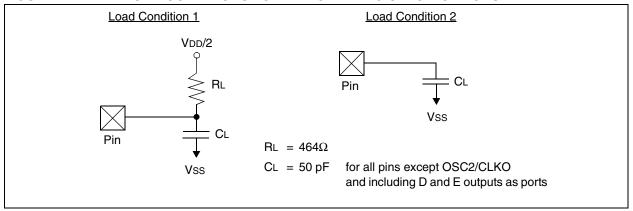

#### 27.4.2 TIMING CONDITIONS

The temperature and voltages specified in Table 27-5 apply to all timing specifications unless otherwise noted. Figure 27-4 specifies the load conditions for the timing specifications.

Note: Because of space limitations, the generic terms "PIC18FXXXX" and "PIC18LFXXXX" are used throughout this section to refer to the PIC18F2585/2680/4585/4680 and PIC18LF2585/2680/4585/4680 families of

devices specifically and only those devices.

#### TABLE 27-5: TEMPERATURE AND VOLTAGE SPECIFICATIONS - AC

AC CHARACTERISTICS

Standard Operating Conditions (unless otherwise stated)

Operating temperature -40°C ≤ TA ≤ +85°C for industrial

Operating voltage VDD range as described in DC spec Section 27.1 and

Section 27.3. LF parts operate for industrial temperatures only.

#### FIGURE 27-4: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS

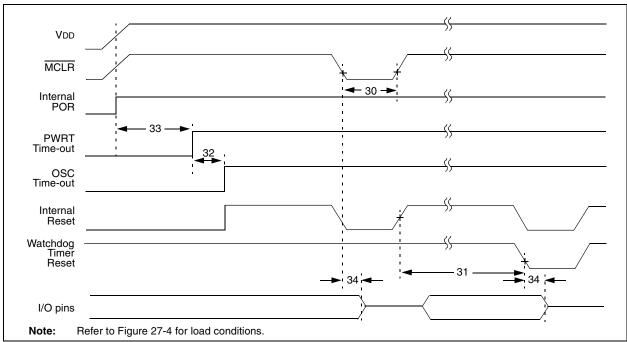

FIGURE 27-7: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER TIMING

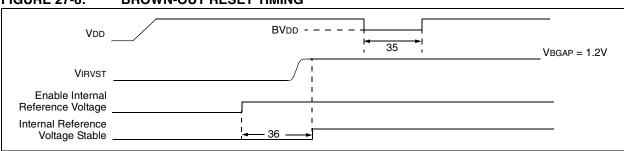

FIGURE 27-8: BROWN-OUT RESET TIMING

TABLE 27-10: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER AND BROWN-OUT RESET REQUIREMENTS

| Param.<br>No. | Sym    | Characteristic                                           | Min       | Тур  | Max       | Units | Conditions            |

|---------------|--------|----------------------------------------------------------|-----------|------|-----------|-------|-----------------------|

| 30            | TMCL   | MCLR Pulse Width (low)                                   | 2         | _    | _         | μs    |                       |

| 31            | TWDT   | Watchdog Timer Time-out Period (no postscaler)           | 3.4       | 4.00 | 4.6       | ms    |                       |

| 32            | Tost   | Oscillation Start-up Timer Period                        | 1024 Tosc | _    | 1024 Tosc | _     | Tosc = OSC1 period    |

| 33            | TPWRT  | Power-up Timer Period                                    | 55.6      | 65.5 | 75        | ms    |                       |

| 34            | Tioz   | I/O High-Impedance from MCLR Low or Watchdog Timer Reset | _         | 2    | _         | μs    |                       |

| 35            | TBOR   | Brown-out Reset Pulse Width                              | 200       | _    | _         | μs    | VDD ≤ BVDD (see D005) |

| 36            | TIRVST | Time for Internal Reference Voltage to become stable     | _         | 20   | 50        | μs    |                       |

| 37            | TLVD   | High/Low-Voltage Detect Pulse Width                      | 200       | _    | _         | μs    | VDD ≤ VLVD            |

| 38            | TCSD   | CPU Start-up Time                                        | _         | 10   | _         | μs    |                       |

| 39            | TIOBST | Time for INTOSC to stabilize                             | _         | 1    | _         | μs    |                       |

#### **INDEX**

| A                                          |

|--------------------------------------------|

| A/D247                                     |

| Acquisition Requirements252                |

| ADCON0 Register247                         |

| ADCON1 Register247                         |

| ADCON2 Register247                         |

| ADRESH Register247, 250                    |

| ADRESL Register247                         |

| Analog Port Pins, Configuring254           |

| Associated Registers256                    |

| Automatic Acquisition Time253              |

| Configuring the Module251                  |

| Conversion Clock (TAD) 253                 |

| Conversion Status (GO/DONE Bit)250         |

| Conversions255                             |

| Converter Characteristics449               |

| Converter Interrupt, Configuring251        |

| Operation in Power Managed Modes254        |

| Special Event Trigger (ECCP1)174, 256      |

| Use of the CCP1 Trigger256                 |

| Absolute Maximum Ratings415                |

| AC (Timing) Characteristics431             |

| Load Conditions for Device                 |

| Timing Specifications432                   |

| Parameter Symbology431                     |

| Temperature and Voltage Specifications432  |

| Timing Conditions432                       |

| Access Bank69                              |

| Mapping with Indexed Literal Offset Mode93 |

| ACKSTAT217                                 |

| ACKSTAT Status Flag217                     |

| ADCON0 Register247                         |

| GO/DONE Bit250                             |

| ADCON1 Register247                         |

| ADCON2 Register247                         |

| ADDFSR                                     |

| ADDLW367                                   |

| ADDULNK404                                 |

| ADDWF                                      |

| ADDWFC                                     |

| ADRESH Register247                         |

| ADRESL Register247, 250                    |

| Analog-to-Digital Converter. See A/D.      |

| and BSR93                                  |

| ANDLW368                                   |

| ANDWF                                      |

| Assembler                                  |

| MPASM Assembler412                         |

| Auto-Wake-up on Sync Break Character240    |

| В                                          |

|                                            |

| Bank Select Register (BSR)                 |

| Baud Rate Generator                        |

| Baud Rate Generator (BRG)231               |

| BC                                         |

| BCF                                        |

| BF                                         |

| BF Status Flag217                          |

| •                                          |

| Bit Timing Configuration Registers         |

| Bit Timing Configuration Registers BRGCON1 |

| Bit Timing Configuration Registers         |

| Block Diagrams                                   |     |

|--------------------------------------------------|-----|

| A/D                                              | 250 |

| Analog Input Model                               |     |

| Baud Rate Generator                              |     |

| CAN Buffers and Protocol Engine                  |     |

| Capture Mode Operation                           |     |

| Comparator Analog Input Model                    |     |

| Comparator I/O Operating Modes                   |     |

| Comparator Output                                |     |

| Comparator Voltage Reference                     |     |

| Compare Mode Operation                           |     |

| Device Clock                                     |     |

| Enhanced PWM                                     |     |

| EUSART Receive                                   |     |

| EUSART Transmit  External Power-on Reset Circuit | 236 |

|                                                  | 40  |

| (Slow VDD Power-up)Fail-Safe Clock Monitor       |     |

| Generic I/O Port Operation                       |     |

| High/Low-Voltage Detect with External Input      |     |

| MSSP (I <sup>2</sup> C Master Mode)              |     |

| MSSP (I <sup>2</sup> C Mode)                     |     |

| MSSP (SPI Mode)                                  |     |

| On-Chip Reset Circuit                            |     |

| PIC18F2585/2680                                  |     |

| PIC18F4585/4680                                  |     |

| PLL (HS Mode)                                    |     |

| PORTD and PORTE (Parallel Slave Port)            |     |

| PWM Operation (Simplified)                       |     |

| Reads from Flash Program Memory                  |     |

| Single Comparator                                |     |

| Table Read Operation                             |     |

| Table Write Operation                            |     |

| Table Writes to Flash Program Memory             |     |

| Timer0 in 16-Bit Mode                            |     |

| Timer0 in 8-Bit Mode                             |     |

| Timer1                                           |     |

| Timer1 (16-Bit Read/Write Mode)                  | 152 |

| Timer2                                           | 158 |

| Timer3                                           | 160 |

| Timer3 (16-Bit Read/Write Mode)                  | 160 |

| Voltage Reference Output Buffer Example          |     |

| Watchdog Timer                                   |     |

| BN                                               | 370 |

| BNC                                              |     |

| BNN                                              |     |

| BNOV                                             |     |

| BNZ                                              | 372 |

| BOR. See Brown-out Reset.                        |     |

| BOV                                              |     |

| BRA                                              | 373 |

| BRG. See Baud Rate Generator.                    |     |

| Brown-out Reset (BOR)                            |     |

| Detecting                                        |     |

| Disabling in Sleep mode                          |     |

| Software Enabled                                 |     |

| BSF                                              |     |

| BTFSC                                            | -   |

| BTG                                              |     |

| BZ                                               |     |

| UL                                               | 3/6 |

| RXBnSIDL (Receive Buffer n Standard                                         |       |

|-----------------------------------------------------------------------------|-------|

| Identifier, Low Byte)                                                       | 291   |

| RXERRCNT (Receive Error Count)                                              |       |

| RXFBCONn (Receive Filter Buffer Control n)                                  |       |

| RXFCONn (Receive Filter Control n)                                          |       |

| RXFnEIDH (Receive Acceptance Filter n                                       | 303   |

| Extended Identifier, High Byte)                                             | 3し3   |

| RXFnEIDL (Receive Acceptance Filter n                                       | 303   |

| Extended Identifier, Low Byte)                                              | 202   |

|                                                                             | 303   |

| RXFnSIDH (Receive Acceptance Filter n                                       | 200   |

| Standard Identifier Filter, High Byte)                                      | 302   |

| RXFnSIDL (Receive Acceptance Filter n                                       | 200   |

| Standard Identifier Filter, Low Byte)                                       | 302   |

| RXMnEIDH (Receive Acceptance Mask n<br>Extended Identifier Mask, High Byte) | 204   |

|                                                                             | 304   |

| RXMnEIDL (Receive Acceptance Mask n                                         | 20.4  |

| Extended Identifier Mask, Low Byte)                                         | 304   |

| RXMnSIDH (Receive Acceptance Mask n                                         | 200   |

| Standard Identifier Mask, High Byte)                                        | 303   |

| RXMnSIDL (Receive Acceptance Mask n                                         |       |

| Standard Identifier Mask, Low Byte)                                         | 304   |

| SDFLC (Standard Data Bytes                                                  |       |

| Filter Length Count)                                                        |       |

| SSPCON1 (MSSP Control 1, I <sup>2</sup> C Mode)                             |       |

| SSPCON1 (MSSP Control 1, SPI Mode)                                          | 189   |

| SSPCON2 (MSSP Control 2, I <sup>2</sup> C Mode)                             | 199   |

| SSPSTAT (MSSP Status, I <sup>2</sup> C Mode)                                | 197   |

| SSPSTAT (MSSP Status, SPI Mode)                                             | 188   |

| Status                                                                      |       |

| STKPTR (Stack Pointer)                                                      |       |

| T0CON (Timer0 Control)                                                      | 147   |

| T1CON (Timer 1 Control)                                                     | 151   |

| T2CON (Timer 2 Control)                                                     | 157   |

| T3CON (Timer3 Control)                                                      |       |

| TRISE (PORTE/PSP Control)                                                   | 142   |

| TXBIE (Transmit Buffers Interrupt Enable)                                   | 318   |

| TXBnCON (Transmit Buffer n Control)                                         | 282   |

| TXBnDLC (Transmit Buffer n                                                  |       |

| Data Length Code)2                                                          | 285   |

| TXBnDm (Transmit Buffer n                                                   |       |

| Data Field Byte m)                                                          | 284   |

| TXBnEIDH (Transmit Buffer n Extended                                        |       |

| Identifier, High Byte)2                                                     | 283   |

| TXBnEIDL (Transmit Buffer n Extended                                        |       |

| Identifier, Low Byte)2                                                      | 284   |

| TXBnSIDH (Transmit Buffer n Standard                                        |       |

| Identifier, High Byte)2                                                     | 283   |

| TXBnSIDL (Transmit Buffer n Standard                                        |       |

| Identifier, Low Byte)                                                       | 283   |

| TXERRCNT (Transmit Error Count)                                             | 285   |

| TXSTA (Transmit Status and Control)                                         |       |

| WDTCON (Watchdog Timer Control)                                             |       |

| RESET                                                                       |       |

| Resets41, 3                                                                 |       |

| Brown-out Reset (BOR)                                                       |       |

| Oscillator Start-up Timer (OST)                                             |       |

| Power-on Reset (POR)                                                        |       |

| Power-up Timer (PWRT)                                                       |       |

| RETFIE                                                                      |       |

| RETLW                                                                       |       |

| RETURN                                                                      |       |

| Return Address Stack                                                        |       |

| and Associated Registers                                                    |       |

| Return Stack Pointer (STKPTR)                                               |       |

| Revision History                                                            |       |

|                                                                             | . • . |

| RLCF                                               | . 394<br>. 394 |

|----------------------------------------------------|----------------|

| S                                                  |                |

| SCKSDI                                             | . 187          |

| SDO                                                |                |

| SEC_IDLE Mode                                      |                |

| SEC_RUN Mode                                       |                |

| Serial Clock, SCK                                  |                |

| Serial Data Out (SDO)                              |                |

| Serial Peripheral Interface. See SPI Mode.         |                |

| SETF                                               | . 395          |

| SLEEP                                              |                |

| Sleep                                              | . 550          |

| OSC1 and OSC2 Pin States                           |                |

| Software Simulator (MPLAB SIM)                     | . 412          |

| Special Event Trigger. See Compare (ECCP1 Module). |                |

| Special Features of the CPU                        |                |

| Special Function Registers                         |                |

| Map                                                | 0-75           |

| Associated Registers                               | 105            |

| Bus Mode Compatibility                             |                |

| Effects of a Reset                                 |                |

| Enabling SPI I/O                                   |                |

| Master Mode                                        |                |

| Master/Slave Connection                            |                |

| Operation                                          | . 190          |

| Operation in Power Managed Modes                   |                |

| Serial Clock                                       |                |

| Serial Data In                                     |                |

| Serial Data Out                                    |                |

| Slave Mode                                         |                |

| Slave SelectSlave Select Synchronization           | . 107<br>103   |

| SPI Clock                                          |                |

| Typical Connection                                 |                |

| SS                                                 |                |

| SSPOV                                              |                |

| SSPOV Status Flag                                  | . 217          |

| SSPSTAT Register                                   |                |

| R/W Bit200                                         |                |

| Stack Full/Underflow Resets                        |                |

| Status Register                                    |                |

| SUBFSRSUBFWB                                       |                |

| SUBLW                                              |                |

| SUBULNK                                            |                |

| SUBWF                                              |                |

| SUBWFB                                             |                |

| SWAPF                                              | . 398          |

| Т                                                  |                |

| Table Pointer Operations (table)                   | ۵g             |

| Table Reads/Table Writes                           |                |

| TBLRD                                              |                |

| TBLWT                                              |                |

| Time-out in Various Situations (table)             |                |

|                                                    |                |

### WORLDWIDE SALES AND SERVICE

#### **AMERICAS**

**Corporate Office**

2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support:

http://support.microchip.com

Web Address: www.microchip.com

Atlanta

Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

**Boston**

Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL

Tel: 630-285-0071 Fax: 630-285-0075

Dallas

Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit

Farmington Hills, MI Tel: 248-538-2250 Fax: 248-538-2260

Kokomo

Kokomo, IN Tel: 765-864-8360 Fax: 765-864-8387

Los Angeles

Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

Santa Clara

Santa Clara, CA Tel: 408-961-6444 Fax: 408-961-6445

**Toronto**

Mississauga, Ontario, Canada

Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

**Asia Pacific Office**

Suites 3707-14, 37th Floor Tower 6, The Gateway Habour City, Kowloon Hong Kong

Tel: 852-2401-1200 Fax: 852-2401-3431

**Australia - Sydney** Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

China - Beijing

Tel: 86-10-8528-2100 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8665-5511

Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

China - Fuzhou

Tel: 86-591-8750-3506 Fax: 86-591-8750-3521

China - Hong Kong SAR

Tel: 852-2401-1200 Fax: 852-2401-3431

China - Qingdao

Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

China - Shanghai

Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

China - Shenyang

Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

China - Shenzhen

Tel: 86-755-8203-2660 Fax: 86-755-8203-1760

China - Shunde

Tel: 86-757-2839-5507 Fax: 86-757-2839-5571

China - Wuhan

Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

China - Xian

Tel: 86-29-8833-7250 Fax: 86-29-8833-7256

#### ASIA/PACIFIC

India - Bangalore

Tel: 91-80-4182-8400 Fax: 91-80-4182-8422

India - New Delhi

Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune

Tel: 91-20-2566-1512 Fax: 91-20-2566-1513

Japan - Yokohama

Tel: 81-45-471- 6166 Fax: 81-45-471-6122

Korea - Gumi

Tel: 82-54-473-4301 Fax: 82-54-473-4302

Korea - Seoul

Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

**Malaysia - Penang** Tel: 60-4-646-8870

Fax: 60-4-646-5086

Philippines - Manila

Tel: 63-2-634-9065 Fax: 63-2-634-9069

**Singapore** Tel: 65-6334-8870

Fax: 65-6334-8850 **Taiwan - Hsin Chu**Tel: 886-3-572-9526

Fax: 886-3-572-6459

**Taiwan - Kaohsiung** Tel: 886-7-536-4818 Fax: 886-7-536-4803

Taiwan - Taipei

Tel: 886-2-2500-6610 Fax: 886-2-2508-0102 Thailand - Bangkok

Tel: 66-2-694-1351 Fax: 66-2-694-1350

#### **EUROPE**

Austria - Wels

Tel: 43-7242-2244-39 Fax: 43-7242-2244-393 Denmark - Copenhagen

Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris

Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

Germany - Munich

Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

Italy - Milan

Tel: 39-0331-742611 Fax: 39-0331-466781

Netherlands - Drunen

Tel: 31-416-690399 Fax: 31-416-690340

**Spain - Madrid** Tel: 34-91-708-08-90

Fax: 34-91-708-08-91 **UK - Wokingham**

Tel: 44-118-921-5869 Fax: 44-118-921-5820

12/08/06