Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 40MHz                                                                     |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                               |

| Number of I/O              | 36                                                                        |

| Program Memory Size        | 48KB (24K x 16)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 1K x 8                                                                    |

| RAM Size                   | 3.25K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 11x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 44-TQFP                                                                   |

| Supplier Device Package    | 44-TQFP (10x10)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f4585-i-pt |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 3.1.3 CLOCK TRANSITIONS AND STATUS INDICATORS

The length of the transition between clock sources is the sum of two cycles of the old clock source and three to four cycles of the new clock source. This formula assumes that the new clock source is stable.

Three bits indicate the current clock source and its status. They are:

- OSTS (OSCCON<3>)

- IOFS (OSCCON<2>)

- T1RUN (T1CON<6>)

In general, only one of these bits will be set while in a given power managed mode. When the OSTS bit is set, the primary clock is providing the device clock. When the IOFS bit is set, the INTOSC output is providing a stable 8 MHz clock source to a divider that actually drives the device clock. When the T1RUN bit is set, the Timer1 oscillator is providing the clock. If none of these bits are set, then either the INTRC clock source is clocking the device, or the INTOSC source is not yet stable.

If the internal oscillator block is configured as the primary clock source by the FOSC3:FOSC0 Configuration bits, then both the OSTS and IOFS bits may be set when in PRI\_RUN or PRI\_IDLE modes. This indicates that the primary clock (INTOSC output) is generating a stable 8 MHz output. Entering another RC power managed mode at the same frequency would clear the OSTS bit.

- Note 1: Caution should be used when modifying a single IRCF bit. If VDD is less than 3V, it is possible to select a higher clock speed than is supported by the low VDD. Improper device operation may result if the VDD/FOSC specifications are violated.

- 2: Executing a SLEEP instruction does not necessarily place the device into Sleep mode. It acts as the trigger to place the controller into either the Sleep mode or one of the Idle modes, depending on the setting of the IDLEN bit.

### 3.1.4 MULTIPLE SLEEP COMMANDS

The power managed mode that is invoked with the SLEEP instruction is determined by the setting of the IDLEN bit at the time the instruction is executed. If another SLEEP instruction is executed, the device will enter the power managed mode specified by IDLEN at that time. If IDLEN has changed, the device will enter the new power managed mode specified by the new setting.

# 3.2 Run Modes

In the Run modes, clocks to both the core and peripherals are active. The difference between these modes is the clock source.

# 3.2.1 PRI\_RUN MODE

The PRI\_RUN mode is the normal, full power execution mode of the microcontroller. This is also the default mode upon a device Reset, unless Two-Speed Start-up is enabled (see **Section 24.3 "Two-Speed Start-up"** for details). In this mode, the OSTS bit is set. The IOFS bit may be set if the internal oscillator block is the primary clock source (see **Section 2.7.1 "Oscillator Control Register"**).

## 3.2.2 SEC\_RUN MODE

The SEC\_RUN mode is the compatible mode to the "clock switching" feature offered in other PIC18 devices. In this mode, the CPU and peripherals are clocked from the Timer1 oscillator. This gives users the option of lower power consumption while still using a high accuracy clock source.

SEC\_RUN mode is entered by setting the SCS1:SCS0 bits to '01'. The device clock source is switched to the Timer1 oscillator (see Figure 3-1), the primary oscillator is shut down, the T1RUN bit (T1CON<6>) is set and the OSTS bit is cleared.

Note: The Timer1 oscillator should already be running prior to entering SEC\_RUN mode. If the T1OSCEN bit is not set when the SCS1:SCS0 bits are set to '01', entry to SEC\_RUN mode will not occur. If the Timer1 oscillator is enabled but not yet running, device clocks will be delayed until the oscillator has started. In such situations, initial oscillator operation is far from stable and unpredictable operation may result.

On transitions from SEC\_RUN mode to PRI\_RUN, the peripherals and CPU continue to be clocked from the Timer1 oscillator while the primary clock is started. When the primary clock becomes ready, a clock switch back to the primary clock occurs (see Figure 3-2). When the clock switch is complete, the T1RUN bit is cleared, the OSTS bit is set and the primary clock is providing the clock. The IDLEN and SCS bits are not affected by the wake-up; the Timer1 oscillator continues to run.

# 4.5 Device Reset Timers

PIC18F2585/2680/4585/4680 devices incorporate three separate on-chip timers that help regulate the Power-on Reset process. Their main function is to ensure that the device clock is stable before code is executed. These timers are:

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- PLL Lock Time-out

#### 4.5.1 POWER-UP TIMER (PWRT)

The Power-up Timer (PWRT) of PIC18F2585/2680/ 4585/4680 devices is an 11-bit counter which uses the INTRC source as the clock input. This yields an approximate time interval of 2048 x 32  $\mu$ s = 65.6 ms. While the PWRT is counting, the device is held in Reset.

The power-up time delay depends on the INTRC clock and will vary from chip to chip due to temperature and process variation. See DC parameter 33 for details.

The PWRT is enabled by clearing the PWRTEN Configuration bit.

#### 4.5.2 OSCILLATOR START-UP TIMER (OST)

The Oscillator Start-up Timer (OST) provides a 1024 oscillator cycle (from OSC1 input) delay after the PWRT delay is over (parameter 33). This ensures that the crystal oscillator or resonator has started and stabilized.

The OST time-out is invoked only for XT, LP, HS and HSPLL modes and only on Power-on Reset or on exit from most power managed modes.

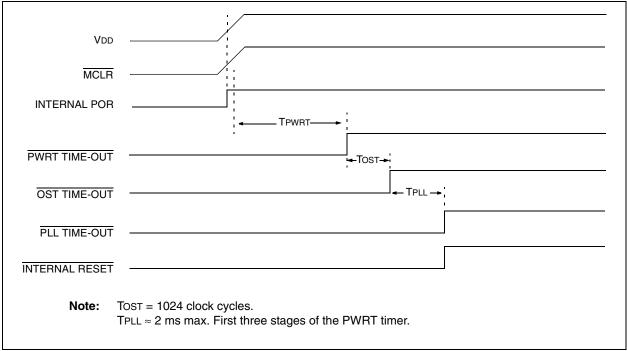

### 4.5.3 PLL LOCK TIME-OUT

With the PLL enabled in its PLL mode, the time-out sequence following a Power-on Reset is slightly different from other oscillator modes. A separate timer is used to provide a fixed time-out that is sufficient for the PLL to lock to the main oscillator frequency. This PLL lock time-out (TPLL) is typically 2 ms and follows the oscillator start-up time-out.

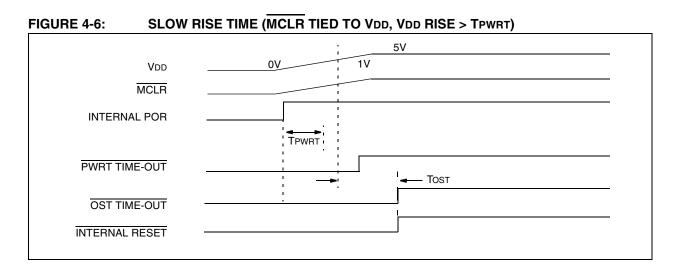

#### 4.5.4 TIME-OUT SEQUENCE

On power-up, the time-out sequence is as follows:

- 1. After the POR pulse has cleared, PWRT time-out is invoked (if enabled).

- 2. Then, the OST is activated.

The total time-out will vary based on oscillator configuration and the status of the PWRT. Figure 4-3, Figure 4-4, Figure 4-5, Figure 4-6 and Figure 4-7 all depict time-out sequences on power-up, with the Power-up Timer enabled and the device operating in HS Oscillator mode. Figures 4-3 through 4-6 also apply to devices operating in XT or LP modes. For devices in RC mode and with the PWRT disabled, on the other hand, there will be no time-out at all.

Since the time-outs occur from the POR pulse, if  $\overline{\text{MCLR}}$  is kept low long enough, all time-outs will expire. Bringing  $\overline{\text{MCLR}}$  high will begin execution immediately (Figure 4-5). This is useful for testing purposes or to synchronize more than one PIC18FXXXX device operating in parallel.

| Oscillator     | Power-up <sup>(2)</sup> an                             | Exit from                       |                                 |

|----------------|--------------------------------------------------------|---------------------------------|---------------------------------|

| Configuration  | <b>PWRTEN</b> = 0                                      | <b>PWRTEN</b> = 1               | Power Managed Mode              |

| HSPLL          | 66 ms <sup>(1)</sup> + 1024 Tosc + 2 ms <sup>(2)</sup> | 1024 Tosc + 2 ms <sup>(2)</sup> | 1024 Tosc + 2 ms <sup>(2)</sup> |

| HS, XT, LP     | 66 ms <sup>(1)</sup> + 1024 Tosc                       | 1024 Tosc                       | 1024 Tosc                       |

| EC, ECIO       | 66 ms <sup>(1)</sup>                                   | _                               | _                               |

| RC, RCIO       | 66 ms <sup>(1)</sup>                                   | _                               | —                               |

| INTIO1, INTIO2 | 66 ms <sup>(1)</sup>                                   | _                               | _                               |

TABLE 4-2:TIME-OUT IN VARIOUS SITUATIONS

**Note 1:** 66 ms (65.5 ms) is the nominal Power-up Timer (PWRT) delay.

2: 2 ms is the nominal time required for the PLL to lock.

# PIC18F2585/2680/4585/4680

© 2007 Microchip Technology Inc.

| <b>TABLE 5-1:</b> | SPECIAL FUNCTION REGISTER MAP FOR             |

|-------------------|-----------------------------------------------|

|                   | PIC18F2585/2680/4585/4680 DEVICES (CONTINUED) |

| D7Fh —<br>D7Eh —<br>D7Eh —<br>D7Dh —<br>D7Ch —<br>D7Ch —<br>D7Bh RXF11EIDL<br>D7Ah RXF11EIDH<br>D7Ah RXF11EIDH<br>D79h RXF11SIDL<br>D78h RXF11SIDH<br>D77h RXF10EIDL<br>D76h RXF10EIDH<br>D75h RXF10SIDL<br>D74h RXF10SIDL<br>D74h RXF9EIDL<br>D72h RXF9EIDL<br>D72h RXF9EIDH<br>D71h RXF9SIDL<br>D72h RXF9SIDL<br>D70h RXF9SIDL<br>D70h RXF9SIDL<br>D6Eh —<br>D6Eh —<br>D6Eh —<br>D6Bh RXF8SIDL<br>D6Ah RXF8SIDL<br>D6Ah RXF8SIDL<br>D68h RXF8SIDL<br>D68h RXF8SIDL<br>D68h RXF8SIDL<br>D66h RXF7SIDL<br>D66h RXF7SIDL<br>D61h RXF6SIDL | Address | Name      |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----------|--|--|--|--|--|

| D7Dh —<br>D7Ch —<br>D7Bh RXF11EIDL<br>D7Ah RXF11EIDL<br>D7Ah RXF11EIDH<br>D79h RXF11SIDL<br>D78h RXF11SIDH<br>D77h RXF10EIDL<br>D76h RXF10EIDH<br>D75h RXF10SIDL<br>D74h RXF10SIDH<br>D73h RXF9EIDL<br>D72h RXF9EIDL<br>D72h RXF9EIDH<br>D71h RXF9SIDL<br>D72h RXF9SIDH<br>D6Fh —<br>D6Eh —<br>D6Eh —<br>D6Ch —<br>D6Bh RXF8SIDH<br>D6Ah RXF8EIDL<br>D6Ah RXF8EIDH<br>D69h RXF8SIDL<br>D68h RXF8SIDL<br>D68h RXF8SIDL<br>D68h RXF8SIDL<br>D66h RXF7EIDL<br>D66h RXF7EIDL<br>D66h RXF7SIDL<br>D66h RXF7SIDL<br>D66h RXF7SIDL<br>D66h RXF7SIDL<br>D66h RXF7SIDL                                                                                                                                                      | D7Fh    |           |  |  |  |  |  |

| D7Ch —<br>D7Bh RXF11EIDL<br>D7Ah RXF11EIDH<br>D79h RXF11SIDL<br>D78h RXF11SIDL<br>D78h RXF11SIDH<br>D77h RXF10EIDL<br>D76h RXF10EIDH<br>D75h RXF10SIDL<br>D74h RXF10SIDH<br>D73h RXF9EIDL<br>D72h RXF9EIDL<br>D72h RXF9EIDH<br>D71h RXF9SIDL<br>D70h RXF9SIDL<br>D6Fh —<br>D6Eh —<br>D6Eh —<br>D6Bh RXF8EIDL<br>D6Ah RXF8EIDL<br>D6Ah RXF8EIDL<br>D68h RXF8SIDL<br>D68h RXF8SIDL<br>D68h RXF8SIDL<br>D68h RXF8SIDL<br>D68h RXF8SIDL<br>D68h RXF7EIDH<br>D65h RXF7SIDL<br>D66h RXF7EIDL<br>D66h RXF7SIDL<br>D66h RXF7SIDL<br>D66h RXF7SIDL                                                                                                                                                                          | D7Eh    | -         |  |  |  |  |  |

| D7BhRXF11EIDLD7AhRXF11EIDHD7AhRXF11SIDLD79hRXF11SIDLD78hRXF11SIDHD77hRXF10EIDLD76hRXF10EIDHD75hRXF10SIDLD74hRXF9EIDLD74hRXF9SIDHD72hRXF9SIDLD70hRXF9SIDLD70hRXF9SIDLD6EhD6BhRXF8EIDLD6AhRXF8EIDLD6AhRXF8SIDLD6AhRXF8SIDLD6AhRXF8SIDLD6AhRXF8SIDLD6AhRXF7SIDLD6AhRXF78SIDLD6AhRXF78SIDLD6AhRXF78SIDLD6AhRXF78SIDLD6AhRXF78SIDLD6AhRXF78SIDLD6AhRXF78SIDLD6AhRXF78SIDLD6AhRXF78SIDLD6AhRXF78SIDLD6AhRXF78SIDLD6AhRXF78SIDLD6AhRXF78SIDLD6AhRXF78SIDLD6AhRXF78SIDLD6AhRXF78SIDLD6AhRXF78SIDLD6AhRXF78SIDLD6AhRXF78SIDLD6AhRXF6EIDLD6AhRXF6EIDLD6AhRXF6EIDLD6AhRXF6EIDLD6AhRXF6EIDLD6AhRXF6EIDLD6AhRXF6EIDLD6AhRXF6EIDLD6AhRXF6EIDLD6AhRXF6EIDLD6AhRXF6EIDLD6AhRXF6EID                                                 | D7Dh    | -         |  |  |  |  |  |

| D7Ah RXF11EIDH<br>D79h RXF11SIDL<br>D78h RXF11SIDL<br>D78h RXF10EIDL<br>D77h RXF10EIDL<br>D76h RXF10EIDH<br>D75h RXF10SIDL<br>D74h RXF10SIDH<br>D73h RXF9EIDL<br>D72h RXF9EIDL<br>D72h RXF9EIDH<br>D71h RXF9SIDL<br>D70h RXF9SIDL<br>D70h RXF9SIDH<br>D6Fh —<br>D6Eh —<br>D6Eh —<br>D6Bh RXF8SIDL<br>D6Ah RXF8EIDL<br>D6Ah RXF8EIDL<br>D68h RXF8SIDL<br>D68h RXF8SIDL<br>D68h RXF7EIDL<br>D66h RXF7EIDL<br>D66h RXF7SIDL<br>D66h RXF7SIDL<br>D66h RXF7SIDL<br>D64h RXF7SIDL<br>D64h RXF7SIDL<br>D64h RXF6EIDL<br>D62h RXF6EIDL                                                                                                                                                                                     | D7Ch    | _         |  |  |  |  |  |

| D79hRXF11SIDLD78hRXF11SIDHD77hRXF10EIDLD77hRXF10EIDLD76hRXF10SIDLD75hRXF10SIDLD74hRXF9EIDLD73hRXF9EIDLD72hRXF9SIDLD71hRXF9SIDLD70hRXF9SIDHD6EhD6BhRXF8EIDLD6AhRXF8EIDLD6AhRXF8SIDLD6AhRXF8SIDLD6AhRXF8SIDLD6AhRXF78IDLD6AhRXF78IDLD6AhRXF78IDLD6AhRXF78IDLD6AhRXF75IDLD6AhRXF75IDLD6AhRXF75IDLD6AhRXF75IDLD6AhRXF75IDLD6AhRXF75IDLD6AhRXF75IDLD6AhRXF75IDLD6AhRXF75IDLD6AhRXF6EIDLD6AhRXF6EIDLD6AhRXF6EIDLD6AhRXF6EIDL                                                                                                                                                                                                                                                                                             | D7Bh    | RXF11EIDL |  |  |  |  |  |

| D78hRXF11SIDHD77hRXF10EIDLD77hRXF10EIDLD76hRXF10SIDLD75hRXF10SIDLD74hRXF10SIDHD73hRXF9EIDLD72hRXF9EIDHD71hRXF9SIDLD70hRXF9SIDLD70hRXF9SIDLD6EhD6ChD6BhRXF8EIDLD6AhRXF8EIDLD6AhRXF8EIDLD6AhRXF8EIDLD6AhRXF8SIDLD6AhRXF8SIDLD6AhRXF78IDLD6AhRXF78IDLD6AhRXF78IDLD6AhRXF75IDLD6AhRXF75IDLD6AhRXF75IDLD6AhRXF75IDLD6AhRXF75IDLD6AhRXF75IDLD6AhRXF75IDLD6AhRXF75IDLD6AhRXF6EIDLD6AhRXF6EIDLD6AhRXF6EIDLD6AhRXF6EIDL                                                                                                                                                                                                                                                                                                     | D7Ah    | RXF11EIDH |  |  |  |  |  |

| D77h RXF10EIDL<br>D76h RXF10EIDH<br>D75h RXF10SIDL<br>D74h RXF10SIDH<br>D73h RXF9EIDL<br>D72h RXF9EIDL<br>D72h RXF9SIDL<br>D70h RXF9SIDH<br>D6Fh —<br>D6Eh —<br>D6Eh —<br>D6Ch —<br>D6Ch —<br>D6Bh RXF8EIDL<br>D6Ah RXF8EIDL<br>D6Ah RXF8SIDL<br>D6Ah RXF8SIDL<br>D68h RXF8SIDL<br>D66h RXF7EIDH<br>D67h RXF7EIDH<br>D65h RXF7SIDL<br>D66h RXF7SIDL<br>D66h RXF7SIDL<br>D66h RXF7SIDL<br>D66h RXF7SIDL<br>D66h RXF7SIDL<br>D66h RXF7SIDL<br>D61h RXF6EIDH                                                                                                                                                                                                                                                          | D79h    | RXF11SIDL |  |  |  |  |  |

| D76hRXF10EIDHD75hRXF10SIDLD74hRXF10SIDHD74hRXF9EIDLD72hRXF9EIDHD72hRXF9SIDHD71hRXF9SIDHD70hRXF9SIDHD6FhD6ChD6ChD6BhRXF8EIDLD6AhRXF8SIDLD69hRXF8SIDLD68hRXF8SIDLD66hRXF8SIDLD66hRXF78IDLD66hRXF75IDLD66hRXF75IDLD66hRXF75IDLD66hRXF75IDLD64hRXF6EIDLD63hRXF6EIDLD63hRXF6EIDLD61hRXF6SIDL                                                                                                                                                                                                                                                                                                                                                                                                                            | D78h    | RXF11SIDH |  |  |  |  |  |

| D75hRXF10SIDLD74hRXF10SIDHD74hRXF9EIDLD73hRXF9EIDLD72hRXF9SIDLD71hRXF9SIDLD70hRXF9SIDHD6FhD6EhD6ChD6BhRXF8EIDLD6AhRXF8EIDLD68hRXF8SIDLD68hRXF8SIDLD68hRXF8SIDLD68hRXF8SIDLD68hRXF78IDLD68hRXF75IDLD66hRXF75IDLD66hRXF75IDLD64hRXF6EIDLD62hRXF6EIDLD61hRXF6SIDL                                                                                                                                                                                                                                                                                                                                                                                                                                                     | D77h    | RXF10EIDL |  |  |  |  |  |

| D74hRXF10SIDHD73hRXF9EIDLD72hRXF9EIDHD72hRXF9SIDLD71hRXF9SIDLD70hRXF9SIDHD6FhD6EhD6DhD6ChD6BhRXF8EIDLD6AhRXF8EIDLD6AhRXF8SIDLD6AhRXF8SIDLD6AhRXF8SIDLD6AhRXF78IDLD6AhRXF78IDLD6AhRXF75IDLD6AhRXF75IDLD6AhRXF75IDLD6AhRXF75IDLD6AhRXF75IDLD6AhRXF6EIDLD63hRXF6EIDLD63hRXF6EIDLD61hRXF6SIDL                                                                                                                                                                                                                                                                                                                                                                                                                          | D76h    | RXF10EIDH |  |  |  |  |  |

| D73hRXF9EIDLD72hRXF9EIDHD72hRXF9EIDHD71hRXF9SIDLD70hRXF9SIDHD6FhD6EhD6ChD6ChD6BhRXF8EIDLD6AhRXF8EIDHD6AhRXF8SIDLD6AhRXF8SIDLD6AhRXF8SIDLD6AhRXF8SIDLD6AhRXF7SIDLD6AhRXF7EIDHD65hRXF7SIDLD64hRXF7SIDLD64hRXF6EIDLD62hRXF6EIDLD61hRXF6SIDL                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | D75h    | RXF10SIDL |  |  |  |  |  |

| D72h RXF9EIDH<br>D71h RXF9SIDL<br>D70h RXF9SIDH<br>D6Fh —<br>D6Eh —<br>D6Dh —<br>D6Ch —<br>D6Bh RXF8EIDL<br>D6Ah RXF8EIDL<br>D6Ah RXF8EIDH<br>D69h RXF8SIDL<br>D68h RXF8SIDH<br>D67h RXF7EIDL<br>D66h RXF7EIDL<br>D66h RXF7EIDH<br>D65h RXF7SIDL<br>D64h RXF7SIDL<br>D64h RXF7SIDL<br>D64h RXF6EIDL<br>D62h RXF6EIDL                                                                                                                                                                                                                                                                                                                                                                                               | D74h    | RXF10SIDH |  |  |  |  |  |

| D71hRXF9SIDLD70hRXF9SIDHD6FhD6EhD6DhD6ChD6BhRXF8EIDLD6AhRXF8EIDHD69hRXF8SIDLD68hRXF8SIDLD68hRXF8SIDLD69hRXF78IDLD68hRXF75IDLD66hRXF75IDLD66hRXF75IDLD64hRXF7SIDLD64hRXF6EIDLD62hRXF6EIDLD61hRXF6SIDL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | D73h    | RXF9EIDL  |  |  |  |  |  |

| D70h RXF9SIDH<br>D6Fh —<br>D6Eh —<br>D6Dh —<br>D6Ch —<br>D6Ch —<br>D6Bh RXF8EIDL<br>D6Ah RXF8EIDH<br>D69h RXF8SIDL<br>D69h RXF8SIDL<br>D69h RXF8SIDL<br>D69h RXF7SIDL<br>D66h RXF7EIDH<br>D65h RXF7SIDL<br>D64h RXF7SIDL<br>D64h RXF7SIDL<br>D64h RXF6EIDL<br>D62h RXF6EIDH<br>D61h RXF6SIDL                                                                                                                                                                                                                                                                                                                                                                                                                       | D72h    | RXF9EIDH  |  |  |  |  |  |

| D6Fh —<br>D6Eh —<br>D6Dh —<br>D6Dh —<br>D6Ch —<br>D6Bh RXF8EIDL<br>D6Ah RXF8EIDH<br>D69h RXF8SIDL<br>D68h RXF8SIDH<br>D69h RXF8SIDH<br>D67h RXF7EIDL<br>D66h RXF7EIDH<br>D65h RXF7SIDL<br>D64h RXF7SIDL<br>D64h RXF7SIDH<br>D63h RXF6EIDL<br>D62h RXF6EIDH<br>D61h RXF6SIDL                                                                                                                                                                                                                                                                                                                                                                                                                                        | D71h    | RXF9SIDL  |  |  |  |  |  |

| D6Eh —<br>D6Dh —<br>D6Dh —<br>D6Ch —<br>D6Bh RXF8EIDL<br>D6Ah RXF8EIDH<br>D69h RXF8SIDL<br>D69h RXF8SIDH<br>D69h RXF8SIDH<br>D67h RXF7EIDL<br>D66h RXF7EIDH<br>D65h RXF7SIDL<br>D64h RXF7SIDL<br>D64h RXF6EIDL<br>D62h RXF6EIDH<br>D61h RXF6SIDL                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | D70h    | RXF9SIDH  |  |  |  |  |  |

| D6Dh —<br>D6Ch —<br>D6Bh RXF8EIDL<br>D6Ah RXF8EIDH<br>D69h RXF8SIDL<br>D68h RXF8SIDL<br>D68h RXF8SIDH<br>D67h RXF7EIDL<br>D66h RXF7EIDH<br>D65h RXF7SIDL<br>D64h RXF7SIDL<br>D64h RXF7SIDH<br>D63h RXF6EIDL<br>D62h RXF6EIDH<br>D61h RXF6SIDL                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | D6Fh    | _         |  |  |  |  |  |

| D6Ch —<br>D6Bh RXF8EIDL<br>D6Ah RXF8EIDH<br>D69h RXF8SIDL<br>D68h RXF8SIDL<br>D68h RXF8SIDH<br>D67h RXF7EIDL<br>D66h RXF7EIDH<br>D65h RXF7SIDL<br>D64h RXF7SIDL<br>D64h RXF6EIDL<br>D62h RXF6EIDH<br>D61h RXF6SIDL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | D6Eh    | _         |  |  |  |  |  |

| D6BhRXF8EIDLD6AhRXF8EIDHD69hRXF8SIDLD69hRXF8SIDLD67hRXF7EIDLD66hRXF7EIDHD65hRXF7SIDLD64hRXF7SIDLD63hRXF6EIDLD62hRXF6EIDHD61hRXF6SIDL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | D6Dh    | _         |  |  |  |  |  |

| D6Ah RXF8EIDH<br>D69h RXF8SIDL<br>D68h RXF8SIDH<br>D67h RXF7EIDL<br>D66h RXF7EIDH<br>D65h RXF7SIDL<br>D64h RXF7SIDH<br>D63h RXF6EIDL<br>D62h RXF6EIDH<br>D61h RXF6SIDL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | D6Ch    | —         |  |  |  |  |  |

| D69hRXF8SIDLD68hRXF8SIDHD67hRXF7EIDLD66hRXF7EIDHD65hRXF7SIDLD64hRXF7SIDHD63hRXF6EIDLD62hRXF6EIDHD61hRXF6SIDL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | D6Bh    | RXF8EIDL  |  |  |  |  |  |

| D68hRXF8SIDHD67hRXF7EIDLD66hRXF7EIDHD65hRXF7SIDLD64hRXF7SIDHD63hRXF6EIDLD62hRXF6EIDHD61hRXF6SIDL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | D6Ah    | RXF8EIDH  |  |  |  |  |  |

| D67hRXF7EIDLD66hRXF7EIDHD65hRXF7SIDLD64hRXF7SIDHD63hRXF6EIDLD62hRXF6EIDHD61hRXF6SIDL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | D69h    | RXF8SIDL  |  |  |  |  |  |

| D66hRXF7EIDHD65hRXF7SIDLD64hRXF7SIDHD63hRXF6EIDLD62hRXF6EIDHD61hRXF6SIDL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | D68h    | RXF8SIDH  |  |  |  |  |  |

| D65hRXF7SIDLD64hRXF7SIDHD63hRXF6EIDLD62hRXF6EIDHD61hRXF6SIDL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | D67h    | RXF7EIDL  |  |  |  |  |  |

| D64hRXF7SIDHD63hRXF6EIDLD62hRXF6EIDHD61hRXF6SIDL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | D66h    | RXF7EIDH  |  |  |  |  |  |

| D63h RXF6EIDL<br>D62h RXF6EIDH<br>D61h RXF6SIDL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | D65h    | RXF7SIDL  |  |  |  |  |  |

| D62h RXF6EIDH<br>D61h RXF6SIDL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | D64h    | RXF7SIDH  |  |  |  |  |  |

| D61h RXF6SIDL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | D63h    | RXF6EIDL  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | D62h    | RXF6EIDH  |  |  |  |  |  |

| D60h RXF6SIDH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | D61h    | RXF6SIDL  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | D60h    | RXF6SIDH  |  |  |  |  |  |

Note 1: Registers available only on PIC18F4X8X devices; otherwise, the registers read as '0'.

2: When any TX\_ENn bit in RX\_TX\_SELn is set, then the corresponding bit in this register has transmit properties.

3: This is not a physical register.

| File Name | Bit 7                          | Bit 6                                                    | Bit 5         | Bit 4         | Bit 3         | Bit 2           | Bit 1            | Bit 0        | Value on POR, BOR | Details<br>on page: |

|-----------|--------------------------------|----------------------------------------------------------|---------------|---------------|---------------|-----------------|------------------|--------------|-------------------|---------------------|

| TOSU      | _                              | _                                                        | _             | Top-of-Stack  | Upper Byte (  | FOS<20:16>)     |                  |              | 0 0000            | 49, 62              |

| TOSH      | Top-of-Stack I                 | High Byte (TO                                            | S<15:8>)      |               |               |                 |                  |              | 0000 0000         | 49, 62              |

| TOSL      | Top-of-Stack I                 | Low Byte (TOS                                            | S<7:0>)       |               |               |                 |                  |              | 0000 0000         | 49, 62              |

| STKPTR    | STKFUL                         | STKUNF                                                   | —             | Return Stack  | Pointer       |                 |                  |              | 00-0 0000         | 49, 63              |

| PCLATU    | _                              | — — bit 21 <sup>(1)</sup> Holding Register for PC<20:16> |               |               |               |                 |                  |              | 0 0000            | 49, 62              |

| PCLATH    | Holding Regis                  | ster for PC<15                                           | :8>           |               |               |                 |                  |              | 0000 0000         | 49, 62              |

| PCL       | PC Low Byte                    | (PC<7:0>)                                                |               |               |               |                 |                  |              | 0000 0000         | 49, 62              |

| TBLPTRU   | —                              | —                                                        | bit 21        | Program Me    | mory Table Po | ointer Upper By | te (TBLPTR<2     | 0:16>)       | 00 0000           | 49, 103             |

| TBLPTRH   | Program Men                    | nory Table Poi                                           | nter High Byt | te (TBLPTR<1  | 5:8>)         |                 |                  |              | 0000 0000         | 49, 103             |

| TBLPTRL   | Program Men                    | nory Table Poi                                           | nter Low Byte | e (TBLPTR<7   | :0>)          |                 |                  |              | 0000 0000         | 49, 103             |

| TABLAT    | Program Men                    | nory Table Late                                          | ch            |               |               |                 |                  |              | 0000 0000         | 49, 103             |

| PRODH     | Product Regis                  | ster High Byte                                           |               |               |               |                 |                  |              | xxxx xxxx         | 49, 111             |

| PRODL     | Product Regis                  | ster Low Byte                                            |               |               |               |                 |                  |              | xxxx xxxx         | 49, 111             |

| INTCON    | GIE/GIEH                       | PEIE/GIEL                                                | TMR0IE        | <b>INTOIE</b> | RBIE          | TMR0IF          | INTOIF           | RBIF         | 0000 000x         | 49, 115             |

| INTCON2   | RBPU                           | INTEDG0                                                  | INTEDG1       | INTEDG2       | _             | TMR0IP          | _                | RBIP         | 1111 -1-1         | 49, 116             |

| INTCON3   | INT2IP                         | INT1IP                                                   | _             | INT2IE        | INT1IE        | _               | INT2IF           | INT1IF       | 11-0 0-00         | 49, 117             |

| INDF0     | Uses contents                  | s of FSR0 to a                                           | ddress data   | memory - valu | ue of FSR0 no | t changed (not  | a physical reg   | ister)       | N/A               | 49, 89              |

| POSTINC0  | Uses contents                  | s of FSR0 to a                                           | ddress data   | memory – valı | ue of FSR0 po | st-incremented  | (not a physica   | al register) | N/A               | 49, 90              |

| POSTDEC0  | Uses contents                  | s of FSR0 to a                                           | ddress data   | memory – valı | ue of FSR0 po | st-decremente   | d (not a physic  | al register) | N/A               | 49, 90              |

| PREINC0   | Uses contents                  | s of FSR0 to a                                           | ddress data   | memory – valı | ue of FSR0 pr | e-incremented   | (not a physical  | register)    | N/A               | 49, 90              |

| PLUSW0    | Uses contents<br>value of FSR  |                                                          | ddress data   | memory – valı | ue of FSR0 pr | e-incremented   | (not a physical  | register),   | N/A               | 49, 90              |

| FSR0H     | _                              | _                                                        | _             | _             | Indirect Data | Memory Addre    | ss Pointer 0 H   | igh          | xxxx              | 49, 89              |

| FSR0L     | Indirect Data                  | Memory Addre                                             | ess Pointer 0 | Low Byte      |               |                 |                  |              | XXXX XXXX         | 49, 89              |

| WREG      | Working Regi                   | ster                                                     |               |               |               |                 |                  |              | xxxx xxxx         | 49                  |

| INDF1     | Uses contents                  | s of FSR1 to a                                           | ddress data   | memory – valı | ue of FSR1 no | t changed (not  | a physical reg   | ister)       | N/A               | 49, 89              |

| POSTINC1  | Uses contents                  | s of FSR1 to a                                           | ddress data   | memory – valı | ue of FSR1 po | st-incremented  | l (not a physica | al register) | N/A               | 49, 90              |

| POSTDEC1  | Uses contents                  | s of FSR1 to a                                           | ddress data   | memory – valı | ue of FSR1 po | st-decremente   | d (not a physic  | al register) | N/A               | 49, 90              |

| PREINC1   | Uses contents                  | s of FSR1 to a                                           | ddress data   | memory – valı | ue of FSR1 pr | e-incremented   | (not a physical  | register)    | N/A               | 49, 90              |

| PLUSW1    | Uses contents<br>value of FSR  |                                                          | ddress data   | memory – valı | ue of FSR1 pr | e-incremented   | (not a physical  | register),   | N/A               | 49, 90              |

| FSR1H     | _                              | _                                                        | _             | _             | Indirect Data | Memory Addre    | ss Pointer 1 H   | igh          | xxxx              | 49, 89              |

| FSR1L     | Indirect Data                  | Memory Addre                                             | ess Pointer 1 | Low Byte      |               |                 |                  |              | xxxx xxxx         | 49, 89              |

| BSR       | _                              | _                                                        | _             | _             | Bank Select   | Register        |                  |              | 0000              | 50, 67              |

| INDF2     | Uses contents                  | s of FSR2 to a                                           | ddress data   | memory – valı | ue of FSR2 no | t changed (not  | a physical reg   | ister)       | N/A               | 50, 89              |

| POSTINC2  | Uses contents                  | s of FSR2 to a                                           | ddress data   | memory – valı | ue of FSR2 pc | st-incremented  | l (not a physica | al register) | N/A               | 50, 90              |

| POSTDEC2  | Uses contents                  | s of FSR2 to a                                           | ddress data   | memory – valı | ue of FSR2 pc | st-decremente   | d (not a physic  | al register) | N/A               | 50, 90              |

| PREINC2   | Uses contents                  | s of FSR2 to a                                           | ddress data   | memory – valı | ue of FSR2 pr | e-incremented   | (not a physical  | register)    | N/A               | 50, 90              |

| PLUSW2    | Uses contents<br>value of FSR2 |                                                          | ddress data   | memory – valı | ue of FSR2 pr | e-incremented   | (not a physical  | register),   | N/A               | 50, 90              |

| FSR2H     | _                              | _                                                        | _             | _             | Indirect Data | Memory Addre    | ss Pointer 2 H   | igh          | xxxx              | 50, 89              |

| FSR2L     | Indirect Data                  | Memory Addre                                             | ess Pointer 2 | Low Byte      |               |                 |                  |              | xxxx xxxx         | 50, 89              |

#### TABLE 5-2: REGISTER FILE SUMMARY (PIC18F2585/2680/4585/4680)

**Note 1:** Bit 21 of the PC is only available in Test mode and Serial Programming modes.

2: The SBOREN bit is only available when CONFIG2L<1:0> = 01; otherwise, it is disabled and reads as '0'. See Section 4.4 "Brown-out Reset (BOR)".

3: These registers and/or bits are not implemented on PIC18F2X8X devices and are read as '0'. Reset values are shown for PIC18F4X8X devices; individual unimplemented bits should be interpreted as '--'.

4: The PLLEN bit is only available in specific oscillator configuration; otherwise, it is disabled and reads as '0'. See Section 2.6.4 "PLL in INTOSC Modes".

5: The RE3 bit is only available when Master Clear Reset is disabled (CONFIG3H<7> = 0); otherwise, RE3 reads as '0'. This bit is read-only.

6: RA6/RA7 and their associated latch and direction bits are individually configured as port pins based on various primary oscillator modes. When disabled, these bits read as '0'.

7: CAN bits have multiple functions depending on the selected mode of the CAN module.

8: This register reads all '0's until the ECAN™ technology is set up in Mode 1 or Mode 2.

9: These registers are available on PIC18F4X8X devices only.

# 9.0 INTERRUPTS

The PIC18F2585/2680/4585/4680 devices have multiple interrupt sources and an interrupt priority feature that allows each interrupt source to be assigned a high priority level or a low priority level. The high priority interrupt vector is at 000008h and the low priority interrupt vector is at 000018h. High priority interrupt events will interrupt any low priority interrupts that may be in progress.

There are ten registers which are used to control interrupt operation. These registers are:

- RCON

- INTCON

- INTCON2

- INTCON3

- PIR1, PIR2, PIR3

- PIE1, PIE2, PIE3

- IPR1, IPR2, IPR3

It is recommended that the Microchip header files supplied with MPLAB<sup>®</sup> IDE be used for the symbolic bit names in these registers. This allows the assembler/ compiler to automatically take care of the placement of these bits within the specified register.

Each interrupt source has three bits to control its operation. The functions of these bits are:

- Flag bit to indicate that an interrupt event occurred

- Enable bit that allows program execution to branch to the interrupt vector address when the flag bit is set

- Priority bit to select high priority or low priority

The interrupt priority feature is enabled by setting the IPEN bit (RCON<7>). When interrupt priority is enabled, there are two bits which enable interrupts globally. Setting the GIEH bit (INTCON<7>) enables all interrupts that have the priority bit set (high priority). Setting the GIEL bit (INTCON<6>) enables all interrupts that have the priority bit cleared (low priority). When the interrupt flag, enable bit and appropriate global interrupt enable bit are set, the interrupt will vector immediately to address 000008h or 000018h, depending on the priority bit setting. Individual interrupts can be disabled through their corresponding enable bits.

When the IPEN bit is cleared (default state), the interrupt priority feature is disabled and interrupts are compatible with PIC<sup>®</sup> mid-range devices. In Compatibility mode, the interrupt priority bits for each source have no effect. INTCON<6> is the PEIE bit, which enables/ disables all peripheral interrupt sources. INTCON<7> is the GIE bit, which enables/disables all interrupt sources. All interrupts branch to address 000008h in Compatibility mode.

When an interrupt is responded to, the global interrupt enable bit is cleared to disable further interrupts. If the IPEN bit is cleared, this is the GIE bit. If interrupt priority levels are used, this will be either the GIEH or GIEL bit. High priority interrupt sources can interrupt a low priority interrupt. Low priority interrupts are not processed while high priority interrupts are in progress.

The return address is pushed onto the stack and the PC is loaded with the interrupt vector address (000008h or 000018h). Once in the Interrupt Service Routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bits must be cleared in software before re-enabling interrupts to avoid recursive interrupts.

The "return from interrupt" instruction, RETFIE, exits the interrupt routine and sets the GIE bit (GIEH or GIEL if priority levels are used), which re-enables interrupts.

For external interrupt events, such as the INT pins or the PORTB input change interrupt, the interrupt latency will be three to four instruction cycles. The exact latency is the same for one or two-cycle instructions. Individual interrupt flag bits are set, regardless of the status of their corresponding enable bit or the GIE bit.

**Note:** Do not use the MOVFF instruction to modify any of the interrupt control registers while **any** interrupt is enabled. Doing so may cause erratic microcontroller behavior.

'0' = Bit is cleared

|       | R/W-1                   | R/W-1               | U-0           | R/W-1                 | R/W-1        | R/W-1       | R/W-1         | R/W-1                  |

|-------|-------------------------|---------------------|---------------|-----------------------|--------------|-------------|---------------|------------------------|

|       | OSCFIP                  | CMIP <sup>(1)</sup> | _             | EEIP                  | BCLIP        | HLVDIP      | TMR3IP        | ECCP1IP <sup>(2)</sup> |

|       | bit 7                   |                     |               |                       |              |             |               | bit 0                  |

| bit 7 | OSCFIP: (               | Dscillator Fail     | Interrupt I   | Priority bit          |              |             |               |                        |

|       | 1 = High p<br>0 = Low p | •                   |               |                       |              |             |               |                        |

| bit 6 | CMIP: Cor               | nparator Inter      | rupt Priori   | ty bit <sup>(1)</sup> |              |             |               |                        |

|       | 1 = High p<br>0 = Low p |                     |               |                       |              |             |               |                        |

| bit 5 | Unimplem                | ented: Read         | <b>as</b> '0' |                       |              |             |               |                        |

| bit 4 | EEIP: Data              | a EEPROM/F          | lash Write    | Operation             | nterrupt Pri | ority bit   |               |                        |

|       | 1 = High p<br>0 = Low p |                     |               |                       |              |             |               |                        |

| bit 3 | BCLIP: Bu               | is Collision In     | terrupt Pri   | ority bit             |              |             |               |                        |

|       | 1 = High p<br>0 = Low p | •                   |               |                       |              |             |               |                        |

| bit 2 | HLVDIP: H               | ligh/Low-Volta      | age Detec     | t Interrupt F         | riority bit  |             |               |                        |

|       | 1 = High p<br>0 = Low p | •                   |               |                       |              |             |               |                        |

| bit 1 | TMR3IP: T               | MR3 Overflo         | w Interrup    | t Priority bit        |              |             |               |                        |

|       | 1 = High p<br>0 = Low p | ,                   |               |                       |              |             |               |                        |

| bit 0 | ECCP1IP:                | ECCP1 Inter         | rupt Priori   | ty bit <sup>(2)</sup> |              |             |               |                        |

|       | 1 = High p<br>0 = Low p |                     |               |                       |              |             |               |                        |

|       | Note 1:                 | This bit is av      | ailable in    | PIC18F4X8             | X devices a  | nd reserved | l in PIC18F2  | X8X devices.           |

|       | 2:                      | This bit is av      | vailable in   | PIC18F4X8             | X devices o  | only.       |               |                        |

|       | Legend:                 |                     |               |                       |              |             |               |                        |

|       | R = Reada               | ble bit             | W = V         | Vritable bit          | U = Un       | implemente  | d bit, read a | is '0'                 |

|       | 1                       |                     |               |                       |              |             |               |                        |

### REGISTER 9-11: IPR2: PERIPHERAL INTERRUPT PRIORITY REGISTER 2

-n = Value at POR

'1' = Bit is set

x = Bit is unknown

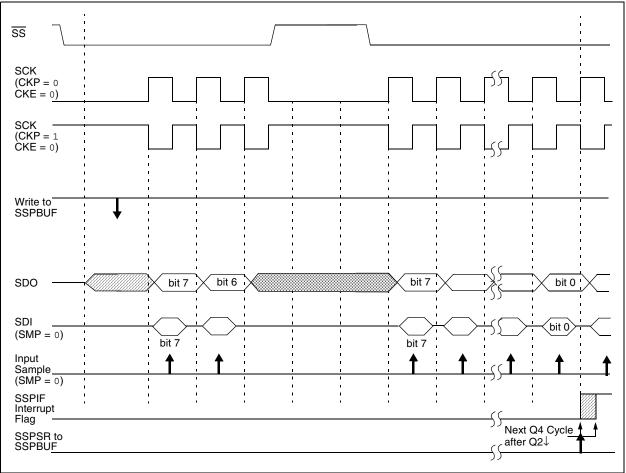

### 17.3.6 SLAVE MODE

In Slave mode, the data is transmitted and received as the external clock pulses appear on SCK. When the last bit is latched, the SSPIF interrupt flag bit is set.

Before enabling the module in SPI Slave mode, the clock line must match the proper Idle state. The clock line can be observed by reading the SCK pin. The Idle state is determined by the CKP bit (SSPCON1<4>).

While in Slave mode, the external clock is supplied by the external clock source on the SCK pin. This external clock must meet the minimum high and low times as specified in the electrical specifications.

While in Sleep mode, the slave can transmit/receive data. When a byte is received, the device will wake-up from Sleep.

### 17.3.7 SLAVE SELECT SYNCHRONIZATION

The  $\overline{SS}$  pin allows a Synchronous Slave mode. The SPI must be in Slave mode with  $\overline{SS}$  pin control enabled (SSPCON1<3:0> = 04h). The pin must not be driven low for the  $\overline{SS}$  pin to function as an input. The data latch

must be high. When the  $\overline{SS}$  pin is low, transmission and reception are enabled and the SDO pin is driven. When the  $\overline{SS}$  pin goes high, the SDO pin is no longer driven, even if in the middle of a transmitted byte and becomes a floating output. External pull-up/pull-down resistors may be desirable depending on the application.

- Note 1: When the SPI is in Slave mode with  $\overline{SS}$  pin control enabled (SSPCON<3:0> = 0100), the SPI module will reset if the  $\overline{SS}$  pin is set to VDD.

- 2: If the SPI is used in Slave mode with CKE set, then the SS pin control must be enabled.

When the SPI module resets, the bit counter is forced to '0'. This can be done by either forcing the  $\overline{SS}$  pin to a high level or clearing the SSPEN bit.

To emulate two-wire communication, the SDO pin can be connected to the SDI pin. When the SPI needs to operate as a receiver, the SDO pin can be configured as an input. This disables transmissions from the SDO. The SDI can always be left as an input (SDI function) since it cannot create a bus conflict.

## FIGURE 17-4: SLAVE SYNCHRONIZATION WAVEFORM

© 2007 Microchip Technology Inc.

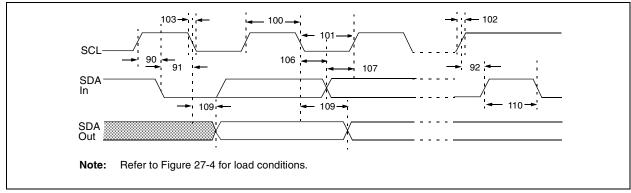

# 17.4.6.1 I<sup>2</sup>C Master Mode Operation

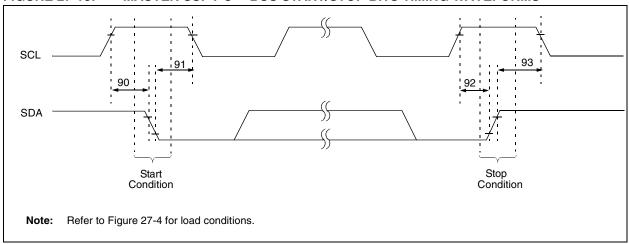

The master device generates all of the serial clock pulses and the Start and Stop conditions. A transfer is ended with a Stop condition or with a Repeated Start condition. Since the Repeated Start condition is also the beginning of the next serial transfer, the I<sup>2</sup>C bus will not be released.

In Master Transmitter mode, serial data is output through SDA, while SCL outputs the serial clock. The first byte transmitted contains the slave address of the receiving device (7 bits) and the Read/Write (R/W) bit. In this case, the R/W bit will be logic '0'. Serial data is transmitted 8 bits at a time. After each byte is transmitted, an Acknowledge bit is received. Start and Stop conditions are output to indicate the beginning and the end of a serial transfer.

In Master Receive mode, the first byte transmitted contains the slave address of the transmitting device (7 bits) and the R/W bit. In this case, the R/W bit will be logic '1' Thus, the first byte transmitted is a 7-bit slave address followed by a '1' to indicate the receive bit. Serial data is received via SDA, while SCL outputs the serial clock. Serial data is received 8 bits at a time. After each byte is received, an Acknowledge bit is transmitted. Start and Stop conditions indicate the beginning and end of transmission.

The Baud Rate Generator used for the SPI mode operation is used to set the SCL clock frequency for either 100 kHz, 400 kHz or 1 MHz I<sup>2</sup>C operation. See **Section 17.4.7 "Baud Rate"** for more detail.

A typical transmit sequence would go as follows:

- 1. The user generates a Start condition by setting the Start Enable bit, SEN (SSPCON2<0>).

- 2. SSPIF is set. The MSSP module will wait the required start time before any other operation takes place.

- 3. The user loads the SSPBUF with the slave address to transmit.

- 4. Address is shifted out the SDA pin until all 8 bits are transmitted.

- 5. The MSSP Module shifts in the ACK bit from the slave device and writes its value into the SSPCON2 register (SSPCON2<6>).

- 6. The MSSP module generates an interrupt at the end of the ninth clock cycle by setting the SSPIF bit.

- 7. The user loads the SSPBUF with eight bits of data.

- 8. Data is shifted out the SDA pin until all 8 bits are transmitted.

- The MSSP module shifts in the ACK bit from the slave device and writes its value into the SSPCON2 register (SSPCON2<6>).

- 10. The MSSP module generates an interrupt at the end of the ninth clock cycle by setting the SSPIF bit.

- 11. The user generates a Stop condition by setting the Stop Enable bit, PEN (SSPCON2<2>).

- 12. Interrupt is generated once the Stop condition is complete.

#### 18.4.2 EUSART SYNCHRONOUS SLAVE RECEPTION

The operation of the Synchronous Master and Slave modes is identical, except in the case of Sleep or any Idle mode and bit SREN, which is a "don't care" in Slave mode.

If receive is enabled by setting the CREN bit prior to entering Sleep or any Idle mode, then a word may be received while in this low-power mode. Once the word is received, the RSR register will transfer the data to the RCREG register; if the RCIE enable bit is set, the interrupt generated will wake the chip from the low-power mode. If the global interrupt is enabled, the program will branch to the interrupt vector. To set up a Synchronous Slave Reception:

- Enable the synchronous master serial port by setting bits SYNC and SPEN and clearing bit CSRC.

- 2. If interrupts are desired, set enable bit RCIE.

- 3. If 9-bit reception is desired, set bit RX9.

- 4. To enable reception, set enable bit CREN.

- 5. Flag bit RCIF will be set when reception is complete. An interrupt will be generated if enable bit RCIE was set.

- 6. Read the RCSTA register to get the 9th bit (if enabled) and determine if any error occurred during reception.

- 7. Read the 8-bit received data by reading the RCREG register.

- 8. If any error occurred, clear the error by clearing bit CREN.

- If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

| Name    | Bit 7                                                          | Bit 6        | Bit 5       | Bit 4        | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

|---------|----------------------------------------------------------------|--------------|-------------|--------------|-------|--------|--------|--------|----------------------------|

| INTCON  | GIE/GIEH                                                       | PEIE/GIEL    | TMR0IE      | INT0IE       | RBIE  | TMR0IF | INT0IF | RBIF   | 49                         |

| PIR1    | PSPIF <sup>(1)</sup> ADIF RCIF TXIF SSPIF CCP1IF TMR2IF TMR1IF |              |             |              |       |        |        | 52     |                            |

| PIE1    | PSPIE <sup>(1)</sup>                                           | ADIE         | RCIE        | TXIE         | SSPIE | CCP1IE | TMR2IE | TMR1IE | 52                         |

| IPR1    | PSPIP <sup>(1)</sup>                                           | ADIP         | RCIP        | TXIP         | SSPIP | CCP1IP | TMR2IP | TMR1IP | 52                         |

| RCSTA   | SPEN                                                           | RX9          | SREN        | CREN         | ADDEN | FERR   | OERR   | RX9D   | 51                         |

| RCREG   | EUSART F                                                       | Receive Regi | ster        |              |       |        |        |        | 51                         |

| TXSTA   | CSRC                                                           | TX9          | TXEN        | SYNC         | SENDB | BRGH   | TRMT   | TX9D   | 51                         |

| BAUDCON | ABDOVF                                                         | RCIDL        | —           | SCKP         | BRG16 | —      | WUE    | ABDEN  | 51                         |

| SPBRGH  | EUSART Baud Rate Generator Register High Byte                  |              |             |              |       |        |        |        |                            |

| SPBRG   | EUSART E                                                       | Baud Rate G  | enerator Re | gister Low I | Byte  |        |        |        | 51                         |

### TABLE 18-10: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE RECEPTION

Legend: — = unimplemented, read as '0'. Shaded cells are not used for synchronous slave reception.

**Note 1:** Reserved in PIC18F2X8X devices; always maintain these bits clear.

# 19.2 Selecting and Configuring Automatic Acquisition Time

The ADCON2 register allows the user to select an acquisition time that occurs each time the  $GO/\overline{DONE}$  bit is set.

When the GO/DONE bit is set, sampling is stopped and a conversion begins. The user is responsible for ensuring the required acquisition time has passed between selecting the desired input channel and setting the GO/DONE bit. This occurs when the ACQT2:ACQT0 bits (ADCON2<5:3>) remain in their Reset state ('000') and is compatible with devices that do not offer programmable acquisition times.

If desired, the ACQT bits can be set to select a programmable acquisition time for the A/D module. When the GO/DONE bit is set, the A/D module continues to sample the input for the selected acquisition time, then automatically begins a conversion. Since the acquisition time is programmed, there may be no need to wait for an acquisition time between selecting a channel and setting the GO/DONE bit.

In either case, when the conversion is completed, the GO/DONE bit is cleared, the ADIF flag is set and the A/D begins sampling the currently selected channel again. If an acquisition time is programmed, there is nothing to indicate if the acquisition time has ended or if the conversion has begun.

# 19.3 Selecting the A/D Conversion Clock

The A/D conversion time per bit is defined as TAD. The A/D conversion requires 11 TAD per 10-bit conversion. The source of the A/D conversion clock is software selectable. There are seven possible options for TAD:

- 2 Tosc

- 4 Tosc

- 8 Tosc

- 16 Tosc

- 32 Tosc

- 64 Tosc

- Internal RC Oscillator

For correct A/D conversions, the A/D conversion clock (TAD) must be as short as possible, but greater than the minimum TAD (approximately 2  $\mu$ s, see parameter 130 for more information).

Table 19-1 shows the resultant TAD times derived from the device operating frequencies and the A/D clock source selected.

| AD Clock S        | ource (TAD) | Maximum Device Frequency |                                 |  |  |  |

|-------------------|-------------|--------------------------|---------------------------------|--|--|--|

| Operation         | ADCS2:ADCS0 | PIC18FX585/X680          | PIC18LFX585/X680 <sup>(4)</sup> |  |  |  |

| 2 Tosc            | 000         | 2.86 MHz                 | 1.43 kHz                        |  |  |  |

| 4 Tosc            | 100         | 5.71 MHz                 | 2.86 MHz                        |  |  |  |

| 8 Tosc            | 001         | 11.43 MHz                | 5.72 MHz                        |  |  |  |

| 16 Tosc           | 101         | 22.86 MHz                | 11.43 MHz                       |  |  |  |

| 32 Tosc           | 010         | 40.0 MHz                 | 22.86 MHz                       |  |  |  |

| 64 Tosc           | 110         | 40.0 MHz                 | 22.86 MHz                       |  |  |  |

| RC <sup>(3)</sup> | x11         | 1.00 MHz <sup>(1)</sup>  | 1.00 MHz <sup>(2)</sup>         |  |  |  |

### TABLE 19-1: TAD VS. DEVICE OPERATING FREQUENCIES

**Note 1:** The RC source has a typical TAD time of 4 ms.

2: The RC source has a typical TAD time of 6 ms.

**3:** For device frequencies above 1 MHz, the device must be in Sleep for the entire conversion or the A/D accuracy may be out of specification.

4: Low-power (PIC18LFXXXX) devices only.

# PIC18F2585/2680/4585/4680

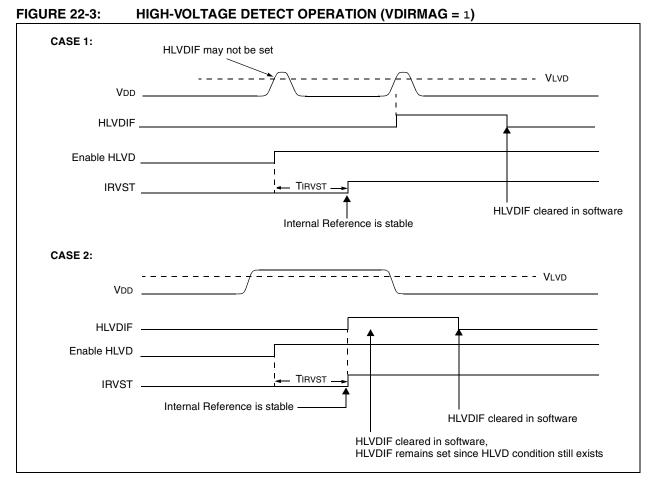

# 22.5 Applications

In many applications, the ability to detect a drop below, or rise above a particular threshold is desirable. For example, the HLVD module could be periodically enabled to detect Universal Serial Bus (USB) attach or detach. This assumes the device is powered by a lower voltage source than the USB when detached. An attach would indicate a high-voltage detect from, for example, 3.3V to 5V (the voltage on USB) and vice versa for a detach. This feature could save a design a few extra components and an attach signal (input pin).

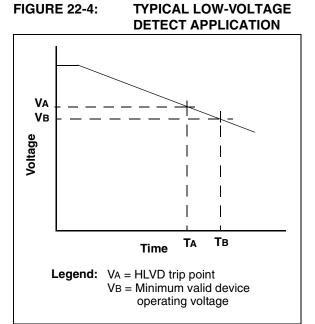

For general battery applications, Figure 22-4 shows a possible voltage curve. Over time, the device voltage decreases. When the device voltage reaches voltage VA, the HLVD logic generates an interrupt at time TA. The interrupt could cause the execution of an ISR, which would allow the application to perform "house-keeping tasks" and perform a controlled shutdown before the device voltage exits the valid operating range at TB. The HLVD, thus, would give the application a time window, represented by the difference between TA and TB, to safely exit.

# PIC18F2585/2680/4585/4680

DS39625C-page 274

| REGISTER 23-57: | PIE3: PEI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | RIPHERAI                                                                                                                                                     |                                                    | UPT ENAI     | BLE REGIS               | STER                  |           |          |  |  |  |  |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|--------------|-------------------------|-----------------------|-----------|----------|--|--|--|--|

| Mode 0          | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | R/W-0                                                                                                                                                        | R/W-0                                              | R/W-0        | R/W-0                   | R/W-0                 | R/W-0     | R/W-0    |  |  |  |  |

| Mode 0          | IRXIE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | WAKIE                                                                                                                                                        | ERRIE                                              | TXB2IE       | TXB1IE <sup>(1)</sup>   | TXB0IE <sup>(1)</sup> | RXB1IE    | RXB0IE   |  |  |  |  |

|                 | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | R/W-0                                                                                                                                                        | R/W-0                                              | R/W-0        | R/W-0                   | R/W-0                 | R/W-0     | R/W-0    |  |  |  |  |

| Mode 1, 2       | IRXIE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | WAKIE                                                                                                                                                        | ERRIE                                              | TXBnIE       | TXB1IE <sup>(1)</sup>   | TXB0IE <sup>(1)</sup> | RXBnIE    | FIFOWMIE |  |  |  |  |

|                 | bit 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                              |                                                    |              |                         |                       |           | bit 0    |  |  |  |  |