Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 40MHz                                                                      |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                |

| Number of I/O              | 36                                                                         |

| Program Memory Size        | 48KB (24K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 1K x 8                                                                     |

| RAM Size                   | 3.25K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                                |

| Data Converters            | A/D 11x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

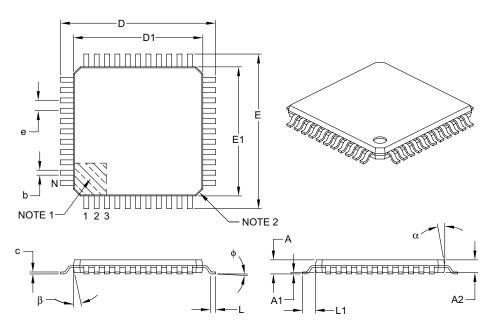

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-VQFN Exposed Pad                                                        |

| Supplier Device Package    | 44-QFN (8x8)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f4585t-i-ml |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Міскоснір PIC18F2585/2680/4585/4680

## 28/40/44-Pin Enhanced Flash Microcontrollers with ECAN<sup>TM</sup> Technology, 10-Bit A/D and nanoWatt Technology

#### **Power Managed Modes:**

- Run: CPU on, peripherals on

- Idle: CPU off, peripherals on

- Sleep: CPU off, peripherals off

- Idle mode currents down to 5.8 μA typical

- Sleep mode currents down to 0.1 µA typical

- Timer1 Oscillator: 1.1 μA, 32 kHz, 2V

- Watchdog Timer: 2.1 μA

- Two-Speed Oscillator Start-up

#### Flexible Oscillator Structure:

- Four Crystal modes, up to 40 MHz

- 4x Phase Lock Loop (PLL) available for crystal and internal oscillators

- Two External RC modes, up to 4 MHz

- Two External Clock modes, up to 40 MHz

- Internal oscillator block:

- 8 user selectable frequencies, from 31 kHz to 8 MHz

- Provides a complete range of clock speeds, from 31 kHz to 32 MHz when used with PLL

- User tunable to compensate for frequency drift

- Secondary oscillator using Timer1 @ 32 kHz

- Fail-Safe Clock Monitor

- Allows for safe shutdown if peripheral clock stops

#### **Special Microcontroller Features:**

- C compiler optimized architecture with optional extended instruction set

- 100,000 erase/write cycle Enhanced Flash program memory typical

- 1,000,000 erase/write cycle Data EEPROM memory typical

- Flash/Data EEPROM Retention: > 40 years

- Self-programmable under software control

- Priority levels for interrupts

- 8 x 8 Single Cycle Hardware Multiplier

- Extended Watchdog Timer (WDT):

- Programmable period from 41 ms to 131sSingle-Supply 5V In-Circuit Serial

- Programming™ (ICSP™) via two pins

- In-Circuit Debug (ICD) via two pins

- Wide operating voltage range: 2.0V to 5.5V

#### **Peripheral Highlights:**

- High current sink/source 25 mA/25 mA

- Three external interrupts

- One Capture/Compare/PWM (CCP1) module

- Enhanced Capture/Compare/PWM (ECCP1) module (40/44-pin devices only):

- One, two or four PWM outputs

- Selectable polarity

- Programmable dead time

- Auto-Shutdown and Auto-Restart

- Master Synchronous Serial Port (MSSP) module supporting 3-wire SPI (all 4 modes) and I<sup>2</sup>C<sup>™</sup> Master and Slave modes

- Enhanced Addressable USART module:

- Supports RS-485, RS-232 and LIN 1.3

- RS-232 operation using internal oscillator block (no external crystal required)

- Auto-Wake-up on Start bit

- Auto-Baud Detect

- 10-bit, up to 11-channel Analog-to-Digital Converter module (A/D), up to 100 Ksps

- Auto-acquisition capability

- Conversion available during Sleep

- · Dual analog comparators with input multiplexing

#### **ECAN Module Features:**

- Message bit rates up to 1 Mbps

- Conforms to CAN 2.0B ACTIVE Specification

- Fully backward compatible with PIC18XXX8 CAN modules

- Three modes of operation:

- Legacy, Enhanced Legacy, FIFO

- Three dedicated transmit buffers with prioritization

- Two dedicated receive buffers

- Six programmable receive/transmit buffers

- Three full 29-bit acceptance masks

- 16 full 29-bit acceptance filters w/ dynamic association

- DeviceNet<sup>™</sup> data byte filter support

- Automatic remote frame handling

- Advanced error management features

|            | Program Memory   |                               | Data Memory     |           |       | 40 D'I             | CCP1/          | MSSP |                             | ВΤ   |       | <b>T</b>           |

|------------|------------------|-------------------------------|-----------------|-----------|-------|--------------------|----------------|------|-----------------------------|------|-------|--------------------|

| Device     | Flash<br>(bytes) | # Single-Word<br>Instructions | SRAM<br>(bytes) | EEPROM VO |       | 10-Bit<br>A/D (ch) | ECCP1<br>(PWM) | SPI  | Master<br>I <sup>2</sup> C™ | EUSA | Comp. | Timers<br>8/16-bit |

| PIC18F2585 | 48K              | 24576                         | 3328            | 1024      | 28    | 8                  | 1/0            | Y    | Y                           | 1    | 0     | 1/3                |

| PIC18F2680 | 64K              | 32768                         | 3328            | 1024      | 28    | 8                  | 1/0            | Y    | Y                           | 1    | 0     | 1/3                |

| PIC18F4585 | 48K              | 24576                         | 3328            | 1024      | 44    | 11                 | 1/1            | Y    | Y                           | 1    | 2     | 1/3                |

| PIC18F4680 | 64K              | 32768                         | 3328            | 1024      | 40/44 | 11                 | 1/1            | Y    | Y                           | 1    | 2     | 1/3                |

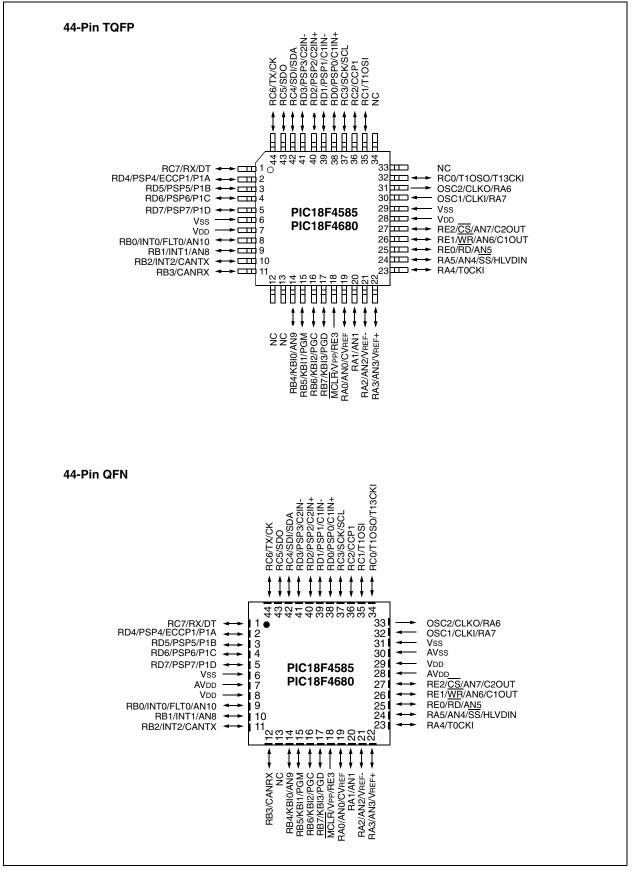

#### **Pin Diagrams (Continued)**

| REGISTER 2-1: | OSCTUNE                          |                                                   | TOR TUN         | ING REGI                         | STER         |               |                |             |  |  |  |

|---------------|----------------------------------|---------------------------------------------------|-----------------|----------------------------------|--------------|---------------|----------------|-------------|--|--|--|

|               | R/W-0                            | R/W-0 <sup>(1)</sup>                              | U-0             | R/W-0                            | R/W-0        | R/W-0         | R/W-0          | R/W-0       |  |  |  |

|               | INTSRC                           | PLLEN <sup>(1)</sup>                              |                 | TUN4                             | TUN3         | TUN2          | TUN1           | TUN0        |  |  |  |

|               | bit 7                            |                                                   |                 |                                  |              | 1             |                | bit 0       |  |  |  |

| bit 7         | INTSRC: Ir                       | nternal Oscill                                    | ator Low-Fr     | equency So                       | urce Select  | bit           |                |             |  |  |  |

|               |                                  | Hz device c                                       |                 |                                  |              | · ·           | e-by-256 ena   | abled)      |  |  |  |

| bit 6         |                                  | equency Mu<br>abled for IN <sup>-</sup><br>sabled |                 |                                  |              | )             |                |             |  |  |  |

|               | Note 1:                          | Available or and reads a                          | 2               | n oscillator o<br>ext for detail | 0            | ns; otherwise | e, this bit is | unavailable |  |  |  |

| bit 5         | Unimplem                         | ented: Read                                       | <b>l as</b> '0' |                                  |              |               |                |             |  |  |  |

| bit 4-0       | TUN4:TUN0: Frequency Tuning bits |                                                   |                 |                                  |              |               |                |             |  |  |  |

|               | 01111 = Maximum frequency        |                                                   |                 |                                  |              |               |                |             |  |  |  |

|               | •                                | •                                                 |                 |                                  |              |               |                |             |  |  |  |

|               | •                                | •                                                 |                 |                                  |              |               |                |             |  |  |  |

|               | 00001                            |                                                   |                 |                                  |              |               |                |             |  |  |  |

|               |                                  | enter freque                                      | ncy. Oscillat   | or module is                     | s running at | the calibrate | ed frequency   | /.          |  |  |  |

|               | 11111                            | •                                                 |                 |                                  |              |               |                |             |  |  |  |

|               | •                                | •                                                 |                 |                                  |              |               |                |             |  |  |  |

|               | 10000 = M                        | linimum freq                                      | uency           |                                  |              |               |                |             |  |  |  |

|               | Legend:                          |                                                   |                 |                                  |              |               |                |             |  |  |  |

|               | R = Reada                        | ble bit                                           | W = W           | ritable bit                      | U = Unin     | nplemented    | bit, read as   | '0'         |  |  |  |

'1' = Bit is set

#### 2.6.5.1 Compensating with the EUSART

-n = Value at POR

An adjustment may be required when the EUSART begins to generate framing errors or receives data with errors while in Asynchronous mode. Framing errors indicate that the device clock frequency is too high. To adjust for this, decrement the value in OSCTUNE to reduce the clock frequency. On the other hand, errors in data may suggest that the clock speed is too low. To compensate, increment OSCTUNE to increase the clock frequency.

#### 2.6.5.2 Compensating with the Timers

This technique compares device clock speed to some reference clock. Two timers may be used; one timer is clocked by the peripheral clock, while the other is clocked by a fixed reference source, such as the Timer1 oscillator.

Both timers are cleared, but the timer clocked by the reference generates interrupts. When an interrupt occurs, the internally clocked timer is read and both timers are cleared. If the internally clocked timer value is greater than expected, then the internal oscillator block is running too fast. To adjust for this, decrement the OSCTUNE register.

#### 2.6.5.3 Compensating with the CCP1 Module in Capture Mode

'0' = Bit is cleared

The CCP1 module can use free running Timer1 (or Timer3), clocked by the internal oscillator block and an external event with a known period (i.e., AC power frequency). The time of the first event is captured in the CCPRxH:CCPRxL registers and is recorded for use later. When the second event causes a capture, the time of the first event is subtracted from the time of the second event. Since the period of the external event is known, the time difference between events can be calculated.

x = Bit is unknown

If the measured time is much greater than the calculated time, the internal oscillator block is running too fast. To compensate, decrement the OSCTUNE register. If the measured time is much less than the calculated time, the internal oscillator block is running too slow. To compensate, increment the OSCTUNE register.

|          |      |         |        |      |                               | -               |                                           |      |                   |

|----------|------|---------|--------|------|-------------------------------|-----------------|-------------------------------------------|------|-------------------|

| Register | Арр  | olicabl | e Devi | ces  | Power-on Res<br>Brown-out Res | WDT<br>RESET IN | Resets,<br>Reset,<br>struction,<br>Resets | •    | via WDT<br>errupt |

| CCPR1H   | 2585 | 2680    | 4585   | 4680 | xxxx xxxx                     | uuuu            | uuuu                                      | uuuu | uuuu              |

| CCPR1L   | 2585 | 2680    | 4585   | 4680 | xxxx xxxx                     | uuuu            | uuuu                                      | uuuu | uuuu              |

| CCP1CON  | 2585 | 2680    | 4585   | 4680 | 00 0000                       | 00              | 0000                                      | uu   | uuuu              |

| ECCPR1H  | 2585 | 2680    | 4585   | 4680 | xxxx xxxx                     | uuuu            | uuuu                                      | uuuu | uuuu              |

| ECCPR1L  | 2585 | 2680    | 4585   | 4680 | xxxx xxxx                     | uuuu            | uuuu                                      | uuuu | uuuu              |

| ECCP1CON | 2585 | 2680    | 4585   | 4680 | 0000 0000                     | 0000            | 0000                                      | uuuu | uuuu              |

| BAUDCON  | 2585 | 2680    | 4585   | 4680 | 01-0 0-00                     | 01-0            | 0 - 0 0                                   | uu   | uuuu              |

| ECCP1DEL | 2585 | 2680    | 4585   | 4680 | 0000 0000                     | 0000            | 0000                                      | uuuu | uuuu              |

| ECCP1AS  | 2585 | 2680    | 4585   | 4680 | 0000 0000                     | 0000            | 0000                                      | uuuu | uuuu              |

| CVRCON   | 2585 | 2680    | 4585   | 4680 | 0000 0000                     | 0000            | 0000                                      | uuuu | uuuu              |

| CMCON    | 2585 | 2680    | 4585   | 4680 | 0000 0111                     | 0000            | 0111                                      | uuuu | uuuu              |

| TMR3H    | 2585 | 2680    | 4585   | 4680 | XXXX XXXX                     | uuuu            | uuuu                                      | uuuu | uuuu              |

| TMR3L    | 2585 | 2680    | 4585   | 4680 | xxxx xxxx                     | uuuu            | uuuu                                      | uuuu | uuuu              |

| T3CON    | 2585 | 2680    | 4585   | 4680 | 0000 0000                     | uuuu            | uuuu                                      | uuuu | uuuu              |

| SPBRGH   | 2585 | 2680    | 4585   | 4680 | 0000 0000                     | 0000            | 0000                                      | uuuu | uuuu              |

| SPBRG    | 2585 | 2680    | 4585   | 4680 | 0000 0000                     | 0000            | 0000                                      | uuuu | uuuu              |

| RCREG    | 2585 | 2680    | 4585   | 4680 | 0000 0000                     | 0000            | 0000                                      | uuuu | uuuu              |

| TXREG    | 2585 | 2680    | 4585   | 4680 | 0000 0000                     | 0000            | 0000                                      | uuuu | uuuu              |

| TXSTA    | 2585 | 2680    | 4585   | 4680 | 0000 0010                     | 0000            | 0010                                      | uuuu | uuuu              |

| RCSTA    | 2585 | 2680    | 4585   | 4680 | 0000 000x                     | 0000            | 000x                                      | uuuu | uuuu              |

| EEADRH   | 2585 | 2680    | 4585   | 4680 | 00                            |                 | 00                                        |      | uu                |

| EEADR    | 2585 | 2680    | 4585   | 4680 | 0000 0000                     | 0000            | 0000                                      | uuuu | uuuu              |

| EEDATA   | 2585 | 2680    | 4585   | 4680 | 0000 0000                     | 0000            | 0000                                      | uuuu | uuuu              |

| EECON2   | 2585 | 2680    | 4585   | 4680 | 0000 0000                     | 0000            | 0000                                      | 0000 | 0000              |

| EECON1   | 2585 | 2680    | 4585   | 4680 | xx-0 x000                     | uu-0            | u000                                      | uu-0 | u000              |

| IPR3     | 2585 | 2680    | 4585   | 4680 | 1111 1111                     | 1111            | 1111                                      | uuuu | uuuu              |

| PIR3     | 2585 | 2680    | 4585   | 4680 | 0000 0000                     | 0000            | 0000                                      | uuuu | uuuu              |

| PIE3     | 2585 | 2680    | 4585   | 4680 | 0000 0000                     | 0000            | 0000                                      | uuuu | uuuu              |

| IPR2     | 2585 | 2680    | 4585   | 4680 | 11-1 1111                     | 11-1            | 1111                                      | uu-u | uuuu              |

|          | 2585 | 2680    | 4585   | 4680 | 11 111-                       | 11              | 111-                                      | uu   |                   |

| PIR2     | 2585 | 2680    | 4585   | 4680 | 00-0 0000                     | 00-0            | 0000                                      | uu-u | սսսս <b>(1)</b>   |

|          | 2585 | 2680    | 4585   | 4680 | 00 000-                       | 0 0             |                                           |      | uuu-(1)           |

#### TABLE 4-4: INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED)

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition. Shaded cells indicate conditions do not apply for the designated device.

Note 1: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

**3:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

4: See Table 4-3 for Reset value for specific condition.

**5:** Bits 6 and 7 of PORTA, LATA and TRISA are enabled, depending on the oscillator mode selected. When not enabled as PORTA pins, they are disabled and read '0'.

6: This register reads all '0's until the ECAN<sup>™</sup> technology is set up in Mode 1 or Mode 2.

| TADLE J-2               |               |                            |                     |                     |                       |                                |                       |                       |                      |                     |  |  |

|-------------------------|---------------|----------------------------|---------------------|---------------------|-----------------------|--------------------------------|-----------------------|-----------------------|----------------------|---------------------|--|--|

| File Name               | Bit 7         | Bit 6                      | Bit 5               | Bit 4               | Bit 3                 | Bit 2                          | Bit 1                 | Bit 0                 | Value on<br>POR, BOR | Details<br>on page: |  |  |

| STATUS                  | _             | —                          |                     | Ν                   | OV                    | Z                              | DC                    | С                     | x xxxx               | 50, 87              |  |  |

| TMR0H                   | Timer0 Regis  | ter High Byte              |                     |                     |                       |                                | •                     | •                     | 0000 0000            | 50, 149             |  |  |

| TMR0L                   | Timer0 Regis  | ter Low Byte               |                     |                     |                       |                                |                       |                       | xxxx xxxx            | 50, 149             |  |  |

| TOCON                   | TMR0ON        | T08BIT                     | TOCS                | T0SE                | PSA                   | T0PS2                          | T0PS1                 | T0PS0                 | 1111 1111            | 50, 149             |  |  |

| OSCCON                  | IDLEN         | IRCF2                      | IRCF1               | IRCF0               | OSTS                  | IOFS                           | SCS1                  | SCS0                  | 0000 q000            | 30, 50              |  |  |

| HLVDCON                 | VDIRMAG       | _                          | IRVST               | HLVDEN              | HLVDL3                | HLVDL2                         | HLVDL1                | HLVDL0                | 0-00 0101            | 50, 267             |  |  |

| WDTCON                  | _             | —                          |                     | _                   | _                     | _                              | —                     | SWDTEN                | 0                    | 50, 353             |  |  |

| RCON                    | IPEN          | SBOREN <sup>(2)</sup>      | _                   | RI                  | TO                    | PD                             | POR                   | BOR                   | 0q-1 11q0            | 50, 127             |  |  |

| TMR1H                   | Timer1 Regis  | ter High Byte              |                     |                     |                       |                                |                       |                       | XXXX XXXX            | 50, 155             |  |  |

| TMR1L                   | Timer1 Regis  | ter Low Byte               |                     | 0000 0000           | 50, 155               |                                |                       |                       |                      |                     |  |  |

| T1CON                   | RD16          | T1RUN                      | T1CKPS1             | T1CKPS0             | T1OSCEN               | T1SYNC                         | TMR1CS                | TMR10N                | 0000 0000            | 50, 151             |  |  |

| TMR2                    | Timer2 Regis  | ter                        |                     |                     |                       |                                |                       |                       | 1111 1111            | 50, 158             |  |  |

| PR2                     | Timer2 Period | d Register                 |                     |                     |                       |                                |                       |                       | -000 0000            | 50, 155             |  |  |

| T2CON                   | _             | T2OUTPS3                   | T2OUTPS2            | T2OUTPS1            | T2OUTPS0              | TMR2ON                         | T2CKPS1               | T2CKPS0               | -000 0000            | 50, 157             |  |  |

| SSPBUF                  | SSP Receive   | Buffer/Transm              | it Register         |                     |                       |                                |                       |                       | xxxx xxxx            | 50, 195             |  |  |

| SSPADD                  | SSP Address   | Register in I <sup>2</sup> | C Slave mode        | e. SSP Baud I       | Rate Reload F         | Register in I <sup>2</sup> C I | Aaster mode.          |                       | 0000 0000            | 50, 195             |  |  |

| SSPSTAT                 | SMP           | CKE                        | D/A                 | Р                   | S                     | R/W                            | UA                    | BF                    | 0000 0000            | 50, 197             |  |  |

| SSPCON1                 | WCOL          | SSPOV                      | SSPEN               | CKP                 | SSPM3                 | SSPM2                          | SSPM1                 | SSPM0                 | 0000 0000            | 50, 198             |  |  |

| SSPCON2                 | GCEN          | ACKSTAT                    | ACKDT               | ACKEN               | RCEN                  | PEN                            | RSEN                  | SEN                   | 0000 0000            | 50, 199             |  |  |

| ADRESH                  | A/D Result Re | egister High By            | /te                 |                     |                       |                                |                       |                       | xxxx xxxx            | 50, 256             |  |  |

| ADRESL                  | A/D Result Re | egister Low By             | te                  |                     |                       |                                |                       |                       | XXXX XXXX            | 50, 256             |  |  |

| ADCON0                  | _             | _                          | CHS3                | CHS2                | CHS1                  | CHS0                           | GO/DONE               | ADON                  | 00 0000              | 50, 247             |  |  |

| ADCON1                  | —             | _                          | VCFG1               | VCFG0               | PCFG3                 | PCFG2                          | PCFG1                 | PCFG0                 | 00 0qqq              | 50, 248             |  |  |

| ADCON2                  | ADFM          | _                          | ACQT2               | ACQT1               | ACQT0                 | ADCS2                          | ADCS1                 | ADCS0                 | 0-00 0000            | 50, 249             |  |  |

| CCPR1H                  | Capture/Com   | pare/PWM Re                | gister 1 High       | Byte                |                       |                                | •                     | •                     | xxxx xxxx            | 51, 168             |  |  |

| CCPR1L                  | Capture/Com   | pare/PWM Re                | gister 1 Low        | Byte                |                       |                                |                       |                       | xxxx xxxx            | 51, 168             |  |  |

| CCP1CON                 | _             | _                          | DC1B1               | DC1B0               | CCP1M3                | CCP1M2                         | CCP1M1                | CCP1M0                | xx xxxx              | 51, 163             |  |  |

| ECCPR1H <sup>(9)</sup>  | Enhanced Ca   | pture/Compar               | e/PWM Regis         | ster 1 High By      | /te                   |                                |                       |                       | xxxx xxxx            | 51, 167             |  |  |

| ECCPR1L <sup>(9)</sup>  | Enhanced Ca   | pture/Compar               | e/PWM Regis         | ster 1 Low By       | te                    |                                |                       |                       | xxxx xxxx            | 51, 167             |  |  |

| ECCP1CON <sup>(9)</sup> | EPWM1M1       | EPWM1M0                    | EDC1B1              | EDC1B0              | ECCP1M3               | ECCP1M2                        | ECCP1M1               | ECCP1M0               | 0000 0000            | 51, 168             |  |  |

| BAUDCON                 | ABDOVF        | RCIDL                      | -                   | SCKP                | BRG16                 | —                              | WUE                   | ABDEN                 | 01-0 0000            | 51, 230             |  |  |

| ECCP1DEL <sup>(9)</sup> | PRSEN         | PDC6 <sup>(3)</sup>        | PDC5 <sup>(3)</sup> | PDC4 <sup>(3)</sup> | PDC3 <sup>(3)</sup>   | PDC2 <sup>(3)</sup>            | PDC1 <sup>(3)</sup>   | PDC0 <sup>(3)</sup>   | 0000 0000            | 51, 182             |  |  |

| ECCP1AS <sup>(9)</sup>  | ECCPASE       | ECCPAS2                    | ECCPAS1             | ECCPAS0             | PSSAC1                | PSSAC0                         | PSSBD1 <sup>(3)</sup> | PSSBD0 <sup>(3)</sup> | 0000 0000            | 51, 183             |  |  |

| CVRCON <sup>(9)</sup>   | CVREN         | CVROE                      | CVRR                | CVRSS               | CVR3                  | CVR2                           | CVR1                  | CVR0                  | 0000 0000            | 51, 263             |  |  |

| CMCON <sup>(9)</sup>    | C2OUT         | C1OUT                      | C2INV               | C1INV               | CIS                   | CM2                            | CM1                   | CM0                   | 0000 0000            | 51, 257             |  |  |

| TMR3H                   | Timer3 Regis  | ter High Byte              |                     |                     |                       |                                | •                     |                       | xxxx xxxx            | 51, 161             |  |  |

| TMR3L                   | Timer3 Regis  | ter Low Byte               |                     |                     |                       |                                |                       |                       | xxxx xxxx            | 51, 161             |  |  |

| T3CON                   | RD16          | T3ECCP1 <sup>(9)</sup>     | T3CKPS1             | T3CKPS0             | T3CCP1 <sup>(9)</sup> | T3SYNC                         | TMR3CS                | TMR3ON                | 0000 0000            | 51, 161             |  |  |

|                         |               |                            |                     |                     |                       |                                |                       |                       |                      |                     |  |  |

#### **TABLE 5-2:** REGISTER FILE SUMMARY (PIC18F2585/2680/4585/4680) (CONTINUED)

Legend: x = unknown, u = unchanged, - = unimplemented, q = value depends on condition Note 1: Bit 21 of the PC is only available in Test mode and Serial Programming modes.

2: The SBOREN bit is only available when CONFIG2L<1:0> = 01; otherwise, it is disabled and reads as '0'. See Section 4.4 "Brown-out Reset (BOR)".

3: These registers and/or bits are not implemented on PIC18F2X8X devices and are read as '0'. Reset values are shown for PIC18F4X8X devices; individual unimplemented bits should be interpreted as '---

The PLLEN bit is only available in specific oscillator configuration; otherwise, it is disabled and reads as '0'. See Section 2.6.4 "PLL in 4: INTOSC Modes".

5: The RE3 bit is only available when Master Clear Reset is disabled (CONFIG3H<7> = 0); otherwise, RE3 reads as '0'. This bit is read-only.

RA6/RA7 and their associated latch and direction bits are individually configured as port pins based on various primary oscillator modes. 6: When disabled, these bits read as '0'.

7: CAN bits have multiple functions depending on the selected mode of the CAN module.

8: This register reads all '0's until the ECAN<sup>™</sup> technology is set up in Mode 1 or Mode 2.

9: These registers are available on PIC18F4X8X devices only.

#### 5.3.5 STATUS REGISTER

**REGISTER 5-2:**

The STATUS register, shown in Register 5-2, contains the arithmetic status of the ALU. As with any other SFR, it can be the operand for any instruction.

If the STATUS register is the destination for an instruction that affects the Z, DC, C, OV or N bits, the results of the instruction are not written; instead, the status is updated according to the instruction performed. Therefore, the result of an instruction with the STATUS register as its destination may be different than intended. As an example, CLRF STATUS will set the Z bit and leave the remaining Status bits unchanged ('000u u1uu').

STATUS REGISTER

It is recommended that only BCF, BSF, SWAPF, MOVFF and MOVWF instructions are used to alter the STATUS register, because these instructions do not affect the Z, C, DC, OV or N bits in the STATUS register.

For other instructions that do not affect Status bits, see the instruction set summaries in Table 25-2 and Table 25-3.

Note: The C and DC bits operate as the borrow and digit borrow bits respectively in subtraction.

|         | U-0                            | U-0                                             | U-0           | R/W-x                                          | R/W-x          | R/W-x        | R/W-x         | R/W-x    |

|---------|--------------------------------|-------------------------------------------------|---------------|------------------------------------------------|----------------|--------------|---------------|----------|

|         | _                              | —                                               |               | N                                              | OV             | Z            | DC            | С        |

|         | bit 7                          |                                                 |               |                                                |                |              |               | bit 0    |

| bit 7-5 | Unimplen                       | nented: Read                                    | <b>as</b> '0' |                                                |                |              |               |          |

| bit 4   | N: Negativ                     |                                                 |               |                                                |                |              |               |          |

|         |                                | used for signe<br>ALU MSB = 1                   |               | tic (2's comp                                  | lement). It ir | ndicates whe | ther the res  | ult was  |

|         |                                | t was negative<br>t was positive                | )             |                                                |                |              |               |          |

| bit 3   | OV: Overf                      | flow bit                                        |               |                                                |                |              |               |          |

|         | magnitude                      | used for signe<br>which cause<br>low occurred f | s the sign I  | bit (bit 7) to c                               | hange state    | ).           |               | he 7-bit |

|         |                                | erflow occurre                                  |               | ,                                              |                | ·            | ,             |          |

| bit 2   | Z: Zero bi                     | t                                               |               |                                                |                |              |               |          |

|         |                                | esult of an arit<br>esult of an arit            |               |                                                |                | D            |               |          |

| bit 1   |                                | carry/ <mark>borrow</mark> b<br>F, ADDLW, S     |               | SUBWF instr                                    | uctions:       |              |               |          |

|         |                                | y-out from the<br>rry-out from th               |               |                                                |                | rred         |               |          |

|         | Note:                          | complement                                      | t of the se   | y is reversed<br>cond operan<br>bit 4 or bit 3 | d. For rotate  | e (RRF, RLF) |               |          |

| bit 0   | <b>C:</b> Carry/t<br>For ADDWI | DORTOW bit                                      | SUBLW and     | SUBWF instr                                    | uctions:       |              |               |          |

|         |                                | y-out from the<br>rry-out from th               |               |                                                |                |              |               |          |

|         | Note:                          | complement                                      | t of the se   | y is reversed<br>cond operan<br>high or low-c  | d. For rotate  | e (RRF, RLF) | ) instruction |          |

|         | Legend:                        |                                                 |               |                                                |                |              |               |          |

|         | R = Read                       | lable bit                                       | W = \         | Nritable bit                                   | U = Unii       | mplemented   | bit, read as  | '0'      |

|         | -n = Value                     | e at POR                                        | '1' = l       | Bit is set                                     |                | is cleared   | x = Bit is i  |          |

#### © 2007 Microchip Technology Inc.

#### 5.4.3.2 FSR Registers and POSTINC, POSTDEC, PREINC and PLUSW

In addition to the INDF operand, each FSR register pair also has four additional indirect operands. Like INDF, these are "virtual" registers that cannot be indirectly read or written to. Accessing these registers actually accesses the associated FSR register pair, but also performs a specific action on its stored value. They are:

- POSTDEC: accesses the FSR value, then automatically decrements it by 1 afterwards

- POSTINC: accesses the FSR value, then automatically increments it by 1 afterwards

- PREINC: increments the FSR value by 1, then uses it in the operation

- PLUSW: adds the signed value of the W register (range of -127 to 128) to that of the FSR and uses the new value in the operation.

In this context, accessing an INDF register uses the value in the FSR registers without changing them. Similarly, accessing a PLUSW register gives the FSR value offset by that in the W register; neither value is actually changed in the operation. Accessing the other virtual registers changes the value of the FSR registers.

Operations on the FSRs with POSTDEC, POSTINC and PREINC affect the entire register pair; that is, rollovers of the FSRnL register from FFh to 00h carry over to the FSRnH register. On the other hand, results of these operations do not change the value of any flags in the STATUS register (e.g., Z, N, OV, etc.).

The PLUSW register can be used to implement a form of indexed addressing in the data memory space. By manipulating the value in the W register, users can reach addresses that are fixed offsets from pointer addresses. In some applications, this can be used to implement some powerful program control structure, such as software stacks, inside of data memory.

#### 5.4.3.3 Operations by FSRs on FSRs

Indirect addressing operations that target other FSRs or virtual registers represent special cases. For example, using an FSR to point to one of the virtual registers will not result in successful operations. As a specific case, assume that FSR0H:FSR0L contains FE7h, the address of INDF1. Attempts to read the value of the INDF1 using INDF0 as an operand will return 00h. Attempts to write to INDF1 using INDF0 as the operand will result in a NOP.

On the other hand, using the virtual registers to write to an FSR pair may not occur as planned. In these cases, the value will be written to the FSR pair but without any incrementing or decrementing. Thus, writing to INDF2 or POSTDEC2 will write the same value to the FSR2H:FSR2L.

Since the FSRs are physical registers mapped in the SFR space, they can be manipulated through all direct operations. Users should proceed cautiously when working on these registers, particularly if their code uses indirect addressing.

Similarly, operations by indirect addressing are generally permitted on all other SFRs. Users should exercise the appropriate caution that they do not inadvertently change settings that might affect the operation of the device.

## PIC18F2585/2680/4585/4680

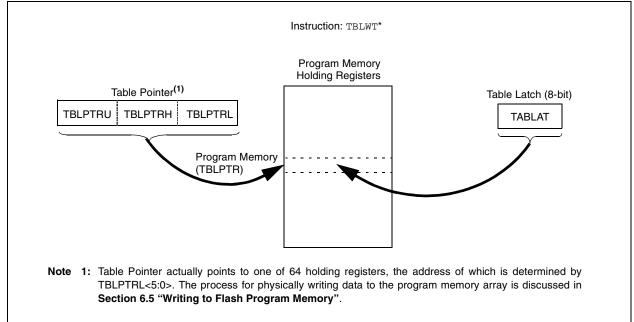

#### FIGURE 6-2: TABLE WRITE OPERATION

#### 6.2 Control Registers

Several control registers are used in conjunction with the TBLRD and TBLWT instructions. These include the:

- EECON1 register

- EECON2 register

- TABLAT register

- TBLPTR registers

#### 6.2.1 EECON1 AND EECON2 REGISTERS

The EECON1 register (Register 6-1) is the control register for memory accesses. The EECON2 register is not a physical register; it is used exclusively in the memory write and erase sequences. Reading EECON2 will read all '0's.

The EEPGD control bit determines if the access will be a program or data EEPROM memory access. When clear, any subsequent operations will operate on the data EEPROM memory. When set, any subsequent operations will operate on the program memory.

The CFGS control bit determines if the access will be to the Configuration/Calibration registers or to program memory/data EEPROM memory. When set, subsequent operations will operate on Configuration registers regardless of EEPGD (see **Section 24.0 "Special Features of the CPU"**). When clear, memory selection access is determined by EEPGD. The FREE bit, when set, will allow a program memory erase operation. When FREE is set, the erase operation is initiated on the next WR command. When FREE is clear, only writes are enabled.

The WREN bit, when set, will allow a write operation. On power-up, the WREN bit is clear. The WRERR bit is set in hardware when the WREN bit is set and cleared when the internal programming timer expires and the write operation is complete.

| Note: | During normal operation, the WRERR is       |  |  |  |  |  |  |  |  |  |  |

|-------|---------------------------------------------|--|--|--|--|--|--|--|--|--|--|

|       | read as '1'. This can indicate that a write |  |  |  |  |  |  |  |  |  |  |

|       | operation was prematurely terminated by     |  |  |  |  |  |  |  |  |  |  |

|       | a Reset, or a write operation was           |  |  |  |  |  |  |  |  |  |  |

|       | attempted improperly.                       |  |  |  |  |  |  |  |  |  |  |

The WR control bit initiates write operations. The bit cannot be cleared, only set, in software; it is cleared in hardware at the completion of the write operation.

Note: The EEIF Interrupt flag bit (PIR2<4>) is set when the write is complete. It must be cleared in software.

## PIC18F2585/2680/4585/4680

| R/W-1                          | R/W-1                          | U-0           | R/W-0                      | R/W-0        | U-0          | R/W-0  | R/W-0 |

|--------------------------------|--------------------------------|---------------|----------------------------|--------------|--------------|--------|-------|

| INT2IP                         | INT1IP                         |               | INT2IE                     | INT1IE       | —            | INT2IF | INT1I |

| bit 7                          |                                |               | ·                          |              |              |        | b     |

| INT2IP: INT                    | 2 External I                   | nterrupt Pr   | iority bit                 |              |              |        |       |

| 1 = High prior 0 = Low prior 1 | ,                              |               |                            |              |              |        |       |

| INT1IP: INT                    | 1 External I                   | nterrupt Pr   | iority bit                 |              |              |        |       |

| 1 = High pr                    | riority                        |               | -                          |              |              |        |       |

| 0 = Low pri                    | ority                          |               |                            |              |              |        |       |

| Unimpleme                      | ented: Read                    | <b>as</b> '0' |                            |              |              |        |       |

| INT2IE: INT                    | 2 External I                   | nterrupt Er   | nable bit                  |              |              |        |       |

|                                | s the INT2 e<br>s the INT2 e   |               |                            |              |              |        |       |

| INT1IE: INT                    | 1 External I                   | nterrupt Er   | nable bit                  |              |              |        |       |

|                                | s the INT1 e<br>s the INT1 e   |               |                            |              |              |        |       |

| Unimpleme                      | ented: Read                    | <b>as</b> '0' |                            |              |              |        |       |

| INT2IF: INT                    | 2 External li                  | nterrupt Fla  | ag bit                     |              |              |        |       |

|                                | T2 external i<br>T2 external i |               | curred (mus<br>d not occur | t be cleared | in software) | 1      |       |

| INT1IF: INT                    | 1 External li                  | nterrupt Fla  | ag bit                     |              |              |        |       |

|                                |                                |               | curred (mus<br>d not occur | t be cleared | in software) | I      |       |

#### **REGISTER 9-**

| Legend:           |                  |                                    |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

|                   |                  |                                    |                    |  |  |  |

Interrupt flag bits are set when an interrupt condition occurs regardless of the state Note: of its corresponding enable bit or the global interrupt enable bit. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt. This feature allows for software polling.

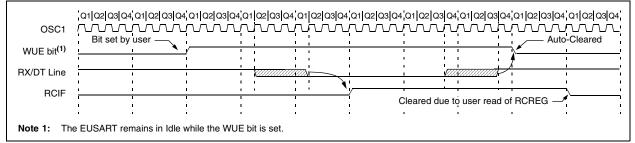

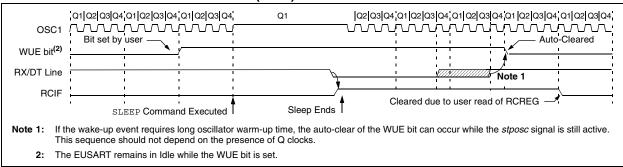

#### 18.2.4 AUTO-WAKE-UP ON SYNC BREAK CHARACTER

During Sleep mode, all clocks to the EUSART are suspended. Because of this, the Baud Rate Generator is inactive and a proper byte reception cannot be performed. The auto-wake-up feature allows the controller to wake-up due to activity on the RX/DT line while the EUSART is operating in Asynchronous mode.

The auto-wake-up feature is enabled by setting the WUE bit (BAUDCON<1>). Once set, the typical receive sequence on RX/DT is disabled and the EUSART remains in an Idle state, monitoring for a wake-up event independent of the CPU mode. A wake-up event consists of a high-to-low transition on the RX/DT line. (This coincides with the start of a Sync Break or a Wake-up Signal character for the LIN protocol.)

Following a wake-up event, the module generates an RCIF interrupt. The interrupt is generated synchronously to the Q clocks in normal operating modes (Figure 18-8) and asynchronously, if the device is in Sleep mode (Figure 18-9). The interrupt condition is cleared by reading the RCREG register.

The WUE bit is automatically cleared once a low-to-high transition is observed on the RX line following the wake-up event. At this point, the EUSART module is in Idle mode and returns to normal operation. This signals to the user that the Sync Break event is over.

#### 18.2.4.1 Special Considerations Using Auto-Wake-up

Since auto-wake-up functions by sensing rising edge transitions on RX/DT, information with any state changes before the Stop bit may signal a false

end-of-character and cause data or framing errors. To work properly, therefore, the initial character in the transmission must be all '0's. This can be 00h (8 bytes) for standard RS-232 devices or 000h (12 bits) for LIN bus.

Oscillator start-up time must also be considered, especially in applications using oscillators with longer start-up intervals (i.e., XT or HS mode). The Sync Break (or Wake-up Signal) character must be of sufficient length and be followed by a sufficient interval to allow enough time for the selected oscillator to start and provide proper initialization of the EUSART.

## 18.2.4.2 Special Considerations Using the WUE Bit

The timing of WUE and RCIF events may cause some confusion when it comes to determining the validity of received data. As noted, setting the WUE bit places the EUSART in an Idle mode. The wake-up event causes a receive interrupt by setting the RCIF bit. The WUE bit is cleared after this when a rising edge is seen on RX/DT. The interrupt condition is then cleared by reading the RCREG register. Ordinarily, the data in RCREG will be dummy data and should be discarded.

The fact that the WUE bit has been cleared (or is still set) and the RCIF flag is set should not be used as an indicator of the integrity of the data in RCREG. Users should consider implementing a parallel method in firmware to verify received data integrity.

To assure that no actual data is lost, check the RCIDL bit to verify that a receive operation is not in process. If a receive operation is not occurring, the WUE bit may then be set just prior to entering the Sleep mode.

#### FIGURE 18-8: AUTO-WAKE-UP BIT (WUE) TIMINGS DURING NORMAL OPERATION

#### FIGURE 18-9: AUTO-WAKE-UP BIT (WUE) TIMINGS DURING SLEEP

#### 19.0 10-BIT ANALOG-TO-DIGITAL CONVERTER (A/D) MODULE

The Analog-to-Digital (A/D) converter module has 8 inputs for the PIC18F2X8X devices and 11 for the PIC18F4X8X devices. This module allows conversion of an analog input signal to a corresponding 10-bit digital number.

The module has five registers:

- A/D Result High Register (ADRESH)

- A/D Result Low Register (ADRESL)

- A/D Control Register 0 (ADCON0)

- A/D Control Register 1 (ADCON1)

- A/D Control Register 2 (ADCON2)

The ADCON0 register, shown in Register 19-1, controls the operation of the A/D module. The ADCON1 register, shown in Register 19-2, configures the functions of the port pins. The ADCON2 register, shown in Register 19-3, configures the A/D clock source, programmed acquisition time and justification.

#### REGISTER 19-1: ADCON0: A/D CONTROL REGISTER 0 U-0 U-0 **R/W-0** R/W-0 R/W-0 **R/W-0 R/W-0** R/W-0 CHS3 CHS2 CHS1 CHS0 GO/DONE ADON bit 7 bit 0

- bit 7-6 Unimplemented: Read as '0'

- bit 5-2 CHS3:CHS0: Analog Channel Select bits

- 0000 = Channel 0 (AN0)

- 0001 = Channel 1 (AN1)

- 0010 = Channel 2 (AN2)

- 0011 = Channel 3 (AN3)

- 0100 = Channel 4 (AN4) 0101 = Channel 5 (AN5)<sup>(1,2)</sup>

- 0110 =Channel 6 (AN6)<sup>(1,2)</sup>

- $0111 = Channel 7 (AN7)^{(1,2)}$

- 1000 = Channel 8 (AN8)

- 1001 = Channel 9 (AN9)

- 1010 = Channel 10 (AN10)

- 1011 = Unused

- 1100 = Unused

- 1101 = Unused

- 1110 = Unused

- 1111 = Unused

- Note 1: These channels are not implemented on PIC18F2X8X devices.

- **2:** Performing a conversion on unimplemented channels will return full-scale measurements.

- bit 1 GO/DONE: A/D Conversion Status bit

- When ADON = 1:

- 1 = A/D conversion in progress

- 0 = A/D Idle

- bit 0 ADON: A/D On bit

- 1 = A/D converter module is enabled

- 0 = A/D converter module is disabled

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

| 51EN 23-1. | CANCON                                                                                      |                                |                | GISIEN       |               |             |                |            |  |  |  |  |

|------------|---------------------------------------------------------------------------------------------|--------------------------------|----------------|--------------|---------------|-------------|----------------|------------|--|--|--|--|

| Mada 0     | R/W-1                                                                                       | R/W-0                          | R/W-0          | R/S-0        | R/W-0         | R/W-0       | R/W-0          | U-0        |  |  |  |  |

| Mode 0     | REQOP2                                                                                      | REQOP1                         | REQOP0         | ABAT         | WIN2          | WIN1        | WIN0           | —          |  |  |  |  |

|            | DAM 4                                                                                       |                                |                |              |               |             |                |            |  |  |  |  |

| Mode 1     | R/W-1                                                                                       | R/W-0                          | R/W-0          | R/S-0        | U-0           | U-0         | U-0            | U-0        |  |  |  |  |

|            | REQOP2                                                                                      | REQOP1                         | REQOP0         | ABAT         | _             |             |                | —          |  |  |  |  |

|            | R/W-1                                                                                       | R/W-0                          | R/W-0          | R/S-0        | R-0           | R-0         | R-0            | R-0        |  |  |  |  |

| Mode 2     | REQOP2                                                                                      | REQOP1                         | REQOP0         | ABAT         | FP3           | FP2         | FP1            | FP0        |  |  |  |  |

|            | REQOP2     REQOP1     REQOP0     ABAI     FP3     FP2     FP1     FP0       bit 7     bit 0 |                                |                |              |               |             |                |            |  |  |  |  |

|            |                                                                                             |                                |                |              |               |             |                |            |  |  |  |  |

| bit 7-5    | REQOP2:F                                                                                    | REQOP0: R                      | equest CAN     | Operation N  | /lode bits    |             |                |            |  |  |  |  |

|            |                                                                                             |                                | uration mode   | -            |               |             |                |            |  |  |  |  |

|            | 011 = Request Listen Only mode                                                              |                                |                |              |               |             |                |            |  |  |  |  |

|            | 010 = Request Loopback mode                                                                 |                                |                |              |               |             |                |            |  |  |  |  |

|            |                                                                                             | uest Disable                   |                |              |               |             |                |            |  |  |  |  |

| L:1 4      | •                                                                                           | uest Normal                    |                |              |               |             |                |            |  |  |  |  |

| bit 4      |                                                                                             |                                | ng Transmiss   |              |               |             |                |            |  |  |  |  |

|            |                                                                                             |                                | ansmissions    |              | mit buffers)  |             |                |            |  |  |  |  |

| bit 3-1    | Mode 0:                                                                                     |                                | securing de m  | orman        |               |             |                |            |  |  |  |  |

|            |                                                                                             | 0: Window A                    | Address bits   |              |               |             |                |            |  |  |  |  |

|            |                                                                                             |                                | of the CAN     | buffers to s | witch into th | e access ba | nk area. Thi   | s allows   |  |  |  |  |

|            |                                                                                             |                                | gisters from a |              |               |             |                |            |  |  |  |  |

|            | -                                                                                           |                                | CODE0 bits     | -            | ied to the W  | IN3:WIN0 b  | ts to select t | he correct |  |  |  |  |

|            |                                                                                             | =                              | 3-2 for a code | e example.   |               |             |                |            |  |  |  |  |

|            |                                                                                             | eive Buffer (                  |                |              |               |             |                |            |  |  |  |  |

|            |                                                                                             | eive Buffer (<br>eive Buffer 1 |                |              |               |             |                |            |  |  |  |  |

|            |                                                                                             | smit Buffer                    |                |              |               |             |                |            |  |  |  |  |

|            | 011 <b>= Tran</b>                                                                           | smit Buffer                    | 1              |              |               |             |                |            |  |  |  |  |

|            |                                                                                             | smit Buffer                    |                |              |               |             |                |            |  |  |  |  |

|            |                                                                                             | eive Buffer (<br>eive Buffer ( |                |              |               |             |                |            |  |  |  |  |

| bit 0      |                                                                                             |                                |                |              |               |             |                |            |  |  |  |  |

| bit 4-0    | Mode 1:                                                                                     | ented: Rea                     |                |              |               |             |                |            |  |  |  |  |

| Dit 4-0    |                                                                                             | ented: Rea                     | d as '∩'       |              |               |             |                |            |  |  |  |  |

|            | Mode 2:                                                                                     | enteu. nea                     |                |              |               |             |                |            |  |  |  |  |

|            |                                                                                             | FIFO Read F                    | Pointer bits   |              |               |             |                |            |  |  |  |  |

|            | These bits point to the message buffer to be read.                                          |                                |                |              |               |             |                |            |  |  |  |  |

|            |                                                                                             |                                | e buffer to be |              |               |             |                |            |  |  |  |  |

|            | 1111:100                                                                                    | 0 = Reserve                    | ed             |              |               |             |                |            |  |  |  |  |

|            | Γ-                                                                                          |                                |                |              |               |             |                | 1          |  |  |  |  |

|            | Legend:                                                                                     |                                |                |              |               |             |                |            |  |  |  |  |

|            | R = Reada                                                                                   |                                | W = Writat     |              |               | -           | bit, read as ' |            |  |  |  |  |

|            | -n = Value                                                                                  | at POR                         | '1' = Bit is   | set          | '0' = Bit is  | cleared     | x = Bit is u   | nknown     |  |  |  |  |

#### REGISTER 23-1: CANCON: CAN CONTROL REGISTER

#### REGISTER 23-24: BnSIDH: TX/RX BUFFER n STANDARD IDENTIFIER REGISTERS, HIGH BYTE IN RECEIVE MODE $[0 \le n \le 5, TXnEN (BSEL0<n>) = 0]^{(1)}$

| R-x   | R-x  | R-x  | R-x  | R-x  | R-x  | R-x  | R-x   |

|-------|------|------|------|------|------|------|-------|

| SID10 | SID9 | SID8 | SID7 | SID6 | SID5 | SID4 | SID3  |

| bit 7 |      |      |      |      |      |      | bit 0 |

bit 7-0 **SID10:SID3:** Standard Identifier bits (if EXIDE (BnSIDL<3>) = 0) Extended Identifier bits EID28:EID21 (if EXIDE = 1).

Note 1: These registers are available in Mode 1 and 2 only.

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### REGISTER 23-25: BnSIDH: TX/RX BUFFER n STANDARD IDENTIFIER REGISTERS,

#### HIGH BYTE IN TRANSMIT MODE $[0 \le n \le 5, TXnEN (BSEL0 < n >) = 1]^{(1)}$

| R/W-x |

|-------|-------|-------|-------|-------|-------|-------|-------|

| SID10 | SID9  | SID8  | SID7  | SID6  | SID5  | SID4  | SID3  |

| bit 7 |       |       |       |       |       |       | bit 0 |

bit 7-0 **SID10:SID3:** Standard Identifier bits (if EXIDE (BnSIDL<3>) = 0) Extended Identifier bits EID28:EID21 (if EXIDE = 1).

Note 1: These registers are available in Mode 1 and 2 only.

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | l bit, read as '0' |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### 23.2.6 CAN INTERRUPT REGISTERS

The registers in this section are the same as described in **Section 9.0 "Interrupts"**. They are duplicated here for convenience.

| GISTER 23-56: | PIR3: PERIPHERAL INTERRUPT REQUEST (FLAG) REGISTER 3                                                                                                                             |                                                                                   |           |           |                       |                       |               |          |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-----------|-----------|-----------------------|-----------------------|---------------|----------|

| Mada 0        | R/W-0                                                                                                                                                                            | R/W-0                                                                             | R/W-0     | R/W-0     | R/W-0                 | R/W-0                 | R/W-0         | R/W-0    |

| Mode 0        | IRXIF                                                                                                                                                                            | WAKIF                                                                             | ERRIF     | TXB2IF    | TXB1IF <sup>(1)</sup> | TXB0IF <sup>(1)</sup> | RXB1IF        | RXB0IF   |

|               | R/W-0                                                                                                                                                                            | R/W-0                                                                             | R/W-0     | R/W-0     | R/W-0                 | R/W-0                 | R/W-0         | R/W-0    |

| Mode 1, 2     | IRXIF                                                                                                                                                                            | WAKIF                                                                             | ERRIF     | TXBnIF    | TXB1IF <sup>(1)</sup> | TXB0IF <sup>(1)</sup> | RXBnIF        | FIFOWMIF |

|               |                                                                                                                                                                                  |                                                                                   |           |           |                       |                       |               | bit 0    |

| bit 7         | IRXIF: CAN Invalid Received Message Interrupt Flag bit                                                                                                                           |                                                                                   |           |           |                       |                       |               |          |

| Dit 1         |                                                                                                                                                                                  | alid messag                                                                       |           |           |                       |                       |               |          |

|               |                                                                                                                                                                                  | 0 = No invalid message on CAN bus                                                 |           |           |                       |                       |               |          |

| bit 6         |                                                                                                                                                                                  | AN bus Acti                                                                       |           |           | Flag bit              |                       |               |          |

|               |                                                                                                                                                                                  | y on CAN bu<br>ivity on CAN                                                       |           | irred     |                       |                       |               |          |

| bit 5         |                                                                                                                                                                                  | AN bus Erro                                                                       |           | -lag hit  |                       |                       |               |          |

| bit 0         |                                                                                                                                                                                  |                                                                                   |           |           | e (multiple sc        | ources)               |               |          |

|               |                                                                                                                                                                                  | N module e                                                                        |           |           | Υ Ι                   | ,                     |               |          |

| bit 4         |                                                                                                                                                                                  | <u>V is in Mode</u>                                                               |           |           |                       |                       |               |          |

|               |                                                                                                                                                                                  | AN Transm                                                                         |           |           |                       | essage and r          | nov bo rolo   | adad     |

|               |                                                                                                                                                                                  |                                                                                   |           |           | smission of a         |                       | nay be reic   | aueu     |

|               |                                                                                                                                                                                  | l is in Mode                                                                      |           |           |                       |                       |               |          |

|               |                                                                                                                                                                                  | ny Transmit                                                                       |           |           |                       |                       |               |          |

|               | 1 = One or more transmit buffers have completed transmission of a message and may be reloaded $0 =$ No transmit buffer is ready for reload                                       |                                                                                   |           |           |                       |                       |               |          |

| bit 3         |                                                                                                                                                                                  | <b>TXB1IF:</b> CAN Transmit Buffer 1 Interrupt Flag bit <sup>(1)</sup>            |           |           |                       |                       |               |          |

|               | 1 = Transr                                                                                                                                                                       | 1 = Transmit Buffer 1 has completed transmission of a message and may be reloaded |           |           |                       |                       |               |          |

|               | 0 = Transmit Buffer 1 has not completed transmission of a message                                                                                                                |                                                                                   |           |           |                       |                       |               |          |

| bit 2         | <b>TXB0IF:</b> CAN Transmit Buffer 0 Interrupt Flag bit <sup>(1)</sup>                                                                                                           |                                                                                   |           |           |                       |                       |               |          |