Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 25MHz                                                                     |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                               |

| Number of I/O              | 36                                                                        |

| Program Memory Size        | 64KB (32K x 16)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 1K x 8                                                                    |

| RAM Size                   | 3.25K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 11x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 44-VQFN Exposed Pad                                                       |

| Supplier Device Package    | 44-QFN (8x8)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f4680-e-ml |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

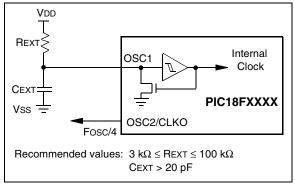

# 2.4 RC Oscillator

For timing insensitive applications, the "RC" and "RCIO" device options offer additional cost savings. The actual oscillator frequency is a function of several factors:

- supply voltage

- values of the external resistor (REXT) and capacitor (CEXT)

- · operating temperature

Given the same device, operating voltage and temperature and component values, there will also be unit-to-unit frequency variations. These are due to factors such as:

- normal manufacturing variation

- difference in lead frame capacitance between package types (especially for low CEXT values)

- variations within the tolerance of limits of REXT and CEXT

In the RC Oscillator mode, the oscillator frequency divided by 4 is available on the OSC2 pin. This signal may be used for test purposes or to synchronize other logic. Figure 2-5 shows how the R/C combination is connected.

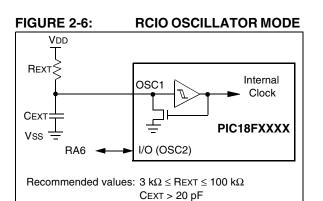

The RCIO Oscillator mode (Figure 2-6) functions like the RC mode, except that the OSC2 pin becomes an additional general purpose I/O pin. The I/O pin becomes bit 6 of PORTA (RA6).

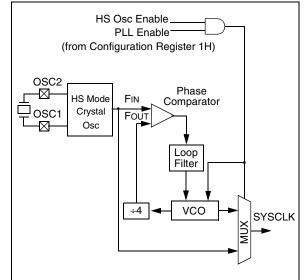

# 2.5 PLL Frequency Multiplier

A Phase Locked Loop (PLL) circuit is provided as an option for users who wish to use a lower frequency oscillator circuit or to clock the device up to its highest rated frequency from a crystal oscillator. This may be useful for customers who are concerned with EMI due to high-frequency crystals or users who require higher clock speeds from an internal oscillator.

### 2.5.1 HSPLL OSCILLATOR MODE

The HSPLL mode makes use of the HS mode oscillator for frequencies up to 10 MHz. A PLL then multiplies the oscillator output frequency by 4 to produce an internal clock frequency up to 40 MHz.

The PLL is only available to the crystal oscillator when the FOSC3:FOSC0 Configuration bits are programmed for HSPLL mode (= 0110).

# FIGURE 2-7: PLL BLOCK DIAGRAM (HS MODE)

## 2.5.2 PLL AND INTOSC

The PLL is also available to the internal oscillator block in selected oscillator modes. In this configuration, the PLL is enabled in software and generates a clock output of up to 32 MHz. The operation of INTOSC with the PLL is described in **Section 2.6.4 "PLL in INTOSC Modes"**.

### 5.1.2.2 Return Stack Pointer (STKPTR)

The STKPTR register (Register 5-1) contains the Stack Pointer value, the STKFUL (Stack Full) status bit and the STKUNF (Stack Underflow) status bits. The value of the Stack Pointer can be 0 through 31. The Stack Pointer increments before values are pushed onto the stack and decrements after values are popped off the stack. On Reset, the Stack Pointer value will be zero. The user may read and write the Stack Pointer value. This feature can be used by a Real-Time Operating System (RTOS) for return stack maintenance.

After the PC is pushed onto the stack 31 times (without popping any values off the stack), the STKFUL bit is set. The STKFUL bit is cleared by software or by a POR.

The action that takes place when the stack becomes full depends on the state of the STVREN (Stack Overflow Reset Enable) Configuration bit. (Refer to **Section 24.1 "Configuration Bits**" for a description of the device Configuration bits.) If STVREN is set (default), the 31st push will push the (PC + 2) value onto the stack, set the STKFUL bit and reset the device. The STKFUL bit will remain set and the Stack Pointer will be set to zero.

If STVREN is cleared, the STKFUL bit will be set on the 31st push and the Stack Pointer will increment to 31. Any additional pushes will not overwrite the 31st push and STKPTR will remain at 31.

When the stack has been popped enough times to unload the stack, the next pop will return a value of zero to the PC and sets the STKUNF bit, while the Stack Pointer remains at zero. The STKUNF bit will remain set until cleared by software or until a POR occurs.

| Note: | Returning a value of zero to the PC on an |  |  |  |  |  |  |  |

|-------|-------------------------------------------|--|--|--|--|--|--|--|

|       | underflow has the effect of vectoring the |  |  |  |  |  |  |  |

|       | program to the Reset vector, where the    |  |  |  |  |  |  |  |

|       | stack conditions can be verified and      |  |  |  |  |  |  |  |

|       | appropriate actions can be taken. This is |  |  |  |  |  |  |  |

|       | not the same as a Reset, as the contents  |  |  |  |  |  |  |  |

|       | of the SFRs are not affected.             |  |  |  |  |  |  |  |

### 5.1.2.3 PUSH and POP Instructions

Since the Top-of-Stack is readable and writable, the ability to push values onto the stack and pull values off the stack without disturbing normal program execution is a desirable feature. The PIC18 instruction set includes two instructions, PUSH and POP, that permit the TOS to be manipulated under software control. TOSU, TOSH and TOSL can be modified to place data or a return address on the stack.

The PUSH instruction places the current PC value onto the stack. This increments the Stack Pointer and loads the current PC value onto the stack.

The POP instruction discards the current TOS by decrementing the Stack Pointer. The previous value pushed onto the stack then becomes the TOS value.

# REGISTER 5-1: STKPTR: STACK POINTER REGISTER

|         | 01101111                                                      |                 |                          |              |              |          |       |       |  |  |  |  |  |

|---------|---------------------------------------------------------------|-----------------|--------------------------|--------------|--------------|----------|-------|-------|--|--|--|--|--|

|         | R/C-0                                                         | R/C-0           | U-0                      | R/W-0        | R/W-0        | R/W-0    | R/W-0 | R/W-0 |  |  |  |  |  |

|         | STKFUL <sup>(1)</sup> STKUNF <sup>(1)</sup> — SP4 SP3 SP2 SP1 |                 |                          |              |              |          |       |       |  |  |  |  |  |

|         | bit 7                                                         |                 |                          |              |              |          |       | bit 0 |  |  |  |  |  |

|         |                                                               |                 |                          |              |              |          |       |       |  |  |  |  |  |

| bit 7   | STKFUL: S                                                     | Stack Full Flag | bit <sup>(1)</sup>       |              |              |          |       |       |  |  |  |  |  |

|         | - 0.000.0                                                     | ecame full or   |                          | <i>.</i>     |              |          |       |       |  |  |  |  |  |

|         | • • •••••                                                     | as not becom    |                          |              |              |          |       |       |  |  |  |  |  |

| bit 6   | STKUNF: S                                                     | Stack Underflo  | w Flag bit <sup>(1</sup> | )            |              |          |       |       |  |  |  |  |  |

|         | 1 = Stack u                                                   | nderflow occu   | rred                     |              |              |          |       |       |  |  |  |  |  |

|         | 0 = Stack underflow did not occur                             |                 |                          |              |              |          |       |       |  |  |  |  |  |

| bit 5   | Unimpleme                                                     | ented: Read a   | <b>as</b> '0'            |              |              |          |       |       |  |  |  |  |  |

| bit 4-0 | SP4:SP0: 8                                                    | Stack Pointer I | _ocation bits            | 5            |              |          |       |       |  |  |  |  |  |

|         | Note 1:                                                       | Bit 7 and bit 6 | are cleare               | d by user so | ftware or by | / a POR. |       |       |  |  |  |  |  |

|         |                                                               |                 |                          |              |              |          |       |       |  |  |  |  |  |

| Legend:           |                  |                      |                        |

|-------------------|------------------|----------------------|------------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | C = Clearable only bit |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown     |

| File Name             | Bit 7              | Bit 6              | Bit 5               | Bit 4                  | Bit 3                  | Bit 2                   | Bit 1                  | Bit 0                  | Value on POR, BOR | Details<br>on page: |

|-----------------------|--------------------|--------------------|---------------------|------------------------|------------------------|-------------------------|------------------------|------------------------|-------------------|---------------------|

| PORTE <sup>(3)</sup>  | _                  | _                  |                     | _                      | RE3 <sup>(5)</sup>     | RE2 <sup>(3)</sup>      | RE1 <sup>(3)</sup>     | RE0 <sup>(3)</sup>     | xxxx              | 52, 145             |

| PORTD <sup>(3)</sup>  | Read PORTD         | pins, Write P      | ORTD Data L         | atch.                  |                        |                         |                        |                        | xxxx xxxx         | 52, 138             |

| PORTC                 | Read PORTC         | pins, Write P      | ORTC Data L         | .atch                  |                        |                         |                        |                        | xxxx xxxx         | 52, 135             |

| PORTB                 | Read PORTB         | pins, Write P      | ORTB Data L         | atch                   |                        |                         |                        |                        | xxxx xxxx         | 52, 132             |

| PORTA                 | RA7 <sup>(6)</sup> | RA6 <sup>(6)</sup> | Read PORT           | A pins, Write          | PORTA Data I           | _atch                   |                        |                        | xx00 0000         | 52, 129             |

| ECANCON               | MDSEL1             | MDSEL0             | FIFOWM              | EWIN4                  | EWIN3                  | EWIN2                   | EWIN1                  | EWIN0                  | 0001 000          | 52, 280             |

| TXERRCNT              | TEC7               | TEC6               | TEC5                | TEC4                   | TEC3                   | TEC2                    | TEC1                   | TEC0                   | 0000 0000         | 52, 285             |

| RXERRCNT              | REC7               | REC6               | REC5                | REC4                   | REC3                   | REC2                    | REC1                   | REC0                   | 0000 0000         | 52, 293             |

| COMSTAT<br>Mode 0     | RXB0OVFL           | RXB1OVFL           | ТХВО                | TXBP                   | RXBP                   | TXWARN                  | RXWARN                 | EWARN                  | 0000 0000         | 52, 281             |

| COMSTAT<br>Mode 1     | —                  | RXBnOVFL           | ТХВО                | TXBP                   | RXBP                   | TXWARN                  | RXWARN                 | EWARN                  | -000 0000         | 52, 281             |

| COMSTAT<br>Mode 2     | FIFOEMPTY          | RXBnOVFL           | ТХВО                | TXBP                   | RXBP                   | TXWARN                  | RXWARN                 | EWARN                  | 0000 0000         | 52, 281             |

| CIOCON                | _                  | _                  | ENDRHI              | CANCAP                 | _                      | _                       | _                      | _                      | 00                | 52, 314             |

| BRGCON3               | WAKDIS             | WAKFIL             | _                   | _                      | _                      | SEG2PH2                 | SEG2PH1                | SEG2PH0                | 00000             | 52, 313             |

| BRGCON2               | SEG2PHTS           | SAM                | SEG1PH2             | SEG1PH1                | SEG1PH0                | PRSEG2                  | PRSEG1                 | PRSEG0                 | 0000 0000         | 52, 312             |

| BRGCON1               | SJW1               | SJW0               | BRP5                | BRP4                   | BRP3                   | BRP2                    | BRP1                   | BRP0                   | 0000 0000         | 52, 311             |

| CANCON<br>Mode 0      | REQOP2             | REQOP1             | REQOP0              | ABAT                   | WIN2 <sup>(7)</sup>    | WIN1 <sup>(7)</sup>     | WIN0 <sup>(7)</sup>    | (7)                    | 1000 000-         | 53, 276             |

| CANCON<br>Mode 1      | REQOP2             | REQOP1             | REQOP0              | ABAT                   | (7)                    | (7)                     | (7)                    | (7)                    | 1000              | 53, 276             |

| CANCON<br>Mode 2      | REQOP2             | REQOP1             | REQOP0              | ABAT                   | FP3 <sup>(7)</sup>     | FP2 <sup>(7)</sup>      | FP1 <sup>(7)</sup>     | FP0 <sup>(7)</sup>     | 1000 0000         | 53, 276             |

| CANSTAT<br>Mode 0     | OPMODE2            | OPMODE1            | OPMODE0             | (7)                    | ICODE3 <sup>(7)</sup>  | ICODE2 <sup>(7)</sup>   | ICODE1 <sup>(7)</sup>  | (7)                    | 000- 0000         | 53, 277             |

| CANSTAT<br>Modes 1, 2 | OPMODE2            | OPMODE1            | OPMODE0             | EICODE4 <sup>(7)</sup> | EICODE3 <sup>(7)</sup> | EICODE2 <sup>(7)</sup>  | EICODE1 <sup>(7)</sup> | EICODE0 <sup>(7)</sup> | 0000 0000         | 53, 277             |

| RXB0D7                | RXB0D77            | RXB0D76            | RXB0D75             | RXB0D74                | RXB0D73                | RXB0D72                 | RXB0D71                | RXB0D70                | xxxx xxxx         | 53, 292             |

| RXB0D6                | RXB0D67            | RXB0D66            | RXB0D65             | RXB0D64                | RXB0D63                | RXB0D62                 | RXB0D61                | RXB0D60                | xxxx xxxx         | 53, 292             |

| RXB0D5                | RXB0D57            | RXB0D56            | RXB0D55             | RXB0D54                | RXB0D53                | RXB0D52                 | RXB0D51                | RXB0D50                | xxxx xxxx         | 53, 292             |

| RXB0D4                | RXB0D47            | RXB0D46            | RXB0D45             | RXB0D44                | RXB0D43                | RXB0D42                 | RXB0D41                | RXB0D40                | xxxx xxxx         | 53, 292             |

| RXB0D3                | RXB0D37            | RXB0D36            | RXB0D35             | RXB0D34                | RXB0D33                | RXB0D32                 | RXB0D31                | RXB0D30                | xxxx xxxx         | 53, 292             |

| RXB0D2                | RXB0D27            | RXB0D26            | RXB0D25             | RXB0D24                | RXB0D23                | RXB0D22                 | RXB0D21                | RXB0D20                | xxxx xxxx         | 53, 292             |

| RXB0D1                | RXB0D17            | RXB0D16            | RXB0D15             | RXB0D14                | RXB0D13                | RXB0D12                 | RXB0D11                | RXB0D10                | xxxx xxxx         | 53, 292             |

| RXB0D0                | RXB0D07            | RXB0D06            | RXB0D05             | RXB0D04                | RXB0D03                | RXB0D02                 | RXB0D01                | RXB0D00                | xxxx xxxx         | 53, 292             |

| RXB0DLC               |                    | RXRTR              | RB1                 | RB0                    | DLC3                   | DLC2                    | DLC1                   | DLC0                   | -xxx xxxx         | 53, 292             |

| RXB0EIDL              | EID7               | EID6               | EID5                | EID4                   | EID3                   | EID2                    | EID1                   | EID0                   | XXXX XXXX         | 53, 291             |

| RXB0EIDH              | EID15              | EID14              | EID13               | EID12                  | EID11                  | EID10                   | EID9                   | EID8                   | XXXX XXXX         | 53, 291             |

| RXB0SIDL              | SID2               | SID1               | SID0                | SRR                    | EXID                   |                         | EID17                  | EID16                  | xxxx x-xx         | 53, 291             |

| RXB0SIDH              | SID10              | SID9               | SID8                | SID7                   | SID6                   | SID5                    | SID4                   | SID3                   | xxxx xxxx         | 53, 290             |

| RXB0CON<br>Mode 0     | RXFUL              | RXM1               | RXM0 <sup>(7)</sup> | (7)                    | RXRTRRO <sup>(7)</sup> | RXBODBEN <sup>(7)</sup> | JTOFF <sup>(7)</sup>   | FILHITO <sup>(7)</sup> | 000- 0000         | 53, 287             |

| RXB0CON<br>Mode 1, 2  | RXFUL              | RXM1               | RTRRO               | FILHIT4                | FILHIT3                | FILHIT2                 | FILHIT1                | FILHIT0                | 0000 0000         | 53, 287             |

#### TABLE 5-2:REGISTER FILE SUMMARY (PIC18F2585/2680/4585/4680) (CONTINUED)

**Legend:** x = unknown, u = unchanged, - = unimplemented, q = value depends on condition

Note 1: Bit 21 of the PC is only available in Test mode and Serial Programming modes.

2: The SBOREN bit is only available when CONFIG2L<1:0> = 01; otherwise, it is disabled and reads as '0'. See Section 4.4 "Brown-out Reset (BOR)".

3: These registers and/or bits are not implemented on PIC18F2X8X devices and are read as '0'. Reset values are shown for PIC18F4X8X devices; individual unimplemented bits should be interpreted as '---'.

4: The PLLEN bit is only available in specific oscillator configuration; otherwise, it is disabled and reads as '0'. See Section 2.6.4 "PLL in INTOSC Modes".

5: The RE3 bit is only available when Master Clear Reset is disabled (CONFIG3H<7> = 0); otherwise, RE3 reads as '0'. This bit is read-only.

6: RA6/RA7 and their associated latch and direction bits are individually configured as port pins based on various primary oscillator modes. When disabled, these bits read as '0'.

7: CAN bits have multiple functions depending on the selected mode of the CAN module.

8: This register reads all '0's until the ECAN<sup>™</sup> technology is set up in Mode 1 or Mode 2.

9: These registers are available on PIC18F4X8X devices only.

| File Name | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | Value on POR, BOR | Details<br>on page: |

|-----------|---------|---------|---------|---------|---------|---------|---------|---------|-------------------|---------------------|

| TXB1SIDL  | SID2    | SID1    | SID0    | _       | EXIDE   | _       | EID17   | EID16   | xxx- x-xx         | 54, 283             |

| TXB1SIDH  | SID10   | SID9    | SID8    | SID7    | SID6    | SID5    | SID4    | SID3    | XXXX XXXX         | 54, 283             |

| TXB1CON   | TXBIF   | TXABT   | TXLARB  | TXERR   | TXREQ   | -       | TXPRI1  | TXPRI0  | 0000 0-00         | 54, 282             |

| TXB2D7    | TXB2D77 | TXB2D76 | TXB2D75 | TXB2D74 | TXB2D73 | TXB2D72 | TXB2D71 | TXB2D70 | XXXX XXXX         | 54, 284             |

| TXB2D6    | TXB2D67 | TXB2D66 | TXB2D65 | TXB2D64 | TXB2D63 | TXB2D62 | TXB2D61 | TXB2D60 | XXXX XXXX         | 54, 284             |

| TXB2D5    | TXB2D57 | TXB2D56 | TXB2D55 | TXB2D54 | TXB2D53 | TXB2D52 | TXB2D51 | TXB2D50 | XXXX XXXX         | 54, 284             |

| TXB2D4    | TXB2D47 | TXB2D46 | TXB2D45 | TXB2D44 | TXB2D43 | TXB2D42 | TXB2D41 | TXB2D40 | XXXX XXXX         | 54, 284             |

| TXB2D3    | TXB2D37 | TXB2D36 | TXB2D35 | TXB2D34 | TXB2D33 | TXB2D32 | TXB2D31 | TXB2D30 | xxxx xxxx         | 54, 284             |

| TXB2D2    | TXB2D27 | TXB2D26 | TXB2D25 | TXB2D24 | TXB2D23 | TXB2D22 | TXB2D21 | TXB2D20 | XXXX XXXX         | 54, 284             |

| TXB2D1    | TXB2D17 | TXB2D16 | TXB2D15 | TXB2D14 | TXB2D13 | TXB2D12 | TXB2D11 | TXB2D10 | XXXX XXXX         | 55, 284             |

| TXB2D0    | TXB2D07 | TXB2D06 | TXB2D05 | TXB2D04 | TXB2D03 | TXB2D02 | TXB2D01 | TXB2D00 | XXXX XXXX         | 55, 284             |

| TXB2DLC   | _       | TXRTR   | —       | —       | DLC3    | DLC2    | DLC1    | DLC0    | -x xxxx           | 55, 285             |

| TXB2EIDL  | EID7    | EID6    | EID5    | EID4    | EID3    | EID2    | EID1    | EID0    | xxxx xxxx         | 55, 284             |

| TXB2EIDH  | EID15   | EID14   | EID13   | EID12   | EID11   | EID10   | EID9    | EID8    | xxxx xxxx         | 55, 283             |

| TXB2SIDL  | SID2    | SID1    | SID0    | _       | EXIDE   | _       | EID17   | EID16   | xxxx x-xx         | 55, 283             |

| TXB2SIDH  | SID10   | SID9    | SID8    | SID7    | SID6    | SID5    | SID4    | SID3    | xxx- x-xx         | 55, 283             |

| TXB2CON   | TXBIF   | TXABT   | TXLARB  | TXERR   | TXREQ   | _       | TXPRI1  | TXPRI0  | 0000 0-00         | 55, 282             |

| RXM1EIDL  | EID7    | EID6    | EID5    | EID4    | EID3    | EID2    | EID1    | EID0    | xxxx xxxx         | 55, 304             |

| RXM1EIDH  | EID15   | EID14   | EID13   | EID12   | EID11   | EID10   | EID9    | EID8    | xxxx xxxx         | 55, 304             |

| RXM1SIDL  | SID2    | SID1    | SID0    | _       | EXIDEN  | _       | EID17   | EID16   | xxx- x-xx         | 55, 304             |

| RXM1SIDH  | SID10   | SID9    | SID8    | SID7    | SID6    | SID5    | SID4    | SID3    | xxxx xxxx         | 55, 304             |

| RXM0EIDL  | EID7    | EID6    | EID5    | EID4    | EID3    | EID2    | EID1    | EID0    | xxxx xxxx         | 55, 304             |

| RXM0EIDH  | EID15   | EID14   | EID13   | EID12   | EID11   | EID10   | EID9    | EID8    | xxxx xxxx         | 55, 304             |

| RXM0SIDL  | SID2    | SID1    | SID0    | _       | EXIDEN  | _       | EID17   | EID16   | xxx- x-xx         | 55, 304             |

| RXM0SIDH  | SID10   | SID9    | SID8    | SID7    | SID6    | SID5    | SID4    | SID3    | xxxx xxxx         | 55, 303             |

| RXF5EIDL  | EID7    | EID6    | EID5    | EID4    | EID3    | EID2    | EID1    | EID0    | xxxx xxxx         | 55, 303             |

| RXF5EIDH  | EID15   | EID14   | EID13   | EID12   | EID11   | EID10   | EID9    | EID8    | xxxx xxxx         | 55, 303             |

| RXF5SIDL  | SID2    | SID1    | SID0    | _       | EXIDEN  | _       | EID17   | EID16   | xxx- x-xx         | 55, 302             |

| RXF5SIDH  | SID10   | SID9    | SID8    | SID7    | SID6    | SID5    | SID4    | SID3    | xxxx xxxx         | 55, 302             |

| RXF4EIDL  | EID7    | EID6    | EID5    | EID4    | EID3    | EID2    | EID1    | EID0    | xxxx xxxx         | 55, 303             |

| RXF4EIDH  | EID15   | EID14   | EID13   | EID12   | EID11   | EID10   | EID9    | EID8    | xxxx xxxx         | 55, 303             |

| RXF4SIDL  | SID2    | SID1    | SID0    | —       | EXIDEN  | —       | EID17   | EID16   | xxx- x-xx         | 55, 302             |

| RXF4SIDH  | SID10   | SID9    | SID8    | SID7    | SID6    | SID5    | SID4    | SID3    | xxxx xxxx         | 55, 302             |

| RXF3EIDL  | EID7    | EID6    | EID5    | EID4    | EID3    | EID2    | EID1    | EID0    | xxxx xxxx         | 55, 303             |

| RXF3EIDH  | EID15   | EID14   | EID13   | EID12   | EID11   | EID10   | EID9    | EID8    | xxxx xxxx         | 55, 303             |

| RXF3SIDL  | SID2    | SID1    | SID0    | —       | EXIDEN  | _       | EID17   | EID16   | xxx- x-xx         | 55, 302             |

| RXF3SIDH  | SID10   | SID9    | SID8    | SID7    | SID6    | SID5    | SID4    | SID3    | xxxx xxxx         | 55, 302             |

| RXF2EIDL  | EID7    | EID6    | EID5    | EID4    | EID3    | EID2    | EID1    | EID0    | xxxx xxxx         | 55, 303             |

| RXF2EIDH  | EID15   | EID14   | EID13   | EID12   | EID11   | EID10   | EID9    | EID8    | xxxx xxxx         | 55, 303             |

| RXF2SIDL  | SID2    | SID1    | SID0    | —       | EXIDEN  | —       | EID17   | EID16   | xxx- x-xx         | 55, 302             |

| RXF2SIDH  | SID10   | SID9    | SID8    | SID7    | SID6    | SID5    | SID4    | SID3    | xxxx xxxx         | 55, 302             |

| TABLE 5-2: REGISTER FILE SUMMARY (PIC18F2585/2680/4585/4680) (CONTINUED | TABLE 5-2: | REGISTER FILE SUMMARY | (PIC18F2585/2680/4585/4680) | (CONTINUED) |

|-------------------------------------------------------------------------|------------|-----------------------|-----------------------------|-------------|

|-------------------------------------------------------------------------|------------|-----------------------|-----------------------------|-------------|

**Legend:** x = unknown, u = unchanged, - = unimplemented, q = value depends on condition **Note 1:** Bit 21 of the PC is only available in Test mode and Serial Programming modes.

2: The SBOREN bit is only available when CONFIG2L<1:0> = 01; otherwise, it is disabled and reads as '0'. See Section 4.4 "Brown-out Reset (BOR)".

3: These registers and/or bits are not implemented on PIC18F2X8X devices and are read as '0'. Reset values are shown for PIC18F4X8X devices; individual unimplemented bits should be interpreted as '---'.

4: The PLLEN bit is only available in specific oscillator configuration; otherwise, it is disabled and reads as '0'. See Section 2.6.4 "PLL in INTOSC Modes".

5: The RE3 bit is only available when Master Clear Reset is disabled (CONFIG3H<7> = 0); otherwise, RE3 reads as '0'. This bit is read-only.

**6:** RA6/RA7 and their associated latch and direction bits are individually configured as port pins based on various primary oscillator modes. When disabled, these bits read as '0'.

7: CAN bits have multiple functions depending on the selected mode of the CAN module.

8: This register reads all '0's until the ECAN<sup>™</sup> technology is set up in Mode 1 or Mode 2.

9: These registers are available on PIC18F4X8X devices only.

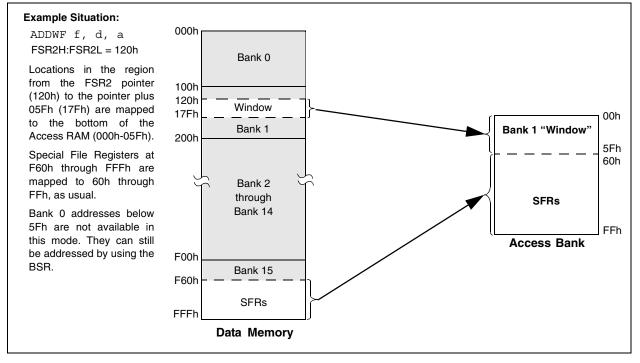

### 5.6.3 MAPPING THE ACCESS BANK IN INDEXED LITERAL OFFSET MODE

The use of Indexed Literal Offset Addressing mode effectively changes how the lower half of Access RAM (00h to 7Fh) is mapped. Rather than containing just the contents of the bottom half of Bank 0, this mode maps the contents from Bank 0 and a user defined "window" that can be located anywhere in the data memory space. The value of FSR2 establishes the lower boundary of the addresses mapped into the window, while the upper boundary is defined by FSR2 plus 95 (5Fh). Addresses in the Access RAM above 5Fh are mapped as previously described (see **Section 5.3.2 "Access Bank**"). An example of Access Bank remapping in this addressing mode is shown in Figure 5-9. Remapping of the Access Bank applies *only* to operations using the Indexed Literal Offset mode. Operations that use the BSR (Access RAM bit is '1') will continue to use direct addressing as before. Any indirect or indexed operation that explicitly uses any of the indirect file operands (including FSR2) will continue to operate as standard indirect addressing. Any instruction that uses the Access Bank, but includes a register address of greater than 05Fh, will use direct addressing and the normal Access Bank map.

#### 5.6.4 BSR IN INDEXED LITERAL OFFSET MODE

Although the Access Bank is remapped when the extended instruction set is enabled, the operation of the BSR remains unchanged. Direct addressing using the BSR to select the data memory bank operates in the same manner as previously described.

#### FIGURE 5-9: REMAPPING THE ACCESS BANK WITH INDEXED LITERAL OFFSET ADDRESSING

#### 7.6 **Operation During Code-Protect**

Data EEPROM memory has its own code-protect bits in Configuration Words. External read and write operations are disabled if code protection is enabled.

The microcontroller itself can both read and write to the internal Data EEPROM, regardless of the state of the code-protect Configuration bit. Refer to Section 24.0 "Special Features of the CPU" for additional information.

#### 7.7 **Protection Against Spurious Write**

There are conditions when the device may not want to write to the data EEPROM memory. To protect against spurious EEPROM writes, various mechanisms have been implemented. On power-up, the WREN bit is cleared. In addition, writes to the EEPROM are blocked during the Power-up Timer period (TPWRT, parameter 33).

The write initiate sequence and the WREN bit together help prevent an accidental write during brown-out, power glitch or software malfunction.

#### 7.8 Using the Data EEPROM

The data EEPROM is a high endurance, byte addressable array that has been optimized for the storage of frequently changing information (e.g., program variables or other data that are updated often). Frequently changing values will typically be updated more often than specification D124. If this is not the case, an array refresh must be performed. For this reason, variables that change infrequently (such as constants, IDs, calibration, etc.) should be stored in Flash program memory.

A simple data EEPROM refresh routine is shown in Example 7-3.

Note: If data EEPROM is only used to store constants and/or data that changes rarely, an array refresh is likely not required. See specification D124.

| EXAM | PLE 7-3: | DATA EEPROM   | REFRESH ROUTINE              |

|------|----------|---------------|------------------------------|

|      | CLRF     | EEADR         | ; Start at address 0         |

|      | CLRF     | EEADRH        | i                            |

|      | BCF      | EECON1, CFGS  | ; Set for memory             |

|      | BCF      | EECON1, EEPGD | ; Set for Data EEPROM        |

|      | BCF      | INTCON, GIE   | ; Disable interrupts         |

|      | BSF      | EECON1, WREN  | ; Enable writes              |

| Loop |          |               | ; Loop to refresh array      |

|      | BSF      | EECON1, RD    | ; Read current address       |

|      | MOVLW    | 55h           | i                            |

|      | MOVWF    | EECON2        | ; Write 55h                  |

|      | MOVLW    | 0AAh          | ;                            |

|      | MOVWF    | EECON2        | ; Write OAAh                 |

|      | BSF      | EECON1, WR    | ; Set WR bit to begin write  |

|      | BTFSC    | EECON1, WR    | ; Wait for write to complete |

|      | BRA      | \$-2          |                              |

|      | INCFSZ   | EEADR, F      | ; Increment address          |

|      | BRA      | LOOP          | ; Not zero, do it again      |

|      | INCFSZ   | EEADRH, F     | ; Increment the high address |

|      | BRA      | LOOP          | ; Not zero, do it again      |

|      | BCF      | EECON1, WREN  | ; Disable writes             |

|      | BSF      | INTCON, GIE   | ; Enable interrupts          |

EX

# 8.0 8 x 8 HARDWARE MULTIPLIER

### 8.1 Introduction

All PIC18 devices include an 8 x 8 hardware multiplier as part of the ALU. The multiplier performs an unsigned operation and yields a 16-bit result that is stored in the product register pair, PRODH:PRODL. The multiplier's operation does not affect any flags in the STATUS register.

Making multiplication a hardware operation allows it to be completed in a single instruction cycle. This has the advantages of higher computational throughput and reduced code size for multiplication algorithms and allows the PIC18 devices to be used in many applications previously reserved for digital signal processors. A comparison of various hardware and software multiply operations, along with the savings in memory and execution time, is shown in Table 8-1.

## 8.2 Operation

Example 8-1 shows the instruction sequence for an 8 x 8 unsigned multiplication. Only one instruction is required when one of the arguments is already loaded in the WREG register.

Example 8-2 shows the sequence to do an 8 x 8 signed multiplication. To account for the signed bits of the arguments, each argument's Most Significant bit (MSb) is tested and the appropriate subtractions are done.

### EXAMPLE 8-1: 8 x 8 UNSIGNED MULTIPLY ROUTINE

| MOVF  | ARG1, | W | ; |                |

|-------|-------|---|---|----------------|

| MULWF | ARG2  |   | ; | ARG1 * ARG2 -> |

|       |       |   | ; | PRODH: PRODL   |

|       |       |   |   |                |

### EXAMPLE 8-2:

| 8 x 8 | SIGNED | MUL | ΓIPLY |

|-------|--------|-----|-------|

| ROU   | TINE   |     |       |

| MOVE | ' ARG  | 31, W | I   |                |  |

|------|--------|-------|-----|----------------|--|

| MULV | IF ARG | 32    | ;   | ARG1 * ARG2 -> |  |

|      |        |       | ;   | PRODH:PRODL    |  |

| BTFS | C ARC  | 32, S | B;  | Test Sign Bit  |  |

| SUBV | IF PRO | DDH,  | F;  | PRODH = PRODH  |  |

|      |        |       | ;   | - ARG1         |  |

| MOVE | r ARG  | 32, W | I   |                |  |

| BTFS | SC ARC | 31, S | B ; | Test Sign Bit  |  |

| SUBV | IF PRO | DDH,  | F;  | PRODH = PRODH  |  |

|      |        |       | ;   | - ARG2         |  |

|      |        |       |     |                |  |

|                  |                           | Program           | Cycles | Time     |          |         |  |  |

|------------------|---------------------------|-------------------|--------|----------|----------|---------|--|--|

| Routine          | Multiply Method           | Memory<br>(Words) | (Max)  | @ 40 MHz | @ 10 MHz | @ 4 MHz |  |  |

| 8 x 8 unsigned   | Without hardware multiply | 13                | 69     | 6.9 μs   | 27.6 μs  | 69 µs   |  |  |

|                  | Hardware multiply         | 1                 | 1      | 100 ns   | 400 ns   | 1 μs    |  |  |

|                  | Without hardware multiply | 33                | 91     | 9.1 μs   | 36.4 μs  | 91 μs   |  |  |

| 8 x 8 signed     | Hardware multiply         | 6                 | 6      | 600 ns   | 2.4 μs   | 6 µs    |  |  |

| 16 x 16 uppigned | Without hardware multiply | 21                | 242    | 24.2 μs  | 96.8 µs  | 242 μs  |  |  |

| 16 x 16 unsigned | Hardware multiply         | 28                | 28     | 2.8 μs   | 11.2 μs  | 28 µs   |  |  |

| 16 x 16 signad   | Without hardware multiply | 52                | 254    | 25.4 μs  | 102.6 μs | 254 μs  |  |  |

| 16 x 16 signed   | Hardware multiply         | 35                | 40     | 4.0 μs   | 16.0 μs  | 40 µs   |  |  |

### TABLE 8-1: PERFORMANCE COMPARISON FOR VARIOUS MULTIPLY OPERATIONS

# 11.3 Prescaler

An 8-bit counter is available as a prescaler for the Timer0 module. The prescaler is not directly readable or writable; its value is set by the PSA and T0PS2:T0PS0 bits (T0CON<3:0>) which determine the prescaler assignment and prescale ratio.

Clearing the PSA bit assigns the prescaler to the Timer0 module. When it is assigned, prescale values from 1:2 through 1:256 in power-of-2 increments are selectable.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g., CLRF TMR0, MOVWF TMR0, BSF TMR0, etc.) clear the prescaler count.

| Note: | Writing to TMR0 when the prescaler is       |

|-------|---------------------------------------------|

|       | assigned to Timer0 will clear the prescaler |

|       | count but will not change the prescaler     |

|       | assignment.                                 |

#### 11.3.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control and can be changed "on-the-fly" during program execution.

# 11.4 Timer0 Interrupt

The TMR0 interrupt is generated when the TMR0 register overflows from FFh to 00h in 8-bit mode, or from FFFFh to 0000h in 16-bit mode. This overflow sets the TMR0IF flag bit. The interrupt can be masked by clearing the TMR0IE bit (INTCON<5>). Before reenabling the interrupt, the TMR0IF bit must be cleared in software by the Interrupt Service Routine.

Since Timer0 is shut down in Sleep mode, the TMR0 interrupt cannot awaken the processor from Sleep.

TABLE 11-1:

REGISTERS ASSOCIATED WITH TIMER0

| Name   | Bit 7                                                       | Bit 6         | Bit 5      | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Reset<br>Values<br>on page |

|--------|-------------------------------------------------------------|---------------|------------|-------|-------|-------|-------|-------|----------------------------|

| TMR0L  | Timer0 Module Low Byte Register                             |               |            |       |       |       |       |       | 50                         |

| TMR0H  | Timer0 Moc                                                  | lule High Byt | e Register |       |       |       |       |       | 50                         |

| INTCON | ON GIE/GIEH PEIE/GIEL TMROIE INTOIE RBIE TMROIF INTOIF RBIF |               |            |       |       |       |       | 49    |                            |

| T0CON  | TMR0ON T08BIT T0CS T0SE PSA T0PS2 T0PS1 T0PS0               |               |            |       |       |       |       |       | 50                         |

| TRISA  | PORTA Data Direction Register                               |               |            |       |       |       |       |       | 52                         |

**Legend:** x = unknown, u = unchanged, — = unimplemented locations, read as '0'. Shaded cells are not used by Timer0.

NOTES:

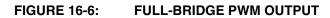

#### 16.4.5 FULL-BRIDGE MODE

In Full-Bridge Output mode, four pins are used as outputs; however, only two outputs are active at a time. In the Forward mode, pin P1A is continuously active and pin P1D is modulated. In the Reverse mode, pin P1C is continuously active and pin P1B is modulated. These are illustrated in Figure 16-6. P1A, P1B, P1C and P1D outputs are multiplexed with the PORTD<4>, PORTD<5>, PORTD<6> and PORTD<7> data latches. The TRISD<4>, TRISD<5>, TRISD<6> and TRISD<7> bits must be cleared to make the P1A, P1B, P1C and P1D pins outputs.

## 18.1 Baud Rate Generator (BRG)

The BRG is a dedicated 8-bit or 16-bit generator that supports both the Asynchronous and Synchronous modes of the EUSART. By default, the BRG operates in 8-bit mode; setting the BRG16 bit (BAUDCON<3>) selects 16-bit mode.

The SPBRGH:SPBRG register pair controls the period of a free running timer. In Asynchronous mode, bits BRGH (TXSTA<2>) and BRG16 (BAUDCON<3>) also control the baud rate. In Synchronous mode, BRGH is ignored. Table 18-1 shows the formula for computation of the baud rate for different EUSART modes which only apply in Master mode (internally generated clock).

Given the desired baud rate and FOSC, the nearest integer value for the SPBRGH:SPBRG registers can be calculated using the formulas in Table 18-1. From this, the error in baud rate can be determined. An example calculation is shown in Example 18-1. Typical baud rates and error values for the various Asynchronous modes are shown in Table 18-2. It may be advantageous to use the high baud rate (BRGH = 1) or the 16-bit BRG to reduce the baud rate error, or achieve a slow baud rate for a fast oscillator frequency.

Writing a new value to the SPBRGH:SPBRG registers causes the BRG timer to be reset (or cleared). This ensures the BRG does not wait for a timer overflow before outputting the new baud rate.

#### 18.1.1 OPERATION IN POWER MANAGED MODES

The device clock is used to generate the desired baud rate. When one of the power managed modes is entered, the new clock source may be operating at a different frequency. This may require an adjustment to the value in the SPBRG register pair.

### 18.1.2 SAMPLING

The data on the RX pin is sampled three times by a majority detect circuit to determine if a high or a low level is present at the RX pin.

| Co   | onfiguration B | its | BRG/EUSART Mode     | Baud Rate Formula  |  |  |

|------|----------------|-----|---------------------|--------------------|--|--|

| SYNC | BRG16 BRGH     |     | BRG/EUSANT Mode     | Baud hate Formula  |  |  |

| 0    | 0              | 0   | 8-bit/Asynchronous  | Fosc/[64 (n + 1)]  |  |  |

| 0    | 0              | 1   | 8-bit/Asynchronous  | Fosc/[16 (n + 1)]  |  |  |

| 0    | 1              | 0   | 16-bit/Asynchronous | F050/[10 (11 + 1)] |  |  |

| 0    | 1              | 1   | 16-bit/Asynchronous |                    |  |  |

| 1    | 1 0            |     | 8-bit/Synchronous   | Fosc/[4 (n + 1)]   |  |  |

| 1    | 1              | x   | 16-bit/Synchronous  |                    |  |  |

TABLE 18-1: BAUD RATE FORMULAS

**Legend:** x = Don't care, n = value of SPBRGH:SPBRG register pair

### EXAMPLE 18-1: CALCULATING BAUD RATE ERROR

| For a device with Fosc | For a device with FOSC of 16 MHz, desired baud rate of 9600, Asynchronous mode, 8-bit BRG: |  |  |  |  |  |  |

|------------------------|--------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Desired Baud Rate      | Desired Baud Rate = $Fosc/(64 ([SPBRGH:SPBRG] + 1))$                                       |  |  |  |  |  |  |

| Solving for SPBRGH:S   | SPBRG:                                                                                     |  |  |  |  |  |  |

| X                      | = ((Fosc/Desired Baud Rate)/64) – 1                                                        |  |  |  |  |  |  |

|                        | = ((1600000/9600)/64) - 1                                                                  |  |  |  |  |  |  |

|                        | = [25.042] = 25                                                                            |  |  |  |  |  |  |

| Calculated Baud Rate   | = 1600000/(64(25+1))                                                                       |  |  |  |  |  |  |

|                        | = 9615                                                                                     |  |  |  |  |  |  |

| Error                  | = (Calculated Baud Rate – Desired Baud Rate)/Desired Baud Rate                             |  |  |  |  |  |  |

|                        | = (9615 - 9600)/9600 = 0.16%                                                               |  |  |  |  |  |  |

### TABLE 18-2: REGISTERS ASSOCIATED WITH BAUD RATE GENERATOR

| Name                                                 | Bit 7      | Bit 6                                   | Bit 5      | Bit 4        | Bit 3      | Bit 2      | Bit 1 | Bit 0 | Reset<br>Values<br>on page |

|------------------------------------------------------|------------|-----------------------------------------|------------|--------------|------------|------------|-------|-------|----------------------------|

| TXSTA                                                | CSRC       | TX9                                     | TXEN       | SYNC         | SENDB      | BRGH       | TRMT  | TX9D  | 51                         |

| RCSTA                                                | SPEN       | SPEN RX9 SREN CREN ADDEN FERR OERR RX9D |            |              |            |            | 51    |       |                            |

| BAUDCON                                              | ABDOVF     | RCIDL                                   | —          | SCKP         | BRG16      | —          | WUE   | ABDEN | 51                         |

| SPBRGH EUSART Baud Rate Generator Register High Byte |            |                                         |            |              |            |            |       | •     | 51                         |

| SPBRG EUSART Baud Rate Generator Register Low Byte   |            |                                         |            |              |            |            |       | 51    |                            |

| Legend: —                                            | = unimplem | ented read                              | as '0' Sha | ded cells ar | e not used | hy the BBG |       |       |                            |

Legend: — = unimplemented, read as '0'. Shaded cells are not used by the BRG.

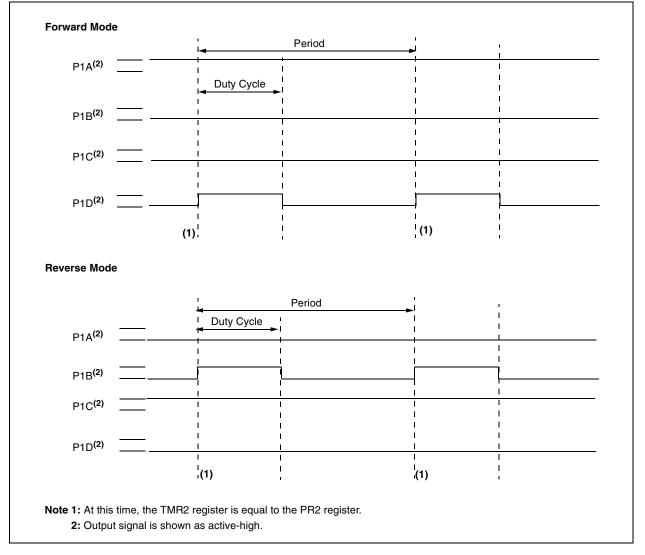

#### FIGURE 18-12: SYNCHRONOUS TRANSMISSION (THROUGH TXEN)

### TABLE 18-7: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER TRANSMISSION

| Name    | Bit 7                                         | Bit 6       | Bit 5  | Bit 4  | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

|---------|-----------------------------------------------|-------------|--------|--------|-------|--------|--------|--------|----------------------------|

| INTCON  | GIE/GIEH                                      | PEIE/GIEL   | TMR0IE | INT0IE | RBIE  | TMR0IF | INT0IF | RBIF   | 49                         |

| PIR1    | PSPIF <sup>(1)</sup>                          | ADIF        | RCIF   | TXIF   | SSPIF | CCP1IF | TMR2IF | TMR1IF | 52                         |

| PIE1    | PSPIE <sup>(1)</sup>                          | ADIE        | RCIE   | TXIE   | SSPIE | CCP1IE | TMR2IE | TMR1IE | 52                         |

| IPR1    | PSPIP <sup>(1)</sup>                          | ADIP        | RCIP   | TXIP   | SSPIP | CCP1IP | TMR2IP | TMR1IP | 52                         |

| RCSTA   | SPEN                                          | RX9         | SREN   | CREN   | ADDEN | FERR   | OERR   | RX9D   | 51                         |

| TXREG   | EUSART T                                      | ransmit Reg | ister  |        |       |        |        |        | 51                         |

| TXSTA   | CSRC                                          | TX9         | TXEN   | SYNC   | SENDB | BRGH   | TRMT   | TX9D   | 51                         |

| BAUDCON | ABDOVF                                        | RCIDL       |        | SCKP   | BRG16 | —      | WUE    | ABDEN  | 51                         |

| SPBRGH  | EUSART Baud Rate Generator Register High Byte |             |        |        |       |        |        |        | 51                         |

| SPBRG   | EUSART Baud Rate Generator Register Low Byte  |             |        |        |       |        |        | 51     |                            |

Legend: — = unimplemented, read as '0'. Shaded cells are not used for synchronous master transmission.

**Note 1:** Reserved in PIC18F2X8X devices; always maintain these bits clear.

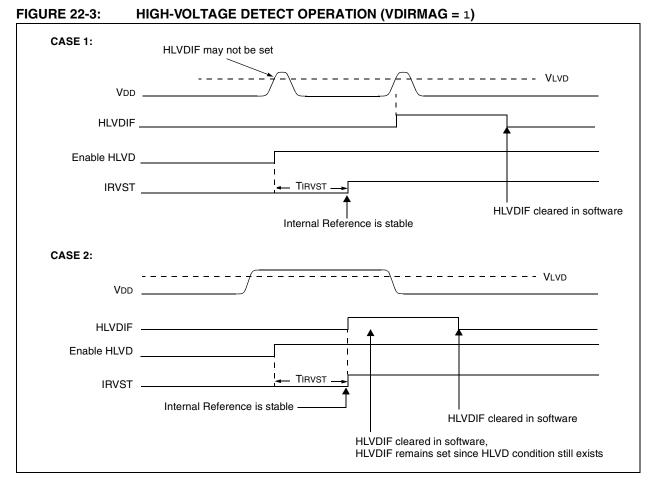

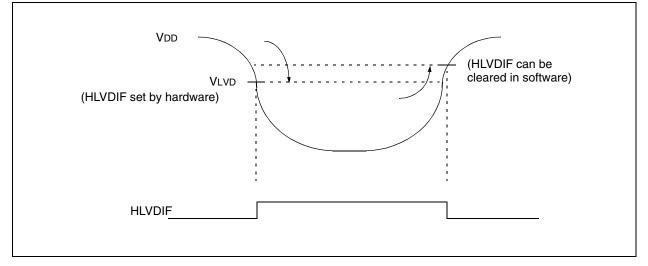

## 22.5 Applications

In many applications, the ability to detect a drop below, or rise above a particular threshold is desirable. For example, the HLVD module could be periodically enabled to detect Universal Serial Bus (USB) attach or detach. This assumes the device is powered by a lower voltage source than the USB when detached. An attach would indicate a high-voltage detect from, for example, 3.3V to 5V (the voltage on USB) and vice versa for a detach. This feature could save a design a few extra components and an attach signal (input pin).

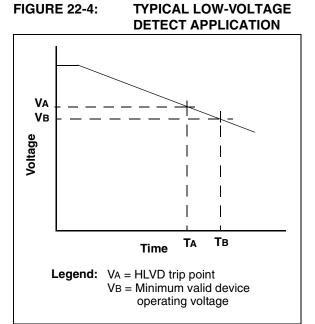

For general battery applications, Figure 22-4 shows a possible voltage curve. Over time, the device voltage decreases. When the device voltage reaches voltage VA, the HLVD logic generates an interrupt at time TA. The interrupt could cause the execution of an ISR, which would allow the application to perform "house-keeping tasks" and perform a controlled shutdown before the device voltage exits the valid operating range at TB. The HLVD, thus, would give the application a time window, represented by the difference between TA and TB, to safely exit.

DS39625C-page 274

'0' = Bit is cleared

x = Bit is unknown

#### **REGISTER 23-16: RXBnSIDL: RECEIVE BUFFER n STANDARD IDENTIFIER REGISTERS,** I OW BYTE [0 < n < 1]

|         | LOW BY I                              | E [0 ≤ n ≤     | 1]              |                |              |             |              |            |

|---------|---------------------------------------|----------------|-----------------|----------------|--------------|-------------|--------------|------------|

|         | R-x                                   | R-x            | R-x             | R-x            | R-x          | U-0         | R-x          | R-x        |

|         | SID2                                  | SID1           | SID0            | SRR            | EXID         | —           | EID17        | EID16      |

|         | bit 7                                 |                |                 |                |              |             |              | bit 0      |

|         |                                       |                |                 |                |              |             |              |            |

| bit 7-5 | SID2:SID0:                            | : Standard I   | dentifier bits  | (if EXID = $0$ | )            |             |              |            |

|         | Extended lo                           | dentifier bits | EID20:EID1      | 18 (if EXID =  | :1).         |             |              |            |

| bit 4   | SRR: Subs                             | titute Remo    | te Request l    | oit            |              |             |              |            |

|         | This bit is a EXID = 0.               | lways 'o' wł   | nen EXID = 1    | 1 or equal to  | the value of | f RXRTRRC   | (RBXnCON     | I<3>) when |

| bit 3   | EXID: Exte                            | nded Identif   | ier bit         |                |              |             |              |            |

|         | 1 = Receive                           | ed message     | is an exten     | ded data fra   | me, SID10:8  | SID0 are EI | 028:EID18    |            |

|         | 0 = Receive                           | ed message     | e is a standa   | rd data fram   | е            |             |              |            |

| bit 2   | Unimplem                              | ented: Read    | <b>d as</b> '0' |                |              |             |              |            |

| bit 1-0 | EID17:EID16: Extended Identifier bits |                |                 |                |              |             |              |            |

|         |                                       |                |                 |                |              |             |              |            |

|         | Legend:                               |                |                 |                |              |             |              |            |

|         | R = Readab                            | ole bit        | W = Writat      | ole bit        | U = Unim     | plemented   | bit, read as | 0'         |

# REGISTER 23-17: RXBnEIDH: RECEIVE BUFFER n EXTENDED IDENTIFIER REGISTERS, HIGH BYTE $[0 \le n \le 1]$

'1' = Bit is set

| R-x   | R-x   | R-x   | R-x   | R-x   | R-x   | R-x  | R-x   |

|-------|-------|-------|-------|-------|-------|------|-------|

| EID15 | EID14 | EID13 | EID12 | EID11 | EID10 | EID9 | EID8  |

| bit 7 |       |       |       |       |       |      | bit 0 |

#### bit 7-0 EID15:EID8: Extended Identifier bits

-n = Value at POR

| Legend:           |                  |                                          |  |

|-------------------|------------------|------------------------------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0'       |  |

| -n = Value at POR | '1' = Bit is set | 0' = Bit is cleared $x = Bit is unknown$ |  |

# REGISTER 23-18: RXBnEIDL: RECEIVE BUFFER n EXTENDED IDENTIFIER REGISTERS,

LOW BYTE  $[0 \le n \le 1]$

| R-x   | R-x  | R-x  | R-x  | R-x  | R-x  | R-x  | R-x   |

|-------|------|------|------|------|------|------|-------|

| EID7  | EID6 | EID5 | EID4 | EID3 | EID2 | EID1 | EID0  |

| bit 7 |      |      |      |      |      |      | bit 0 |

#### bit 7-0 **EID7:EID0:** Extended Identifier bits

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

Move Indexed to f

MOVSF [zs], fd

$0 \leq z_s \leq 127$  $0 \leq f_d \leq 4095$

MOVSF

Syntax:

Operands:

| CAL                                                                                              | .LW            | Subrouti                                                                                                                                                        | Subroutine Call Using WREG                                                                                              |                                                                                                            |                                                                                |  |  |  |

|--------------------------------------------------------------------------------------------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|--|--|--|

| Synta                                                                                            | ax:            | CALLW                                                                                                                                                           |                                                                                                                         |                                                                                                            |                                                                                |  |  |  |

| Oper                                                                                             | ands:          | None                                                                                                                                                            |                                                                                                                         |                                                                                                            |                                                                                |  |  |  |

| Oper                                                                                             | ation:         | (PC + 2) -<br>$(W) \rightarrow PCI$<br>(PCLATH)<br>(PCLATU)                                                                                                     | $\rightarrow$ PCH,                                                                                                      |                                                                                                            |                                                                                |  |  |  |

| Statu                                                                                            | s Affected:    | None                                                                                                                                                            |                                                                                                                         |                                                                                                            |                                                                                |  |  |  |

| Enco                                                                                             | ding:          | 0000                                                                                                                                                            | 0000                                                                                                                    | 0001                                                                                                       | 0100                                                                           |  |  |  |

| Desc                                                                                             | ription        | First, the re<br>pushed on<br>contents of<br>existing va<br>contents of<br>latched inter<br>respectivel<br>executed a<br>new next in<br>Unlike CAI<br>update W, | to the retu<br>f W are wi<br>lue is disc<br>f PCLATH<br>o PCH an<br>y. The sec<br>is a NOP i<br>nstruction<br>CL, there | urn stack<br>ritten to<br>carded. 1<br>and PC<br>d PCU,<br>cond cyc<br>nstructio<br>is fetche<br>is no opt | Next, the<br>PCL; the<br>Then, the<br>LATU are<br>cle is<br>n while the<br>ed. |  |  |  |

| Word                                                                                             | ls:            | 1                                                                                                                                                               | 1                                                                                                                       |                                                                                                            |                                                                                |  |  |  |

| Cycle                                                                                            | es:            | 2                                                                                                                                                               |                                                                                                                         |                                                                                                            |                                                                                |  |  |  |

| QC                                                                                               | ycle Activity: |                                                                                                                                                                 |                                                                                                                         |                                                                                                            |                                                                                |  |  |  |

|                                                                                                  | Q1             | Q2                                                                                                                                                              | Q3                                                                                                                      |                                                                                                            | Q4                                                                             |  |  |  |

|                                                                                                  | Decode         | Read<br>WREG                                                                                                                                                    | Push Po<br>stack                                                                                                        |                                                                                                            | No<br>operation                                                                |  |  |  |

|                                                                                                  | No             | No                                                                                                                                                              | No                                                                                                                      |                                                                                                            | No                                                                             |  |  |  |

|                                                                                                  | operation      | operation                                                                                                                                                       | operati                                                                                                                 | ion c                                                                                                      | operation                                                                      |  |  |  |

| Example: HERE CALLW<br>Before Instruction<br>PC = address (HERE)<br>PCLATH = 10h<br>PCLATU = 00h |                |                                                                                                                                                                 |                                                                                                                         |                                                                                                            |                                                                                |  |  |  |

|                                                                                                  | W              | = 06h                                                                                                                                                           |                                                                                                                         |                                                                                                            |                                                                                |  |  |  |

001006h address (HERE + 2) 10h 00h 06h

| Operation:       |     | ((FSR2) +                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | $z_s) \rightarrow f_d$ |                                                                                                                                                                                        |   |                   |

|------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-------------------|

| Status Affected: |     | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                        |                                                                                                                                                                                        |   |                   |

| Encoding:        |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                        |                                                                                                                                                                                        |   |                   |

| 1st word (source | e)  | 1110                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1011                   | 0 z z                                                                                                                                                                                  |   | ZZZZS             |

| 2nd word (destir | า.) | 1111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ffff                   | fff                                                                                                                                                                                    | f | ffff <sub>d</sub> |

| Description:     |     | moved to destination register 'f <sub>d</sub> '. The actual address of the source register is determined by adding the 7-bit literal offset ' $z_s$ ' in the first word to the value of FSR2. The address of the destination register is specified by the 12-bit literal 'f <sub>d</sub> ' in the second word. Both addresse can be anywhere in the 4096-byte data space (000h to FFFh). The MOVSF instruction cannot use the PCL, TOSU, TOSH or TOSL as the destination register. If the resultant source address points to |                        | urce register is<br>e 7-bit literal<br>d to the value of<br>he destination<br>he 12-bit literal<br>Both addresses<br>4096-byte data<br>annot use the<br>OSL as the<br>ddress points to |   |                   |

|                  |     | an indirect<br>value retur                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                        |                                                                                                                                                                                        |   | , the             |

| Words:           |     | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                        |                                                                                                                                                                                        |   |                   |

| Cycles:          |     | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                        |                                                                                                                                                                                        |   |                   |

| Q Cycle Activity | /:  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                        |                                                                                                                                                                                        |   |                   |

| Q1               |     | Q2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Q3                     | 3                                                                                                                                                                                      |   | Q4                |

| Decode           | Г   | Determine                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Determ                 | nine                                                                                                                                                                                   |   | Read              |

| Q1     | Q2                          | Q3              | Q4                              |

|--------|-----------------------------|-----------------|---------------------------------|

| Decode | Determine                   | Determine       | Read                            |

|        | source addr                 | source addr     | source reg                      |

| Decode | No<br>operation<br>No dummy | No<br>operation | Write<br>register 'f'<br>(dest) |

|        | read                        |                 | (uoot)                          |

| Example: | MOVSF | [05h], | REG2 |

|----------|-------|--------|------|

|----------|-------|--------|------|

| •                  |   |      |

|--------------------|---|------|

| Before Instruction |   |      |

| FSR2               | = | 80h  |

| Contents<br>of 85h | _ | 33h  |

| BFG2               | = | 11h  |

|                    | = | 1111 |

| After Instruction  |   |      |

| FSR2               | = | 80h  |

| Contents           |   |      |

| of 85h             | = | 33h  |

| REG2               | = | 33h  |

|                    |   |      |

After Instruction