Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 40MHz                                                                      |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                |

| Number of I/O              | 36                                                                         |

| Program Memory Size        | 64KB (32K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 1K x 8                                                                     |

| RAM Size                   | 3.25K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                                |

| Data Converters            | A/D 11x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-VQFN Exposed Pad                                                        |

| Supplier Device Package    | 44-QFN (8x8)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f4680t-i-ml |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TABLE 2-2:CAPACITOR SELECTION FOR<br/>CRYSTAL OSCILLATOR

| Osc Type | Crystal | Typical Capacitor Value<br>Tested: |       |  |  |

|----------|---------|------------------------------------|-------|--|--|

|          | Freq    | C1                                 | C2    |  |  |

| LP       | 32 kHz  | 33 pF                              | 33 pF |  |  |

|          | 200 kHz | 15 pF                              | 15 pF |  |  |

| XT       | 1 MHz   | 33 pF                              | 33 pF |  |  |

|          | 4 MHz   | 27 pF                              | 27 pF |  |  |

| HS       | 4 MHz   | 27 pF                              | 27 pF |  |  |

|          | 8 MHz   | 22 pF                              | 22 pF |  |  |

|          | 20 MHz  | 15 pF                              | 15 pF |  |  |

|          |         |                                    |       |  |  |

#### Capacitor values are for design guidance only.

These capacitors were tested with the crystals listed below for basic start-up and operation. **These values are not optimized.**

Different capacitor values may be required to produce acceptable oscillator operation. The user should test the performance of the oscillator over the expected VDD and temperature range for the application.

See the notes following this table for additional information.

| Crystals Used: |        |  |  |  |  |  |

|----------------|--------|--|--|--|--|--|

| 32 kHz         | 4 MHz  |  |  |  |  |  |

| 200 kHz        | 8 MHz  |  |  |  |  |  |

| 1 MHz          | 20 MHz |  |  |  |  |  |

- Note 1: Higher capacitance increases the stability of the oscillator but also increases the start-up time.

- 2: When operating below 3V VDD, or when using certain ceramic resonators at any voltage, it may be necessary to use the HS mode or switch to a crystal oscillator.

- 3: Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components.

- 4: Rs may be required to avoid overdriving crystals with low drive level specification.

- 5: Always verify oscillator performance over the VDD and temperature range that is expected for the application.

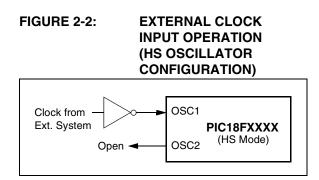

An external clock source may also be connected to the OSC1 pin in the HS mode, as shown in Figure 2-2.

# 2.3 External Clock Input

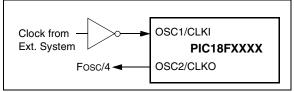

The EC and ECIO Oscillator modes require an external clock source to be connected to the OSC1 pin. There is no oscillator start-up time required after a Power-on Reset or after an exit from Sleep mode.

In the EC Oscillator mode, the oscillator frequency divided by 4 is available on the OSC2 pin. This signal may be used for test purposes or to synchronize other logic. Figure 2-3 shows the pin connections for the EC Oscillator mode.

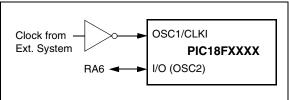

### FIGURE 2-3: EXTERNAL CLOCK INPUT OPERATION (EC CONFIGURATION)

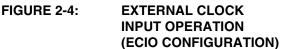

The ECIO Oscillator mode functions like the EC mode, except that the OSC2 pin becomes an additional general purpose I/O pin. The I/O pin becomes bit 6 of PORTA (RA6). Figure 2-4 shows the pin connections for the ECIO Oscillator mode.

# 4.5 Device Reset Timers

PIC18F2585/2680/4585/4680 devices incorporate three separate on-chip timers that help regulate the Power-on Reset process. Their main function is to ensure that the device clock is stable before code is executed. These timers are:

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- PLL Lock Time-out

#### 4.5.1 POWER-UP TIMER (PWRT)

The Power-up Timer (PWRT) of PIC18F2585/2680/ 4585/4680 devices is an 11-bit counter which uses the INTRC source as the clock input. This yields an approximate time interval of 2048 x 32  $\mu$ s = 65.6 ms. While the PWRT is counting, the device is held in Reset.

The power-up time delay depends on the INTRC clock and will vary from chip to chip due to temperature and process variation. See DC parameter 33 for details.

The PWRT is enabled by clearing the PWRTEN Configuration bit.

#### 4.5.2 OSCILLATOR START-UP TIMER (OST)

The Oscillator Start-up Timer (OST) provides a 1024 oscillator cycle (from OSC1 input) delay after the PWRT delay is over (parameter 33). This ensures that the crystal oscillator or resonator has started and stabilized.

The OST time-out is invoked only for XT, LP, HS and HSPLL modes and only on Power-on Reset or on exit from most power managed modes.

#### 4.5.3 PLL LOCK TIME-OUT

With the PLL enabled in its PLL mode, the time-out sequence following a Power-on Reset is slightly different from other oscillator modes. A separate timer is used to provide a fixed time-out that is sufficient for the PLL to lock to the main oscillator frequency. This PLL lock time-out (TPLL) is typically 2 ms and follows the oscillator start-up time-out.

#### 4.5.4 TIME-OUT SEQUENCE

On power-up, the time-out sequence is as follows:

- 1. After the POR pulse has cleared, PWRT time-out is invoked (if enabled).

- 2. Then, the OST is activated.

The total time-out will vary based on oscillator configuration and the status of the PWRT. Figure 4-3, Figure 4-4, Figure 4-5, Figure 4-6 and Figure 4-7 all depict time-out sequences on power-up, with the Power-up Timer enabled and the device operating in HS Oscillator mode. Figures 4-3 through 4-6 also apply to devices operating in XT or LP modes. For devices in RC mode and with the PWRT disabled, on the other hand, there will be no time-out at all.

Since the time-outs occur from the POR pulse, if  $\overline{\text{MCLR}}$  is kept low long enough, all time-outs will expire. Bringing  $\overline{\text{MCLR}}$  high will begin execution immediately (Figure 4-5). This is useful for testing purposes or to synchronize more than one PIC18FXXXX device operating in parallel.

| Oscillator<br>Configuration | Power-up <sup>(2)</sup> an                             | Exit from                       |                                 |

|-----------------------------|--------------------------------------------------------|---------------------------------|---------------------------------|

|                             | <b>PWRTEN</b> = 0                                      | <b>PWRTEN</b> = 1               | Power Managed Mode              |

| HSPLL                       | 66 ms <sup>(1)</sup> + 1024 Tosc + 2 ms <sup>(2)</sup> | 1024 Tosc + 2 ms <sup>(2)</sup> | 1024 Tosc + 2 ms <sup>(2)</sup> |

| HS, XT, LP                  | 66 ms <sup>(1)</sup> + 1024 Tosc                       | 1024 Tosc                       | 1024 Tosc                       |

| EC, ECIO                    | 66 ms <sup>(1)</sup>                                   | _                               | _                               |

| RC, RCIO                    | 66 ms <sup>(1)</sup>                                   | _                               | —                               |

| INTIO1, INTIO2              | 66 ms <sup>(1)</sup>                                   | _                               | _                               |

TABLE 4-2:TIME-OUT IN VARIOUS SITUATIONS

**Note 1:** 66 ms (65.5 ms) is the nominal Power-up Timer (PWRT) delay.

2: 2 ms is the nominal time required for the PLL to lock.

# TABLE 5-1:SPECIAL FUNCTION REGISTER MAP FOR<br/>PIC18F2585/2680/4585/4680 DEVICES (CONTINUED)

| Address | Name                  | Address | Name                  | Address | Name                  | Address | Name                  |

|---------|-----------------------|---------|-----------------------|---------|-----------------------|---------|-----------------------|

| E7Fh    | CANCON_RO4            | E6Fh    | CANCON_RO5            | E5Fh    | CANCON_RO6            | E4Fh    | CANCON_RO7            |

| E7Eh    | CANSTAT_RO4           | E6Eh    | CANSTAT_RO5           | E5Eh    | CANSTAT_RO6           | E4Eh    | CANSTAT_RO7           |

| E7Dh    | B5D7 <sup>(2)</sup>   | E6Dh    | B4D7 <sup>(2)</sup>   | E5Dh    | B3D7 <sup>(2)</sup>   | E4Dh    | B2D7 <sup>(2)</sup>   |

| E7Ch    | B5D6 <sup>(2)</sup>   | E6Ch    | B4D6 <sup>(2)</sup>   | E5Ch    | B3D6 <sup>(2)</sup>   | E4Ch    | B2D6 <sup>(2)</sup>   |

| E7Bh    | B5D5 <sup>(2)</sup>   | E6Bh    | B4D5 <sup>(2)</sup>   | E5Bh    | B3D5 <sup>(2)</sup>   | E4Bh    | B2D5 <sup>(2)</sup>   |

| E7Ah    | B5D4 <sup>(2)</sup>   | E6Ah    | B4D4 <sup>(2)</sup>   | E5Ah    | B3D4 <sup>(2)</sup>   | E4Ah    | B2D4 <sup>(2)</sup>   |

| E79h    | B5D3 <sup>(2)</sup>   | E69h    | B4D3 <sup>(2)</sup>   | E59h    | B3D3 <sup>(2)</sup>   | E49h    | B2D3 <sup>(2)</sup>   |

| E78h    | B5D2 <sup>(2)</sup>   | E68h    | B4D2 <sup>(2)</sup>   | E58h    | B3D2 <sup>(2)</sup>   | E48h    | B2D2 <sup>(2)</sup>   |

| E77h    | B5D1 <sup>(2)</sup>   | E67h    | B4D1 <sup>(2)</sup>   | E57h    | B3D1 <sup>(2)</sup>   | E47h    | B2D1 <sup>(2)</sup>   |

| E76h    | B5D0 <sup>(2)</sup>   | E66h    | B4D0 <sup>(2)</sup>   | E56h    | B3D0 <sup>(2)</sup>   | E46h    | B2D0 <sup>(2)</sup>   |

| E75h    | B5DLC <sup>(2)</sup>  | E65h    | B4DLC <sup>(2)</sup>  | E55h    | B3DLC <sup>(2)</sup>  | E45h    | B2DLC <sup>(2)</sup>  |

| E74h    | B5EIDL <sup>(2)</sup> | E64h    | B4EIDL <sup>(2)</sup> | E54h    | B3EIDL <sup>(2)</sup> | E44h    | B2EIDL <sup>(2)</sup> |

| E73h    | B5EIDH <sup>(2)</sup> | E63h    | B4EIDH <sup>(2)</sup> | E53h    | B3EIDH <sup>(2)</sup> | E43h    | B2EIDH <sup>(2)</sup> |

| E72h    | B5SIDL <sup>(2)</sup> | E62h    | B4SIDL <sup>(2)</sup> | E52h    | B3SIDL <sup>(2)</sup> | E42h    | B2SIDL <sup>(2)</sup> |

| E71h    | B5SIDH <sup>(2)</sup> | E61h    | B4SIDH <sup>(2)</sup> | E51h    | B3SIDH <sup>(2)</sup> | E41h    | B2SIDH <sup>(2)</sup> |

| E70h    | B5CON <sup>(2)</sup>  | E60h    | B4CON <sup>(2)</sup>  | E50h    | B3CON <sup>(2)</sup>  | E40h    | B2CON <sup>(2)</sup>  |

| E3Fh    | CANCON_RO8            | E2Fh    | CANCON_RO9            | E1Fh    | —                     | E0Fh    | —                     |

| E3Eh    | CANSTAT_RO8           | E2Eh    | CANSTAT_RO9           | E1Eh    | —                     | E0Eh    | —                     |

| E3Dh    | B1D7 <sup>(2)</sup>   | E2Dh    | B0D7 <sup>(2)</sup>   | E1Dh    | —                     | E0Dh    | —                     |

| E3Ch    | B1D6 <sup>(2)</sup>   | E2Ch    | B0D6 <sup>(2)</sup>   | E1Ch    | —                     | E0Ch    | —                     |

| E3Bh    | B1D5 <sup>(2)</sup>   | E2Bh    | B0D5 <sup>(2)</sup>   | E1Bh    | —                     | E0Bh    | —                     |

| E3Ah    | B1D4 <sup>(2)</sup>   | E2Ah    | B0D4 <sup>(2)</sup>   | E1Ah    | _                     | E0Ah    | _                     |

| E39h    | B1D3 <sup>(2)</sup>   | E29h    | B0D3 <sup>(2)</sup>   | E19h    | —                     | E09h    | —                     |

| E38h    | B1D2 <sup>(2)</sup>   | E28h    | B0D2 <sup>(2)</sup>   | E18h    | —                     | E08h    | —                     |

| E37h    | B1D1 <sup>(2)</sup>   | E27h    | B0D1 <sup>(2)</sup>   | E17h    | —                     | E07h    | —                     |

| E36h    | B1D0 <sup>(2)</sup>   | E26h    | B0D0 <sup>(2)</sup>   | E16h    | —                     | E06h    | —                     |

| E35h    | B1DLC <sup>(2)</sup>  | E25h    | B0DLC <sup>(2)</sup>  | E15h    | —                     | E05h    | —                     |

| E34h    | B1EIDL <sup>(2)</sup> | E24h    | B0EIDL <sup>(2)</sup> | E14h    | _                     | E04h    | _                     |

| E33h    | B1EIDH <sup>(2)</sup> | E23h    | B0EIDH <sup>(2)</sup> | E13h    | _                     | E03h    | _                     |

| E32h    | B1SIDL <sup>(2)</sup> | E22h    | B0SIDL <sup>(2)</sup> | E12h    | _                     | E02h    | _                     |

| E31h    | B1SIDH <sup>(2)</sup> | E21h    | B0SIDH <sup>(2)</sup> | E11h    | _                     | E01h    |                       |

| E30h    | B1CON <sup>(2)</sup>  | E20h    | B0CON <sup>(2)</sup>  | E10h    | _                     | E00h    | —                     |

Note 1: Registers available only on PIC18F4X8X devices; otherwise, the registers read as '0'.

2: When any TX\_ENn bit in RX\_TX\_SELn is set, then the corresponding bit in this register has transmit properties.

3: This is not a physical register.

#### 5.4 Data Addressing Modes

| Note: | The execution of some instructions in the core PIC18 instruction set are changed when the PIC18 extended instruction |

|-------|----------------------------------------------------------------------------------------------------------------------|

|       | set is enabled. See Section 5.6 "Data<br>Memory and the Extended Instruction<br>Set" for more information.           |

While the program memory can be addressed in only one way – through the program counter – information in the data memory space can be addressed in several ways. For most instructions, the addressing mode is fixed. Other instructions may use up to three modes, depending on which operands are used and whether or not the extended instruction set is enabled.

The addressing modes are:

- Inherent

- Literal

- Direct

- Indirect

An additional addressing mode, Indexed Literal Offset, is available when the extended instruction set is enabled (XINST Configuration bit = 1). Its operation is discussed in greater detail in **Section 5.6.1** "**Indexed Addressing with Literal Offset**".

# 5.4.1 INHERENT AND LITERAL ADDRESSING

Many PIC18 control instructions do not need any argument at all; they either perform an operation that globally affects the device or they operate implicitly on one register. This addressing mode is known as Inherent Addressing. Examples include SLEEP, RESET and DAW.

Other instructions work in a similar way but require an additional explicit argument in the opcode. This is known as Literal Addressing mode because they require some literal value as an argument. Examples include ADDLW and MOVLW which, respectively, add or move a literal value to the W register. Other examples include CALL and GOTO, which include a 20-bit program memory address.

#### 5.4.2 DIRECT ADDRESSING

Direct addressing specifies all or part of the source and/or destination address of the operation within the opcode itself. The options are specified by the arguments accompanying the instruction.

In the core PIC18 instruction set, bit-oriented and byte-oriented instructions use some version of direct addressing by default. All of these instructions include some 8-bit literal address as their Least Significant Byte. This address specifies either a register address in one of the banks of data RAM (Section 5.3.3 "General **Purpose Register File**") or a location in the Access Bank (Section 5.3.2 "Access Bank") as the data source for the instruction.

The Access RAM bit 'a' determines how the address is interpreted. When 'a' is '1', the contents of the BSR (Section 5.3.1 "Bank Select Register (BSR)") are used with the address to determine the complete 12-bit address of the register. When 'a' is '0', the address is interpreted as being a register in the Access Bank. Addressing that uses the Access RAM is sometimes also known as Direct Forced Addressing mode.

A few instructions, such as MOVFF, include the entire 12-bit address (either source or destination) in their opcodes. In those cases, the BSR is ignored entirely.

The destination of the operation's results is determined by the destination bit 'd'. When 'd' is '1', the results are stored back in the source register, overwriting its original contents. When 'd' is '0', the results are stored in the W register. Instructions without the 'd' argument have a destination that is implicit in the instruction; their destination is either the target register being operated on or the W register.

#### 5.4.3 INDIRECT ADDRESSING

Indirect addressing allows the user to access a location in data memory without giving a fixed address in the instruction. This is done by using File Select Registers (FSRs) as pointers to the locations to be read or written to. Since the FSRs are themselves located in RAM as Special File Registers, they can also be directly manipulated under program control. This makes FSRs very useful in implementing data structures, such as tables and arrays in data memory.

The registers for indirect addressing are also implemented with Indirect File Operands (INDFs) that permit automatic manipulation of the pointer value with auto-incrementing, auto-decrementing or offsetting with another value. This allows for efficient code, using loops, such as the example of clearing an entire RAM bank in Example 5-5.

#### EXAMPLE 5-5: HOW TO CLEAR RAM (BANK 1) USING INDIRECT ADDRESSING

|         | LFSR  | FSR0, 100h | ; |                |

|---------|-------|------------|---|----------------|

| NEXT    | CLRF  | POSTINC0   | ; | Clear INDF     |

|         |       |            | ; | register then  |

|         |       |            | ; | inc pointer    |

|         | BTFSS | FSR0H, 1   | ; | All done with  |

|         |       |            | ; | Bank1?         |

|         | BRA   | NEXT       | ; | NO, clear next |

| CONTINU | JE    |            | ; | YES, continue  |

|         |       |            |   |                |

# PIC18F2585/2680/4585/4680

| <b>REGISTER 9-2:</b> | 2: INTCON2: INTERRUPT CONTROL REGISTER 2                                   |               |              |                |              |           |              |        |

|----------------------|----------------------------------------------------------------------------|---------------|--------------|----------------|--------------|-----------|--------------|--------|

|                      | R/W-1                                                                      | R/W-1         | R/W-1        | R/W-1          | U-0          | R/W-1     | U-0          | R/W-1  |

|                      | RBPU                                                                       | INTEDG0       | INTEDG1      | INTEDG2        | —            | TMR0IP    | _            | RBIP   |

|                      | bit 7                                                                      |               |              |                |              |           |              | bit 0  |

|                      |                                                                            |               |              |                |              |           |              |        |

| bit 7                | RBPU: PO                                                                   | RTB Pull-up   | Enable bit   |                |              |           |              |        |

|                      |                                                                            | RTB pull-up   |              |                |              |           |              |        |

|                      | 0 = PORT                                                                   | B pull-ups a  | re enabled b | y individual p | ort latch va | ues       |              |        |

| bit 6                | INTEDG0:                                                                   | External Inte | errupt 0 Edg | e Select bit   |              |           |              |        |

|                      |                                                                            | pt on rising  |              |                |              |           |              |        |

|                      |                                                                            | pt on falling | 0            |                |              |           |              |        |

| bit 5                |                                                                            | External Inte | 1 0          | e Select bit   |              |           |              |        |

|                      |                                                                            | pt on rising  | 0            |                |              |           |              |        |

|                      |                                                                            | pt on falling | 0            |                |              |           |              |        |

| bit 4                |                                                                            | External Inte |              | e Select bit   |              |           |              |        |

|                      |                                                                            | pt on rising  | •            |                |              |           |              |        |

|                      | 0 = Interrupt on falling edge                                              |               |              |                |              |           |              |        |

| bit 3                | Unimplemented: Read as '0'<br>TMR0IP: TMR0 Overflow Interrupt Priority bit |               |              |                |              |           |              |        |

| bit 2                |                                                                            |               |              |                |              |           |              |        |

|                      | 1 = High p                                                                 | ,             |              |                |              |           |              |        |

|                      | 0 = Low pl                                                                 | •             |              |                |              |           |              |        |

| bit 1                | •                                                                          | ented: Read   |              |                |              |           |              |        |

| bit 0                | RBIP: RB Port Change Interrupt Priority bit                                |               |              |                |              |           |              |        |

|                      | 1 = High p                                                                 | •             |              |                |              |           |              |        |

|                      | 0 = Low pr                                                                 | riority       |              |                |              |           |              |        |

|                      |                                                                            |               |              |                |              |           |              |        |

|                      | Legend:                                                                    |               |              |                |              |           |              |        |

|                      | R = Reada                                                                  | able bit      | W = W        | /ritable bit   | U = Unim     | plemented | bit, read as | '0'    |

|                      | -n = Value                                                                 | at POR        | '1' = B      | it is set      | '0' = Bit is | s cleared | x = Bit is u | nknown |

**Note:** Interrupt flag bits are set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the global interrupt enable bit. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt. This feature allows for software polling.

# PIC18F2585/2680/4585/4680

| R/W-1                                                                                                                                             | R/W-1         | U-0           | R/W-0                      | R/W-0        | U-0          | R/W-0  | R/W-0 |

|---------------------------------------------------------------------------------------------------------------------------------------------------|---------------|---------------|----------------------------|--------------|--------------|--------|-------|

| INT2IP                                                                                                                                            | INT1IP        |               | INT2IE                     | INT1IE       | —            | INT2IF | INT1I |

| bit 7                                                                                                                                             |               |               | ·                          |              |              |        | b     |

| INT2IP: INT                                                                                                                                       | 2 External I  | nterrupt Pr   | iority bit                 |              |              |        |       |

| 1 = High prior 0 = Low prior 1                                                                                                                    | ,             |               |                            |              |              |        |       |

| INT1IP: INT                                                                                                                                       | 1 External I  | nterrupt Pr   | iority bit                 |              |              |        |       |

| 1 = High pr                                                                                                                                       | riority       |               | -                          |              |              |        |       |

| 0 = Low pri                                                                                                                                       | ority         |               |                            |              |              |        |       |

| Unimpleme                                                                                                                                         | ented: Read   | <b>as</b> '0' |                            |              |              |        |       |

| INT2IE: INT                                                                                                                                       | 2 External I  | nterrupt Er   | nable bit                  |              |              |        |       |

| <ul> <li>1 = Enables the INT2 external interrupt</li> <li>0 = Disables the INT2 external interrupt</li> </ul>                                     |               |               |                            |              |              |        |       |

| INT1IE: INT1 External Interrupt Enable bit                                                                                                        |               |               |                            |              |              |        |       |

| <ul> <li>1 = Enables the INT1 external interrupt</li> <li>0 = Disables the INT1 external interrupt</li> </ul>                                     |               |               |                            |              |              |        |       |

| Unimplemented: Read as '0'                                                                                                                        |               |               |                            |              |              |        |       |

| INT2IF: INT2 External Interrupt Flag bit                                                                                                          |               |               |                            |              |              |        |       |

| <ul> <li>1 = The INT2 external interrupt occurred (must be cleared in software)</li> <li>0 = The INT2 external interrupt did not occur</li> </ul> |               |               |                            |              |              |        |       |

| INT1IF: INT                                                                                                                                       | 1 External li | nterrupt Fla  | ag bit                     |              |              |        |       |

|                                                                                                                                                   |               |               | curred (mus<br>d not occur | t be cleared | in software) | I      |       |

#### **REGISTER 9-**

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

|                   |                  |                      |                    |

Interrupt flag bits are set when an interrupt condition occurs regardless of the state Note: of its corresponding enable bit or the global interrupt enable bit. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt. This feature allows for software polling.

# 14.2 Timer3 16-Bit Read/Write Mode

Timer3 can be configured for 16-bit reads and writes (see Figure 14-2). When the RD16 control bit (T3CON<7>) is set, the address for TMR3H is mapped to a buffer register for the high byte of Timer3. A read from TMR3L will load the contents of the high byte of Timer3 into the Timer3 High Byte Buffer register. This provides the user with the ability to accurately read all 16 bits of Timer1 without having to determine whether a read of the high byte, followed by a read of the low byte, has become invalid due to a rollover between reads.

A write to the high byte of Timer3 must also take place through the TMR3H Buffer register. The Timer3 high byte is updated with the contents of TMR3H when a write occurs to TMR3L. This allows a user to write all 16 bits to both the high and low bytes of Timer3 at once.

The high byte of Timer3 is not directly readable or writable in this mode. All reads and writes must take place through the Timer3 High Byte Buffer register.

Writes to TMR3H do not clear the Timer3 prescaler. The prescaler is only cleared on writes to TMR3L.

## 14.3 Using the Timer1 Oscillator as the Timer3 Clock Source

The Timer1 internal oscillator may be used as the clock source for Timer3. The Timer1 oscillator is enabled by setting the T1OSCEN (T1CON<3>) bit. To use it as the Timer3 clock source, the TMR3CS bit must also be set. As previously noted, this also configures Timer3 to increment on every rising edge of the oscillator source.

The Timer1 oscillator is described in Section 12.0 "Timer1 Module".

# 14.4 Timer3 Interrupt

The TMR3 register pair (TMR3H:TMR3L) increments from 0000h to FFFFh and overflows to 0000h. The Timer3 interrupt, if enabled, is generated on overflow and is latched in the interrupt flag bit, TMR3IF (PIR2<1>). This interrupt can be enabled or disabled by setting or clearing the Timer3 Interrupt Enable bit, TMR3IE (PIE2<1>).

# 14.5 Resetting Timer3 Using the ECCP1 Special Event Trigger

If the ECCP1 module is configured to generate a special event trigger in Compare mode (ECCP1M3:ECCP1M0 = 1011), this signal will reset Timer3. It will also start an A/D conversion if the A/D module is enabled (see Section 15.3.4 "Special Event Trigger" for more information.).

The module must be configured as either a timer or synchronous counter to take advantage of this feature. When used this way, the ECCPR1H:ECCPR1L register pair effectively becomes a period register for Timer3.

If Timer3 is running in Asynchronous Counter mode, the Reset operation may not work.

In the event that a write to Timer3 coincides with a special event trigger from a CCP1 module, the write will take precedence.

Note: The special event triggers from the ECCP1 module will not set the TMR3IF interrupt flag bit (PIR1<0>).

| Name   | Bit 7                      | Bit 6                  | Bit 5   | Bit 4   | Bit 3                 | Bit 2         | Bit 1  | Bit 0                  | Reset<br>Values<br>on page |

|--------|----------------------------|------------------------|---------|---------|-----------------------|---------------|--------|------------------------|----------------------------|

| INTCON | GIE/GIEH                   | PEIE/GIEL              | TMR0IE  | INT0IE  | RBIE                  | TMR0IF        | INTOIF | RBIF                   | 49                         |

| PIR2   | OSCFIF                     | CMIF <sup>(2)</sup>    | _       | EEIF    | BCLIF                 | HLVDIF        | TMR3IF | ECCP1IF <sup>(2)</sup> | 51                         |

| PIE2   | OSCFIE                     | CMIE <sup>(2)</sup>    | —       | EEIE    | BCLIE                 | HLVDIE        | TMR3IE | ECCP1IE <sup>(2)</sup> | 52                         |

| IPR2   | OSCFIP                     | CMIP <sup>(2)</sup>    | —       | EEIP    | BCLIP                 | HLVDIP        | TMR3IP | ECCP1IP <sup>(2)</sup> | 51                         |

| TMR3L  | Timer3 Register, Low Byte  |                        |         |         |                       |               |        |                        | 51                         |

| TMR3H  | Timer3 Register, High Byte |                        |         |         |                       |               |        | 51                     |                            |

| T1CON  | RD16                       | T1RUN                  | T1CKPS1 | T1CKPS0 | T1OSCEN               | T1SYNC        | TMR1CS | TMR1ON                 | 50                         |

| T3CON  | RD16                       | T3ECCP1 <sup>(1)</sup> | T3CKPS1 | T3CKPS0 | T3CCP1 <sup>(1)</sup> | <b>T3SYNC</b> | TMR3CS | TMR3ON                 | 51                         |

TABLE 14-1:

REGISTERS ASSOCIATED WITH TIMER3 AS A TIMER/COUNTER

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by the Timer3 module.

**Note 1:** These bits are available in PIC18F4X8X devices only.

2: These bits are available in PIC18F4X8X devices and reserved in PIC18F2X8X devices.

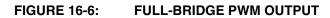

#### 16.4.5 FULL-BRIDGE MODE

In Full-Bridge Output mode, four pins are used as outputs; however, only two outputs are active at a time. In the Forward mode, pin P1A is continuously active and pin P1D is modulated. In the Reverse mode, pin P1C is continuously active and pin P1B is modulated. These are illustrated in Figure 16-6. P1A, P1B, P1C and P1D outputs are multiplexed with the PORTD<4>, PORTD<5>, PORTD<6> and PORTD<7> data latches. The TRISD<4>, TRISD<5>, TRISD<6> and TRISD<7> bits must be cleared to make the P1A, P1B, P1C and P1D pins outputs.

# 17.0 MASTER SYNCHRONOUS SERIAL PORT (MSSP) MODULE

#### 17.1 Master SSP (MSSP) Module Overview

The Master Synchronous Serial Port (MSSP) module is a serial interface, useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial EEPROMs, shift registers, display drivers, A/D converters, etc. The MSSP module can operate in one of two modes:

- Serial Peripheral Interface (SPI)

- Inter-Integrated Circuit (I<sup>2</sup>C)

- Full Master mode

- Slave mode (with general address call)

The  ${\rm I}^2{\rm C}$  interface supports the following modes in hardware:

- Master mode

- Multi-Master mode

- Slave mode

# 17.2 Control Registers

The MSSP module has three associated registers. These include a status register (SSPSTAT) and two control registers (SSPCON1 and SSPCON2). The use of these registers and their individual configuration bits differ significantly depending on whether the MSSP module is operated in SPI or  $I^2C$  mode.

Additional details are provided under the individual sections.

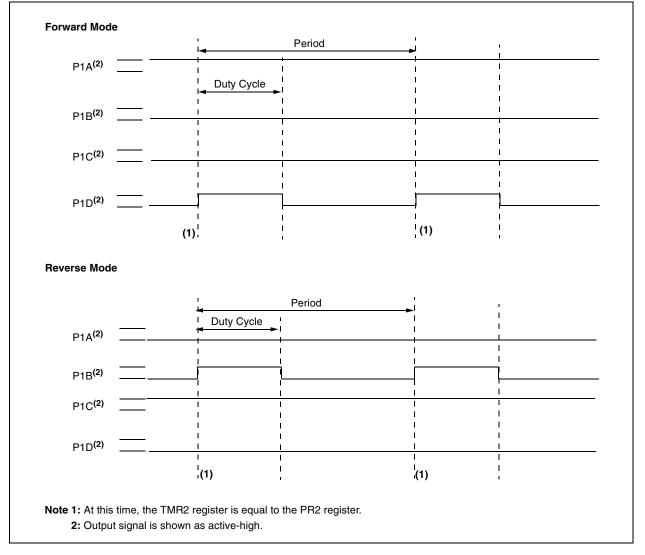

### 17.3 SPI Mode

The SPI mode allows 8 bits of data to be synchronously transmitted and received simultaneously. All four modes of SPI are supported. To accomplish communication, typically three pins are used:

- Serial Data Out (SDO) RC5/SDO

- Serial Data In (SDI) RC4/SDI/SDA

- Serial Clock (SCK) RC3/SCK/SCL

Additionally, a fourth pin may be used when in a Slave mode of operation:

• Slave Select (SS) - RA5/AN4/SS/HLVDIN

Figure 17-1 shows the block diagram of the MSSP module when operating in SPI mode.

# FIGURE 17-1: MSSP BLOCK DIAGRAM (SPI MODE)

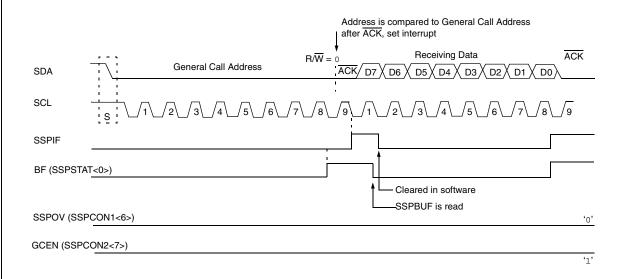

#### 17.4.5 GENERAL CALL ADDRESS SUPPORT

The addressing procedure for the I<sup>2</sup>C bus is such that the first byte after the Start condition usually determines which device will be the slave addressed by the master. The exception is the general call address which can address all devices. When this address is used, all devices should, in theory, respond with an Acknowledge.

The general call address is one of eight addresses reserved for specific purposes by the  $I^2C$  protocol. It consists of all '0's with R/W = 0.

The general call address is recognized when the General Call Enable bit, GCEN, is enabled (SSPCON2<7> set). Following a Start bit detect, 8 bits are shifted into the SSPSR and the address is compared against the SSPADD. It is also compared to the general call address and fixed in hardware.

If the general call address matches, the SSPSR is transferred to the SSPBUF, the BF flag bit is set (eighth bit) and on the falling edge of the ninth bit (ACK bit), the SSPIF interrupt flag bit is set.

When the interrupt is serviced, the source for the interrupt can be checked by reading the contents of the SSPBUF. The value can be used to determine if the address was device specific or a general call address.

In 10-bit mode, the SSPADD is required to be updated for the second half of the address to match and the UA bit is set (SSPSTAT<1>). If the general call address is sampled when the GCEN bit is set, while the slave is configured in 10-bit Address mode, then the second half of the address is not necessary, the UA bit will not be set and the slave will begin receiving data after the Acknowledge (Figure 17-15).

#### 18.1.3 AUTO-BAUD RATE DETECT

The Enhanced USART module supports the automatic detection and calibration of baud rate. This feature is active only in Asynchronous mode and while the WUE bit is clear.

The automatic baud rate measurement sequence (Figure 18-1) begins whenever a Start bit is received and the ABDEN bit is set. The calculation is self-averaging.

In the Auto-Baud Rate Detect (ABD) mode, the clock to the BRG is reversed. Rather than the BRG clocking the incoming RX signal, the RX signal is timing the BRG. In ABD mode, the internal Baud Rate Generator is used as a counter to time the bit period of the incoming serial byte stream.

Once the ABDEN bit is set, the state machine will clear the BRG and look for a Start bit. The Auto-Baud Rate Detection must receive a byte with the value 55h (ASCII "U", which is also the LIN bus Sync character) in order to calculate the proper bit rate. The measurement is taken over both a low and a high bit time in order to minimize any effects caused by asymmetry of the incoming signal. After a Start bit, the SPBRG begins counting up, using the preselected clock source on the first rising edge of RX. After eight bits on the RX pin or the fifth rising edge, an accumulated value totalling the proper BRG period is left in the SPBRGH:SPBRG register pair. Once the 5th edge is seen (this should correspond to the Stop bit), the ABDEN bit is automatically cleared.

If a rollover of the BRG occurs (an overflow from FFFFh to 0000h), the event is trapped by the ABDOVF status bit (BAUDCON<7>). It is set in hardware by BRG rollovers and can be set or cleared by the user in software. ABD mode remains active after rollover events and the ABDEN bit remains set (Figure 18-2).

While calibrating the baud rate period, the BRG registers are clocked at 1/8th the preconfigured clock rate. Note that the BRG clock will be configured by the BRG16 and BRGH bits. Independent of the BRG16 bit setting, both the SPBRG and SPBRGH will be used as a 16-bit counter. This allows the user to verify that no carry occurred for 8-bit modes by checking for 00h in the SPBRGH register. Refer to Table 18-4 for counter clock rates to the BRG.

While the ABD sequence takes place, the EUSART state machine is held in Idle. The RCIF interrupt is set once the fifth rising edge on RX is detected. The value in the RCREG needs to be read to clear the RCIF interrupt. The contents of RCREG should be discarded.

- Note 1: If the WUE bit is set with the ABDEN bit, Auto-Baud Rate Detection will occur on the byte *following* the Break character.

- 2: It is up to the user to determine that the incoming character baud rate is within the range of the selected BRG clock source. Some combinations of oscillator frequency and EUSART baud rates are not possible due to bit error rates. Overall system timing and communication baud rates must be taken into consideration when using the Auto-Baud Rate Detection feature.

# TABLE 18-4:BRG COUNTERCLOCK RATES

| BRG16 | BRGH | BRG Counter Clock |  |  |  |  |

|-------|------|-------------------|--|--|--|--|

| 0     | 0    | Fosc/512          |  |  |  |  |

| 0     | 1    | Fosc/128          |  |  |  |  |

| 1     | 0    | Fosc/128          |  |  |  |  |

| 1     | 1    | Fosc/32           |  |  |  |  |

**Note:** During the ABD sequence, SPBRG and SPBRGH are both used as a 16-bit counter, independent of the BRG16 setting.

#### 18.1.3.1 ABD and EUSART Transmission

Since the BRG clock is reversed during ABD acquisition, the EUSART transmitter cannot be used during ABD. This means that whenever the ABDEN bit is set, TXREG cannot be written to. Users should also ensure that ABDEN does not become set during a transmit sequence. Failing to do this may result in unpredictable EUSART operation.

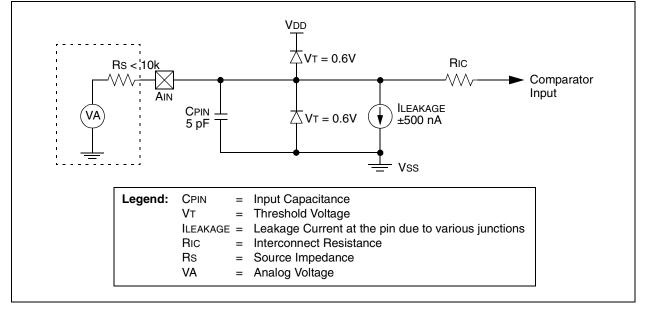

# 20.9 Analog Input Connection Considerations

A simplified circuit for an analog input is shown in Figure 20-4. Since the analog pins are connected to a digital output, they have reverse biased diodes to VDD and Vss. The analog input, therefore, must be between Vss and VDD. If the input voltage deviates from this

range by more than 0.6V in either direction, one of the diodes is forward biased and a latch-up condition may occur. A maximum source impedance of 10 k $\Omega$  is recommended for the analog sources. Any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have very little leakage current.

# FIGURE 20-4: COMPARATOR ANALOG INPUT MODEL

#### TABLE 20-1: REGISTERS ASSOCIATED WITH COMPARATOR MODULE

| Name                  | Bit 7                 | Bit 6                 | Bit 5     | Bit 4        | Bit 3      | Bit 2  | Bit 1  | Bit 0                  | Reset<br>Values<br>on page |

|-----------------------|-----------------------|-----------------------|-----------|--------------|------------|--------|--------|------------------------|----------------------------|

| CMCON <sup>(3)</sup>  | C2OUT                 | C1OUT                 | C2INV     | C1INV        | CIS        | CM2    | CM1    | CM0                    | 51                         |

| CVRCON <sup>(3)</sup> | CVREN                 | CVROE                 | CVRR      | CVRSS        | CVR3       | CVR2   | CVR1   | CVR0                   | 51                         |

| INTCON                | GIE/GIEH              | PEIE/GIEL             | TMR0IE    | INT0IE       | RBIE       | TMR0IF | INT0IF | RBIF                   | 52                         |

| IPR2                  | OSCFIP                | CMIP <sup>(2)</sup>   | _         | EEIP         | BCLIP      | HLVDIP | TMR3IP | ECCP1IP <sup>(2)</sup> | 51                         |

| PIR2                  | OSCFIF                | CMIF <sup>(2)</sup>   | _         | EEIF         | BCLIF      | HLVDIF | TMR3IF | ECCP1IF <sup>(2)</sup> | 51                         |

| PIE2                  | OSCFIE                | CMIE <sup>(2)</sup>   | _         | EEIE         | BCLIE      | HLVDIE | TMR3IE | ECCP1IE <sup>(2)</sup> | 52                         |

| PORTA                 | RA7 <sup>(1)</sup>    | RA6 <sup>(1)</sup>    | RA5       | RA4          | RA3        | RA2    | RA1    | RA0                    | 52                         |

| LATA                  | LATA7 <sup>(1)</sup>  | LATA6 <sup>(1)</sup>  | LATA Data | Output Re    | gister     |        |        |                        | 52                         |

| TRISA                 | TRISA7 <sup>(1)</sup> | TRISA6 <sup>(1)</sup> | PORTA Da  | ata Directio | n Register |        |        |                        | 52                         |

Legend: — = unimplemented, read as '0'. Shaded cells are unused by the comparator module.

Note 1: PORTA pins are enabled based on oscillator configuration.

2: These bits are available in PIC18F4X8X devices and reserved in PIC18F2X8X devices.

3: These registers are unimplemented on PIC18F2X8X devices.

#### EXAMPLE 23-1: CHANGING TO CONFIGURATION MODE

```

; Request Configuration mode.

MOVLW B'1000000'

; Set to Configuration Mode.

MOVWF CANCON

; A request to switch to Configuration mode may not be immediately honored.

; Module will wait for CAN bus to be idle before switching to Configuration Mode.

; Request for other modes such as Loopback, Disable etc. may be honored immediately.

; It is always good practice to wait and verify before continuing.

ConfigWait:

MOVF CANSTAT, W

; Read current mode state.

ANDLW B'1000000'

; Interested in OPMODE bits only.

TSTFSZ WREG

; Is it Configuration mode yet?

; No. Continue to wait...

BRA ConfigWait

; Module is in Configuration mode now.

; Modify configuration registers as required.

; Switch back to Normal mode to be able to communicate.

```

# EXAMPLE 23-2: WIN AND ICODE BITS USAGE IN INTERRUPT SERVICE ROUTINE TO ACCESS TX/RX BUFFERS

```

; Save application required context.

; Poll interrupt flags and determine source of interrupt

; This was found to be CAN interrupt

; TempCANCON and TempCANSTAT are variables defined in Access Bank low

MOVFF CANCON, TempCANCON

; Save CANCON.WIN bits

; This is required to prevent CANCON

; from corrupting CAN buffer access

; in-progress while this interrupt

; occurred

MOVFF CANSTAT, TempCANSTAT

; Save CANSTAT register

; This is required to make sure that

; we use same CANSTAT value rather

; than one changed by another CAN

; interrupt.

; Retrieve ICODE bits

MOVF

TempCANSTAT, W

ANDLW B'00001110'

ADDWF PCL, F

; Perform computed GOTO

; to corresponding interrupt cause

; 000 = No interrupt

BRA

NoInterrupt

; 001 = Error interrupt

; 010 = TXB2 interrupt

ErrorInterrupt

BRA

TXB2Interrupt

BRA

BRA TXB1Interrupt

; 011 = TXB1 interrupt

BRA TXB0Interrupt

; 100 = TXB0 interrupt

BRA RXB1Interrupt

; 101 = RXB1 interrupt

BRA RXB0Interrupt

; 110 = RXB0 interrupt

; 111 = Wake-up on interrupt

WakeupInterrupt

BCF PIR3, WAKIF

; Clear the interrupt flag

; User code to handle wake-up procedure

;

;

; Continue checking for other interrupt source or return from here

NoInterrupt

; PC should never vector here. User may

; place a trap such as infinite loop or pin/port

; indication to catch this error.

```

|         | R/W-0                                                                                                                | R/W-0                                                                                  | R/W-0                                                                                                    | R/W-0                            | R/W-0         | R/W-0       | R/W-0          | R/W-0  |

|---------|----------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|----------------------------------|---------------|-------------|----------------|--------|

|         | SEG2PHTS                                                                                                             | SAM                                                                                    | SEG1PH2                                                                                                  | SEG1PH1                          | SEG1PH0       | PRSEG2      | PRSEG1         | PRSEG0 |

|         | bit 7                                                                                                                |                                                                                        |                                                                                                          |                                  |               |             |                | bit 0  |

|         |                                                                                                                      |                                                                                        |                                                                                                          |                                  |               |             |                |        |

| bit 7   | SEG2PHTS:                                                                                                            | Phase Seg                                                                              | gment 2 Tim                                                                                              | e Select bit                     |               |             |                |        |

|         | 1 = Freely pr<br>0 = Maximun                                                                                         | •                                                                                      |                                                                                                          | tion Process                     | sing Time (IP | T), whichev | ver is greate  | r      |

| bit 6   | SAM: Sampl                                                                                                           | e of the CA                                                                            | N bus Line                                                                                               | bit                              |               |             |                |        |

|         | 1 = Bus line i<br>0 = Bus line i                                                                                     |                                                                                        |                                                                                                          | •                                |               | t           |                |        |

| bit 5-3 | SEG1PH2:S                                                                                                            | EG1PH0: F                                                                              | hase Segm                                                                                                | ent 1 bits                       |               |             |                |        |

|         | 111 = Phase<br>110 = Phase<br>101 = Phase<br>010 = Phase<br>011 = Phase<br>010 = Phase<br>001 = Phase<br>000 = Phase | Segment<br>Segment<br>Segment<br>Segment<br>Segment                                    | 1  time = 7  x<br>1  time = 6  x<br>1  time = 5  x<br>1  time = 4  x<br>1  time = 3  x<br>1  time = 2  x | Ta<br>Ta<br>Ta<br>Ta<br>Ta<br>Ta |               |             |                |        |

| bit 2-0 | PRSEG2:PR                                                                                                            | SEG0: Pro                                                                              | pagation Tir                                                                                             | ne Select bi                     | ts            |             |                |        |

|         | 111 = Propa<br>110 = Propa<br>101 = Propa<br>100 = Propa<br>011 = Propa<br>010 = Propa<br>001 = Propa                | gation time<br>gation time<br>gation time<br>gation time<br>gation time<br>gation time | = 7 x TQ<br>= 6 x TQ<br>= 5 x TQ<br>= 4 x TQ<br>= 3 x TQ<br>= 2 x TQ                                     |                                  |               |             |                |        |

|         | Legend:                                                                                                              |                                                                                        |                                                                                                          |                                  |               |             |                |        |

|         | R = Readable                                                                                                         | e bit                                                                                  | W = Writab                                                                                               | le bit                           | U = Unim      | plemented b | oit, read as ' | 0'     |

'0' = Bit is cleared

#### REGISTER 23-53: BRGCON2: BAUD RATE CONTROL REGISTER 2

'1' = Bit is set

-n = Value at POR

x = Bit is unknown

### 23.7.3 ENHANCED FIFO MODE

When configured for Mode 2, two of the dedicated receive buffers in combination with one or more programmable transmit/receive buffers, are used to create a maximum of an 8 buffer deep FIFO buffer. In this mode, there is no direct correlation between filters and receive buffer registers. Any filter that has been enabled can generate an acceptance. When a message has been accepted, it is stored in the next available receive buffer register and an internal write pointer is incremented. The FIFO can be a maximum of 8 buffers deep. The entire FIFO must consist of contiguous receive buffers. The FIFO head begins at RXB0 buffer and its tail spans toward B5. The maximum length of the FIFO is limited by the presence or absence of the first transmit buffer starting from B0. If a buffer is configured as a transmit buffer, the FIFO length is reduced accordingly. For instance, if B3 is configured as a transmit buffer, the actual FIFO will consist of RXB0, RXB1, B0, B1 and B2, a total of 5 buffers. If B0 is configured as a transmit buffer, the FIFO length will be 2. If none of the programmable buffers are configured as a transmit buffer, the FIFO will be 8 buffers deep. A system that requires more transmit buffers should try to locate transmit buffers at the very end of B0-B5 buffers to maximize available FIFO length.

When a message is received in FIFO mode, the interrupt flag code bits (EICODE<4:0>) in the CANSTAT register will have a value of '10000', indicating the FIFO has received a message. FIFO Pointer bits, FP<3:0> in the CANCON register, point to the buffer that contains data not yet read. The FIFO pointer bits, in this sense, serve as the FIFO read pointer. The user should use FP bits and read corresponding buffer data. When receive data is no longer needed, the RXFUL bit in the current buffer must be cleared, causing FP<3:0> to be updated by the module.

To determine whether FIFO is empty or not, the user may use FP<3:0> bits to access the RXFUL bit in the current buffer. If RXFUL is cleared, the FIFO is considered to be empty. If it is set, the FIFO may contain one or more messages. In Mode 2, the module also provides a bit called FIFO High Water Mark (FIFOWM) in the ECANCON register. This bit can be used to cause an interrupt whenever the FIFO contains only one or four empty buffers. The FIFO high water mark interrupt can serve as an early warning to a full FIFO condition.

### 23.7.4 TIME-STAMPING

The CAN module can be programmed to generate a time-stamp for every message that is received. When enabled, the module generates a capture signal for CCP1, which in turn captures the value of either Timer1 or Timer3. This value can be used as the message time-stamp.

To use the time-stamp capability, the CANCAP bit (CIOCAN<4>) must be set. This replaces the capture input for CCP1 with the signal generated from the CAN module. In addition, CCP1CON<3:0> must be set to '0011' to enable the CCP special event trigger for CAN events.

## 23.8 Message Acceptance Filters and Masks

The message acceptance filters and masks are used to determine if a message in the Message Assembly Buffer should be loaded into any of the receive buffers. Once a valid message has been received into the MAB, the identifier fields of the message are compared to the filter values. If there is a match, that message will be loaded into the appropriate receive buffer. The filter masks are used to determine which bits in the identifier are examined with the filters. A truth table is shown below in Table 23-2 that indicates how each bit in the identifier is compared to the masks and filters to determine if a message should be loaded into a receive buffer. The mask essentially determines which bits to apply the acceptance filters to. If any mask bit is set to a zero, then that bit will automatically be accepted regardless of the filter bit.

| TABLE 23-2: F | ILTER/MASK TRUTH TABLE |

|---------------|------------------------|

|---------------|------------------------|

| Mask<br>bit n | Filter<br>bit n | Message<br>Identifier<br>bit n001 | Accept or<br>Reject<br>bit n |

|---------------|-----------------|-----------------------------------|------------------------------|

| 0             | х               | x                                 | Accept                       |

| 1             | 0               | 0                                 | Accept                       |

| 1             | 0               | 1                                 | Reject                       |

| 1             | 1               | 0                                 | Reject                       |

| 1             | 1               | 1                                 | Accept                       |

**Legend:** x = don't care

In Mode 0, acceptance filters RXF0 and RXF1 and filter mask RXM0 are associated with RXB0. Filters RXF2, RXF3, RXF4 and RXF5 and mask RXM1 are associated with RXB1.

### 26.11 PICSTART Plus Development Programmer

The PICSTART Plus Development Programmer is an easy-to-use, low-cost, prototype programmer. It connects to the PC via a COM (RS-232) port. MPLAB Integrated Development Environment software makes using the programmer simple and efficient. The PICSTART Plus Development Programmer supports most PIC devices in DIP packages up to 40 pins. Larger pin count devices, such as the PIC16C92X and PIC17C76X, may be supported with an adapter socket. The PICSTART Plus Development Programmer is CE compliant.

# 26.12 PICkit 2 Development Programmer

The PICkit<sup>™</sup> 2 Development Programmer is a low-cost programmer and selected Flash device debugger with an easy-to-use interface for programming many of Microchip's baseline, mid-range and PIC18F families of Flash memory microcontrollers. The PICkit 2 Starter Kit includes a prototyping development board, twelve sequential lessons, software and HI-TECH's PICC<sup>™</sup> Lite C compiler, and is designed to help get up to speed quickly using PIC<sup>®</sup> microcontrollers. The kit provides everything needed to program, evaluate and develop applications using Microchip's powerful, mid-range Flash memory family of microcontrollers.

# 26.13 Demonstration, Development and Evaluation Boards

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart<sup>®</sup> battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Check the Microchip web page (www.microchip.com) and the latest *"Product Selector Guide"* (DS00148) for the complete list of demonstration, development and evaluation kits.

# 27.2 DC Characteristics: Power-Down and Supply Current PIC18F2585/2680/4585/4680 (Industrial) PIC18LF2585/2680/4585/4680 (Industrial) (Continued)

| PIC18LF<br>(Indus | <b>2585/2680/4585/4680</b><br>strial)   | <b>Standar</b><br>Operatin | •     | 0     | •                                                                                                             | nditions (unless otherwise stated)<br>$-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial |                                            |  |  |  |

|-------------------|-----------------------------------------|----------------------------|-------|-------|---------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|--------------------------------------------|--|--|--|

|                   | 585/2680/4585/4680<br>strial, Extended) | <b>Standar</b><br>Operatin | •     | •     | conditions (unless otherwise stated)<br>-40°C ≤ TA ≤ +85°C for industrial<br>-40°C ≤ TA ≤ +125°C for extended |                                                                                             |                                            |  |  |  |

| Param Device      |                                         | Тур                        | Max   | Units | Conditions                                                                                                    |                                                                                             |                                            |  |  |  |

|                   | Supply Current (IDD) <sup>(2,3)</sup>   |                            |       |       |                                                                                                               |                                                                                             |                                            |  |  |  |

|                   | PIC18FX585/X680                         | 15.00                      | 23.00 | mA    | +125°C                                                                                                        | VDD = 4.2V                                                                                  | Fosc = 25 MHz                              |  |  |  |

|                   |                                         | 20.00                      | 31.00 | mA    | +125°C                                                                                                        | VDD = 5.0V                                                                                  | (PRI_RUN, EC oscillator)                   |  |  |  |

|                   | All devices                             | 30.00                      | 38.00 | mA    | -40°C                                                                                                         |                                                                                             |                                            |  |  |  |

|                   |                                         | 31.00                      | 38.00 | mA    | +25°C                                                                                                         | VDD = 4.2V                                                                                  |                                            |  |  |  |

|                   |                                         | 31.00                      | 38.00 | mA    | +85°C                                                                                                         |                                                                                             | Fosc = 40 MHz                              |  |  |  |

|                   | All devices                             | 37.00                      | 44.00 | mA    | -40°C                                                                                                         |                                                                                             | (PRI_RUN, EC oscillator)                   |  |  |  |

|                   |                                         | 38.00                      | 44.00 | mA    | +25°C                                                                                                         | VDD = 5.0V                                                                                  |                                            |  |  |  |

|                   |                                         | 39.00                      | 44.00 | mA    | +85°C                                                                                                         |                                                                                             |                                            |  |  |  |

|                   | All devices                             | 7.50                       | 16.00 | mA    | -40°C                                                                                                         |                                                                                             |                                            |  |  |  |

|                   |                                         | 7.40                       | 15.00 | mA    | +25°C                                                                                                         | VDD = 4.2V                                                                                  | Fosc = 4 MHz<br>( <b>PRI_RUN HS+PLL</b> )  |  |  |  |

|                   |                                         | 7.30                       | 14.00 | mA    | +85°C                                                                                                         |                                                                                             | (1 m_non 10 1 22)                          |  |  |  |

|                   | All devices                             | 10.00                      | 21.00 | mA    | -40°C                                                                                                         |                                                                                             |                                            |  |  |  |

|                   |                                         | 10.00                      | 20.00 | mA    | +25°C                                                                                                         | VDD = 5.0V                                                                                  | Fosc = 4 MHz<br>( <b>PRI_RUN HS+PLL</b> )  |  |  |  |

|                   |                                         | 9.70                       | 19.00 | mA    | +85°C                                                                                                         |                                                                                             | (                                          |  |  |  |

|                   | All devices                             | 17.00                      | 35.00 | mA    | -40°C                                                                                                         |                                                                                             |                                            |  |  |  |

|                   |                                         | 17.00                      | 35.00 | mA    | +25°C                                                                                                         | VDD = 4.2V                                                                                  | Fosc = 10 MHz<br>( <b>PRI_RUN HS+PLL</b> ) |  |  |  |

|                   |                                         | 17.00                      | 35.00 | mA    | +85°C                                                                                                         |                                                                                             | (····_································     |  |  |  |

|                   | All devices                             | 23.00                      | 40.00 | mA    | -40°C                                                                                                         |                                                                                             | E000 - 10 MHZ                              |  |  |  |

|                   |                                         | 23.00                      | 40.00 | mA    | +25°C                                                                                                         | VDD = 5.0V                                                                                  | Fosc = 10 MHz<br>( <b>PRI_RUN HS+PLL</b> ) |  |  |  |

|                   |                                         | 23.00                      | 40.00 | mA    | +85°C                                                                                                         |                                                                                             | ( ···_·································    |  |  |  |

Legend: Shading of rows is to assist in readability of the table.

Note 1: The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD or VSS and all features that add delta current disabled (such as WDT, Timer1 Oscillator, BOR, etc.).

2: The supply current is mainly a function of operating voltage, frequency and mode. Other factors, such as I/O pin loading and switching rate, oscillator type and circuit, internal code execution pattern and temperature, also have an impact on the current consumption. The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD;

$\overline{\text{MCLR}}$  = VDD; WDT enabled/disabled as specified.

**3:** For RC oscillator configurations, current through REXT is not included. The current through the resistor can be estimated by the formula Ir = VDD/2REXT (mA) with REXT in kΩ.

4: Standard low-cost 32 kHz crystals have an operating temperature range of -10°C to +70°C. Extended temperature crystals are available at a much higher cost.

| DC Cha       | racteris | stics                                                                |      |      |       |       | unless otherwise stated)<br>≤ +85°C for industrial               |

|--------------|----------|----------------------------------------------------------------------|------|------|-------|-------|------------------------------------------------------------------|

| Param<br>No. | Sym      | Characteristic                                                       | Min  | Тур† | Max   | Units | Conditions                                                       |

|              |          | Internal Program Memory<br>Programming Specifications <sup>(1)</sup> |      |      |       |       |                                                                  |

| D110         | Vpp      | Voltage on MCLR/VPP/RE3 pin                                          | 9.00 | —    | 13.25 | V     | (Note 3)                                                         |

| D113         | IDDP     | Supply Current during<br>Programming                                 | —    | —    | 10    | mA    |                                                                  |

|              |          | Data EEPROM Memory                                                   |      |      |       |       |                                                                  |

| D120         | ED       | Byte Endurance                                                       | 100K | 1M   |       | E/W   | -40°C to +85°C                                                   |

| D121         | Vdrw     | VDD for Read/Write                                                   | VMIN | —    | 5.5   | V     | Using EECON to read/write<br>VMIN = Minimum operating<br>voltage |

| D122         | TDEW     | Erase/Write Cycle Time                                               | —    | 4    | —     | ms    |                                                                  |

| D123         | TRETD    | Characteristic Retention                                             | 40   | —    | —     | Year  | Provided no other specifications are violated                    |

| D124         | TREF     | Number of Total Erase/Write<br>Cycles before Refresh <sup>(2)</sup>  | 1M   | 10M  | —     | E/W   | -40°C to +85°C                                                   |