#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 40MHz                                                                      |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 48KB (24K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 1K x 8                                                                     |

| RAM Size                   | 3.25K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                  |

| Data Converters            | A/D 8x10b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Through Hole                                                               |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                    |

| Supplier Device Package    | 28-SPDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf2585-i-sp |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

# QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV ISO/TS 16949:2002

#### Trademarks

The Microchip name and logo, the Microchip logo, Accuron, dsPIC, KEELOQ, KEELOQ logo, microID, MPLAB, PIC, PICmicro, PICSTART, PRO MATE, PowerSmart, rfPIC, and SmartShunt are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

AmpLab, FilterLab, Linear Active Thermistor, Migratable Memory, MXDEV, MXLAB, PS logo, SEEVAL, SmartSensor and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, ECAN, ECONOMONITOR, FanSense, FlexROM, fuzzyLAB, In-Circuit Serial Programming, ICSP, ICEPIC, Mindi, MiWi, MPASM, MPLAB Certified logo, MPLIB, MPLINK, PICkit, PICDEM, PICDEM.net, PICLAB, PICtail, PowerCal, PowerInfo, PowerMate, PowerTool, REAL ICE, rfLAB, rfPICDEM, Select Mode, Smart Serial, SmartTel, Total Endurance, UNI/O, WiperLock and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2007, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Microchip received ISO/TS-16949:2002 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona, Gresham, Oregon and Mountain View, California. The Company's quality system processes and procedures are for its PIC<sup>®</sup> MCUs and dsPIC<sup>®</sup> DSCs, KEELOC<sup>®</sup> code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

# 3.0 POWER MANAGED MODES

PIC18F2585/2680/4585/4680 devices offer a total of seven operating modes for more efficient power management. These modes provide a variety of options for selective power conservation in applications where resources may be limited (i.e., battery-powered devices).

There are three categories of power managed modes:

- Run modes

- Idle modes

- Sleep mode

These categories define which portions of the device are clocked and sometimes, what speed. The Run and Idle modes may use any of the three available clock sources (primary, secondary or internal oscillator block); the Sleep mode does not use a clock source.

The power managed modes include several power saving features offered on previous PIC<sup>®</sup> devices. One is the clock switching feature, offered in other PIC18 devices, allowing the controller to use the Timer1 oscillator in place of the primary oscillator. Also included is the Sleep mode, offered by all PIC devices, where all device clocks are stopped.

#### 3.1 Selecting Power Managed Modes

Selecting a power managed mode requires two decisions: if the CPU is to be clocked or not and the selection of a clock source. The IDLEN bit (OSCCON<7>) controls CPU clocking, while the SCS1:SCS0 bits (OSCCON<1:0>) select the clock source. The individual modes, bit settings, clock sources and affected modules are summarized in Table 3-1.

## 3.1.1 CLOCK SOURCES

The SCS1:SCS0 bits allow the selection of one of three clock sources for power managed modes. They are:

- the primary clock, as defined by the FOSC3:FOSC0 Configuration bits

- the secondary clock (the Timer1 oscillator)

- the internal oscillator block (for RC modes)

#### 3.1.2 ENTERING POWER MANAGED MODES

Switching from one power managed mode to another begins by loading the OSCCON register. The SCS1:SCS0 bits select the clock source and determine which Run or Idle mode is to be used. Changing these bits causes an immediate switch to the new clock source, assuming that it is running. The switch may also be subject to clock transition delays. These are discussed in Section 3.1.3 "Clock Transitions And Status Indicators" and subsequent sections.

Entry to the Power Managed Idle or Sleep modes is triggered by the execution of a SLEEP instruction. The actual mode that results depends on the status of the IDLEN bit.

Depending on the current mode and the mode being switched to, a change to a power managed mode does not always require setting all of these bits. Many transitions may be done by changing the oscillator select bits, or changing the IDLEN bit, prior to issuing a SLEEP instruction. If the IDLEN bit is already configured correctly, it may only be necessary to perform a SLEEP instruction to switch to the desired mode.

| TADLE 3-1. | ADLE 3-1. FOWER MANAGED MODES |                |         |             |                                                                                                              |  |  |  |  |  |  |

|------------|-------------------------------|----------------|---------|-------------|--------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Mode       | oso                           | CON Bits       | Modul   | e Clocking  | Available Clock and Oscillator Source                                                                        |  |  |  |  |  |  |

| wode       | IDLEN<7> <sup>(1)</sup>       | SCS1:SCS0<1:0> | CPU     | Peripherals |                                                                                                              |  |  |  |  |  |  |

| Sleep      | 0                             | N/A            | Off     | Off         | None – All clocks are disabled                                                                               |  |  |  |  |  |  |

| PRI_RUN    | N/A                           | 00             | Clocked | Clocked     | Primary – LP, XT, HS, HSPLL, RC, EC, INTRC <sup>(2)</sup> :<br>This is the normal full power execution mode. |  |  |  |  |  |  |

| SEC_RUN    | N/A                           | 01             | Clocked | Clocked     | Secondary – Timer1 Oscillator                                                                                |  |  |  |  |  |  |

| RC_RUN     | N/A                           | lx             | Clocked | Clocked     | Internal Oscillator Block <sup>(2)</sup>                                                                     |  |  |  |  |  |  |

| PRI_IDLE   | 1                             | 00             | Off     | Clocked     | Primary – LP, XT, HS, HSPLL, RC, EC                                                                          |  |  |  |  |  |  |

| SEC_IDLE   | 1                             | 01             | Off     | Clocked     | Secondary – Timer1 Oscillator                                                                                |  |  |  |  |  |  |

| RC_IDLE    | 1                             | 1x             | Off     | Clocked     | Internal Oscillator Block <sup>(2)</sup>                                                                     |  |  |  |  |  |  |

TABLE 3-1: POWER MANAGED MODES

Note 1: IDLEN reflects its value when the SLEEP instruction is executed.

2: Includes INTOSC and INTOSC postscaler, as well as the INTRC source.

## 3.4.3 RC\_IDLE MODE

In RC\_IDLE mode, the CPU is disabled but the peripherals continue to be clocked from the internal oscillator block using the INTOSC multiplexer. This mode allows for controllable power conservation during Idle periods.

From RC\_RUN, this mode is entered by setting the IDLEN bit and executing a SLEEP instruction. If the device is in another Run mode, first set IDLEN, then set the SCS1 bit and execute SLEEP. Although its value is ignored, it is recommended that SCS0 also be cleared; this is to maintain software compatibility with future devices. The INTOSC multiplexer may be used to select a higher clock frequency, by modifying the IRCF bits, before executing the SLEEP instruction. When the clock source is switched to the INTOSC multiplexer, the primary oscillator is shut down and the OSTS bit is cleared.

If the IRCF bits are set to any non-zero value or the INTSRC bit is set, the INTOSC output is enabled. The IOFS bit becomes set, after the INTOSC output becomes stable, after an interval of TIOBST (parameter 39, Table 27-10). Clocks to the peripherals continue while the INTOSC source stabilizes. If the IRCF bits were previously at a non-zero value, or INTSRC was set before the SLEEP instruction was executed and the INTOSC source was already stable, the IOFS bit will remain set. If the IRCF bits and INTSRC are all clear, the INTOSC output will not be enabled, the IOFS bit will remain clear and there will be no indication of the current clock source.

When a wake event occurs, the peripherals continue to be clocked from the INTOSC multiplexer. After a delay of TCSD following the wake event, the CPU begins executing code being clocked by the INTOSC multiplexer. The IDLEN and SCS bits are not affected by the wake-up. The INTRC source will continue to run if either the WDT or the Fail-Safe Clock Monitor is enabled.

## 3.5 Exiting Idle and Sleep Modes

An exit from Sleep mode or any of the Idle modes is triggered by an interrupt, a Reset or a WDT time-out. This section discusses the triggers that cause exits from power managed modes. The clocking subsystem actions are discussed in each of the power managed modes (see Section 3.2 "Run Modes", Section 3.3 "Sleep Mode" and Section 3.4 "Idle Modes").

#### 3.5.1 EXIT BY INTERRUPT

Any of the available interrupt sources can cause the device to exit from an Idle mode or the Sleep mode to a Run mode. To enable this functionality, an interrupt source must be enabled by setting its enable bit in one of the INTCON or PIE registers. The exit sequence is initiated when the corresponding interrupt flag bit is set.

On all exits from Idle or Sleep modes by interrupt, code execution branches to the interrupt vector if the GIE/GIEH bit (INTCON<7>) is set. Otherwise, code execution continues or resumes without branching (see Section 9.0 "Interrupts").

A fixed delay of interval TCSD following the wake event is required when leaving Sleep and Idle modes. This delay is required for the CPU to prepare for execution. Instruction execution resumes on the first clock cycle following this delay.

#### 3.5.2 EXIT BY WDT TIME-OUT

A WDT time-out will cause different actions depending on which power managed mode the device is in when the time-out occurs.

If the device is not executing code (all Idle modes and Sleep mode), the time-out will result in an exit from the power managed mode (see Section 3.2 "Run Modes" and Section 3.3 "Sleep Mode"). If the device is executing code (all Run modes), the time-out will result in a WDT Reset (see Section 24.2 "Watchdog Timer (WDT)").

The WDT timer and postscaler are cleared by executing a SLEEP or CLRWDT instruction, the loss of a currently selected clock source (if the Fail-Safe Clock Monitor is enabled) and modifying the IRCF bits in the OSCCON register if the internal oscillator block is the device clock source.

#### 3.5.3 EXIT BY RESET

Normally, the device is held in Reset by the Oscillator Start-up Timer (OST) until the primary clock becomes ready. At that time, the OSTS bit is set and the device begins executing code. If the internal oscillator block is the new clock source, the IOFS bit is set instead.

The exit delay time from Reset to the start of code execution depends on both the clock sources before and after the wake-up and the type of oscillator if the new clock source is the primary clock. Exit delays are summarized in Table 3-2.

Code execution can begin before the primary clock becomes ready. If either the Two-Speed Start-up (see Section 24.3 "Two-Speed Start-up") or Fail-Safe Clock Monitor (see Section 24.4 "Fail-Safe Clock Monitor") is enabled, the device may begin execution as soon as the Reset source has cleared. Execution is clocked by the INTOSC multiplexer driven by the internal oscillator block. Execution is clocked by the internal oscillator block until either the primary clock becomes ready or a power managed mode is entered before the primary clock becomes ready; the primary clock is then shut down.

#### 3.5.4 EXIT WITHOUT AN OSCILLATOR START-UP DELAY

Certain exits from power managed modes do not invoke the OST at all. There are two cases:

- PRI\_IDLE mode where the primary clock source is not stopped; and

- the primary clock source is not any of the LP, XT, HS or HSPLL modes.

In these instances, the primary clock source either does not require an oscillator start-up delay, since it is already running (PRI\_IDLE), or normally does not require an oscillator start-up delay (RC, EC and INTIO Oscillator modes). However, a fixed delay of interval TCSD following the wake event is still required when leaving Sleep and Idle modes to allow the CPU to prepare for execution. Instruction execution resumes on the first clock cycle following this delay.

# TABLE 3-2:EXIT DELAY ON WAKE-UP BY RESET FROM SLEEP MODE OR ANY IDLE MODE<br/>(BY CLOCK SOURCES)

| Clock Source<br>Before Wake-up          | Clock Source<br>After Wake-up | Exit Delay                            | Clock Ready Status<br>Bit (OSCCON) |  |  |

|-----------------------------------------|-------------------------------|---------------------------------------|------------------------------------|--|--|

|                                         | LP, XT, HS                    |                                       |                                    |  |  |

| Drive and Device Ole als                | HSPLL                         |                                       | OSTS                               |  |  |

| Primary Device Clock<br>(PRI_IDLE mode) | EC, RC                        | Tcsd <sup>(2)</sup>                   |                                    |  |  |

|                                         | INTRC <sup>(1)</sup>          |                                       | —                                  |  |  |

|                                         | INTOSC <sup>(3)</sup>         |                                       | IOFS                               |  |  |

|                                         | LP, XT, HS                    | Tost <sup>(4)</sup>                   |                                    |  |  |

|                                         | HSPLL                         | Tost + t <sub>rc</sub> (4)            | OSTS                               |  |  |

| T1OSC or INTRC <sup>(1)</sup>           | EC, RC                        | T <sub>CSD</sub> (2)                  |                                    |  |  |

|                                         | INTRC <sup>(1)</sup>          | 103047                                | —                                  |  |  |

|                                         | INTOSC <sup>(2)</sup>         | TIOBST <sup>(5)</sup>                 | IOFS                               |  |  |

|                                         | LP, XT, HS                    | Tost <sup>(5)</sup>                   |                                    |  |  |

|                                         | HSPLL                         | Tost + t <sub>rc</sub> (4)            | OSTS                               |  |  |

| INTOSC <sup>(3)</sup>                   | EC, RC                        | T <sub>CSD</sub> (2)                  |                                    |  |  |

|                                         | INTRC <sup>(1)</sup>          | 105047                                | —                                  |  |  |

|                                         | INTOSC <sup>(2)</sup>         | None                                  | IOFS                               |  |  |

|                                         | LP, XT, HS                    | Tost <sup>(4)</sup>                   |                                    |  |  |

|                                         | HSPLL                         | TOST + t <sub>rc</sub> <sup>(4)</sup> | OSTS                               |  |  |

| None<br>(Sleep mode)                    | EC, RC                        | TCSD(2)                               | ]                                  |  |  |

|                                         | INTRC <sup>(1)</sup>          |                                       | —                                  |  |  |

|                                         | INTOSC <sup>(2)</sup>         | TIOBST <sup>(5)</sup>                 | IOFS                               |  |  |

**Note 1:** In this instance, refers specifically to the 31 kHz INTRC clock source.

2: TCSD (parameter 38) is a required delay when waking from Sleep and all Idle modes and runs concurrently with any other required delays (see Section 3.4 "Idle Modes").

- 3: Includes both the INTOSC 8 MHz source and postscaler derived frequencies.

- 4: TOST is the Oscillator Start-up Timer (parameter 32). t<sub>rc</sub> is the PLL Lock-out Timer (parameter F12); it is also designated as TPLL.

- 5: Execution continues during TIOBST (parameter 39), the INTOSC stabilization period.

|          | INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED) |      |      |                               |           |                 |                                           |         |                   |                 |  |

|----------|---------------------------------------------------------|------|------|-------------------------------|-----------|-----------------|-------------------------------------------|---------|-------------------|-----------------|--|

| Register | Applicable Devices                                      |      |      | Power-on Res<br>Brown-out Res |           | WDT<br>RESET IN | Resets,<br>Reset,<br>struction,<br>Resets | •       | via WDT<br>errupt |                 |  |

| CCPR1H   | 2585                                                    | 2680 | 4585 | 4680                          | xxxx xxxx |                 | uuuu                                      | uuuu    | uuuu              | uuuu            |  |

| CCPR1L   | 2585                                                    | 2680 | 4585 | 4680                          | xxxx xxxx |                 | uuuu                                      | uuuu    | uuuu              | uuuu            |  |

| CCP1CON  | 2585                                                    | 2680 | 4585 | 4680                          | 00 0000   |                 | 00                                        | 0000    | uu                | uuuu            |  |

| ECCPR1H  | 2585                                                    | 2680 | 4585 | 4680                          | xxxx xxxx |                 | uuuu                                      | uuuu    | uuuu              | uuuu            |  |

| ECCPR1L  | 2585                                                    | 2680 | 4585 | 4680                          | xxxx xxxx |                 | uuuu                                      | uuuu    | uuuu              | uuuu            |  |

| ECCP1CON | 2585                                                    | 2680 | 4585 | 4680                          | 0000 0000 |                 | 0000                                      | 0000    | uuuu              | uuuu            |  |

| BAUDCON  | 2585                                                    | 2680 | 4585 | 4680                          | 01-0 0-00 |                 | 01-0                                      | 0 - 0 0 | uu                | uuuu            |  |

| ECCP1DEL | 2585                                                    | 2680 | 4585 | 4680                          | 0000 0000 |                 | 0000                                      | 0000    | uuuu              | uuuu            |  |

| ECCP1AS  | 2585                                                    | 2680 | 4585 | 4680                          | 0000 0000 |                 | 0000                                      | 0000    | uuuu              | uuuu            |  |

| CVRCON   | 2585                                                    | 2680 | 4585 | 4680                          | 0000 0000 |                 | 0000                                      | 0000    | uuuu              | uuuu            |  |

| CMCON    | 2585                                                    | 2680 | 4585 | 4680                          | 0000 0111 |                 | 0000                                      | 0111    | uuuu              | uuuu            |  |

| TMR3H    | 2585                                                    | 2680 | 4585 | 4680                          | XXXX XXXX |                 | uuuu                                      | uuuu    | uuuu              | uuuu            |  |

| TMR3L    | 2585                                                    | 2680 | 4585 | 4680                          | xxxx xxxx |                 | uuuu                                      | uuuu    | uuuu              | uuuu            |  |

| T3CON    | 2585                                                    | 2680 | 4585 | 4680                          | 0000 0000 |                 | uuuu                                      | uuuu    | uuuu              | uuuu            |  |

| SPBRGH   | 2585                                                    | 2680 | 4585 | 4680                          | 0000 0000 |                 | 0000                                      | 0000    | uuuu              | uuuu            |  |

| SPBRG    | 2585                                                    | 2680 | 4585 | 4680                          | 0000 0000 |                 | 0000                                      | 0000    | uuuu              | uuuu            |  |

| RCREG    | 2585                                                    | 2680 | 4585 | 4680                          | 0000 0000 |                 | 0000                                      | 0000    | uuuu              | uuuu            |  |

| TXREG    | 2585                                                    | 2680 | 4585 | 4680                          | 0000 0000 |                 | 0000                                      | 0000    | uuuu              | uuuu            |  |

| TXSTA    | 2585                                                    | 2680 | 4585 | 4680                          | 0000 0010 |                 | 0000                                      | 0010    | uuuu              | uuuu            |  |

| RCSTA    | 2585                                                    | 2680 | 4585 | 4680                          | 0000 000x |                 | 0000                                      | 000x    | uuuu              | uuuu            |  |

| EEADRH   | 2585                                                    | 2680 | 4585 | 4680                          | 00        |                 |                                           | 00      |                   | uu              |  |

| EEADR    | 2585                                                    | 2680 | 4585 | 4680                          | 0000 0000 |                 | 0000                                      | 0000    | uuuu              | uuuu            |  |

| EEDATA   | 2585                                                    | 2680 | 4585 | 4680                          | 0000 0000 |                 | 0000                                      | 0000    | uuuu              | uuuu            |  |

| EECON2   | 2585                                                    | 2680 | 4585 | 4680                          | 0000 0000 |                 | 0000                                      | 0000    | 0000              | 0000            |  |

| EECON1   | 2585                                                    | 2680 | 4585 | 4680                          | xx-0 x000 |                 | uu-0                                      | u000    | uu-0              | u000            |  |

| IPR3     | 2585                                                    | 2680 | 4585 | 4680                          | 1111 1111 |                 | 1111                                      | 1111    | uuuu              | uuuu            |  |

| PIR3     | 2585                                                    | 2680 | 4585 | 4680                          | 0000 0000 |                 | 0000                                      | 0000    | uuuu              | uuuu            |  |

| PIE3     | 2585                                                    | 2680 | 4585 | 4680                          | 0000 0000 |                 | 0000                                      | 0000    | uuuu              | uuuu            |  |

| IPR2     | 2585                                                    | 2680 | 4585 | 4680                          | 11-1 1111 |                 | 11-1                                      | 1111    | uu-u              | uuuu            |  |

|          | 2585                                                    | 2680 | 4585 | 4680                          | 11 111-   |                 | 11                                        | 111-    | uu                |                 |  |

| PIR2     | 2585                                                    | 2680 | 4585 | 4680                          | 00-0 0000 |                 | 00-0                                      | 0000    | uu-u              | սսսս <b>(1)</b> |  |

|          | 2585                                                    | 2680 | 4585 | 4680                          | 00 000-   |                 | 0 0                                       |         |                   | uuu-(1)         |  |

#### TABLE 4-4: INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED)

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition. Shaded cells indicate conditions do not apply for the designated device.

Note 1: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

**3:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

4: See Table 4-3 for Reset value for specific condition.

**5:** Bits 6 and 7 of PORTA, LATA and TRISA are enabled, depending on the oscillator mode selected. When not enabled as PORTA pins, they are disabled and read '0'.

6: This register reads all '0's until the ECAN<sup>™</sup> technology is set up in Mode 1 or Mode 2.

| CANSTAT 2<br>RXB0D7 2 | 2585<br>2585<br>2585 | 2680 | <b>e Devi</b><br>4585 | <b>ces</b><br>4680 | Power-o<br>Brown-o | n Reset,<br>out Reset |      | Resets,<br>Reset, | Wake-up | via WDT |

|-----------------------|----------------------|------|-----------------------|--------------------|--------------------|-----------------------|------|-------------------|---------|---------|

| CANSTAT 2<br>RXB0D7 2 | 2585<br>2585         |      | 4585                  | 1690               |                    |                       |      | Resets            | or Inte | errupt  |

| RXB0D7 2              | 2585                 | 2680 |                       | 4000               | 1000               | 000-                  | 1000 | 000-              | uuuu    | uuu-    |

|                       |                      |      | 4585                  | 4680               | 100-               | 000-                  | 100- | 000-              | uuu-    | uuu-    |

| RXB0D6 2              |                      | 2680 | 4585                  | 4680               | xxxx               | xxxx                  | uuuu | uuuu              | uuuu    | uuuu    |

|                       | 2585                 | 2680 | 4585                  | 4680               | xxxx               | xxxx                  | uuuu | uuuu              | uuuu    | uuuu    |

| RXB0D5 2              | 2585                 | 2680 | 4585                  | 4680               | xxxx               | xxxx                  | uuuu | uuuu              | սսսս    | uuuu    |

| RXB0D4 2              | 2585                 | 2680 | 4585                  | 4680               | xxxx               | xxxx                  | uuuu | uuuu              | uuuu    | uuuu    |

| RXB0D3 2              | 2585                 | 2680 | 4585                  | 4680               | xxxx               | xxxx                  | uuuu | uuuu              | uuuu    | uuuu    |

| RXB0D2 2              | 2585                 | 2680 | 4585                  | 4680               | xxxx               | xxxx                  | uuuu | uuuu              | uuuu    | uuuu    |

| RXB0D1 2              | 2585                 | 2680 | 4585                  | 4680               | xxxx               | xxxx                  | uuuu | uuuu              | uuuu    | uuuu    |

| RXB0D0 2              | 2585                 | 2680 | 4585                  | 4680               | xxxx               | xxxx                  | uuuu | uuuu              | uuuu    | uuuu    |

| RXB0DLC 2             | 2585                 | 2680 | 4585                  | 4680               | -xxx               | xxxx                  | -uuu | uuuu              | -uuu    | uuuu    |

| RXB0EIDL 2            | 2585                 | 2680 | 4585                  | 4680               | xxxx               | xxxx                  | uuuu | uuuu              | uuuu    | uuuu    |

| RXB0EIDH 2            | 2585                 | 2680 | 4585                  | 4680               | xxxx               | xxxx                  | uuuu | uuuu              | uuuu    | uuuu    |

| RXB0SIDL 2            | 2585                 | 2680 | 4585                  | 4680               | xxxx               | x-xx                  | uuuu | u-uu              | uuuu    | u-uu    |

| RXB0SIDH 2            | 2585                 | 2680 | 4585                  | 4680               | xxxx               | xxxx                  | uuuu | uuuu              | uuuu    | uuuu    |

| RXB0CON 2             | 2585                 | 2680 | 4585                  | 4680               | 000-               | 0000                  | 000- | 0000              | uuu-    | uuuu    |

| RXB1D7 2              | 2585                 | 2680 | 4585                  | 4680               | xxxx               | xxxx                  | uuuu | uuuu              | uuuu    | uuuu    |

| RXB1D6 2              | 2585                 | 2680 | 4585                  | 4680               | xxxx               | xxxx                  | uuuu | uuuu              | uuuu    | uuuu    |

| RXB1D5 2              | 2585                 | 2680 | 4585                  | 4680               | xxxx               | xxxx                  | uuuu | uuuu              | uuuu    | uuuu    |

| RXB1D4 2              | 2585                 | 2680 | 4585                  | 4680               | xxxx               | xxxx                  | uuuu | uuuu              | uuuu    | uuuu    |

| RXB1D3 2              | 2585                 | 2680 | 4585                  | 4680               | xxxx               | xxxx                  | uuuu | uuuu              | uuuu    | uuuu    |

| RXB1D2 2              | 2585                 | 2680 | 4585                  | 4680               | xxxx               | xxxx                  | uuuu | uuuu              | uuuu    | uuuu    |

| RXB1D1 2              | 2585                 | 2680 | 4585                  | 4680               | xxxx               | xxxx                  | uuuu | uuuu              | uuuu    | uuuu    |

| RXB1D0 2              | 2585                 | 2680 | 4585                  | 4680               | xxxx               | xxxx                  | uuuu | uuuu              | uuuu    | uuuu    |

| RXB1DLC 2             | 2585                 | 2680 | 4585                  | 4680               | -xxx               | xxxx                  | -uuu | uuuu              | -uuu    | uuuu    |

| RXB1EIDL 2            | 2585                 | 2680 | 4585                  | 4680               | xxxx               | xxxx                  | uuuu | uuuu              | սսսս    | uuuu    |

| RXB1EIDH 2            | 2585                 | 2680 | 4585                  | 4680               | xxxx               | xxxx                  | uuuu | uuuu              | uuuu    | uuuu    |

| RXB1SIDL 2            | 2585                 | 2680 | 4585                  | 4680               | xxxx               | x-xx                  | uuuu | u-uu              | սսսս    | u-uu    |

| RXB1SIDH 2            | 2585                 | 2680 | 4585                  | 4680               | xxxx               | xxxx                  | uuuu | uuuu              | uuuu    | uuuu    |

| RXB1CON 2             | 2585                 | 2680 | 4585                  | 4680               | 000-               | 0000                  | 000- | 0000              | uuu-    | uuuu    |

| TXB0D7 2              | 2585                 | 2680 | 4585                  | 4680               | xxxx               | xxxx                  | uuuu | uuuu              | սսսս    | uuuu    |

| TXB0D6 2              | 2585                 | 2680 | 4585                  | 4680               | xxxx               | xxxx                  | uuuu | uuuu              | uuuu    | uuuu    |

#### TABLE 4-4: INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED)

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition. Shaded cells indicate conditions do not apply for the designated device.

Note 1: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

**3:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

4: See Table 4-3 for Reset value for specific condition.

**5:** Bits 6 and 7 of PORTA, LATA and TRISA are enabled, depending on the oscillator mode selected. When not enabled as PORTA pins, they are disabled and read '0'.

6: This register reads all '0's until the ECAN<sup>™</sup> technology is set up in Mode 1 or Mode 2.

| IADLE 4-4.            | INTIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED) |                    |      |      |                                    |                                                                  |                                 |  |  |  |  |

|-----------------------|--------------------------------------------------------|--------------------|------|------|------------------------------------|------------------------------------------------------------------|---------------------------------|--|--|--|--|

| Register              | Арј                                                    | Applicable Devices |      |      | Power-on Reset,<br>Brown-out Reset | MCLR Resets,<br>WDT Reset,<br>RESET Instruction,<br>Stack Resets | Wake-up via WDT<br>or Interrupt |  |  |  |  |

| B4EIDH <sup>(6)</sup> | 2585                                                   | 2680               | 4585 | 4680 | xxxx xxxx                          | uuuu uuuu                                                        | uuuu uuuu                       |  |  |  |  |

| B4SIDL <sup>(6)</sup> | 2585                                                   | 2680               | 4585 | 4680 | xxxx x-xx                          | uuuu u-uu                                                        | uuuu u-uu                       |  |  |  |  |

| B4SIDH <sup>(6)</sup> | 2585                                                   | 2680               | 4585 | 4680 | xxxx xxxx                          | uuuu uuuu                                                        | uuuu uuuu                       |  |  |  |  |

| B4CON <sup>(6)</sup>  | 2585                                                   | 2680               | 4585 | 4680 | 0000 0000                          | 0000 0000                                                        | uuuu uuuu                       |  |  |  |  |

| B3D7 <sup>(6)</sup>   | 2585                                                   | 2680               | 4585 | 4680 | xxxx xxxx                          | uuuu uuuu                                                        | uuuu uuuu                       |  |  |  |  |

| B3D6 <sup>(6)</sup>   | 2585                                                   | 2680               | 4585 | 4680 | xxxx xxxx                          | uuuu uuuu                                                        | uuuu uuuu                       |  |  |  |  |

| B3D5 <sup>(6)</sup>   | 2585                                                   | 2680               | 4585 | 4680 | xxxx xxxx                          | uuuu uuuu                                                        | uuuu uuuu                       |  |  |  |  |

| B3D4 <sup>(6)</sup>   | 2585                                                   | 2680               | 4585 | 4680 | xxxx xxxx                          | uuuu uuuu                                                        | uuuu uuuu                       |  |  |  |  |

| B3D3 <sup>(6)</sup>   | 2585                                                   | 2680               | 4585 | 4680 | xxxx xxxx                          | uuuu uuuu                                                        | uuuu uuuu                       |  |  |  |  |

| B3D2 <sup>(6)</sup>   | 2585                                                   | 2680               | 4585 | 4680 | xxxx xxxx                          | uuuu uuuu                                                        | uuuu uuuu                       |  |  |  |  |

| B3D1 <sup>(6)</sup>   | 2585                                                   | 2680               | 4585 | 4680 | XXXX XXXX                          | uuuu uuuu                                                        | uuuu uuuu                       |  |  |  |  |

| B3D0 <sup>(6)</sup>   | 2585                                                   | 2680               | 4585 | 4680 | XXXX XXXX                          | uuuu uuuu                                                        | uuuu uuuu                       |  |  |  |  |

| B3DLC <sup>(6)</sup>  | 2585                                                   | 2680               | 4585 | 4680 | -xxx xxxx                          | -uuu uuuu                                                        | -uuu uuuu                       |  |  |  |  |

| B3EIDL <sup>(6)</sup> | 2585                                                   | 2680               | 4585 | 4680 | XXXX XXXX                          | uuuu uuuu                                                        | uuuu uuuu                       |  |  |  |  |

| B3EIDH <sup>(6)</sup> | 2585                                                   | 2680               | 4585 | 4680 | XXXX XXXX                          | uuuu uuuu                                                        | uuuu uuuu                       |  |  |  |  |

| B3SIDL <sup>(6)</sup> | 2585                                                   | 2680               | 4585 | 4680 | xxxx x-xx                          | uuuu u-uu                                                        | uuuu u-uu                       |  |  |  |  |

| B3SIDH <sup>(6)</sup> | 2585                                                   | 2680               | 4585 | 4680 | xxxx xxxx                          | uuuu uuuu                                                        | uuuu uuuu                       |  |  |  |  |

| B3CON <sup>(6)</sup>  | 2585                                                   | 2680               | 4585 | 4680 | 0000 0000                          | 0000 0000                                                        | uuuu uuuu                       |  |  |  |  |

| B2D7 <sup>(6)</sup>   | 2585                                                   | 2680               | 4585 | 4680 | xxxx xxxx                          | uuuu uuuu                                                        | uuuu uuuu                       |  |  |  |  |

| B2D6 <sup>(6)</sup>   | 2585                                                   | 2680               | 4585 | 4680 | XXXX XXXX                          | uuuu uuuu                                                        | uuuu uuuu                       |  |  |  |  |

| B2D5 <sup>(6)</sup>   | 2585                                                   | 2680               | 4585 | 4680 | xxxx xxxx                          | uuuu uuuu                                                        | uuuu uuuu                       |  |  |  |  |

| B2D4 <sup>(6)</sup>   | 2585                                                   | 2680               | 4585 | 4680 | xxxx xxxx                          | սսսս սսսս                                                        | սսսս սսսս                       |  |  |  |  |

| B2D3 <sup>(6)</sup>   | 2585                                                   | 2680               | 4585 | 4680 | xxxx xxxx                          | uuuu uuuu                                                        | uuuu uuuu                       |  |  |  |  |

| B2D2 <sup>(6)</sup>   | 2585                                                   | 2680               | 4585 | 4680 | xxxx xxxx                          | uuuu uuuu                                                        | uuuu uuuu                       |  |  |  |  |

| B2D1 <sup>(6)</sup>   | 2585                                                   | 2680               | 4585 | 4680 | xxxx xxxx                          | սսսս սսսս                                                        | uuuu uuuu                       |  |  |  |  |

| B2D0 <sup>(6)</sup>   | 2585                                                   | 2680               | 4585 | 4680 | xxxx xxxx                          | uuuu uuuu                                                        | uuuu uuuu                       |  |  |  |  |

| B2DLC <sup>(6)</sup>  | 2585                                                   | 2680               | 4585 | 4680 | -xxx xxxx                          | -uuu uuuu                                                        | -uuu uuuu                       |  |  |  |  |

| B2EIDL <sup>(6)</sup> | 2585                                                   | 2680               | 4585 | 4680 | xxxx xxxx                          | սսսս սսսս                                                        | uuuu uuuu                       |  |  |  |  |

| B2EIDH <sup>(6)</sup> | 2585                                                   | 2680               | 4585 | 4680 | xxxx xxxx                          | uuuu uuuu                                                        | uuuu uuuu                       |  |  |  |  |

| B2SIDL <sup>(6)</sup> | 2585                                                   | 2680               | 4585 | 4680 | xxxx x-xx                          | uuuu u-uu                                                        | uuuu u-uu                       |  |  |  |  |

| B2SIDH <sup>(6)</sup> | 2585                                                   | 2680               | 4585 | 4680 | xxxx xxxx                          | uuuu uuuu                                                        | uuuu uuuu                       |  |  |  |  |

#### TABLE 4-4: INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED)

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition. Shaded cells indicate conditions do not apply for the designated device.

Note 1: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

**3:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

4: See Table 4-3 for Reset value for specific condition.

**5:** Bits 6 and 7 of PORTA, LATA and TRISA are enabled, depending on the oscillator mode selected. When not enabled as PORTA pins, they are disabled and read '0'.

6: This register reads all '0's until the ECAN<sup>™</sup> technology is set up in Mode 1 or Mode 2.

| Pin Name  | Function | I/O | TRIS | Buffer | Description                                                                                                                   |

|-----------|----------|-----|------|--------|-------------------------------------------------------------------------------------------------------------------------------|

| RD0/PSP0/ | RD0      | OUT | 0    | DIG    | LATD<0> data output.                                                                                                          |

| C1IN+     |          | IN  | 1    | ST     | PORTD<0> data input.                                                                                                          |

|           | PSP0     | OUT | х    | DIG    | Parallel Slave Port (PSP) data output (overrides the TRIS<0> control when enabled).                                           |

|           |          | IN  | х    | TTL    | Parallel Slave Port (PSP) data input (overrides the TRIS<0> control when enabled).                                            |

|           | C1IN+    | IN  | 1    | ANA    | Comparator 1 positive input B. Default on POR. This analog input overrides the digital input (read as clear – low level).     |

| RD1/PSP1/ | RD1      | OUT | 0    | DIG    | LATD<1> data output.                                                                                                          |

| C1IN-     |          | IN  | 1    | ST     | PORTD<1> data input.                                                                                                          |

|           | PSP1     | OUT | х    | DIG    | Parallel Slave Port (PSP) data output (overrides the TRIS<1> control when enabled).                                           |

|           |          | IN  | x    | TTL    | Parallel Slave Port (PSP) data input (overrides the TRIS<1> control when enabled).                                            |

|           | C1IN-    | IN  | 1    | ANA    | Comparator 1 negative input. Default on POR. This analog input overrides the digital input (read as clear – low level).       |

| RD2/PSP2/ | RD2      | OUT | 0    | DIG    | LATD<2> data output.                                                                                                          |

| C2IN+     |          | IN  | 1    | ST     | PORTD<2> data input.                                                                                                          |

|           | PSP2     | OUT | х    | DIG    | Parallel Slave Port (PSP) data output (overrides the TRIS<2> control when enabled).                                           |

|           |          | IN  | x    | TTL    | Parallel Slave Port (PSP) data input (overrides the TRIS<2> control when enabled).                                            |

|           | C2IN+    | IN  | 1    | ANA    | Comparator 2 positive input. Default on POR. This analog input overrides the digital input (read as clear – low level).       |

| RD3/PSP3/ | RD3      | OUT | 0    | DIG    | LATD<3> data output.                                                                                                          |

| C2IN-     |          | IN  | 1    | ST     | PORTD<3> data input.                                                                                                          |

|           | PSP3     | OUT | x    | DIG    | Parallel Slave Port (PSP) data output (overrides the TRIS<3> control when enabled).                                           |

| C21       |          | IN  | x    | TTL    | Parallel Slave Port (PSP) data input (overrides the TRIS<3> control when enabled).                                            |

|           | C2IN-    | IN  | 1    | ANA    | Comparator 2 negative input. Default input on POR. This analog input overrides the digital input (read as clear – low level). |

| RD4/PSP4/ | RD4      | OUT | 0    | DIG    | LATD<4> data output.                                                                                                          |

| ECCP1/P1A |          | IN  | 1    | ST     | PORTD<4> data input.                                                                                                          |

|           | PSP4     | OUT | x    | DIG    | Parallel Slave Port (PSP) data output (overrides the TRIS<4> control when enabled).                                           |

|           |          | IN  | х    | TTL    | Parallel Slave Port (PSP) data input (overrides the TRIS<4> control when enabled).                                            |

|           | ECCP1    | OUT | 0    | DIG    | ECCP1 compare output.                                                                                                         |

|           |          | IN  | 1    | ST     | ECCP1 capture input.                                                                                                          |

|           | P1A      | OUT | 0    | DIG    | ECCP1 Enhanced PWM output, channel A.                                                                                         |

| RD5/PSP5/ | RD5      | OUT | 0    | DIG    | LATD<5> data output.                                                                                                          |

| P1B       |          | IN  | 1    | ST     | PORTD<5> data input.                                                                                                          |

|           | PSP5     | OUT | Х    | DIG    | Parallel Slave Port (PSP) data output (overrides the TRIS<5> control when enabled).                                           |

|           |          | IN  | x    | TTL    | Parallel Slave Port (PSP) data input (overrides the TRIS<5> control when enabled).                                            |

|           | P1B      | OUT | 0    | DIG    | ECCP1 Enhanced PWM output, channel B.                                                                                         |

| RD6/PSP6/ | RD6      | OUT | 0    | DIG    | LATD<6> data output.                                                                                                          |

| P1C       |          | IN  | 1    | ST     | PORTD<6> data input.                                                                                                          |

|           | PSP6     | OUT | x    | DIG    | Parallel Slave Port (PSP) data output (overrides the TRIS<6> control when enabled).                                           |

|           |          | IN  | x    | TTL    | Parallel Slave Port (PSP) data input (overrides the TRIS<6> control when enabled).                                            |

|           | P1C      | OUT | 0    | DIG    | ECCP1 Enhanced PWM output, channel C.                                                                                         |

| RD7/PSP7/ | RD7      | OUT | 0    | DIG    | LATD<7> data output.                                                                                                          |

| P1D       |          | IN  | 1    | ST     | PORTD<7> data input.                                                                                                          |

|           | PSP7     | OUT | x    | DIG    | Parallel Slave Port (PSP) data output (overrides the TRIS<7> control when enabled).                                           |

|           |          | IN  | x    | TTL    | Parallel Slave Port (PSP) data input (overrides the TRIS<7> control when enabled).                                            |

|           |          |     |      |        |                                                                                                                               |

# TABLE 10-7: PORTD I/O SUMMARY

Legend: PWR = Power Supply; OUT = Output; IN = Input; ANA = Analog Signal; DIG = Digital Output; ST = Schmitt Buffer Input; TTL = TTL Buffer Input

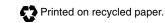

#### 17.4.12 ACKNOWLEDGE SEQUENCE TIMING

An Acknowledge sequence is enabled by setting the Acknowledge sequence enable bit. ACKEN (SSPCON2<4>). When this bit is set, the SCL pin is pulled low and the contents of the Acknowledge data bit are presented on the SDA pin. If the user wishes to generate an Acknowledge, then the ACKDT bit should be cleared. If not, the user should set the ACKDT bit before starting an Acknowledge sequence. The Baud Rate Generator then counts for one rollover period (TBRG) and the SCL pin is deasserted (pulled high). When the SCL pin is sampled high (clock arbitration), the Baud Rate Generator counts for TBRG. The SCL pin is then pulled low. Following this, the ACKEN bit is automatically cleared, the Baud Rate Generator is turned off and the MSSP module then goes into Idle mode (Figure 17-23).

#### 17.4.12.1 WCOL Status Flag

If the user writes the SSPBUF when an Acknowledge sequence is in progress, then WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

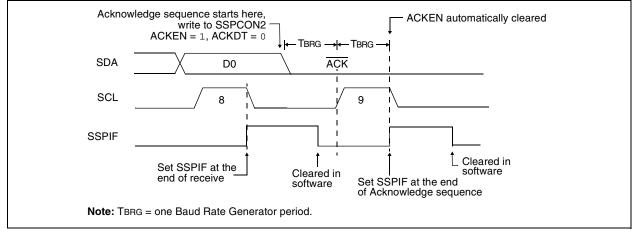

### 17.4.13 STOP CONDITION TIMING

A Stop bit is asserted on the SDA pin at the end of a receive/transmit by setting the Stop Sequence Enable bit, PEN (SSPCON2<2>). At the end of a receive/ transmit, the SCL line is held low after the falling edge of the ninth clock. When the PEN bit is set, the master will assert the SDA line low. When the SDA line is sampled low, the Baud Rate Generator is reloaded and counts down to '0'. When the Baud Rate Generator times out, the SCL pin will be brought high and one TBRG (Baud Rate Generator rollover count) later, the SDA pin will be deasserted. When the SDA pin is sampled high while SCL is high, the P bit (SSPSTAT<4>) is set. A TBRG later, the PEN bit is cleared and the SSPIF bit is set (Figure 17-24).

#### 17.4.13.1 WCOL Status Flag

If the user writes the SSPBUF when a Stop sequence is in progress, then the WCOL bit is set and the contents of the buffer are unchanged (the write doesn't occur).

#### FIGURE 17-23: ACKNOWLEDGE SEQUENCE WAVEFORM

#### FIGURE 17-24: STOP CONDITION RECEIVE OR TRANSMIT MODE

#### 18.4.2 EUSART SYNCHRONOUS SLAVE RECEPTION

The operation of the Synchronous Master and Slave modes is identical, except in the case of Sleep or any Idle mode and bit SREN, which is a "don't care" in Slave mode.

If receive is enabled by setting the CREN bit prior to entering Sleep or any Idle mode, then a word may be received while in this low-power mode. Once the word is received, the RSR register will transfer the data to the RCREG register; if the RCIE enable bit is set, the interrupt generated will wake the chip from the low-power mode. If the global interrupt is enabled, the program will branch to the interrupt vector. To set up a Synchronous Slave Reception:

- Enable the synchronous master serial port by setting bits SYNC and SPEN and clearing bit CSRC.

- 2. If interrupts are desired, set enable bit RCIE.

- 3. If 9-bit reception is desired, set bit RX9.

- 4. To enable reception, set enable bit CREN.

- 5. Flag bit RCIF will be set when reception is complete. An interrupt will be generated if enable bit RCIE was set.

- 6. Read the RCSTA register to get the 9th bit (if enabled) and determine if any error occurred during reception.

- 7. Read the 8-bit received data by reading the RCREG register.

- 8. If any error occurred, clear the error by clearing bit CREN.

- If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

| Name    | Bit 7                                              | Bit 6        | Bit 5       | Bit 4        | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

|---------|----------------------------------------------------|--------------|-------------|--------------|-------|--------|--------|--------|----------------------------|

| INTCON  | GIE/GIEH                                           | PEIE/GIEL    | TMR0IE      | INT0IE       | RBIE  | TMR0IF | INT0IF | RBIF   | 49                         |

| PIR1    | PSPIF <sup>(1)</sup>                               | ADIF         | RCIF        | TXIF         | SSPIF | CCP1IF | TMR2IF | TMR1IF | 52                         |

| PIE1    | PSPIE <sup>(1)</sup>                               | ADIE         | RCIE        | TXIE         | SSPIE | CCP1IE | TMR2IE | TMR1IE | 52                         |

| IPR1    | PSPIP <sup>(1)</sup>                               | ADIP         | RCIP        | TXIP         | SSPIP | CCP1IP | TMR2IP | TMR1IP | 52                         |

| RCSTA   | SPEN                                               | RX9          | SREN        | CREN         | ADDEN | FERR   | OERR   | RX9D   | 51                         |

| RCREG   | EUSART F                                           | Receive Regi | ster        |              |       |        |        |        | 51                         |

| TXSTA   | CSRC                                               | TX9          | TXEN        | SYNC         | SENDB | BRGH   | TRMT   | TX9D   | 51                         |

| BAUDCON | ABDOVF                                             | RCIDL        | —           | SCKP         | BRG16 | —      | WUE    | ABDEN  | 51                         |

| SPBRGH  | BRGH EUSART Baud Rate Generator Register High Byte |              |             |              |       |        |        |        | 51                         |

| SPBRG   | EUSART E                                           | Baud Rate G  | enerator Re | gister Low I | Byte  |        |        |        | 51                         |

#### TABLE 18-10: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE RECEPTION

Legend: — = unimplemented, read as '0'. Shaded cells are not used for synchronous slave reception.

**Note 1:** Reserved in PIC18F2X8X devices; always maintain these bits clear.

#### 19.4 Operation in Power Managed Modes

The selection of the automatic acquisition time and A/D conversion clock is determined in part, by the clock source and frequency while in a power managed mode.

If the A/D is expected to operate while the device is in a power managed mode, the ACQT2:ACQT0 and ADCS2:ADCS0 bits in ADCON2 should be updated in accordance with the clock source to be used in that mode. After entering the mode, an A/D acquisition or conversion may be started. Once started, the device should continue to be clocked by the same clock source until the conversion has been completed.

If desired, the device may be placed into the corresponding Idle mode during the conversion. If the device clock frequency is less than 1 MHz, the A/D RC clock source should be selected.

Operation in the Sleep mode requires the A/D FRC clock to be selected. If bits ACQT2:ACQT0 are set to '000' and a conversion is started, the conversion will be delayed one instruction cycle to allow execution of the SLEEP instruction and entry to Sleep mode. The IDLEN bit (OSCCON<7>) must have already been cleared prior to starting the conversion.

# 19.5 Configuring Analog Port Pins

The ADCON1, TRISA, TRISB and TRISE registers all configure the A/D port pins. The port pins needed as analog inputs must have their corresponding TRIS bits set (input). If the TRIS bit is cleared (output), the digital output level (VOH or VOL) will be converted.

The A/D operation is independent of the state of the CHS3:CHS0 bits and the TRIS bits.

- Note 1: When reading the Port register, all pins configured as analog input channels will read as cleared (a low level). Pins configured as digital inputs will convert an analog input. Analog levels on a digitally configured input will be accurately converted.

- 2: Analog levels on any pin defined as a digital input may cause the digital input buffer to consume current out of the device's specification limits.

- 3: The PBADEN bit in Configuration Register 3H configures PORTB pins to reset as analog or digital pins by controlling how the PCFG0 bits in ADCON1 are reset.

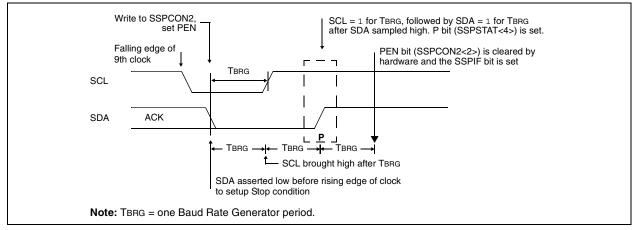

## 22.5 Applications

In many applications, the ability to detect a drop below, or rise above a particular threshold is desirable. For example, the HLVD module could be periodically enabled to detect Universal Serial Bus (USB) attach or detach. This assumes the device is powered by a lower voltage source than the USB when detached. An attach would indicate a high-voltage detect from, for example, 3.3V to 5V (the voltage on USB) and vice versa for a detach. This feature could save a design a few extra components and an attach signal (input pin).

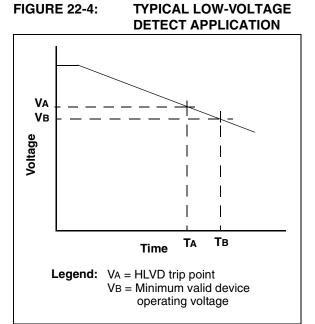

For general battery applications, Figure 22-4 shows a possible voltage curve. Over time, the device voltage decreases. When the device voltage reaches voltage VA, the HLVD logic generates an interrupt at time TA. The interrupt could cause the execution of an ISR, which would allow the application to perform "house-keeping tasks" and perform a controlled shutdown before the device voltage exits the valid operating range at TB. The HLVD, thus, would give the application a time window, represented by the difference between TA and TB, to safely exit.

| REGISTER 23-2: | CANSTAT: CA                                                | N STATU                               | S REGISTER                                        |                                    |                            |                          |                           |                        |

|----------------|------------------------------------------------------------|---------------------------------------|---------------------------------------------------|------------------------------------|----------------------------|--------------------------|---------------------------|------------------------|

| Mode 0         | R-1                                                        | R-0                                   | R-0                                               | R-0                                | R-0                        | R-0                      | R-0                       | U-0                    |

| Mode 0         | OPMODE2 <sup>(1)</sup> OF                                  | MODE1 <sup>(1)</sup>                  | OPMODE0 <sup>(1)</sup>                            | _                                  | ICODE3                     | ICODE2                   | ICODE1                    |                        |

|                |                                                            | <b>D</b> 0                            |                                                   |                                    |                            |                          | <b>D</b> 0                |                        |

| Mode 1, 2      | R-1                                                        | R-0                                   | R-0                                               | R-0                                | R-0                        | R-0                      | R-0                       | R-0                    |

|                | L                                                          | MODE1 <sup>(1)</sup>                  | OPMODE0 <sup>(1)</sup>                            | EICODE4                            | EICODE3                    | EICODE2                  | EICODE1                   | EICODE0                |

|                | bit 7                                                      |                                       |                                                   |                                    |                            |                          |                           | bit 0                  |

| bit 7-5        | OPMODE2:OPM                                                |                                       | oration Mode                                      | Statue bite                        | 1)                         |                          |                           |                        |

| Dit 7-5        | 111 = Reserved                                             | <b>ODE0.</b> Op                       |                                                   | bialus bils                        |                            |                          |                           |                        |

|                | 110 = Reserved                                             |                                       |                                                   |                                    |                            |                          |                           |                        |

|                | 101 = Reserved                                             |                                       |                                                   |                                    |                            |                          |                           |                        |

|                | 100 = Configurat                                           | ion mode                              |                                                   |                                    |                            |                          |                           |                        |

|                | 011 = Listen Only                                          |                                       |                                                   |                                    |                            |                          |                           |                        |

|                | 010 = Loopback                                             |                                       |                                                   |                                    |                            |                          |                           |                        |

|                | 001 = Disable/Sl<br>000 = Normal mo                        | •                                     |                                                   |                                    |                            |                          |                           |                        |

| bit 4          | <u>Mode 0:</u>                                             | Jue                                   |                                                   |                                    |                            |                          |                           |                        |

| Dit 4          | Unimplemented                                              | : Read as                             | ʻ0'                                               |                                    |                            |                          |                           |                        |

| bit 3-1        | ICODE3:ICODE1                                              |                                       |                                                   |                                    |                            |                          |                           |                        |

|                | When an interrup                                           |                                       |                                                   | led interru                        | nt value w                 | ill he prese             | ont in these              | hits This              |

|                | code indicates the<br>or EICODE4:EIC<br>buffer to map into | e source of<br>ODE0 to I<br>the Acces | the interrupt. B<br>EWIN4:EWIN0<br>s Bank area. S | y copying<br>(Mode 1 a<br>ee Examp | iCODE3:IC<br>and 2), it is | CODE1 to V<br>s possible | VIN2:WIN0<br>to select th | (Mode 0)<br>ne correct |

|                | description, the fo                                        | bliowing tai                          |                                                   | DITS.                              |                            |                          |                           | •                      |

|                |                                                            |                                       | Mode 0                                            |                                    | Mode 1                     |                          | Mode                      |                        |

|                | No interrupt                                               |                                       | 00000                                             |                                    | 00000                      |                          | 00000                     |                        |

|                | Error interrupt<br>TXB2 interrupt                          |                                       | 00010                                             |                                    | 00010                      |                          | 00010                     |                        |

|                | TXB1 interrupt                                             |                                       | 00100<br>00110                                    |                                    | 00100<br>00110             |                          | 00100<br>00110            |                        |

|                | TXB0 interrupt                                             |                                       | 01000                                             |                                    | 01000                      |                          | 01000                     |                        |

|                | RXB1 interrupt                                             |                                       | 01010                                             |                                    | 10001                      |                          |                           |                        |

|                | RXB0 interrupt                                             |                                       | 01100                                             |                                    | 10001                      |                          | 10000                     |                        |

|                | Wake-up interrup                                           | ot                                    | 00010                                             |                                    | 01110                      |                          | 01110                     |                        |

|                | RXB0 interrupt                                             |                                       |                                                   |                                    | 10000                      |                          | 10000                     |                        |

|                | RXB1 interrupt                                             |                                       |                                                   |                                    | 10001                      |                          | 10000                     |                        |

|                | RX/TX B0 interru                                           | upt                                   |                                                   |                                    | 10010                      |                          | 10010                     |                        |

|                | RX/TX B1 interru                                           | .pt                                   |                                                   |                                    | 10011                      |                          | 10011                     | (2)                    |