Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 40MHz                                                                      |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 64KB (32K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 1K x 8                                                                     |

| RAM Size                   | 3.25K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                  |

| Data Converters            | A/D 8x10b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Through Hole                                                               |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                    |

| Supplier Device Package    | 28-SPDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf2680-i-sp |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

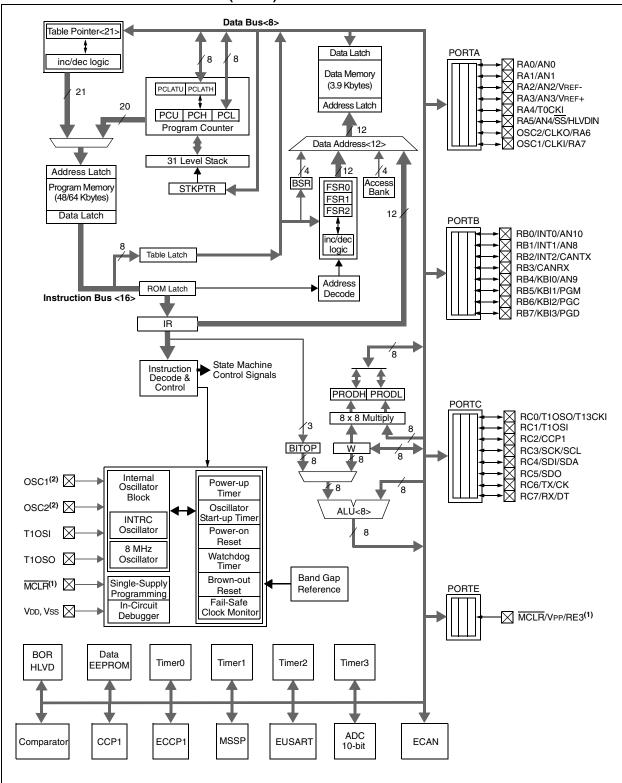

#### FIGURE 1-1: PIC18F2585/2680 (28-PIN) BLOCK DIAGRAM

Note 1: RE3 is multiplexed with MCLR and is only available when the MCLR Resets are disabled.

2: OSC1/CLKI and OSC2/CLKO are only available in select oscillator modes and when these pins are not being used as digital I/O. Refer to Section 2.0 "Oscillator Configurations" for additional information.

| File Name             | Bit 7              | Bit 6                                   | Bit 5               | Bit 4                  | Bit 3                  | Bit 2                   | Bit 1                  | Bit 0                  | Value on POR, BOR | Details<br>on page: |

|-----------------------|--------------------|-----------------------------------------|---------------------|------------------------|------------------------|-------------------------|------------------------|------------------------|-------------------|---------------------|

| PORTE <sup>(3)</sup>  | _                  | —                                       |                     | _                      | RE3 <sup>(5)</sup>     | RE2 <sup>(3)</sup>      | RE1 <sup>(3)</sup>     | RE0 <sup>(3)</sup>     | xxxx              | 52, 145             |

| PORTD <sup>(3)</sup>  | Read PORTD         | Read PORTD pins, Write PORTD Data Latch |                     |                        |                        |                         |                        |                        |                   | 52, 138             |

| PORTC                 | Read PORTC         | pins, Write P                           | ORTC Data L         | .atch                  |                        |                         |                        |                        | xxxx xxxx         | 52, 135             |

| PORTB                 | Read PORTB         | pins, Write P                           | ORTB Data L         | atch                   |                        |                         |                        |                        | xxxx xxxx         | 52, 132             |

| PORTA                 | RA7 <sup>(6)</sup> | RA6 <sup>(6)</sup>                      | Read PORT           | A pins, Write          | PORTA Data I           | _atch                   |                        |                        | xx00 0000         | 52, 129             |

| ECANCON               | MDSEL1             | MDSEL0                                  | FIFOWM              | EWIN4                  | EWIN3                  | EWIN2                   | EWIN1                  | EWIN0                  | 0001 000          | 52, 280             |

| TXERRCNT              | TEC7               | TEC6                                    | TEC5                | TEC4                   | TEC3                   | TEC2                    | TEC1                   | TEC0                   | 0000 0000         | 52, 285             |

| RXERRCNT              | REC7               | REC6                                    | REC5                | REC4                   | REC3                   | REC2                    | REC1                   | REC0                   | 0000 0000         | 52, 293             |

| COMSTAT<br>Mode 0     | RXB0OVFL           | RXB1OVFL                                | ТХВО                | TXBP                   | RXBP                   | TXWARN                  | RXWARN                 | EWARN                  | 0000 0000         | 52, 281             |

| COMSTAT<br>Mode 1     | —                  | RXBnOVFL                                | ТХВО                | TXBP                   | RXBP                   | TXWARN                  | RXWARN                 | EWARN                  | -000 0000         | 52, 281             |

| COMSTAT<br>Mode 2     | FIFOEMPTY          | RXBnOVFL                                | ТХВО                | TXBP                   | RXBP                   | TXWARN                  | RXWARN                 | EWARN                  | 0000 0000         | 52, 281             |

| CIOCON                | _                  | _                                       | ENDRHI              | CANCAP                 | _                      | _                       | _                      | _                      | 00                | 52, 314             |

| BRGCON3               | WAKDIS             | WAKFIL                                  | _                   | _                      | _                      | SEG2PH2                 | SEG2PH1                | SEG2PH0                | 00000             | 52, 313             |

| BRGCON2               | SEG2PHTS           | SAM                                     | SEG1PH2             | SEG1PH1                | SEG1PH0                | PRSEG2                  | PRSEG1                 | PRSEG0                 | 0000 0000         | 52, 312             |

| BRGCON1               | SJW1               | SJW0                                    | BRP5                | BRP4                   | BRP3                   | BRP2                    | BRP1                   | BRP0                   | 0000 0000         | 52, 311             |

| CANCON<br>Mode 0      | REQOP2             | REQOP1                                  | REQOP0              | ABAT                   | WIN2 <sup>(7)</sup>    | WIN1 <sup>(7)</sup>     | WIN0 <sup>(7)</sup>    | (7)                    | 1000 000-         | 53, 276             |

| CANCON<br>Mode 1      | REQOP2             | REQOP1                                  | REQOP0              | ABAT                   | (7)                    | (7)                     | (7)                    | (7)                    | 1000              | 53, 276             |

| CANCON<br>Mode 2      | REQOP2             | REQOP1                                  | REQOP0              | ABAT                   | FP3 <sup>(7)</sup>     | FP2 <sup>(7)</sup>      | FP1 <sup>(7)</sup>     | FP0 <sup>(7)</sup>     | 1000 0000         | 53, 276             |

| CANSTAT<br>Mode 0     | OPMODE2            | OPMODE1                                 | OPMODE0             | (7)                    | ICODE3 <sup>(7)</sup>  | ICODE2 <sup>(7)</sup>   | ICODE1 <sup>(7)</sup>  | (7)                    | 000- 0000         | 53, 277             |

| CANSTAT<br>Modes 1, 2 | OPMODE2            | OPMODE1                                 | OPMODE0             | EICODE4 <sup>(7)</sup> | EICODE3 <sup>(7)</sup> | EICODE2 <sup>(7)</sup>  | EICODE1 <sup>(7)</sup> | EICODE0 <sup>(7)</sup> | 0000 0000         | 53, 277             |

| RXB0D7                | RXB0D77            | RXB0D76                                 | RXB0D75             | RXB0D74                | RXB0D73                | RXB0D72                 | RXB0D71                | RXB0D70                | xxxx xxxx         | 53, 292             |

| RXB0D6                | RXB0D67            | RXB0D66                                 | RXB0D65             | RXB0D64                | RXB0D63                | RXB0D62                 | RXB0D61                | RXB0D60                | xxxx xxxx         | 53, 292             |

| RXB0D5                | RXB0D57            | RXB0D56                                 | RXB0D55             | RXB0D54                | RXB0D53                | RXB0D52                 | RXB0D51                | RXB0D50                | xxxx xxxx         | 53, 292             |

| RXB0D4                | RXB0D47            | RXB0D46                                 | RXB0D45             | RXB0D44                | RXB0D43                | RXB0D42                 | RXB0D41                | RXB0D40                | xxxx xxxx         | 53, 292             |

| RXB0D3                | RXB0D37            | RXB0D36                                 | RXB0D35             | RXB0D34                | RXB0D33                | RXB0D32                 | RXB0D31                | RXB0D30                | xxxx xxxx         | 53, 292             |

| RXB0D2                | RXB0D27            | RXB0D26                                 | RXB0D25             | RXB0D24                | RXB0D23                | RXB0D22                 | RXB0D21                | RXB0D20                | xxxx xxxx         | 53, 292             |

| RXB0D1                | RXB0D17            | RXB0D16                                 | RXB0D15             | RXB0D14                | RXB0D13                | RXB0D12                 | RXB0D11                | RXB0D10                | xxxx xxxx         | 53, 292             |

| RXB0D0                | RXB0D07            | RXB0D06                                 | RXB0D05             | RXB0D04                | RXB0D03                | RXB0D02                 | RXB0D01                | RXB0D00                | xxxx xxxx         | 53, 292             |

| RXB0DLC               |                    | RXRTR                                   | RB1                 | RB0                    | DLC3                   | DLC2                    | DLC1                   | DLC0                   | -xxx xxxx         | 53, 292             |

| RXB0EIDL              | EID7               | EID6                                    | EID5                | EID4                   | EID3                   | EID2                    | EID1                   | EID0                   | XXXX XXXX         | 53, 291             |

| RXB0EIDH              | EID15              | EID14                                   | EID13               | EID12                  | EID11                  | EID10                   | EID9                   | EID8                   | XXXX XXXX         | 53, 291             |

| RXB0SIDL              | SID2               | SID1                                    | SID0                | SRR                    | EXID                   |                         | EID17                  | EID16                  | xxxx x-xx         | 53, 291             |

| RXB0SIDH              | SID10              | SID9                                    | SID8                | SID7                   | SID6                   | SID5                    | SID4                   | SID3                   | xxxx xxxx         | 53, 290             |

| RXB0CON<br>Mode 0     | RXFUL              | RXM1                                    | RXM0 <sup>(7)</sup> | (7)                    | RXRTRRO <sup>(7)</sup> | RXBODBEN <sup>(7)</sup> | JTOFF <sup>(7)</sup>   | FILHITO <sup>(7)</sup> | 000- 0000         | 53, 287             |

| RXB0CON<br>Mode 1, 2  | RXFUL              | RXM1                                    | RTRRO               | FILHIT4                | FILHIT3                | FILHIT2                 | FILHIT1                | FILHIT0                | 0000 0000         | 53, 287             |

#### TABLE 5-2:REGISTER FILE SUMMARY (PIC18F2585/2680/4585/4680) (CONTINUED)

**Legend:** x = unknown, u = unchanged, - = unimplemented, q = value depends on condition

Note 1: Bit 21 of the PC is only available in Test mode and Serial Programming modes.

2: The SBOREN bit is only available when CONFIG2L<1:0> = 01; otherwise, it is disabled and reads as '0'. See Section 4.4 "Brown-out Reset (BOR)".

3: These registers and/or bits are not implemented on PIC18F2X8X devices and are read as '0'. Reset values are shown for PIC18F4X8X devices; individual unimplemented bits should be interpreted as '---'.

4: The PLLEN bit is only available in specific oscillator configuration; otherwise, it is disabled and reads as '0'. See Section 2.6.4 "PLL in INTOSC Modes".

5: The RE3 bit is only available when Master Clear Reset is disabled (CONFIG3H<7> = 0); otherwise, RE3 reads as '0'. This bit is read-only.

6: RA6/RA7 and their associated latch and direction bits are individually configured as port pins based on various primary oscillator modes. When disabled, these bits read as '0'.

7: CAN bits have multiple functions depending on the selected mode of the CAN module.

8: This register reads all '0's until the ECAN<sup>™</sup> technology is set up in Mode 1 or Mode 2.

9: These registers are available on PIC18F4X8X devices only.

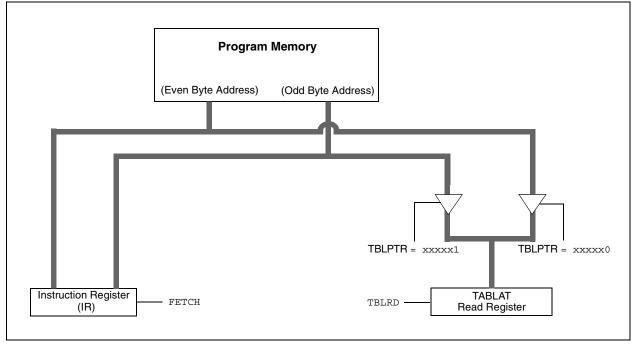

#### 6.3 Reading the Flash Program Memory

The TBLRD instruction is used to retrieve data from program memory and places it into data RAM. Table reads from program memory are performed one byte at a time.

TBLPTR points to a byte address in program space. Executing TBLRD places the byte pointed to into TABLAT. In addition, TBLPTR can be modified automatically for the next table read operation.

The internal program memory is typically organized by words. The Least Significant bit of the address selects between the high and low bytes of the word. Figure 6-4 shows the interface between the internal program memory and the TABLAT.

#### FIGURE 6-4: READS FROM FLASH PROGRAM MEMORY

#### EXAMPLE 6-1: READING A FLASH PROGRAM MEMORY WORD

|           | MOVLW   | CODE_ADDR_UPPER | ; | Load TBLPTR with the base      |

|-----------|---------|-----------------|---|--------------------------------|

|           | MOVWF   | TBLPTRU         | ; | address of the word            |

|           | MOVLW   | CODE_ADDR_HIGH  |   |                                |

|           | MOVWF   | TBLPTRH         |   |                                |

|           | MOVLW   | CODE_ADDR_LOW   |   |                                |

|           | MOVWF   | TBLPTRL         |   |                                |

| READ_WORD |         |                 |   |                                |

| _         | TBLRD*+ |                 | ; | read into TABLAT and increment |

|           | MOVF    | TABLAT, W       | ; | get data                       |

|           | MOVWF   | WORD EVEN       |   |                                |

|           | TBLRD*+ |                 | ; | read into TABLAT and increment |

|           | MOVF    | TABLAT, W       | ; | get data                       |

|           | MOVF    | WORD ODD        |   |                                |

|           |         | _               |   |                                |

## 9.6 INTn Pin Interrupts

External interrupts on the RB0/INT0, RB1/INT1 and RB2/INT2 pins are edge-triggered. If the corresponding INTEDGx bit in the INTCON2 register is set (= 1), the interrupt is triggered by a rising edge; if the bit is clear, the trigger is on the falling edge. When a valid edge appears on the RBx/INTx pin, the corresponding flag bit INTxF is set. This interrupt can be disabled by clearing the corresponding enable bit INTxE. Flag bit INTxF must be cleared in software in the Interrupt.

All external interrupts (INT0, INT1 and INT2) can wake-up the processor from the power managed modes, if bit INTxE was set prior to going into power managed modes. If the Global Interrupt Enable bit, GIE, is set, the processor will branch to the interrupt vector following wake-up.

Interrupt priority for INT1 and INT2 is determined by the value contained in the interrupt priority bits, INT1IP (INTCON3<6>) and INT2IP (INTCON3<7>). There is no priority bit associated with INT0. It is always a high priority interrupt source.

## 9.7 TMR0 Interrupt

In 8-bit mode (which is the default), an overflow in the TMR0 register (FFh  $\rightarrow$  00h) will set flag bit TMR0IF. In 16-bit mode, an overflow in the TMR0H:TMR0L register pair (FFFFh  $\rightarrow$  0000h) will set TMR0IF. The interrupt can be enabled/disabled by setting/clearing enable bit TMR0IE (INTCON<5>). Interrupt priority for Timer0 is determined by the value contained in the interrupt priority bit, TMR0IP (INTCON2<2>). See Section 11.0 "Timer0 Module" for further details on the Timer0 module.

### 9.8 PORTB Interrupt-on-Change

An input change on PORTB<7:4> sets flag bit, RBIF (INTCON<0>). The interrupt can be enabled/disabled by setting/clearing enable bit, RBIE (INTCON<3>). Interrupt priority for PORTB interrupt-on-change is determined by the value contained in the interrupt priority bit, RBIP (INTCON2<0>).

### 9.9 Context Saving During Interrupts

During interrupts, the return PC address is saved on the stack. Additionally, the WREG, STATUS and BSR registers are saved on the fast return stack. If a fast return from interrupt is not used (See **Section 5.3 "Data Memory Organization**"), the user may need to save the WREG, STATUS and BSR registers on entry to the Interrupt Service Routine. Depending on the user's application, other registers may also need to be saved. Example 9-1 saves and restores the WREG, STATUS and BSR registers during an Interrupt Service Routine.

| MOVWF  | W_TEMP              | ; W_TEMP is in virtual bank    |

|--------|---------------------|--------------------------------|

| MOVFF  | STATUS, STATUS_TEMP | ; STATUS_TEMP located anywhere |

| MOVFF  | BSR, BSR_TEMP       | ; BSR_TMEP located anywhere    |

| ;      |                     |                                |

| ; USER | ISR CODE            |                                |

| ;      |                     |                                |

| MOVFF  | BSR_TEMP, BSR       | ; Restore BSR                  |

| MOVF   | W_TEMP, W           | ; Restore WREG                 |

| MOVFF  | STATUS TEMP, STATUS | ; Restore STATUS               |

EXAMPLE 9-1: SAVING STATUS, WREG AND BSR REGISTERS IN RAM

-n = Value at POR

| ER 10-1: | I RISE RE               | GISTER (I                        |                |                       | ONLT)         |              |              |              |

|----------|-------------------------|----------------------------------|----------------|-----------------------|---------------|--------------|--------------|--------------|

|          | R-0                     | R-0                              | R/W-0          | R/W-0                 | U-0           | R/W-1        | R/W-1        | R/W-1        |

|          | IBF                     | OBF                              | IBOV           | PSPMODE               | _             | TRISE2       | TRISE1       | TRISE0       |

|          | bit 7                   |                                  |                |                       |               |              |              | bit 0        |

|          |                         |                                  |                |                       |               |              |              |              |

| bit 7    | IBF: Input              | Buffer Full S                    | Status bit     |                       |               |              |              |              |

|          |                         | l has been r<br>rd has been      |                | l waiting to be       | read by the   | e CPU        |              |              |

| bit 6    | OBF: Outp               | out Buffer Fu                    | ull Status bit |                       |               |              |              |              |

|          |                         | itput buffer s<br>itput buffer h |                | oreviously writ<br>ad | tten word     |              |              |              |

| bit 5    | IBOV: Inpu              | ut Buffer Ove                    | erflow Deteo   | ct bit (in Micro      | processor r   | node)        |              |              |

|          |                         | e occurred wi<br>erflow occu     | •              | usly input word       | l has not bee | en read (mus | t be cleared | in software) |

| bit 4    | PSPMODE                 | : Parallel S                     | lave Port M    | ode Select bit        |               |              |              |              |

|          |                         | I Slave Port                     |                |                       |               |              |              |              |

|          |                         | al Purpose I                     |                |                       |               |              |              |              |

| bit 3    | •                       | ented: Rea                       |                |                       |               |              |              |              |

| bit 2    |                         | E2 Direction                     | n Control bi   | t                     |               |              |              |              |

|          | 1 = Input<br>0 = Output | :                                |                |                       |               |              |              |              |

| bit 1    | TRISE1: R               | E1 Direction                     | n Control bi   | t                     |               |              |              |              |

|          | 1 = Input               |                                  |                |                       |               |              |              |              |

|          | 0 = Output              |                                  |                |                       |               |              |              |              |

| bit 0    | TRISE0: R               | E0 Direction                     | n Control bi   | t                     |               |              |              |              |

|          | 1 = Input<br>0 = Output | :                                |                |                       |               |              |              |              |

|          | Legend:                 |                                  |                |                       |               |              |              |              |

|          | R = Reada               | ble bit                          | W = V          | Vritable bit          | U = Unim      | plemented    | bit, read as | '0'          |

|          | 1                       |                                  |                |                       |               |              |              |              |

#### REGISTER 10-1: TRISE REGISTER (PIC18F4X8X DEVICES ONLY)

'1' = Bit is set

'0' = Bit is cleared

x = Bit is unknown

## 14.0 TIMER3 MODULE

The Timer3 module timer/counter incorporates these features:

- Software selectable operation as a 16-bit timer or counter

- Readable and writable 8-bit registers (TMR3H and TMR3L)

- Selectable clock source (internal or external) with device clock or Timer1 oscillator internal options

- Interrupt-on-overflow

- Module Reset on CCP1 special event trigger

A simplified block diagram of the Timer3 module is shown in Figure 14-1. A block diagram of the module's operation in Read/Write mode is shown in Figure 14-2.

The Timer3 module is controlled through the T3CON register (Register 14-1). It also selects the clock source options for the CCP1 modules (see **Section 15.1.1** "**CCP1 Modules and Timer Resources**" for more information).

### REGISTER 14-1: T3CON: TIMER3 CONTROL REGISTER

| R/W-0 | R/W-0                  | R/W-0   | R/W-0   | R/W-0                 | R/W-0         | R/W-0  | R/W-0  |

|-------|------------------------|---------|---------|-----------------------|---------------|--------|--------|

| RD16  | T3ECCP1 <sup>(1)</sup> | T3CKPS1 | T3CKPS0 | T3CCP1 <sup>(1)</sup> | <b>T3SYNC</b> | TMR3CS | TMR3ON |

| bit 7 |                        |         |         |                       |               |        | bit 0  |

| bit 7   | <b>RD16:</b> 16-bit Read/Write Mode Enable bit                                                                                                                                                                                                                                                                                                                        |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>1 = Enables register read/write of Timer3 in one 16-bit operation</li> <li>0 = Enables register read/write of Timer3 in two 8-bit operations</li> </ul>                                                                                                                                                                                                      |

| bit 6,3 | T3ECCP1:T3CCP1: Timer3 and Timer1 to ECCP1/CCP1 Enable bits <sup>(1)</sup><br>1x = Timer3 is the capture/compare clock source for both CCP1 and ECCP1 modules<br>01 = Timer3 is the capture/compare clock source for ECCP1;<br>Timer1 is the capture/compare clock source for CCP1<br>00 = Timer1 is the capture/compare clock source for both CCP1 and ECCP1 modules |

|         | Note 1: These bits are available on PIC18F4X8X devices only.                                                                                                                                                                                                                                                                                                          |

| bit 5-4 | <b>T3CKPS1:T3CKPS0</b> : Timer3 Input Clock Prescale Select bits<br>11 = 1:8 Prescale value<br>10 = 1:4 Prescale value<br>01 = 1:2 Prescale value<br>00 = 1:1 Prescale value                                                                                                                                                                                          |

| bit 2   | T3SYNC: Timer3 External Clock Input Synchronization Control bit         (Not usable if the device clock comes from Timer1/Timer3.)         When TMR3CS = 1:         1 = Do not synchronize external clock input         0 = Synchronize external clock input         When TMR3CS = 0:         This bit is ignored. Timer3 uses the internal clock when TMR3CS = 0.    |

| bit 1   | <ul> <li>TMR3CS: Timer3 Clock Source Select bit</li> <li>1 = External clock input from Timer1 oscillator or T13CKI (on the rising edge after the first falling edge)</li> <li>0 = Internal clock (FOSC/4)</li> </ul>                                                                                                                                                  |

| bit 0   | TMR3ON: Timer3 On bit<br>1 = Enables Timer3<br>0 = Stops Timer3                                                                                                                                                                                                                                                                                                       |

|         | Legend:                                                                                                                                                                                                                                                                                                                                                               |

| Legena:           |                  |                                        |

|-------------------|------------------|----------------------------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0'     |

| -n = Value at POR | '1' = Bit is set | 0' = Bit is cleared x = Bit is unknown |

NOTES:

The ECCPR1H register and a 2-bit internal latch are used to double-buffer the PWM duty cycle. This double-buffering is essential for glitchless PWM operation.

When the ECCPR1H and 2-bit latch match TMR2, concatenated with an internal 2-bit Q clock or 2 bits of the TMR2 prescaler, the CCP1 pin is cleared.

The maximum PWM resolution (bits) for a given PWM frequency is given by the equation.

#### EQUATION 15-3:

PWM Resolution (max) =

$$\frac{\log\left(\frac{FOSC}{FPWM}\right)}{\log(2)}$$

bits

Note: If the PWM duty cycle value is longer than the PWM period, the ECCP1 pin will not be cleared.

## TABLE 15-4: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS AT 40 MHz

| PWM Frequency              | 2.44 kHz | 9.77 kHz | 39.06 kHz | 156.25 kHz | 312.50 kHz | 416.67 kHz |

|----------------------------|----------|----------|-----------|------------|------------|------------|

| Timer Prescaler (1, 4, 16) | 16       | 4        | 1         | 1          | 1          | 1          |

| PR2 Value                  | FFh      | FFh      | FFh       | 3Fh        | 1Fh        | 17h        |

| Maximum Resolution (bits)  | 14       | 12       | 10        | 8          | 7          | 6.58       |

#### 15.4.3 PWM AUTO-SHUTDOWN (ECCP1 ONLY)

The PWM auto-shutdown features of the Enhanced CCP1 module are available to ECCP1 in PIC18F4585/4680 (40/44-pin) devices. The operation of this feature is discussed in detail in **Section 16.4.7** "Enhanced PWM Auto-Shutdown".

Auto-shutdown features are not available for CCP1.

### 15.4.4 SETUP FOR PWM OPERATION

The following steps should be taken when configuring the CCP1 module for PWM operation:

- 1. Set the PWM period by writing to the PR2 register.

- Set the PWM duty cycle by writing to the CCPR1L register and CCP1CON<5:4> bits.

- 3. Make the CCP1 pin an output by clearing the appropriate TRIS bit.

- 4. Set the TMR2 prescale value, then enable Timer2 by writing to T2CON.

- 5. Configure the CCP1 module for PWM operation.

#### 17.3.8 OPERATION IN POWER MANAGED MODES

In SPI Master mode, module clocks may be operating at a different speed than when in full power mode; in the case of the Sleep mode, all clocks are halted.

In most power managed modes, a clock is provided to the peripherals. That clock should be from the primary clock source, the secondary clock (Timer1 oscillator at 32.768 kHz) or the INTOSC source. See **Section 2.7 "Clock Sources and Oscillator Switching**" for additional information.

In most cases, the speed that the master clocks SPI data is not important; however, this should be evaluated for each system.

If MSSP interrupts are enabled, they can wake the controller from Sleep mode, or one of the Idle modes, when the master completes sending data. If an exit from Sleep or Idle mode is not desired, MSSP interrupts should be disabled.

If the Sleep mode is selected, all module clocks are halted and the transmission/reception will remain in that state until the devices wakes. After the device returns to Run mode, the module will resume transmitting and receiving data.

In SPI Slave mode, the SPI Transmit/Receive Shift register operates asynchronously to the device. This allows the device to be placed in any power managed mode and data to be shifted into the SPI Transmit/ Receive Shift register. When all 8 bits have been received, the MSSP interrupt flag bit will be set and if enabled, will wake the device.

### 17.3.9 EFFECTS OF A RESET

A Reset disables the MSSP module and terminates the current transfer.

#### 17.3.10 BUS MODE COMPATIBILITY

Table 17-1 shows the compatibility between the standard SPI modes and the states of the CKP and CKE control bits.

| Standard SPI Mode | Control Bits State |     |  |  |  |

|-------------------|--------------------|-----|--|--|--|

| Terminology       | СКР                | CKE |  |  |  |

| 0, 0              | 0                  | 1   |  |  |  |

| 0, 1              | 0                  | 0   |  |  |  |

| 1, 0              | 1                  | 1   |  |  |  |

| 1, 1              | 1                  | 0   |  |  |  |

#### TABLE 17-1: SPI BUS MODES

There is also a SMP bit which controls when the data is sampled.

| Name    | Bit 7                                                    | Bit 6         | Bit 5    | Bit 4         | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

|---------|----------------------------------------------------------|---------------|----------|---------------|-------|--------|--------|--------|----------------------------|

| INTCON  | GIE/GIEH                                                 | PEIE/GIEL     | TMR0IE   | <b>INTOIE</b> | RBIE  | TMR0IF | INT0IF | RBIF   | 49                         |

| PIR1    | PSPIF <sup>(1)</sup>                                     | ADIF          | RCIF     | TXIF          | SSPIF | CCP1IF | TMR2IF | TMR1IF | 52                         |

| PIE1    | PSPIE <sup>(1)</sup>                                     | ADIE          | RCIE     | TXIE          | SSPIE | CCP1IE | TMR2IE | TMR1IE | 52                         |

| IPR1    | PSPIP <sup>(1)</sup>                                     | ADIP          | RCIP     | TXIP          | SSPIP | CCP1IP | TMR2IP | TMR1IP | 52                         |

| TRISA   | PORTA Da                                                 | ta Direction  | Register |               |       |        |        |        | 52                         |

| TRISC   | PORTC Da                                                 | ata Direction | Register |               |       |        |        |        | 52                         |

| SSPBUF  | Synchronous Serial Port Receive Buffer/Transmit Register |               |          |               |       |        |        |        | 50                         |

| SSPCON1 | WCOL                                                     | SSPOV         | SSPEN    | CKP           | SSPM3 | SSPM2  | SSPM1  | SSPM0  | 50                         |

| SSPSTAT | SMP                                                      | CKE           | D/A      | Р             | S     | R/W    | UA     | BF     | 50                         |

TABLE 17-2: REGISTERS ASSOCIATED WITH SPI OPERATION

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by the MSSP in SPI mode.

**Note 1:** These bits are unimplemented in PIC18F2X8X devices; always maintain these bits clear.

### REGISTER 23-24: BnSIDH: TX/RX BUFFER n STANDARD IDENTIFIER REGISTERS, HIGH BYTE IN RECEIVE MODE $[0 \le n \le 5, TXnEN (BSEL0<n>) = 0]^{(1)}$

| R-x   | R-x  | R-x  | R-x  | R-x  | R-x  | R-x  | R-x   |

|-------|------|------|------|------|------|------|-------|

| SID10 | SID9 | SID8 | SID7 | SID6 | SID5 | SID4 | SID3  |

| bit 7 |      |      |      |      |      |      | bit 0 |

bit 7-0 **SID10:SID3:** Standard Identifier bits (if EXIDE (BnSIDL<3>) = 0) Extended Identifier bits EID28:EID21 (if EXIDE = 1).

**Note 1:** These registers are available in Mode 1 and 2 only.

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

## REGISTER 23-25: BnSIDH: TX/RX BUFFER n STANDARD IDENTIFIER REGISTERS,

#### HIGH BYTE IN TRANSMIT MODE $[0 \le n \le 5, TXnEN (BSEL0 < n >) = 1]^{(1)}$

| R/W-x |

|-------|-------|-------|-------|-------|-------|-------|-------|

| SID10 | SID9  | SID8  | SID7  | SID6  | SID5  | SID4  | SID3  |

| bit 7 |       |       |       |       |       |       | bit 0 |

bit 7-0 **SID10:SID3:** Standard Identifier bits (if EXIDE (BnSIDL<3>) = 0) Extended Identifier bits EID28:EID21 (if EXIDE = 1).

Note 1: These registers are available in Mode 1 and 2 only.

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | l bit, read as '0' |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

## REGISTER 23-35: BnDLC: TX/RX BUFFER n DATA LENGTH CODE REGISTERS IN TRANSMIT MODE $[0 \le n \le 5, TXnEN (BSEL < n >) = 1]^{(1)}$

|         | $[0 \ge 11 \ge 0]$ |                 | 022/11/) -      | - <b>-</b> 1.               |             |       |       |       |

|---------|--------------------|-----------------|-----------------|-----------------------------|-------------|-------|-------|-------|

|         | U-0                | R/W-x           | U-0             | U-0                         | R/W-x       | R/W-x | R/W-x | R/W-x |

|         | —                  | TXRTR           | —               | —                           | DLC3        | DLC2  | DLC1  | DLC0  |

|         | bit 7              |                 |                 |                             |             |       |       | bit 0 |

|         |                    |                 |                 |                             |             |       |       |       |

| bit 7   | Unimplem           | ented: Read     | <b>d as</b> '0' |                             |             |       |       |       |

| bit 6   | TXRTR: Tra         | ansmitter Re    | emote Trans     | mission Rec                 | uest bit    |       |       |       |

|         |                    |                 |                 | RTR bit set<br>RTR bit clea |             |       |       |       |

| bit 5-4 | Unimplem           | ented: Read     | <b>d as</b> '0' |                             |             |       |       |       |

| bit 3-0 | DLC3:DLC           | 0: Data Len     | gth Code bit    | ts                          |             |       |       |       |

|         |                    | = Reserve       |                 |                             |             |       |       |       |

|         |                    | ta length = 8   | •               |                             |             |       |       |       |

|         |                    | ta length = 7   | •               |                             |             |       |       |       |

|         |                    | ta length = $6$ | •               |                             |             |       |       |       |

|         |                    | ta length = $5$ | •               |                             |             |       |       |       |

|         |                    | ta length = $4$ | -               |                             |             |       |       |       |

|         |                    | ta length = 3   | •               |                             |             |       |       |       |

|         |                    | ta length = $2$ | •               |                             |             |       |       |       |

|         |                    | ta length = $1$ | -               |                             |             |       |       |       |

|         | 0000 = Dat         | ta length = C   | ) bytes         |                             |             |       |       |       |

|         | Note 1:            | These regi      | sters are av    | ailable in Mo               | ode 1 and 2 | only. |       |       |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

## REGISTER 23-36: BSEL0: BUFFER SELECT REGISTER 0<sup>(1)</sup>

| R/W-0  | R/W-0  | R/W-0         | R/W-0  | R/W-0  | R/W-0  | U-0 | U-0   |

|--------|--------|---------------|--------|--------|--------|-----|-------|

| B5TXEN | B4TXEN | <b>B3TXEN</b> | B2TXEN | B1TXEN | B0TXEN | _   | —     |

| bit 7  |        |               |        |        |        |     | bit 0 |

#### bit 7-2 B5TXEN:B0TXEN: Buffer 5 to Buffer 0 Transmit Enable bit

1 = Buffer is configured in Transmit mode

0 = Buffer is configured in Receive mode

bit 1-0 Unimplemented: Read as '0'

**Note 1:** This register is available in Mode 1 and 2 only.

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

| REGISTER 23-57: | PIE3: PEI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | RIPHERAI                                                                                                                                                    |                               | UPT ENAI     | BLE REGIS               | STER                  |        |          |  |  |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|--------------|-------------------------|-----------------------|--------|----------|--|--|

| Mode 0          | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | R/W-0                                                                                                                                                       | R/W-0                         | R/W-0        | R/W-0                   | R/W-0                 | R/W-0  | R/W-0    |  |  |

| Mode 0          | IRXIE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | WAKIE                                                                                                                                                       | ERRIE                         | TXB2IE       | TXB1IE <sup>(1)</sup>   | TXB0IE <sup>(1)</sup> | RXB1IE | RXB0IE   |  |  |

|                 | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | R/W-0                                                                                                                                                       | R/W-0                         | R/W-0        | R/W-0                   | R/W-0                 | R/W-0  | R/W-0    |  |  |

| Mode 1, 2       | IRXIE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | WAKIE                                                                                                                                                       | ERRIE                         | TXBnIE       | TXB1IE <sup>(1)</sup>   | TXB0IE <sup>(1)</sup> | RXBnIE | FIFOWMIE |  |  |

|                 | bit 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                             |                               |              |                         |                       |        | bit 0    |  |  |

| L:+ <b>7</b>    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                             |                               |              |                         | L :1                  |        |          |  |  |

| bit 7           | 1 = Enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | IRXIE: CAN Invalid Received Message Interrupt Enable bit<br>1 = Enable invalid message received interrupt<br>0 = Disable invalid message received interrupt |                               |              |                         |                       |        |          |  |  |

| bit 6           | 1 = Enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | AN bus Act<br>bus activit<br>e bus activi                                                                                                                   | y wake-up                     |              | Enable bit              |                       |        |          |  |  |

| bit 5           | 1 = Enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | AN bus Erro<br>e CAN bus<br>e CAN bus                                                                                                                       | error interru                 | ıpt          |                         |                       |        |          |  |  |

| bit 4           | <b>TXB2IE:</b> (<br>1 = Enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | e Transmit E                                                                                                                                                | nit Buffer 2<br>Buffer 2 inte |              | able bit                |                       |        |          |  |  |

|                 | <ul> <li>0 = Disable Transmit Buffer 2 interrupt</li> <li><u>When CAN is in Mode 1 or 2:</u></li> <li><b>TXBnIE:</b> CAN Transmit Buffer Interrupts Enable bit</li> <li>1 = Enable transmit buffer interrupt; individual interrupt is enabled by TXBIE and BIE0</li> <li>0 = Disable all transmit buffer interrupts</li> </ul>                                                                                                                                                                                                                                                                                             |                                                                                                                                                             |                               |              |                         |                       |        |          |  |  |

| bit 3           | 1 = Enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | CAN Transn<br>e Transmit E<br>e Transmit                                                                                                                    | Buffer 1 inte                 |              | able bit <sup>(1)</sup> |                       |        |          |  |  |

| bit 2           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                             |                               | Interrupt En | able bit <sup>(1)</sup> |                       |        |          |  |  |

|                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | e Transmit E<br>e Transmit                                                                                                                                  |                               |              |                         |                       |        |          |  |  |

| bit 1           | <b>RXB1IE:</b> CAN Receive Buffer 1 Interrupt Enable bit         1 = Enable Receive Buffer 1 interrupt         0 = Disable Receive Buffer 1 interrupt         When CAN is in Mode 1 or 2: <b>RXBnIE:</b> CAN Receive Buffer Interrupts Enable bit         1 = Enable receive buffer interrupt; individual interrupt is enabled by BIE0                                                                                                                                                                                                                                                                                     |                                                                                                                                                             |                               |              |                         |                       |        |          |  |  |

| bit 0           | <ul> <li>0 = Disable all receive buffer interrupts</li> <li>bit 0 When CAN is in Mode 0:<br/><b>RXBOIE:</b> CAN Receive Buffer 0 Interrupt Enable bit         1 = Enable Receive Buffer 0 interrupt         0 = Disable Receive Buffer 0 interrupt         When CAN is in Mode 1:         Unimplemented: Read as '0'         When CAN is in Mode 2:         FIFOWMIE: FIFO Watermark Interrupt Enable bit         1 = Enable FIFO watermark interrupt         0 = Disable FIFO watermark interrupt         0 = Disable FIFO watermark interrupt         Note 1: In CAN Mode 1 and 2, this bit is forced to '0'.</li> </ul> |                                                                                                                                                             |                               |              |                         |                       |        |          |  |  |

|                 | Legend:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                             |                               |              |                         |                       |        |          |  |  |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented b  | oit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### 23.5.4 PROGRAMMABLE AUTO-RTR BUFFERS

In Mode 1 and 2, any of six programmable transmit/ receive buffers may be programmed to automatically respond to predefined RTR messages without user firmware intervention. Automatic RTR handling is enabled by setting the TXnEN bit in the BSEL0 register and the RTREN bit in the BnCON register. After this setup, when an RTR request is received, the TXREQ bit is automatically set and the current buffer content is automatically queued for transmission as a RTR response. As with all transmit buffers, once the TXREQ bit is set, buffer registers become read-only and any writes to them will be ignored.

The following outlines the steps required to automatically handle RTR messages:

- 1. Set buffer to Transmit mode by setting TXnEN bit to '1' in BSEL0 register.

- 2. At least one acceptance filter must be associated with this buffer and preloaded with expected RTR identifier.

- 3. Bit RTREN in BnCON register must be set to '1'.

- 4. Buffer must be preloaded with the data to be sent as a RTR response.

Normally, user firmware will keep buffer data registers up to date. If firmware attempts to update the buffer while an automatic RTR response is in the process of transmission, all writes to buffers are ignored.

## 23.6 CAN Message Transmission

#### 23.6.1 INITIATING TRANSMISSION

For the MCU to have write access to the message buffer, the TXREQ bit must be clear, indicating that the message buffer is clear of any pending message to be transmitted. At a minimum, the SIDH, SIDL and DLC registers must be loaded. If data bytes are present in the message, the data registers must also be loaded. If the message is to use extended identifiers, the EIDH:EIDL registers must also be loaded and the EXIDE bit set.

To initiate message transmission, the TXREQ bit must be set for each buffer to be transmitted. When TXREQ is set, the TXABT, TXLARB and TXERR bits will be cleared. To successfully complete the transmission, there must be at least one node with matching baud rate on the network. Setting the TXREQ bit does not initiate a message transmission; it merely flags a message buffer as ready for transmission. Transmission will start when the device detects that the bus is available. The device will then begin transmission of the highest priority message that is ready.

When the transmission has completed successfully, the TXREQ bit will be cleared, the TXBnIF bit will be set and an interrupt will be generated if the TXBnIE bit is set.

If the message transmission fails, the TXREQ will remain set, indicating that the message is still pending for transmission and one of the following condition flags will be set. If the message started to transmit but encountered an error condition, the TXERR and the IRXIF bits will be set and an interrupt will be generated. If the message lost arbitration, the TXLARB bit will be set.

### 23.6.2 ABORTING TRANSMISSION

The MCU can request to abort a message by clearing the TXREQ bit associated with the corresponding message buffer (TXBnCON<3> or BnCON<3>). Setting the ABAT bit (CANCON<4>) will request an abort of all pending messages. If the message has not yet started transmission, or if the message started but is interrupted by loss of arbitration or an error, the abort will be processed. The abort is indicated when the module sets the TXABT bit for the corresponding buffer (TXBnCON<6> or BnCON<6>). If the message has started to transmit, it will attempt to transmit the current message fully. If the current message is transmitted fully and is not lost to arbitration or an error, the TXABT bit will not be set because the message was transmitted successfully. Likewise, if a message is being transmitted during an abort request and the message is lost to arbitration or an error, the message will not be retransmitted and the TXABT bit will be set, indicating that the message was successfully aborted.

Once an abort is requested by setting the ABAT or TXABT bits, it cannot be cleared to cancel the abort request. Only CAN module hardware or a POR condition can clear it.

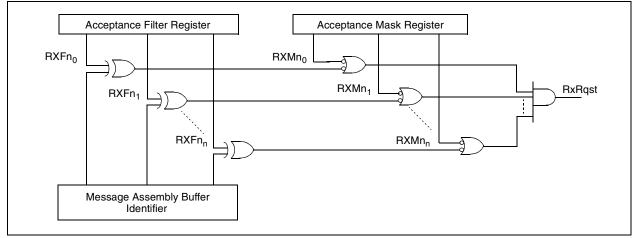

In Mode 1 and 2, there are an additional 10 acceptance filters, RXF6-RXF15, creating a total of 16 available filters. RXF15 can be used either as an acceptance filter or acceptance mask register. Each of these acceptance filters can be individually enabled or disabled by setting or clearing the RXFENn bit in the RXFCONn register. Any of these 16 acceptance filters can be dynamically associated with any of the receive buffers. Actual association is made by setting appropriate bits in the RXFBCONn register. Each RXFBCONn register contains a nibble for each filter. This nibble can be used to associate a specific filter to any of available receive buffers. User firmware may associate more than one filter to any one specific receive buffer.

In addition to dynamic filter to buffer association, in Mode 1 and 2, each filter can also be dynamically associated to available acceptance mask registers. The FILn\_m bits in the MSELn register can be used to link a specific acceptance filter to an acceptance mask register. As with filter to buffer association, one can also associate more than one mask to a specific acceptance filter.

When a filter matches and a message is loaded into the receive buffer, the filter number that enabled the message reception is loaded into the FILHIT bit(s). In Mode 0 for RXB1, the RXB1CON register contains the FILHIT<2:0> bits. They are coded as follows:

- 101 = Acceptance Filter 5 (RXF5)

- 100 = Acceptance Filter 4 (RXF4)

- 011 = Acceptance Filter 3 (RXF3)

- 010 = Acceptance Filter 2 (RXF2)

- 001 = Acceptance Filter 1 (RXF1)

- 000 = Acceptance Filter 0 (RXF0)

Note: '000' and '001' can only occur if the RXB0DBEN bit is set in the RXB0CON register, allowing RXB0 messages to rollover into RXB1. The coding of the RXB0DBEN bit enables these three bits to be used similarly to the FILHIT bits and to distinguish a hit on filter RXF0 and RXF1, in either RXB0 or after a rollover into RXB1.

- 111 = Acceptance Filter 1 (RXF1)

- 110 = Acceptance Filter 0 (RXF0)

- 001 = Acceptance Filter 1 (RXF1)

- 000 = Acceptance Filter 0 (RXF0)

If the RXB0DBEN bit is clear, there are six codes corresponding to the six filters. If the RXB0DBEN bit is set, there are six codes corresponding to the six filters, plus two additional codes corresponding to RXF0 and RXF1 filters, that rollover into RXB1.

In Mode 1 and 2, each buffer control register contains 5 bits of filter hit bits (FILHIT<4:0>). A binary value of '0' indicates a hit from RXF0 and 15 indicates RXF15.

If more than one acceptance filter matches, the FILHIT bits will encode the binary value of the lowest numbered filter that matched. In other words, if filter RXF2 and filter RXF4 match, FILHIT will be loaded with the value for RXF2. This essentially prioritizes the acceptance filters with a lower number filter having higher priority. Messages are compared to filters in ascending order of filter number.

The mask and filter registers can only be modified when the PIC18F2585/2680/4585/4680 devices are in Configuration mode.

#### FIGURE 23-3: MESSAGE ACCEPTANCE MASK AND FILTER OPERATION

| BRA         | ۱.                           | Unconditional Branch                 |                                                                                                         |                             |  |  |  |  |

|-------------|------------------------------|--------------------------------------|---------------------------------------------------------------------------------------------------------|-----------------------------|--|--|--|--|

| Synta       | ax:                          | BRA n                                |                                                                                                         |                             |  |  |  |  |

| Oper        | ands:                        | -1024 ≤ n ≤                          | 1023                                                                                                    |                             |  |  |  |  |

| Oper        | ation:                       | (PC) + 2 + 2                         | $2n \rightarrow PC$                                                                                     |                             |  |  |  |  |

| Statu       | s Affected:                  | None                                 |                                                                                                         |                             |  |  |  |  |

| Enco        | ding:                        | 1101                                 | 0nnn nnr                                                                                                | nn nnnn                     |  |  |  |  |

| Desc        | ription:                     | the PC. Sin incremented instruction, | complement r<br>ce the PC will<br>d to fetch the r<br>the new addre<br>n. This instruct<br>instruction. | have<br>next<br>ess will be |  |  |  |  |

| Word        | ls:                          | 1                                    |                                                                                                         |                             |  |  |  |  |

| Cycle       | es:                          | 2                                    | 2                                                                                                       |                             |  |  |  |  |

| QC          | ycle Activity:               |                                      |                                                                                                         |                             |  |  |  |  |

|             | Q1                           | Q2                                   | Q3                                                                                                      | Q4                          |  |  |  |  |

|             | Decode                       | Read literal<br>'n'                  | Process<br>Data                                                                                         | Write to PC                 |  |  |  |  |

|             | No<br>operation              | No<br>operation                      | No<br>operation                                                                                         | No<br>operation             |  |  |  |  |

| <u>Exan</u> | Before Instruc               |                                      | BRA Jump                                                                                                |                             |  |  |  |  |

|             | PC<br>After Instructio<br>PC | on                                   | dress (HERE)<br>dress (Jump)                                                                            |                             |  |  |  |  |

| BSF                                                                 | Bit Set f                                                                                           |                                                                  |                                                             |                                      |                                                    |  |  |  |

|---------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|------------------------------------------------------------------|-------------------------------------------------------------|--------------------------------------|----------------------------------------------------|--|--|--|

| Syntax:                                                             | BSF f, b                                                                                            | {,a}                                                             |                                                             |                                      |                                                    |  |  |  |

| Operands:                                                           | 0 ≤ f ≤ 255<br>0 ≤ b ≤ 7<br>a ∈ [0,1]                                                               |                                                                  |                                                             |                                      |                                                    |  |  |  |

| Operation:                                                          | $1 \rightarrow \text{f}$                                                                            |                                                                  |                                                             |                                      |                                                    |  |  |  |

| Status Affected:                                                    | None                                                                                                |                                                                  |                                                             |                                      |                                                    |  |  |  |

| Encoding:                                                           | 1000                                                                                                | bbba                                                             | fff                                                         | f                                    | ffff                                               |  |  |  |

| Description:                                                        | Bit 'b' in re                                                                                       | gister 'f' i                                                     | s set.                                                      |                                      |                                                    |  |  |  |

|                                                                     | If 'a' is '0',<br>If 'a' is '1',<br>GPR bank                                                        | the BSR i                                                        | s used                                                      |                                      |                                                    |  |  |  |

|                                                                     | If 'a' is '0' a<br>set is enab<br>in Indexed<br>mode whe<br>Section 2!<br>Bit-Orient<br>Literal Off | bled, this i<br>Literal O<br>never f ≤<br>5.2.3 "By<br>ed Instru | nstructi<br>ffset Ac<br>95 (5Ff<br><b>te-Orie</b><br>ctions | ion<br>ddre<br>h). S<br>ente<br>in I | operates<br>ssing<br>See<br><b>d and</b><br>ndexed |  |  |  |

| Words:                                                              | 1                                                                                                   |                                                                  |                                                             |                                      |                                                    |  |  |  |

| Cycles:                                                             | 1                                                                                                   |                                                                  |                                                             |                                      |                                                    |  |  |  |

| Q Cycle Activity:                                                   |                                                                                                     |                                                                  |                                                             |                                      |                                                    |  |  |  |

| Q1                                                                  | Q2                                                                                                  | Q3                                                               | ;                                                           |                                      | Q4                                                 |  |  |  |

| Decode                                                              | ReadProcessWriteregister 'f'Dataregister 'f'                                                        |                                                                  |                                                             |                                      |                                                    |  |  |  |

| Example: BSF FLAG_REG, 7, 1<br>Before Instruction<br>FLAG_REG = 0Ah |                                                                                                     |                                                                  |                                                             |                                      |                                                    |  |  |  |