Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

|                            |                                                                             |

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 40MHz                                                                       |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                 |

| Number of I/O              | 36                                                                          |

| Program Memory Size        | 48KB (24K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 1K x 8                                                                      |

| RAM Size                   | 3.25K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                   |

| Data Converters            | A/D 11x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 44-TQFP                                                                     |

| Supplier Device Package    | 44-TQFP (10x10)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf4585t-i-pt |

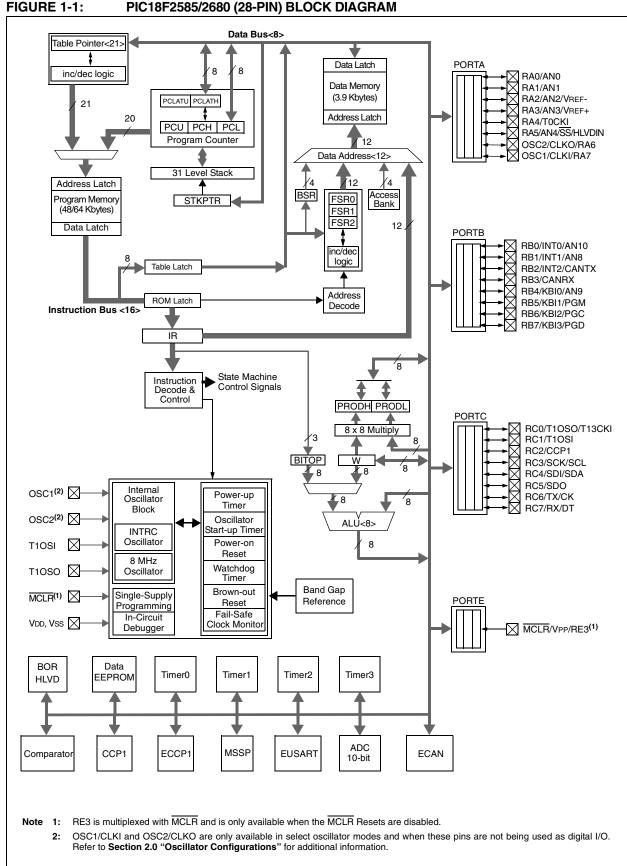

PIC18F2585/2680 (28-PIN) BLOCK DIAGRAM

# 3.1.3 CLOCK TRANSITIONS AND STATUS INDICATORS

The length of the transition between clock sources is the sum of two cycles of the old clock source and three to four cycles of the new clock source. This formula assumes that the new clock source is stable.

Three bits indicate the current clock source and its status. They are:

- OSTS (OSCCON<3>)

- IOFS (OSCCON<2>)

- T1RUN (T1CON<6>)

In general, only one of these bits will be set while in a given power managed mode. When the OSTS bit is set, the primary clock is providing the device clock. When the IOFS bit is set, the INTOSC output is providing a stable 8 MHz clock source to a divider that actually drives the device clock. When the T1RUN bit is set, the Timer1 oscillator is providing the clock. If none of these bits are set, then either the INTRC clock source is clocking the device, or the INTOSC source is not yet stable.

If the internal oscillator block is configured as the primary clock source by the FOSC3:FOSC0 Configuration bits, then both the OSTS and IOFS bits may be set when in PRI\_RUN or PRI\_IDLE modes. This indicates that the primary clock (INTOSC output) is generating a stable 8 MHz output. Entering another RC power managed mode at the same frequency would clear the OSTS bit.

- Note 1: Caution should be used when modifying a single IRCF bit. If VDD is less than 3V, it is possible to select a higher clock speed than is supported by the low VDD. Improper device operation may result if the VDD/Fosc specifications are violated.

- 2: Executing a SLEEP instruction does not necessarily place the device into Sleep mode. It acts as the trigger to place the controller into either the Sleep mode or one of the Idle modes, depending on the setting of the IDLEN bit.

### 3.1.4 MULTIPLE SLEEP COMMANDS

The power managed mode that is invoked with the SLEEP instruction is determined by the setting of the IDLEN bit at the time the instruction is executed. If another SLEEP instruction is executed, the device will enter the power managed mode specified by IDLEN at that time. If IDLEN has changed, the device will enter the new power managed mode specified by the new setting.

#### 3.2 Run Modes

In the Run modes, clocks to both the core and peripherals are active. The difference between these modes is the clock source.

### 3.2.1 PRI RUN MODE

The PRI\_RUN mode is the normal, full power execution mode of the microcontroller. This is also the default mode upon a device Reset, unless Two-Speed Start-up is enabled (see **Section 24.3** "Two-Speed Start-up" for details). In this mode, the OSTS bit is set. The IOFS bit may be set if the internal oscillator block is the primary clock source (see **Section 2.7.1** "Oscillator Control Register").

### 3.2.2 SEC RUN MODE

result.

The SEC\_RUN mode is the compatible mode to the "clock switching" feature offered in other PIC18 devices. In this mode, the CPU and peripherals are clocked from the Timer1 oscillator. This gives users the option of lower power consumption while still using a high accuracy clock source.

SEC\_RUN mode is entered by setting the SCS1:SCS0 bits to '01'. The device clock source is switched to the Timer1 oscillator (see Figure 3-1), the primary oscillator is shut down, the T1RUN bit (T1CON<6>) is set and the OSTS bit is cleared.

Note: The Timer1 oscillator should already be running prior to entering SEC\_RUN mode. If the T1OSCEN bit is not set when the SCS1:SCS0 bits are set to '01', entry to SEC\_RUN mode will not occur. If the Timer1 oscillator is enabled but not yet running, device clocks will be delayed until the oscillator has started. In such situations, initial oscillator operation is far from stable and unpredictable operation may

On transitions from SEC\_RUN mode to PRI\_RUN, the peripherals and CPU continue to be clocked from the Timer1 oscillator while the primary clock is started. When the primary clock becomes ready, a clock switch back to the primary clock occurs (see Figure 3-2). When the clock switch is complete, the T1RUN bit is cleared, the OSTS bit is set and the primary clock is providing the clock. The IDLEN and SCS bits are not affected by the wake-up; the Timer1 oscillator continues to run.

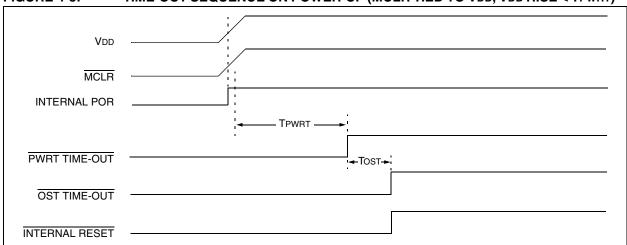

FIGURE 4-3: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD, VDD RISE < TPWRT)

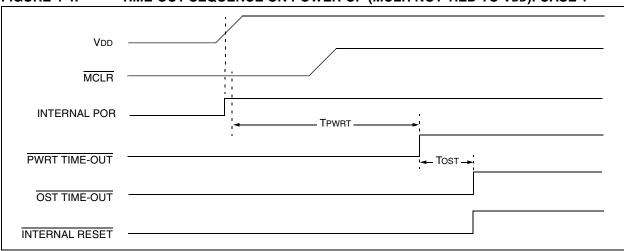

FIGURE 4-4: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 1

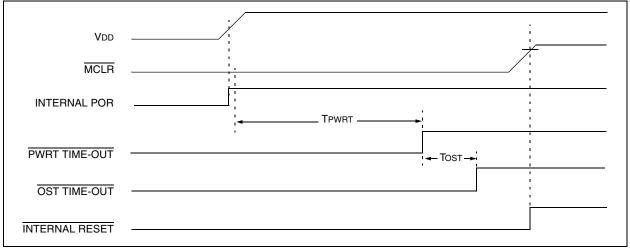

FIGURE 4-5: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 2

TABLE 4-4: INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED)

| Register              | Applicable Devices |      | Power-on Reset,<br>Brown-out Reset | MCLR Resets,<br>WDT Reset,<br>RESET Instruction,<br>Stack Resets | Wake-up via WDT<br>or Interrupt |           |           |

|-----------------------|--------------------|------|------------------------------------|------------------------------------------------------------------|---------------------------------|-----------|-----------|

| B2CON <sup>(6)</sup>  | 2585               | 2680 | 4585                               | 4680                                                             | 0000 0000                       | 0000 0000 | uuuu uuuu |

| B1D7 <sup>(6)</sup>   | 2585               | 2680 | 4585                               | 4680                                                             | xxxx xxxx                       | uuuu uuuu | uuuu uuuu |

| B1D6 <sup>(6)</sup>   | 2585               | 2680 | 4585                               | 4680                                                             | xxxx xxxx                       | uuuu uuuu | uuuu uuuu |

| B1D5 <sup>(6)</sup>   | 2585               | 2680 | 4585                               | 4680                                                             | xxxx xxxx                       | uuuu uuuu | uuuu uuuu |

| B1D4 <sup>(6)</sup>   | 2585               | 2680 | 4585                               | 4680                                                             | xxxx xxxx                       | uuuu uuuu | uuuu uuuu |

| B1D3 <sup>(6)</sup>   | 2585               | 2680 | 4585                               | 4680                                                             | xxxx xxxx                       | uuuu uuuu | uuuu uuuu |

| B1D2 <sup>(6)</sup>   | 2585               | 2680 | 4585                               | 4680                                                             | xxxx xxxx                       | uuuu uuuu | uuuu uuuu |

| B1D1 <sup>(6)</sup>   | 2585               | 2680 | 4585                               | 4680                                                             | xxxx xxxx                       | uuuu uuuu | uuuu uuuu |

| B1D0 <sup>(6)</sup>   | 2585               | 2680 | 4585                               | 4680                                                             | xxxx xxxx                       | uuuu uuuu | uuuu uuuu |

| B1DLC <sup>(6)</sup>  | 2585               | 2680 | 4585                               | 4680                                                             | -xxx xxxx                       | -uuu uuuu | -uuu uuuu |

| B1EIDL <sup>(6)</sup> | 2585               | 2680 | 4585                               | 4680                                                             | xxxx xxxx                       | uuuu uuuu | uuuu uuuu |

| B1EIDH <sup>(6)</sup> | 2585               | 2680 | 4585                               | 4680                                                             | xxxx xxxx                       | uuuu uuuu | uuuu uuuu |

| B1SIDL <sup>(6)</sup> | 2585               | 2680 | 4585                               | 4680                                                             | xxxx x-xx                       | uuuu u-uu | uuuu u-uu |

| B1SIDH <sup>(6)</sup> | 2585               | 2680 | 4585                               | 4680                                                             | xxxx xxxx                       | uuuu uuuu | uuuu uuuu |

| B1CON <sup>(6)</sup>  | 2585               | 2680 | 4585                               | 4680                                                             | 0000 0000                       | 0000 0000 | uuuu uuuu |

| B0D7 <sup>(6)</sup>   | 2585               | 2680 | 4585                               | 4680                                                             | xxxx xxxx                       | uuuu uuuu | uuuu uuuu |

| B0D6 <sup>(6)</sup>   | 2585               | 2680 | 4585                               | 4680                                                             | xxxx xxxx                       | uuuu uuuu | uuuu uuuu |

| B0D5 <sup>(6)</sup>   | 2585               | 2680 | 4585                               | 4680                                                             | xxxx xxxx                       | uuuu uuuu | uuuu uuuu |

| B0D4 <sup>(6)</sup>   | 2585               | 2680 | 4585                               | 4680                                                             | xxxx xxxx                       | uuuu uuuu | uuuu uuuu |

| B0D3 <sup>(6)</sup>   | 2585               | 2680 | 4585                               | 4680                                                             | xxxx xxxx                       | uuuu uuuu | uuuu uuuu |

| B0D2 <sup>(6)</sup>   | 2585               | 2680 | 4585                               | 4680                                                             | xxxx xxxx                       | uuuu uuuu | uuuu uuuu |

| B0D1 <sup>(6)</sup>   | 2585               | 2680 | 4585                               | 4680                                                             | xxxx xxxx                       | uuuu uuuu | uuuu uuuu |

| B0D0 <sup>(6)</sup>   | 2585               | 2680 | 4585                               | 4680                                                             | xxxx xxxx                       | uuuu uuuu | uuuu uuuu |

| B0DLC <sup>(6)</sup>  | 2585               | 2680 | 4585                               | 4680                                                             | -xxx xxxx                       | -uuu uuuu | -uuu uuuu |

| B0EIDL <sup>(6)</sup> | 2585               | 2680 | 4585                               | 4680                                                             | xxxx xxxx                       | uuuu uuuu | uuuu uuuu |

| B0EIDH <sup>(6)</sup> | 2585               | 2680 | 4585                               | 4680                                                             | xxxx xxxx                       | uuuu uuuu | uuuu uuuu |

| B0SIDL <sup>(6)</sup> | 2585               | 2680 | 4585                               | 4680                                                             | xxxx x-xx                       | uuuu u-uu | uuuu u-uu |

| B0SIDH <sup>(6)</sup> | 2585               | 2680 | 4585                               | 4680                                                             | xxxx xxxx                       | uuuu uuuu | uuuu uuuu |

| B0CON <sup>(6)</sup>  | 2585               | 2680 | 4585                               | 4680                                                             | 0000 0000                       | 0000 0000 | uuuu uuuu |

| TXBIE <sup>(6)</sup>  | 2585               | 2680 | 4585                               | 4680                                                             | 0 00                            | u uu      | u uu      |

| BIE0 <sup>(6)</sup>   | 2585               | 2680 | 4585                               | 4680                                                             | 0000 0000                       | 0000 0000 | uuuu uuuu |

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0', <math>q = value depends on condition. Shaded cells indicate conditions do not apply for the designated device.

- Note 1: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

- 2: When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

- **3:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

- **4:** See Table 4-3 for Reset value for specific condition.

- 5: Bits 6 and 7 of PORTA, LATA and TRISA are enabled, depending on the oscillator mode selected. When not enabled as PORTA pins, they are disabled and read '0'.

- 6: This register reads all '0's until the ECAN™ technology is set up in Mode 1 or Mode 2.

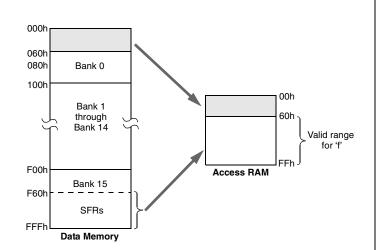

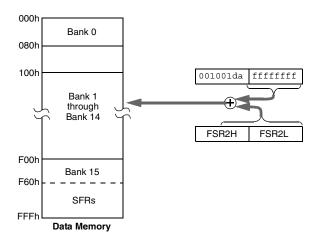

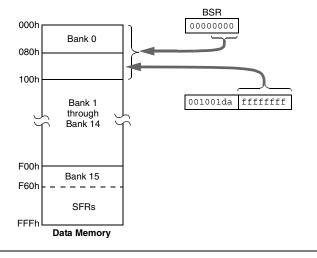

# FIGURE 5-8: COMPARING ADDRESSING OPTIONS FOR BIT-ORIENTED AND BYTE-ORIENTED INSTRUCTIONS (EXTENDED INSTRUCTION SET ENABLED)

**EXAMPLE INSTRUCTION:** ADDWF, f, d, a (Opcode: 0010 01da ffff fffff)

#### When a = 0 and $f \ge 60h$ :

The instruction executes in Direct Forced mode. 'f' is interpreted as a location in the Access RAM between 060h and 0FFh. This is the same as the SFRs, or locations F60h to 0FFh (Bank 15) of data memory.

Locations below 60h are not available in this addressing mode.

#### When a = 0 and $f \le 5Fh$ :

The instruction executes in Indexed Literal Offset mode. 'f' is interpreted as an offset to the address value in FSR2. The two are added together to obtain the address of the target register for the instruction. The address can be anywhere in the data memory space.

Note that in this mode, the correct syntax is now:  $\label{eq:add_power} \texttt{ADDWF} \ \ [\texttt{k}] \ , \ \ \texttt{d}$

where 'k' is the same as 'f'.

#### When a = 1 (all values of f):

The instruction executes in Direct mode (also known as Direct Long mode). 'f' is interpreted as a location in one of the 16 banks of the data memory space. The bank is designated by the Bank Select Register (BSR). The address can be in any implemented bank in the data memory space.

NOTES:

NOTES:

Note:

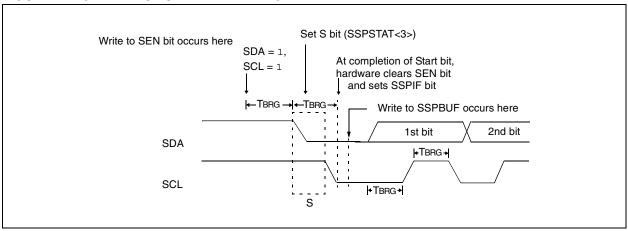

# 17.4.8 I<sup>2</sup>C MASTER MODE START CONDITION TIMING

To initiate a Start condition, the user sets the Start Enable bit, SEN (SSPCON2<0>). If the SDA and SCL pins are sampled high, the Baud Rate Generator is reloaded with the contents of SSPADD<6:0> and starts its count. If SCL and SDA are both sampled high when the Baud Rate Generator times out (TBRG), the SDA pin is driven low. The action of the SDA being driven low while SCL is high is the Start condition and causes the S bit (SSPSTAT<3>) to be set. Following this, the Baud Rate Generator is reloaded with the contents of SSPADD<6:0> and resumes its count. When the Baud Rate Generator times out (TBRG), the SEN bit (SSPCON2<0>) will be automatically cleared by hardware, the Baud Rate Generator is suspended, leaving the SDA line held low and the Start condition is complete.

If at the beginning of the Start condition, the SDA and SCL pins are already sampled low, or if during the Start condition, the SCL line is sampled low before the SDA line is driven low, a bus collision occurs, the Bus Collision Interrupt Flag, BCLIF, is set, the Start condition is aborted and the I<sup>2</sup>C module is reset into its Idle state.

### 17.4.8.1 WCOL Status Flag

If the user writes the SSPBUF when a Start sequence is in progress, the WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

bte: Because queueing of events is not allowed, writing to the lower 5 bits of SSPCON2 is disabled until the Start condition is complete.

#### REGISTER 18-1: TXSTA: TRANSMIT STATUS AND CONTROL REGISTER

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R-1  | R/W-0 |

|-------|-------|-------|-------|-------|-------|------|-------|

| CSRC  | TX9   | TXEN  | SYNC  | SENDB | BRGH  | TRMT | TX9D  |

| bit 7 |       |       | •     |       |       | •    | bit 0 |

bit 0

bit 7 **CSRC:** Clock Source Select bit

Asynchronous mode:

Don't care.

Synchronous mode:

1 = Master mode (clock generated internally from BRG)

0 = Slave mode (clock from external source)

bit 6 TX9: 9-bit Transmit Enable bit

1 = Selects 9-bit transmission

0 = Selects 8-bit transmission

bit 5 TXEN: Transmit Enable bit

1 = Transmit enabled

0 = Transmit disabled

SREN/CREN overrides TXEN in Sync mode.

bit 4 SYNC: EUSART Mode Select bit

1 = Synchronous mode

0 = Asynchronous mode

bit 3 SENDB: Send Break Character bit

Asynchronous mode:

1 = Send Sync Break on next transmission (cleared by hardware upon completion)

0 = Sync Break transmission completed

Synchronous mode:

Don't care.

bit 2 **BRGH:** High Baud Rate Select bit

Asynchronous mode:

1 = High speed

0 = Low speed

Synchronous mode:

Unused in this mode.

bit 1 TRMT: Transmit Shift Register Status bit

1 = TSR empty

0 = TSR full

bit 0 TX9D: 9th bit of Transmit Data

Can be address/data bit or a parity bit.

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

'1' = Bit is set -n = Value at POR '0' = Bit is cleared x = Bit is unknown

## 19.2 Selecting and Configuring Automatic Acquisition Time

The ADCON2 register allows the user to select an acquisition time that occurs each time the GO/DONE bit is set.

When the GO/DONE bit is set, sampling is stopped and a conversion begins. The user is responsible for ensuring the required acquisition time has passed between selecting the desired input channel and setting the GO/DONE bit. This occurs when the ACQT2:ACQT0 bits (ADCON2<5:3>) remain in their Reset state ('000') and is compatible with devices that do not offer programmable acquisition times.

If desired, the ACQT bits can be set to select a programmable acquisition time for the A/D module. When the GO/DONE bit is set, the A/D module continues to sample the input for the selected acquisition time, then automatically begins a conversion. Since the acquisition time is programmed, there may be no need to wait for an acquisition time between selecting a channel and setting the GO/DONE bit.

In either case, when the conversion is completed, the GO/DONE bit is cleared, the ADIF flag is set and the A/D begins sampling the currently selected channel again. If an acquisition time is programmed, there is nothing to indicate if the acquisition time has ended or if the conversion has begun.

# 19.3 Selecting the A/D Conversion Clock

The A/D conversion time per bit is defined as TAD. The A/D conversion requires 11 TAD per 10-bit conversion. The source of the A/D conversion clock is software selectable. There are seven possible options for TAD:

- 2 Tosc

- 4 Tosc

- 8 Tosc

- 16 Tosc

- 32 Tosc

- 64 Tosc

- · Internal RC Oscillator

For correct A/D conversions, the A/D conversion clock (TAD) must be as short as possible, but greater than the minimum TAD (approximately 2  $\mu$ s, see parameter 130 for more information).

Table 19-1 shows the resultant TAD times derived from the device operating frequencies and the A/D clock source selected.

TABLE 19-1: TAD vs. DEVICE OPERATING FREQUENCIES

| AD Clock S        | ource (TAD) | Maximum Device Frequency |                                 |  |  |  |

|-------------------|-------------|--------------------------|---------------------------------|--|--|--|

| Operation         | ADCS2:ADCS0 | PIC18FX585/X680          | PIC18LFX585/X680 <sup>(4)</sup> |  |  |  |

| 2 Tosc            | 000         | 2.86 MHz                 | 1.43 kHz                        |  |  |  |

| 4 Tosc            | 100         | 5.71 MHz                 | 2.86 MHz                        |  |  |  |

| 8 Tosc            | 001         | 11.43 MHz                | 5.72 MHz                        |  |  |  |

| 16 Tosc           | 101         | 22.86 MHz                | 11.43 MHz                       |  |  |  |

| 32 Tosc           | 010         | 40.0 MHz                 | 22.86 MHz                       |  |  |  |

| 64 Tosc           | 110         | 40.0 MHz                 | 22.86 MHz                       |  |  |  |

| RC <sup>(3)</sup> | x11         | 1.00 MHz <sup>(1)</sup>  | 1.00 MHz <sup>(2)</sup>         |  |  |  |

- Note 1: The RC source has a typical TAD time of 4 ms.

- 2: The RC source has a typical TAD time of 6 ms.

- 3: For device frequencies above 1 MHz, the device must be in Sleep for the entire conversion or the A/D accuracy may be out of specification.

- 4: Low-power (PIC18LFXXXX) devices only.

# REGISTER 23-34: BnDLC: TX/RX BUFFER n DATA LENGTH CODE REGISTERS IN RECEIVE MODE $[0 \le n \le 5, \text{ TXnEN (BSEL} < n >) = 0]^{(1)}$

| U-0   | R-x   | R-x | R-x | R-x  | R-x  | R-x  | R-x   |

|-------|-------|-----|-----|------|------|------|-------|

| _     | RXRTR | RB1 | RB0 | DLC3 | DLC2 | DLC1 | DLC0  |

| bit 7 |       |     |     |      |      |      | bit 0 |

bit 7 Unimplemented: Read as '0'

bit 6 RXRTR: Receiver Remote Transmission Request bit

1 = This is a remote transmission request0 = This is not a remote transmission request

bit 5 **RB1:** Reserved bit 1

Reserved by CAN Spec and read as '0'.

bit 4 RB0: Reserved bit 0

Reserved by CAN Spec and read as '0'.

bit 3-0 DLC3:DLC0: Data Length Code bits

1111 = Reserved

1110 = Reserved

1101 = Reserved

1100 = Reserved

1011 = Reserved 1010 = Reserved

1001 = Reserved

1000 = Data length = 8 bytes

0111 = Data length = 7 bytes

0110 = Data length = 6 bytes

0101 = Data length = 5 bytes

0100 = Data length = 4 bytes 0011 = Data length = 3 bytes

0010 = Data length = 2 bytes

0001 = Data length = 1 bytes

0000 = Data length = 0 bytes

Note 1: These registers are available in Mode 1 and 2 only.

### Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

### REGISTER 23-58: IPR3: PERIPHERAL INTERRUPT PRIORITY REGISTER 5

| Mode 0 | R/W-1 | R/W-1 | R/W-1 | R/W-1  | R/W-1                 | R/W-1                 | R/W-1  | R/W-1  |

|--------|-------|-------|-------|--------|-----------------------|-----------------------|--------|--------|

| woue o | IRXIP | WAKIP | ERRIP | TXB2IP | TXB1IP <sup>(1)</sup> | TXB0IP <sup>(1)</sup> | RXB1IP | RXB0IP |

| Mode 1 2  | R/W-1  | R/W-1 | R/W-1 | R/W-1  | R/W-1                 | R/W-1                 | R/W-1  | R/W-1    |

|-----------|--------|-------|-------|--------|-----------------------|-----------------------|--------|----------|

| Mode 1, 2 | IRXIP  | WAKIP | ERRIP | TXBnIP | TXB1IP <sup>(1)</sup> | TXB0IP <sup>(1)</sup> | RXBnIP | FIFOWMIP |

|           | 1 11 7 |       |       |        |                       |                       |        | 1 11 0   |

bit 7 bit 0

bit 7 IRXIP: CAN Invalid Received Message Interrupt Priority bit

1 = High priority0 = Low priority

bit 6 WAKIP: CAN bus Activity Wake-up Interrupt Priority bit

1 = High priority0 = Low priority

bit 5 ERRIP: CAN bus Error Interrupt Priority bit

1 = High priority0 = Low priority

bit 4 When CAN is in Mode 0:

TXB2IP: CAN Transmit Buffer 2 Interrupt Priority bit

1 = High priority0 = Low priority

When CAN is in Mode 1 or 2:

TXBnIP: CAN Transmit Buffer Interrupt Priority bit

1 = High priority0 = Low priority

bit 3 **TXB1IP:** CAN Transmit Buffer 1 Interrupt Priority bit<sup>(1)</sup>

1 = High priority0 = Low priority

bit 2 **TXB0IP:** CAN Transmit Buffer 0 Interrupt Priority bit<sup>(1)</sup>

1 = High priority0 = Low priority

bit 1 When CAN is in Mode 0:

RXB1IP: CAN Receive Buffer 1 Interrupt Priority bit

1 = High priority0 = Low priority

When CAN is in Mode 1 or 2:

**RXBnIP:** CAN Receive Buffer Interrupts Priority bit

1 = High priority0 = Low priority

bit 0 When CAN is in Mode 0:

RXB0IP: CAN Receive Buffer 0 Interrupt Priority bit

1 = High priority0 = Low priority

When CAN is in Mode 1: Unimplemented: Read as '0' When CAN is in Mode 2:

FIFOWMIP: FIFO Watermark Interrupt Priority bit

1 = High priority0 = Low priority

Note 1: In CAN Mode 1 and 2, this bit is forced to '0'.

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

TABLE 23-1: CAN CONTROLLER REGISTER MAP (CONTINUED)

| Address <sup>(1)</sup> | Name      |  |  |  |  |

|------------------------|-----------|--|--|--|--|

| D7Fh                   | (4)       |  |  |  |  |

| D7Eh                   | (4)       |  |  |  |  |

| D7Dh                   | (4)       |  |  |  |  |

| D7Ch                   | (4)       |  |  |  |  |

| D7Bh                   | RXF11EIDL |  |  |  |  |

| D7Ah                   | RXF11EIDH |  |  |  |  |

| D79h                   | RXF11SIDL |  |  |  |  |

| D78h                   | RXF11SIDH |  |  |  |  |

| D77h                   | RXF10EIDL |  |  |  |  |

| D76h                   | RXF10EIDH |  |  |  |  |

| D75h                   | RXF10SIDL |  |  |  |  |

| D74h                   | RXF10SIDH |  |  |  |  |

| D73h                   | RXF9EIDL  |  |  |  |  |

| D72h                   | RXF9EIDH  |  |  |  |  |

| D71h                   | RXF9SIDL  |  |  |  |  |

| D70h                   | RXF9SIDH  |  |  |  |  |

| D6Fh                   | (4)       |  |  |  |  |

| D6Eh                   | (4)       |  |  |  |  |

| D6Dh                   | (4)       |  |  |  |  |

| D6Ch                   | (4)       |  |  |  |  |

| D6Bh                   | RXF8EIDL  |  |  |  |  |

| D6Ah                   | RXF8EIDH  |  |  |  |  |

| D69h                   | RXF8SIDL  |  |  |  |  |

| D68h                   | RXF8SIDH  |  |  |  |  |

| D67h                   | RXF7EIDL  |  |  |  |  |

| D66h                   | RXF7EIDH  |  |  |  |  |

| D65h                   | RXF7SIDL  |  |  |  |  |

| D64h                   | RXF7SIDH  |  |  |  |  |

| D63h                   | RXF6EIDL  |  |  |  |  |

| D62h                   | RXF6EIDH  |  |  |  |  |

| D61h                   | RXF6SIDL  |  |  |  |  |

| D60h                   | RXF6SIDH  |  |  |  |  |

- Note 1: Shaded registers are available in Access Bank low area while the rest are available in Bank 15.

- **2:** CANSTAT register is repeated in these locations to simplify application firmware. Unique names are given for each instance of the controller register due to the Microchip header file requirement.

- 3: These registers are not CAN registers.

- 4: Unimplemented registers are read as '0'.

# 24.0 SPECIAL FEATURES OF THE CPU

PIC18F2585/2680/4585/4680 devices include several features intended to maximize reliability and minimize cost through elimination of external components. These are:

- · Oscillator Selection

- Resets:

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Brown-out Reset (BOR)

- Interrupts

- Watchdog Timer (WDT)

- · Fail-Safe Clock Monitor

- · Two-Speed Start-up

- Code Protection

- ID Locations

- · In-Circuit Serial Programming

The oscillator can be configured for the application depending on frequency, power, accuracy and cost. All of the options are discussed in detail in **Section 2.0** "Oscillator Configurations".

A complete discussion of device Resets and interrupts is available in previous sections of this data sheet.

In addition to their Power-up and Oscillator Start-up Timers provided for Resets, PIC18F2585/2680/4585/4680 devices have a Watchdog Timer, which is either permanently enabled via the Configuration bits or software controlled (if configured as disabled).

The inclusion of an internal RC oscillator also provides the additional benefits of a Fail-Safe Clock Monitor (FSCM) and Two-Speed Start-up. FSCM provides for background monitoring of the peripheral clock and automatic switchover in the event of its failure. Two-Speed Start-up enables code to be executed almost immediately on start-up, while the primary clock source completes its start-up delays.

All of these features are enabled and configured by setting the appropriate Configuration register bits.

### 24.1 Configuration Bits

The Configuration bits can be programmed (read as '0') or left unprogrammed (read as '1') to select various device configurations. These bits are mapped starting at program memory location 300000h.

The user will note that address 300000h is beyond the user program memory space. In fact, it belongs to the configuration memory space (300000h-3FFFFFh), which can only be accessed using table reads and table writes.

Programming the Configuration registers is done in a manner similar to programming the Flash memory. The WR bit in the EECON1 register starts a self-timed write to the Configuration register. In normal operation mode, a TBLWT instruction with the TBLPTR pointing to the Configuration register sets up the address and the data for the Configuration register write. Setting the WR bit starts a long write to the Configuration register. The Configuration registers are written a byte at a time. To write or erase a configuration cell, a TBLWT instruction can write a '1' or a '0' into the cell. For additional details on Flash programming, refer to Section 6.5 "Writing to Flash Program Memory".

TABLE 24-1: CONFIGURATION BITS AND DEVICE IDs

| File    | Name     | Bit 7 | Bit 6 | Bit 5  | Bit 4  | Bit 3  | Bit 2   | Bit 1  | Bit 0  | Default/<br>Unprogrammed<br>Value |

|---------|----------|-------|-------|--------|--------|--------|---------|--------|--------|-----------------------------------|

| 300001h | CONFIG1H | IESO  | FCMEN | _      | _      | FOSC3  | FOSC2   | FOSC1  | FOSC0  | 00 0111                           |

| 300002h | CONFIG2L | _     | _     | _      | BORV1  | BORV0  | BOREN1  | BOREN0 | PWRTEN | 1 1111                            |

| 300003h | CONFIG2H | _     | _     | _      | WDTPS3 | WDTPS2 | WDTPS1  | WDTPS0 | WDTEN  | 1 1111                            |

| 300005h | CONFIG3H | MCLRE | -     | _      |        | -      | LPT1OSC | PBADEN |        | 101-                              |

| 300006h | CONFIG4L | DEBUG | XINST | BBSIZ1 | BBSIZ2 | -      | LVP     | 1      | STVREN | 1000 -1-1                         |

| 300008h | CONFIG5L | _     | _     | _      | _      | CP3    | CP2     | CP1    | CP0    | 1111                              |

| 300009h | CONFIG5H | CPD   | СРВ   | _      | _      | _      | _       | _      | _      | 11                                |

| 30000Ah | CONFIG6L |       |       | _      |        | WRT3   | WRT2    | WRT1   | WRT0   | 1111                              |

| 30000Bh | CONFIG6H | WRTD  | WRTB  | WRTC   | _      | _      | _       | _      | _      | 111                               |

| 30000Ch | CONFIG7L | _     | _     | _      | _      | EBTR3  | EBTR2   | EBTR1  | EBTR0  | 1111                              |

| 30000Dh | CONFIG7H | _     | EBTRB | _      | _      | _      | _       |        | _      | -1                                |

| 3FFFFEh | DEVID1   | DEV2  | DEV1  | DEV0   | REV4   | REV3   | REV2    | REV1   | REV0   | xxxx xxxx(1)                      |

| 3FFFFFh | DEVID2   | DEV10 | DEV9  | DEV8   | DEV7   | DEV6   | DEV5    | DEV4   | DEV3   | 0000 1100                         |

$\begin{tabular}{ll} \textbf{Legend:} & $x=$ unknown, $u=$ unchanged, $-=$ unimplemented, $q=$ value depends on condition. \\ & Shaded cells are unimplemented, read as '0'. \\ \end{tabular}$

Note 1: See Register 24-14 for DEVID1 values. DEVID registers are read-only and cannot be programmed by the user.

### 25.1.1 STANDARD INSTRUCTION SET

| ADD   | LW             | ADD Lite                             | ADD Literal to W    |  |            |  |  |  |  |

|-------|----------------|--------------------------------------|---------------------|--|------------|--|--|--|--|

| Synta | ax:            | ADDLW                                | k                   |  |            |  |  |  |  |

| Oper  | ands:          | $0 \le k \le 255$                    | $0 \leq k \leq 255$ |  |            |  |  |  |  |

| Oper  | ation:         | $\text{(W)} + \text{k} \rightarrow$  | W                   |  |            |  |  |  |  |

| Statu | s Affected:    | N, OV, C, [                          | C, Z                |  |            |  |  |  |  |

| Enco  | ding:          | 0000                                 | 0000 1111 kkkk kkkk |  |            |  |  |  |  |

| Desc  | ription:       | The conter<br>8-bit literal<br>in W. |                     |  |            |  |  |  |  |

| Word  | ls:            | 1                                    |                     |  |            |  |  |  |  |

| Cycle | es:            | 1                                    |                     |  |            |  |  |  |  |

| QC    | ycle Activity: |                                      |                     |  |            |  |  |  |  |

|       | Q1             | Q2                                   | Q3                  |  | Q4         |  |  |  |  |

|       | Decode         | Read<br>literal 'k'                  | Proce<br>Data       |  | /rite to W |  |  |  |  |

Example: ADDLW 15h

Before Instruction W = 10hAfter Instruction W = 25h

| ADDWF             | ADD W to                                                                                                                                                                     | o f                                                                                                                       |          |                    |  |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|----------|--------------------|--|

| Syntax:           | ADDWF                                                                                                                                                                        | f {,d {,a}}                                                                                                               | }        |                    |  |

| Operands:         | $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$                                                                                                                          |                                                                                                                           |          |                    |  |

| Operation:        | $(W) + (f) \to$                                                                                                                                                              | dest                                                                                                                      |          |                    |  |

| Status Affected:  | N, OV, C, D                                                                                                                                                                  | )C, Z                                                                                                                     |          |                    |  |

| Encoding:         | 0010                                                                                                                                                                         | 01da                                                                                                                      | ffff     | ffff               |  |

| Description:      | result is sto<br>result is sto<br>(default).<br>If 'a' is '0', t<br>If 'a' is '1', t<br>GPR bank<br>If 'a' is '0' a<br>set is enabl<br>in Indexed<br>mode when<br>Section 25 | Add W to register 'f'. If 'd' is 'o', the result is stored in W. If 'd' is '1', the result is stored back in register 'f' |          |                    |  |

| Words:            | 1                                                                                                                                                                            | oct mode                                                                                                                  | ioi dete |                    |  |

| Cycles:           | 1                                                                                                                                                                            |                                                                                                                           |          |                    |  |

| Q Cycle Activity: | •                                                                                                                                                                            |                                                                                                                           |          |                    |  |

| Q1                | Q2                                                                                                                                                                           | Q3                                                                                                                        |          | Q4                 |  |

| Decode            | Read<br>register 'f'                                                                                                                                                         | Proces<br>Data                                                                                                            |          | Vrite to stination |  |

Example:

ADDWF

REG, 0, 0

0

Before Instruction

W = 17h REG = 0C2h

0.02h

<

**Note:** All PIC18 instructions may take an optional label argument preceding the instruction mnemonic for use in symbolic addressing. If a label is used, the instruction format then becomes: {label} instruction argument(s).

| BCF              | Bit Clear                                                                                                                                                                                                                                                                                                                                                                             | f            |            |      |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|------------|------|--|--|

| Syntax:          | BCF f, b                                                                                                                                                                                                                                                                                                                                                                              | (,a)         |            |      |  |  |

| Operands:        | $0 \le f \le 255$<br>$0 \le b \le 7$<br>$a \in [0,1]$                                                                                                                                                                                                                                                                                                                                 | ;            |            |      |  |  |

| Operation:       | $0 \to f {<} b {>}$                                                                                                                                                                                                                                                                                                                                                                   |              |            |      |  |  |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                                                                                  |              |            |      |  |  |

| Encoding:        | 1001                                                                                                                                                                                                                                                                                                                                                                                  | bbba         | ffff       | ffff |  |  |

| Description:     | Bit 'b' in re                                                                                                                                                                                                                                                                                                                                                                         | gister 'f' i | s cleared. |      |  |  |

|                  | Bit 'b' in register 'f' is cleared.  If 'a' is '0', the Access Bank is selected.  If 'a' is '1', the BSR is used to select the GPR bank (default).  If 'a' is '0' and the extended instruction set is enabled, this instruction operates in Indexed Literal Offset Addressing mode whenever f ≤ 95 (5Fh). See  Section 25.2.3 "Byte-Oriented and Bit-Oriented Instructions in Indexed |              |            |      |  |  |

| Words:           | 1                                                                                                                                                                                                                                                                                                                                                                                     |              |            |      |  |  |

| Cycles:          | 1                                                                                                                                                                                                                                                                                                                                                                                     |              |            |      |  |  |

| Q1     | Q2           | Q3      | Q4           |  |

|--------|--------------|---------|--------------|--|

| Decode | Read         | Process | Write        |  |

|        | register 'f' | Data    | register 'f' |  |

Example: FLAG\_REG, 7, 0 BCF

Before Instruction  $FLAG_REG = C7h$ After Instruction  $FLAG_REG = 47h$

Q Cycle Activity:

| BN                | Branch if Negative                                                                                                                                                                                          |                |             |    |  |  |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-------------|----|--|--|

| Syntax:           | BN n                                                                                                                                                                                                        |                |             |    |  |  |

| Operands:         | -128 ≤ n ≤                                                                                                                                                                                                  | -128 ≤ n ≤ 127 |             |    |  |  |

| Operation:        | if Negative bit is '1' $(PC) + 2 + 2n \rightarrow PC$                                                                                                                                                       |                |             |    |  |  |

| Status Affected:  | None                                                                                                                                                                                                        |                |             |    |  |  |

| Encoding:         | 1110 0110 nnnn nnnn                                                                                                                                                                                         |                |             |    |  |  |

| Description:      | If the Nega                                                                                                                                                                                                 |                | '1', then t | he |  |  |

|                   | The 2's complement number '2n' is added to the PC. Since the PC will have incremented to fetch the next instruction, the new address will be PC + 2 + 2n. This instruction is then a two-cycle instruction. |                |             |    |  |  |

| Words:            | 1                                                                                                                                                                                                           |                |             |    |  |  |

| Cycles:           | 1(2)                                                                                                                                                                                                        |                |             |    |  |  |

| Q Cycle Activity: |                                                                                                                                                                                                             |                |             |    |  |  |

| Q1        | Q2           | Q3        | Q4          |

|-----------|--------------|-----------|-------------|

| Decode    | Read literal | Process   | Write to PC |

|           | 'n'          | Data      |             |

| No        | No           | No        | No          |

| operation | operation    | operation | operation   |

|           |              |           |             |

If No Jump:

If Jump:

| Q1     | Q2           | Q3      | Q4        |

|--------|--------------|---------|-----------|

| Decode | Read literal | Process | No        |

|        | ʻn'          | Data    | operation |

Example: HERE Jump

Before Instruction

PC address (HERE)

After Instruction

If Negative PC address (Jump)

If Negative PC

address (HERE + 2)

| SUBLW                  | Subtrac                   | t W from               | Lite | ral  |        |  |

|------------------------|---------------------------|------------------------|------|------|--------|--|

| Syntax:                | SUBLW                     | k                      |      |      |        |  |

| Operands:              | $0 \le k \le 25$          | 5                      |      |      |        |  |

| Operation:             | k – (W) –                 | $k-(W)\to W$           |      |      |        |  |

| Status Affected:       | N, OV, C,                 | DC, Z                  |      |      |        |  |

| Encoding:              | 0000                      | 1000                   | kkk  | k    | kkkk   |  |

| Description:           | W is subt<br>literal 'k'. |                        |      | _    |        |  |

| Words:                 | 1                         |                        |      |      |        |  |

| Cycles:                | 1                         |                        |      |      |        |  |

| Q Cycle Activity:      |                           |                        |      |      |        |  |

| Q1                     | Q2                        | Q3                     |      |      | Q4     |  |

| Decode                 | Read                      | Proces                 |      | Writ | e to W |  |

|                        | literal 'k'               | Data                   | l    |      |        |  |

| Example 1:             | SUBLW                     | 02h                    |      |      |        |  |

| Before Instruc         | tion                      |                        |      |      |        |  |

| W<br>C                 | = 01h<br>= ?              |                        |      |      |        |  |

| After Instruction      | •                         |                        |      |      |        |  |

| W                      | = 01h                     |                        |      |      |        |  |

| C<br>7                 | = 1 ; r<br>= 0            | 1 ; result is positive |      |      |        |  |

| Z<br>N                 | = 0                       |                        |      |      |        |  |

| Example 2:             | SUBLW                     | 02h                    |      |      |        |  |

| Before Instruc         | tion                      |                        |      |      |        |  |

| W                      | = 02h                     |                        |      |      |        |  |

| C<br>After Instruction | = ?                       |                        |      |      |        |  |

| W                      | = 00h                     |                        |      |      |        |  |

| Ç                      |                           | esult is ze            | ero  |      |        |  |

| Z<br>N                 | = 1<br>= 0                |                        |      |      |        |  |

| Example 3:             | SUBLW                     | 02h                    |      |      |        |  |

| Before Instruc         | tion                      |                        |      |      |        |  |

|                        |                           |                        |      |      |        |  |

| SUBWF Subtract W from f                      |                                  |                  |                                                                                                                                                                                                                  |                                                                                                                                                |                                                                                            |  |  |

|----------------------------------------------|----------------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|--|--|

| Synta                                        | ax:                              |                  | SUBWF                                                                                                                                                                                                            | f {,d {,a}}                                                                                                                                    |                                                                                            |  |  |

| Oper                                         | ands:                            |                  | $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$                                                                                                                                                              | 5                                                                                                                                              |                                                                                            |  |  |

| Oper                                         | ation:                           |                  | (f) - (W) -                                                                                                                                                                                                      | → dest                                                                                                                                         |                                                                                            |  |  |

| Statu                                        | s Affected:                      |                  | N, OV, C,                                                                                                                                                                                                        | DC, Z                                                                                                                                          |                                                                                            |  |  |

| Enco                                         | ding:                            |                  | 0101                                                                                                                                                                                                             | 11da ffi                                                                                                                                       | ff ffff                                                                                    |  |  |

| Desc                                         | ription:                         |                  | Subtract W from register 'f' (2's complement method). If 'd' is 'o', the result is stored in W. If 'd' is '1', the result is stored back in register 'f' (default).  If 'a' is 'o', the Access Bank is selected. |                                                                                                                                                |                                                                                            |  |  |

|                                              |                                  |                  | GPR bank<br>If 'a' is '0'<br>set is enal<br>in Indexed<br>mode who<br>Section 2<br>Bit-Orien                                                                                                                     | the BSR is use (default).  and the extend oled, this instruct d Literal Offset anever f ≤ 95 (5 15.2.3 "Byte-Or ted Instruction fset Mode" for | ed instruction<br>ction operates<br>Addressing<br>Fh). See<br>riented and<br>ns in Indexed |  |  |

| Word                                         | ls:                              |                  | 1                                                                                                                                                                                                                |                                                                                                                                                |                                                                                            |  |  |

| Cycle                                        | es:                              |                  | 1                                                                                                                                                                                                                |                                                                                                                                                |                                                                                            |  |  |

| Q Cycle Activity:                            |                                  |                  |                                                                                                                                                                                                                  |                                                                                                                                                |                                                                                            |  |  |

| ı                                            | Q1                               |                  | Q2                                                                                                                                                                                                               | Q3                                                                                                                                             | Q4                                                                                         |  |  |

|                                              | Decode                           | re               | Read Process egister 'f' Data                                                                                                                                                                                    |                                                                                                                                                | Write to destination                                                                       |  |  |

| _                                            |                                  | 10               |                                                                                                                                                                                                                  |                                                                                                                                                | destination                                                                                |  |  |

|                                              | <u>nple 1:</u><br>Before Instruc | tion             | SUBWF                                                                                                                                                                                                            | REG, 1, 0                                                                                                                                      |                                                                                            |  |  |

|                                              | REG<br>W                         | =                | 3<br>2                                                                                                                                                                                                           |                                                                                                                                                |                                                                                            |  |  |

|                                              | C<br>After Instruction           | =                | ?                                                                                                                                                                                                                |                                                                                                                                                |                                                                                            |  |  |

|                                              | REG<br>W<br>C<br>Z               | = =              | 1<br>2<br>1 ; re                                                                                                                                                                                                 | esult is positive                                                                                                                              |                                                                                            |  |  |

|                                              | N<br>!- 0:                       | =                |                                                                                                                                                                                                                  | DEG 0 0                                                                                                                                        |                                                                                            |  |  |

|                                              | <u>nple 2:</u><br>Before Instruc | tion             | SUBWF                                                                                                                                                                                                            | REG, 0, 0                                                                                                                                      |                                                                                            |  |  |

|                                              | REG<br>W<br>C                    | =<br>=<br>=<br>= | 2<br>2<br>2<br>?                                                                                                                                                                                                 |                                                                                                                                                |                                                                                            |  |  |

| After Instruction  REG =  W =  C =  Z =  N = |                                  |                  | 1 ; result is zero<br>1                                                                                                                                                                                          |                                                                                                                                                |                                                                                            |  |  |

| Example 3:                                   |                                  |                  | 0<br>SUBWF                                                                                                                                                                                                       | REG, 1, 0                                                                                                                                      |                                                                                            |  |  |

| Before Instruction                           |                                  |                  |                                                                                                                                                                                                                  |                                                                                                                                                |                                                                                            |  |  |

|                                              | REG<br>W<br>C                    | = =              | 1<br>2<br>?                                                                                                                                                                                                      |                                                                                                                                                |                                                                                            |  |  |

|                                              | After Instruction                | n                |                                                                                                                                                                                                                  |                                                                                                                                                |                                                                                            |  |  |

|                                              | REG<br>W                         | =                | FFh ;(<br>2                                                                                                                                                                                                      | 2's complemer                                                                                                                                  | nt)                                                                                        |  |  |

|                                              | C<br>Z<br>N                      | = =              |                                                                                                                                                                                                                  | result is negati                                                                                                                               | ve                                                                                         |  |  |

FFh; (2's complement) 0 ; result is negative 0

W After Instruction

W C Z N

= = =

#### 25.2 Extended Instruction Set

In addition to the standard 75 instructions of the PIC18 instruction set, PIC18F2585/2680/4585/4680 devices also provide an optional extension to the core CPU functionality. The added features include eight additional instructions that augment indirect and indexed addressing operations and the implementation of Indexed Literal Offset Addressing mode for many of the standard PIC18 instructions.

The additional features are disabled by default. To enable them, users must set the XINST Configuration bit.

The instructions in the extended set can all be classified as literal operations, which either manipulate the File Select Registers or use them for indexed addressing. Two of the instructions, ADDFSR and SUBFSR, each have an additional special instantiation for using FSR2. These versions (ADDULNK and SUBULNK) allow for automatic return after execution.

The extended instructions are specifically implemented to optimize re-entrant program code (that is, code that is recursive or that uses a software stack) written in high-level languages, particularly C. Among other things, they allow users working in high-level languages to perform certain operations on data structures more efficiently. These include:

- dynamic allocation and de-allocation of software stack space when entering and leaving subroutines

- function pointer invocation

- software stack pointer manipulation

- manipulation of variables located in a software stack

A summary of the instructions in the extended instruction set is provided in Table 25-3. Detailed descriptions are provided in **Section 25.2.2 "Extended Instruction Set"**. The opcode field descriptions in Table 25-1 apply to both the standard and extended PIC18 instruction sets.

| Note: | The instruction set extension and the Indexed Literal Offset Addressing mode were designed for optimizing applications written in C; the user may likely never use these instructions directly in assembler. The syntax for these commands is provided as a reference for users who may be reviewing code that has been generated by a compiler. |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

#### 25.2.1 EXTENDED INSTRUCTION SYNTAX

Most of the extended instructions use indexed arguments, using one of the File Select Registers and some offset to specify a source or destination register. When an argument for an instruction serves as part of indexed addressing, it is enclosed in square brackets ("[]"). This is done to indicate that the argument is used as an index or offset. MPASM<sup>TM</sup> Assembler will flag an error if it determines that an index or offset value is not bracketed.

When the extended instruction set is enabled, brackets are also used to indicate index arguments in bitoriented and byte-oriented instructions. This is in addition to other changes in their syntax. For more details, see Section 25.2.3.1 "Extended Instruction Syntax with Standard PIC18 Commands".

| Note: | In the past, square brackets have been used to denote optional arguments in the PIC18 and earlier instruction sets. In this |

|-------|-----------------------------------------------------------------------------------------------------------------------------|

|       | text and going forward, optional arguments are denoted by braces ("{ }").                                                   |

TABLE 25-3: EXTENSIONS TO THE PIC18 INSTRUCTION SET

| Mnemonic, |               | Description                              | Cycles | 16-Bit Instruction Word |      |      |      | Status   |

|-----------|---------------|------------------------------------------|--------|-------------------------|------|------|------|----------|

| Operar    | nds           | Description                              | Cycles | MSb                     |      |      | LSb  | Affected |

| ADDFSR    | f, k          | Add literal to FSR                       | 1      | 1110                    | 1000 | ffkk | kkkk | None     |

| ADDULNK   | k             | Add literal to FSR2 and return           | 2      | 1110                    | 1000 | 11kk | kkkk | None     |

| CALLW     |               | Call subroutine using WREG               | 2      | 0000                    | 0000 | 0001 | 0100 | None     |

| MOVSF     | $z_s$ , $f_d$ | Move z <sub>s</sub> (source) to 1st word | 2      | 1110                    | 1011 | 0zzz | ZZZZ | None     |

|           |               | f <sub>d</sub> (destination) 2nd word    |        | 1111                    | ffff | ffff | ffff |          |

| MOVSS     | $z_s, z_d$    | Move z <sub>s</sub> (source) to 1st word | 2      | 1110                    | 1011 | 1zzz | ZZZZ | None     |

|           |               | z <sub>d</sub> (destination) 2nd word    |        | 1111                    | xxxx | XZZZ | ZZZZ |          |

| PUSHL     | k             | Store literal at FSR2,                   | 1      | 1110                    | 1010 | kkkk | kkkk | None     |

|           |               | decrement FSR2                           |        |                         |      |      |      |          |

| SUBFSR    | f, k          | Subtract literal from FSR                | 1      | 1110                    | 1001 | ffkk | kkkk | None     |

| SUBULNK   | k             | Subtract literal from FSR2 and           | 2      | 1110                    | 1001 | 11kk | kkkk | None     |

|           |               | return                                   |        |                         |      |      |      |          |

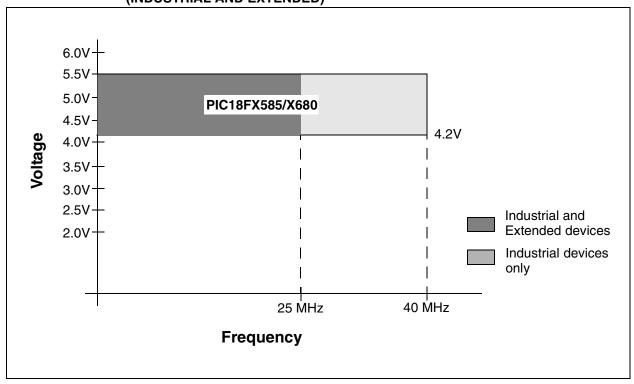

**FIGURE 27-1:** PIC18F2585/2680/4585/4680 VOLTAGE-FREQUENCY GRAPH (INDUSTRIAL AND EXTENDED)

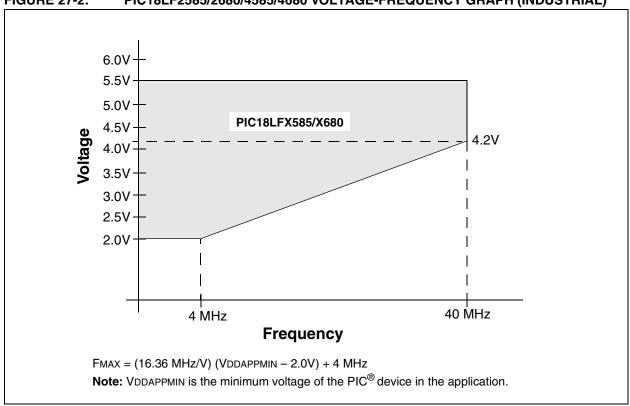

**FIGURE 27-2:** PIC18LF2585/2680/4585/4680 VOLTAGE-FREQUENCY GRAPH (INDUSTRIAL)

### **TABLE 27-2: COMPARATOR SPECIFICATIONS**

**Operating Conditions:** 3.0V < VDD < 5.5V,  $-40^{\circ}C < TA < +85^{\circ}C$  (unless otherwise stated).

| Param<br>No. | Sym    | Characteristics                         | Min | Тур   | Max       | Units | Comments                   |

|--------------|--------|-----------------------------------------|-----|-------|-----------|-------|----------------------------|

| D300         | VIOFF  | Input Offset Voltage                    | _   | ± 5.0 | ± 10      | mV    |                            |

| D301         | VICM   | Input Common Mode Voltage*              | 0   | _     | VDD - 1.5 | V     |                            |

| D302         | CMRR   | Common Mode Rejection Ratio*            | 55  | _     | _         | dB    |                            |

| 300          | TRESP  | Response Time <sup>(1)*</sup>           | _   | 150   | 400       | ns    | PIC18FXXXX                 |

| 300A         |        | ·                                       | _   | 150   | 600       | ns    | PIC18LFXXXX,<br>VDD = 2.0V |

| 301          | Тмс2оv | Comparator Mode Change to Output Valid* | _   | _     | 10        | μs    |                            |