Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                    |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 40MHz                                                                       |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                 |

| Number of I/O              | 36                                                                          |

| Program Memory Size        | 64KB (32K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 1K x 8                                                                      |

| RAM Size                   | 3.25K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                   |

| Data Converters            | A/D 11x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 44-VQFN Exposed Pad                                                         |

| Supplier Device Package    | 44-QFN (8x8)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf4680t-i-ml |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

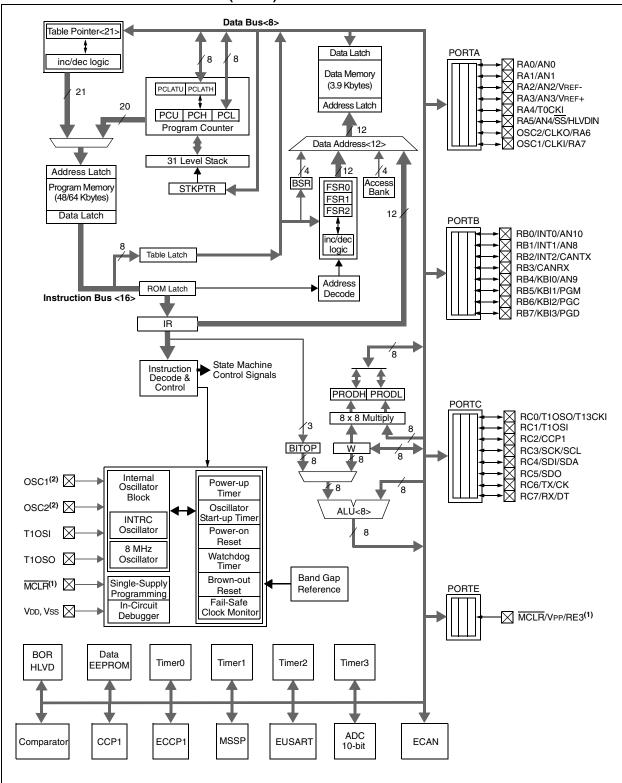

### FIGURE 1-1: PIC18F2585/2680 (28-PIN) BLOCK DIAGRAM

Note 1: RE3 is multiplexed with MCLR and is only available when the MCLR Resets are disabled.

2: OSC1/CLKI and OSC2/CLKO are only available in select oscillator modes and when these pins are not being used as digital I/O. Refer to Section 2.0 "Oscillator Configurations" for additional information.

### 5.3.5 STATUS REGISTER

**REGISTER 5-2:**

The STATUS register, shown in Register 5-2, contains the arithmetic status of the ALU. As with any other SFR, it can be the operand for any instruction.

If the STATUS register is the destination for an instruction that affects the Z, DC, C, OV or N bits, the results of the instruction are not written; instead, the status is updated according to the instruction performed. Therefore, the result of an instruction with the STATUS register as its destination may be different than intended. As an example, CLRF STATUS will set the Z bit and leave the remaining Status bits unchanged ('000u u1uu').

STATUS REGISTER

It is recommended that only BCF, BSF, SWAPF, MOVFF and MOVWF instructions are used to alter the STATUS register, because these instructions do not affect the Z, C, DC, OV or N bits in the STATUS register.

For other instructions that do not affect Status bits, see the instruction set summaries in Table 25-2 and Table 25-3.

Note: The C and DC bits operate as the borrow and digit borrow bits respectively in subtraction.

|         | U-0                            | U-0                                             | U-0           | R/W-x                                          | R/W-x          | R/W-x        | R/W-x         | R/W-x    |

|---------|--------------------------------|-------------------------------------------------|---------------|------------------------------------------------|----------------|--------------|---------------|----------|

|         | _                              | —                                               |               | N                                              | OV             | Z            | DC            | С        |

|         | bit 7                          |                                                 |               |                                                |                |              |               | bit 0    |

| bit 7-5 | Unimplen                       | nented: Read                                    | <b>as</b> '0' |                                                |                |              |               |          |

| bit 4   | N: Negativ                     |                                                 |               |                                                |                |              |               |          |

|         |                                | used for signe<br>ALU MSB = 1                   |               | tic (2's comp                                  | lement). It ir | ndicates whe | ther the res  | ult was  |

|         |                                | t was negative<br>t was positive                | )             |                                                |                |              |               |          |

| bit 3   | OV: Overf                      | flow bit                                        |               |                                                |                |              |               |          |

|         | magnitude                      | used for signe<br>which cause<br>low occurred f | s the sign I  | bit (bit 7) to c                               | hange state    | ).           |               | he 7-bit |

|         |                                | erflow occurre                                  |               | ,                                              |                | ·            | ,             |          |

| bit 2   | Z: Zero bi                     | t                                               |               |                                                |                |              |               |          |

|         |                                | esult of an arit<br>esult of an arit            |               |                                                |                | D            |               |          |

| bit 1   |                                | carry/ <mark>borrow</mark> b<br>F, ADDLW, S     |               | SUBWF instr                                    | uctions:       |              |               |          |

|         |                                | y-out from the<br>rry-out from th               |               |                                                |                | rred         |               |          |

|         | Note:                          | complement                                      | t of the se   | y is reversed<br>cond operan<br>bit 4 or bit 3 | d. For rotate  | e (RRF, RLF) |               |          |

| bit 0   | <b>C:</b> Carry/t<br>For ADDWI | DORTOW bit                                      | SUBLW and     | SUBWF instr                                    | uctions:       |              |               |          |

|         |                                | y-out from the<br>rry-out from th               |               |                                                |                |              |               |          |

|         | Note:                          | complement                                      | t of the se   | y is reversed<br>cond operan<br>high or low-c  | d. For rotate  | e (RRF, RLF) | ) instruction |          |

|         | Legend:                        |                                                 |               |                                                |                |              |               |          |

|         | R = Read                       | lable bit                                       | W = \         | Nritable bit                                   | U = Unii       | mplemented   | bit, read as  | '0'      |

|         | -n = Value                     | e at POR                                        | '1' = l       | Bit is set                                     |                | is cleared   | x = Bit is i  |          |

#### © 2007 Microchip Technology Inc.

### 5.4 Data Addressing Modes

| Note: | The execution of some instructions in the core PIC18 instruction set are changed when the PIC18 extended instruction |

|-------|----------------------------------------------------------------------------------------------------------------------|

|       | set is enabled. See Section 5.6 "Data<br>Memory and the Extended Instruction<br>Set" for more information.           |

While the program memory can be addressed in only one way – through the program counter – information in the data memory space can be addressed in several ways. For most instructions, the addressing mode is fixed. Other instructions may use up to three modes, depending on which operands are used and whether or not the extended instruction set is enabled.

The addressing modes are:

- Inherent

- Literal

- Direct

- Indirect

An additional addressing mode, Indexed Literal Offset, is available when the extended instruction set is enabled (XINST Configuration bit = 1). Its operation is discussed in greater detail in **Section 5.6.1** "**Indexed Addressing with Literal Offset**".

### 5.4.1 INHERENT AND LITERAL ADDRESSING

Many PIC18 control instructions do not need any argument at all; they either perform an operation that globally affects the device or they operate implicitly on one register. This addressing mode is known as Inherent Addressing. Examples include SLEEP, RESET and DAW.

Other instructions work in a similar way but require an additional explicit argument in the opcode. This is known as Literal Addressing mode because they require some literal value as an argument. Examples include ADDLW and MOVLW which, respectively, add or move a literal value to the W register. Other examples include CALL and GOTO, which include a 20-bit program memory address.

#### 5.4.2 DIRECT ADDRESSING

Direct addressing specifies all or part of the source and/or destination address of the operation within the opcode itself. The options are specified by the arguments accompanying the instruction.

In the core PIC18 instruction set, bit-oriented and byte-oriented instructions use some version of direct addressing by default. All of these instructions include some 8-bit literal address as their Least Significant Byte. This address specifies either a register address in one of the banks of data RAM (Section 5.3.3 "General **Purpose Register File**") or a location in the Access Bank (Section 5.3.2 "Access Bank") as the data source for the instruction.

The Access RAM bit 'a' determines how the address is interpreted. When 'a' is '1', the contents of the BSR (Section 5.3.1 "Bank Select Register (BSR)") are used with the address to determine the complete 12-bit address of the register. When 'a' is '0', the address is interpreted as being a register in the Access Bank. Addressing that uses the Access RAM is sometimes also known as Direct Forced Addressing mode.

A few instructions, such as MOVFF, include the entire 12-bit address (either source or destination) in their opcodes. In those cases, the BSR is ignored entirely.

The destination of the operation's results is determined by the destination bit 'd'. When 'd' is '1', the results are stored back in the source register, overwriting its original contents. When 'd' is '0', the results are stored in the W register. Instructions without the 'd' argument have a destination that is implicit in the instruction; their destination is either the target register being operated on or the W register.

### 5.4.3 INDIRECT ADDRESSING

Indirect addressing allows the user to access a location in data memory without giving a fixed address in the instruction. This is done by using File Select Registers (FSRs) as pointers to the locations to be read or written to. Since the FSRs are themselves located in RAM as Special File Registers, they can also be directly manipulated under program control. This makes FSRs very useful in implementing data structures, such as tables and arrays in data memory.

The registers for indirect addressing are also implemented with Indirect File Operands (INDFs) that permit automatic manipulation of the pointer value with auto-incrementing, auto-decrementing or offsetting with another value. This allows for efficient code, using loops, such as the example of clearing an entire RAM bank in Example 5-5.

### EXAMPLE 5-5: HOW TO CLEAR RAM (BANK 1) USING INDIRECT ADDRESSING

|          | LFSR  | FSR0, 100h | ; |                |

|----------|-------|------------|---|----------------|

| NEXT     | CLRF  | POSTINC0   | ; | Clear INDF     |

|          |       |            | ; | register then  |

|          |       |            | ; | inc pointer    |

|          | BTFSS | FSR0H, 1   | ; | All done with  |

|          |       |            | ; | Bank1?         |

|          | BRA   | NEXT       | ; | NO, clear next |

| CONTINUE |       |            | ; | YES, continue  |

|          |       |            |   |                |

# 5.4.3.1 FSR Registers and the INDF Operand

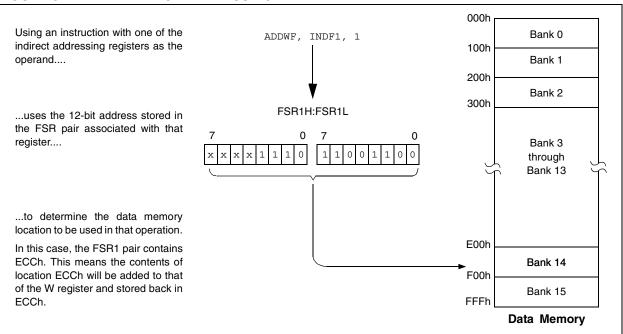

At the core of indirect addressing are three sets of registers: FSR0, FSR1 and FSR2. Each represents a pair of 8-bit registers, FSRnH and FSRnL. The four upper bits of the FSRnH register are not used, so each FSR pair holds a 12-bit value. This represents a value that can address the entire range of the data memory in a linear fashion. The FSR register pairs, then, serve as pointers to data memory locations.

Indirect addressing is accomplished with a set of Indirect File Operands, INDF0 through INDF2. These can be thought of as "virtual" registers: they are mapped in the SFR space, but are not physically implemented. Reading or writing to a particular INDF register actually accesses its corresponding FSR register pair. A read from INDF1, for example, reads the data at the address indicated by FSR1H:FSR1L. Instructions that use the INDF registers as operands actually use the contents of their corresponding FSR as a pointer to the instruction's target. The INDF operand is just a convenient way of using the pointer.

Because indirect addressing uses a full 12-bit address, data RAM banking is not necessary. Thus, the current contents of the BSR and the Access RAM bit have no effect on determining the target address.

### FIGURE 5-7: INDIRECT ADDRESSING

© 2007 Microchip Technology Inc.

### 6.4 Erasing Flash Program Memory

The minimum erase block is 32 words or 64 bytes. Only through the use of an external programmer, or through ICSP control, can larger blocks of program memory be bulk erased. Word erase in the Flash array is not supported.

When initiating an erase sequence from the microcontroller itself, a block of 64 bytes of program memory is erased. The Most Significant 16 bits of the TBLPTR<21:6> point to the block being erased. TBLPTR<5:0> are ignored.

The EECON1 register commands the erase operation. The EEPGD bit must be set to point to the Flash program memory. The WREN bit must be set to enable write operations. The FREE bit is set to select an erase operation.

For protection, the write initiate sequence for EECON2 must be used.

A long write is necessary for erasing the internal Flash. Instruction execution is halted while in a long write cycle. The long write will be terminated by the internal programming timer.

### 6.4.1 FLASH PROGRAM MEMORY ERASE SEQUENCE

The sequence of events for erasing a block of internal program memory location is:

- 1. Load Table Pointer register with address of row being erased.

- 2. Set the EECON1 register for the erase operation:

- set EEPGD bit to point to program memory;

- clear the CFGS bit to access program memory;

- set WREN bit to enable writes;

- set FREE bit to enable the erase.

- 3. Disable interrupts.

- 4. Write 55h to EECON2.

- 5. Write 0AAh to EECON2.

- 6. Set the WR bit. This will begin the row erase cycle.

- 7. The CPU will stall for duration of the erase (about 2 ms using internal timer).

- 8. Re-enable interrupts.

|                      | MOVLW<br>MOVWF<br>MOVWF<br>MOVLW<br>MOVLW<br>MOVWF | CODE_ADDR_UPPER<br>TBLPTRU<br>CODE_ADDR_HIGH<br>TBLPTRH<br>CODE_ADDR_LOW<br>TBLPTRL | ; load TBLPTR with the base<br>; address of the memory block                                                                                         |

|----------------------|----------------------------------------------------|-------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| ERASE_ROW            |                                                    |                                                                                     |                                                                                                                                                      |

|                      | BSF<br>BCF<br>BSF<br>BSF<br>BCF                    | EECON1, EEPGD<br>EECON1, CFGS<br>EECON1, WREN<br>EECON1, FREE<br>INTCON, GIE        | ; point to Flash program memory<br>; access Flash program memory<br>; enable write to memory<br>; enable Row Erase operation<br>; disable interrupts |

| Required<br>Sequence | MOVLW<br>MOVWF<br>MOVLW<br>MOVWF<br>BSF            | 55h<br>EECON2<br>0AAh<br>EECON2<br>EECON1, WR                                       | ; write 55h<br>; write 0AAh<br>; start erase (CPU stall)                                                                                             |

|                      | BSF                                                | INTCON, GIE                                                                         | ; re-enable interrupts                                                                                                                               |

### EXAMPLE 6-2: ERASING A FLASH PROGRAM MEMORY ROW

### 6.5 Writing to Flash Program Memory

The minimum programming block is 32 words or 64 bytes. Word or byte programming is not supported.

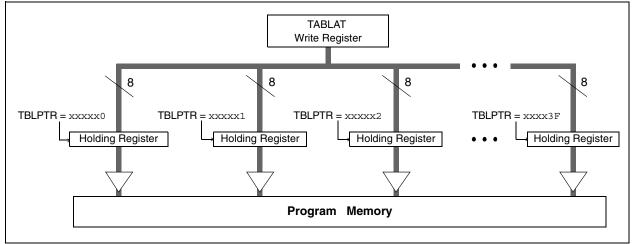

Table writes are used internally to load the holding registers needed to program the Flash memory. There are 64 holding registers used by the table writes for programming.

Since the Table Latch (TABLAT) is only a single byte, the TBLWT instruction may need to be executed 64 times for each programming operation. All of the table write operations will essentially be short writes because only the holding registers are written. At the end of updating the 64 holding registers, the EECON1 register must be written to in order to start the programming operation with a long write. The long write is necessary for programming the internal Flash. Instruction execution is halted while in a long write cycle. The long write will be terminated by the internal programming timer.

The EEPROM on-chip timer controls the write time. The write/erase voltages are generated by an on-chip charge pump, rated to operate over the voltage range of the device.

Note: The default value of the holding registers on device Resets and after write operations is FFh. A write of FFh to a holding register does not modify that byte. This means that individual bytes of program memory may be modified, provided that the change does not attempt to change any bit from a '0' to a '1'. When modifying individual bytes, it is not necessary to load all 64 holding registers before executing a write operation.

### 6.5.1 FLASH PROGRAM MEMORY WRITE SEQUENCE

The sequence of events for programming an internal program memory location should be:

- 1. Read 64 bytes into RAM.

- 2. Update data values in RAM as necessary.

- 3. Load Table Pointer register with address being erased.

- 4. Execute the row erase procedure.

- 5. Load Table Pointer register with address of first byte being written.

- 6. Write the 64 bytes into the holding registers with auto-increment.

- 7. Set the EECON1 register for the write operation:

- set EEPGD bit to point to program memory;

- clear the CFGS bit to access program memory;

- set WREN to enable byte writes.

- 8. Disable interrupts.

- 9. Write 55h to EECON2.

- 10. Write 0AAh to EECON2.

- 11. Set the WR bit. This will begin the write cycle.

- 12. The CPU will stall for duration of the write (about 2 ms using internal timer).

- 13. Re-enable interrupts.

- 14. Verify the memory (table read).

This procedure will require about 18 ms to update one row of 64 bytes of memory. An example of the required code is given in Example 6-3.

Note: Before setting the WR bit, the Table Pointer address needs to be within the intended address range of the 64 bytes in the holding register. NOTES:

In addition to the expanded range of modes available through the CCP1CON register, the ECCP1 module has two additional registers associated with Enhanced PWM operation and auto-shutdown features. They are:

- ECCP1DEL (Dead-band delay)

- ECCP1AS (Auto-shutdown configuration)

### 16.1 ECCP1 Outputs and Configuration

The Enhanced CCP1 module may have up to four PWM outputs, depending on the selected operating mode. These outputs, designated P1A through P1D, are multiplexed with I/O pins on PORTC and PORTD. The outputs that are active depend on the CCP1 operating mode selected. The pin assignments are summarized in Table 16-1.

To configure the I/O pins as PWM outputs, the proper PWM mode must be selected by setting the EPWM1M1:EPWM1M0 and CCP1M3:CCP1M0 bits. The appropriate TRISC and TRISD direction bits for the port pins must also be set as outputs.

### 16.1.1 ECCP1 MODULES AND TIMER RESOURCES

Like the standard CCP1 modules, the ECCP1 module can utilize Timers 1, 2 or 3, depending on the mode selected. Timer1 and Timer3 are available for modules in Capture or Compare modes, while Timer2 is available for modules in PWM mode. Interactions between the standard and Enhanced CCP1 modules are identical to those described for standard CCP1 modules. Additional details on timer resources are provided in Section 15.1.1 "CCP1 Modules and Timer Resources".

### 16.2 Capture and Compare Modes

Except for the operation of the special event trigger discussed below, the Capture and Compare modes of the ECCP1 module are identical in operation to that of CCP1. These are discussed in detail in Section 15.2 "Capture Mode" and Section 15.3 "Compare Mode".

### 16.2.1 SPECIAL EVENT TRIGGER

The special event trigger output of ECCP1 resets the TMR1 or TMR3 register pair, depending on which timer resource is currently selected. This allows the ECCP1 register to effectively be a 16-bit programmable period register for Timer1 or Timer3. The special event trigger for ECCP1 can also start an A/D conversion. In order to start the conversion, the A/D converter must be previously enabled.

### 16.3 Standard PWM Mode

When configured in Single Output mode, the ECCP1 module functions identically to the standard CCP1 module in PWM mode, as described in **Section 15.4 "PWM Mode"**. This is also sometimes referred to as "Compatible CCP1" mode, as in Table 16-1.

Note: When setting up single output PWM operations, users are free to use either of the processes described in Section 15.4.4 "Setup for PWM Operation" or Section 16.4.9 "Setup for PWM Operation". The latter is more generic but will work for either single or multi-output PWM.

| ECCP1 Mode CCP1CON<br>Configuration |           | RD4  | RD5      | RD6      | RD7      |  |  |  |  |

|-------------------------------------|-----------|------|----------|----------|----------|--|--|--|--|

| All PIC18F4585/4680 devices:        |           |      |          |          |          |  |  |  |  |

| Compatible CCP1                     | 00xx 11xx | CCP1 | RD5/PSP5 | RD6/PSP6 | RD7/PSP7 |  |  |  |  |

| Dual PWM 10xx 11xx                  |           | P1A  | P1B      | RD6/PSP6 | RD7/PSP7 |  |  |  |  |

| Quad PWM                            | x1xx 11xx | P1A  | P1B      | P1C      | P1D      |  |  |  |  |

### TABLE 16-1: PIN ASSIGNMENTS FOR VARIOUS ECCP1 MODES

**Legend:** x = Don't care. Shaded cells indicate pin assignments not used by ECCP1 in a given mode.

### 16.4.9 SETUP FOR PWM OPERATION

The following steps should be taken when configuring the ECCP1 module for PWM operation:

- 1. Configure the PWM pins P1A and P1B (and P1C and P1D, if used) as inputs by setting the corresponding TRIS bits.

- 2. Set the PWM period by loading the PR2 register.

- Configure the ECCP1 module for the desired PWM mode and configuration by loading the ECCP1CON register with the appropriate values:

- Select one of the available output configurations and direction with the EPWM1M1:EPWM1M0 bits.

- Select the polarities of the PWM output signals with the ECCP1M3:ECCP1M0 bits.

- 4. Set the PWM duty cycle by loading the ECCPR1L register and ECCP1CON<5:4> bits.

- 5. For Half-Bridge Output mode, set the dead-band delay by loading ECCP1DEL<6:0> with the appropriate value.

- 6. If auto-shutdown operation is required, load the ECCP1AS register:

- Select the auto-shutdown sources using the ECCPAS2:ECCPAS0 bits.

- Select the shutdown states of the PWM output pins using PSSAC1:PSSAC0 and PSSBD1:PSSBD0 bits.

- Set the ECCPASE bit (ECCP1AS<7>).

- Configure the comparators using the CMCON register.

- Configure the comparator inputs as analog inputs.

- 7. If auto-restart operation is required, set the PRSEN bit (ECCP1DEL<7>).

- 8. Configure and start TMR2:

- Clear the TMR2 interrupt flag bit by clearing the TMR2IF bit (PIR1<1>).

- Set the TMR2 prescale value by loading the T2CKPS bits (T2CON<1:0>).

- Enable Timer2 by setting the TMR2ON bit (T2CON<2>).

- 9. Enable PWM outputs after a new PWM cycle has started:

- Wait until TMRn overflows (TMRnIF bit is set).

- Enable the ECCP1/P1A, P1B, P1C and/or P1D pin outputs by clearing the respective TRIS bits.

- Clear the ECCPASE bit (ECCP1AS<7>).

### 16.4.10 EFFECTS OF A RESET

Both Power-on Reset and subsequent Resets will force all ports to Input mode and the CCP1 registers to their Reset states.

This forces the Enhanced CCP1 module to reset to a state compatible with the standard CCP1 module.

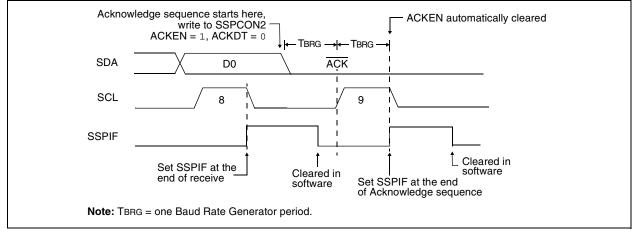

### 17.4.12 ACKNOWLEDGE SEQUENCE TIMING

An Acknowledge sequence is enabled by setting the Acknowledge sequence enable bit. ACKEN (SSPCON2<4>). When this bit is set, the SCL pin is pulled low and the contents of the Acknowledge data bit are presented on the SDA pin. If the user wishes to generate an Acknowledge, then the ACKDT bit should be cleared. If not, the user should set the ACKDT bit before starting an Acknowledge sequence. The Baud Rate Generator then counts for one rollover period (TBRG) and the SCL pin is deasserted (pulled high). When the SCL pin is sampled high (clock arbitration), the Baud Rate Generator counts for TBRG. The SCL pin is then pulled low. Following this, the ACKEN bit is automatically cleared, the Baud Rate Generator is turned off and the MSSP module then goes into Idle mode (Figure 17-23).

### 17.4.12.1 WCOL Status Flag

If the user writes the SSPBUF when an Acknowledge sequence is in progress, then WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

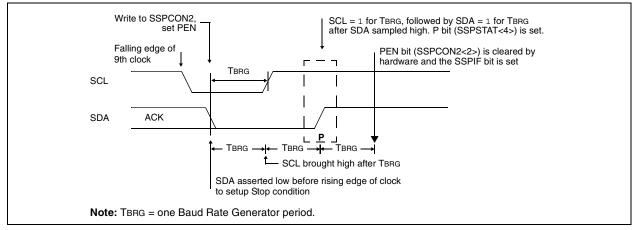

### 17.4.13 STOP CONDITION TIMING

A Stop bit is asserted on the SDA pin at the end of a receive/transmit by setting the Stop Sequence Enable bit, PEN (SSPCON2<2>). At the end of a receive/ transmit, the SCL line is held low after the falling edge of the ninth clock. When the PEN bit is set, the master will assert the SDA line low. When the SDA line is sampled low, the Baud Rate Generator is reloaded and counts down to '0'. When the Baud Rate Generator times out, the SCL pin will be brought high and one TBRG (Baud Rate Generator rollover count) later, the SDA pin will be deasserted. When the SDA pin is sampled high while SCL is high, the P bit (SSPSTAT<4>) is set. A TBRG later, the PEN bit is cleared and the SSPIF bit is set (Figure 17-24).

### 17.4.13.1 WCOL Status Flag

If the user writes the SSPBUF when a Stop sequence is in progress, then the WCOL bit is set and the contents of the buffer are unchanged (the write doesn't occur).

### FIGURE 17-23: ACKNOWLEDGE SEQUENCE WAVEFORM

### FIGURE 17-24: STOP CONDITION RECEIVE OR TRANSMIT MODE

# PIC18F2585/2680/4585/4680

| ER 18-3: | BAUDCON: BAUD RATE CONTROL REGISTER                                                                                                                           |                              |                                                 |                         |                         |             |               |              |  |  |  |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|-------------------------------------------------|-------------------------|-------------------------|-------------|---------------|--------------|--|--|--|

|          | R/W-0                                                                                                                                                         | R-1                          | U-0                                             | R/W-0                   | R/W-0                   | U-0         | R/W-0         | R/W-0        |  |  |  |

|          | ABDOVF                                                                                                                                                        | RCIDL                        |                                                 | SCKP                    | BRG16                   | _           | WUE           | ABDEN        |  |  |  |

|          | bit 7                                                                                                                                                         |                              |                                                 |                         |                         |             |               | bit 0        |  |  |  |

| bit 7    | ABDOVF:                                                                                                                                                       | Auto-Baud                    | Acquisition F                                   | Rollover Stat           | us bit                  |             |               |              |  |  |  |

|          | (must l                                                                                                                                                       | be cleared i                 |                                                 | C C                     | Baud Rate D             | etect mode  |               |              |  |  |  |

| bit 6    | RCIDL: Re                                                                                                                                                     | ceive Opera                  | ation Idle Sta                                  | atus bit                |                         |             |               |              |  |  |  |

|          |                                                                                                                                                               | ve operation<br>ve operation |                                                 |                         |                         |             |               |              |  |  |  |

| bit 5    | Unimplem                                                                                                                                                      | ented: Rea                   | <b>d as</b> '0'                                 |                         |                         |             |               |              |  |  |  |

| bit 4    | SCKP: Syr                                                                                                                                                     | nchronous C                  | lock Polarity                                   | / Select bit            |                         |             |               |              |  |  |  |

|          | <b>SCKP:</b> Synchronous Clock Polarity Select bit<br><u>Asynchronous mode:</u><br>Unused in this mode.                                                       |                              |                                                 |                         |                         |             |               |              |  |  |  |

|          |                                                                                                                                                               | ate for clock                | (CK) is a hi<br>(CK) is a lo                    |                         |                         |             |               |              |  |  |  |

| bit 3    | <b>BRG16:</b> 16                                                                                                                                              | bit Baud R                   | ate Register                                    | <sup>r</sup> Enable bit |                         |             |               |              |  |  |  |

|          |                                                                                                                                                               |                              | Generator –<br>enerator – S                     |                         | nd SPBRG<br>(Compatible | e mode), SP | BRGH valu     | e ignored    |  |  |  |

| bit 2    | Unimplem                                                                                                                                                      | ented: Rea                   | <b>d as</b> '0'                                 |                         |                         |             |               |              |  |  |  |

| bit 1    | WUE: Wak                                                                                                                                                      | e-up Enable                  | e bit                                           |                         |                         |             |               |              |  |  |  |

|          | Asynchronous mode:                                                                                                                                            |                              |                                                 |                         |                         |             |               |              |  |  |  |

|          | cleared                                                                                                                                                       | d in hardwa                  | tinue to sam<br>re on followin<br>red or rising | ng rising ed            |                         | upt generat | ted on fallir | ig edge; bit |  |  |  |

|          | Synchronous mode:                                                                                                                                             |                              |                                                 |                         |                         |             |               |              |  |  |  |

|          | Unused in t                                                                                                                                                   |                              |                                                 |                         |                         |             |               |              |  |  |  |

| bit 0    | ABDEN: A                                                                                                                                                      | uto-Baud De                  | etect Enable                                    | bit                     |                         |             |               |              |  |  |  |

|          | Asynchronous mode:                                                                                                                                            |                              |                                                 |                         |                         |             |               |              |  |  |  |

|          | <ul> <li>1 = Enable baud rate measurement on the next character. Requires reception of a Sync field<br/>(55h); cleared in hardware upon completion</li> </ul> |                              |                                                 |                         |                         |             |               |              |  |  |  |

|          | 0 = Baud rate measurement disabled or completed                                                                                                               |                              |                                                 |                         |                         |             |               |              |  |  |  |

|          | <u>Synchrono</u><br>Unused in t                                                                                                                               |                              |                                                 |                         |                         |             |               |              |  |  |  |

|          | Unused III I                                                                                                                                                  |                              |                                                 |                         |                         |             |               |              |  |  |  |

|          |                                                                                                                                                               |                              |                                                 |                         |                         |             |               |              |  |  |  |

### REGISTER 18-3: BAUDCON: BAUD RATE CONTROL REGISTER

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

### 18.4 EUSART Synchronous Slave Mode

Synchronous Slave mode is entered by clearing bit, CSRC (TXSTA<7>). This mode differs from the Synchronous Master mode in that the shift clock is supplied externally at the CK pin (instead of being supplied internally in Master mode). This allows the device to transfer or receive data while in any low-power mode.

### 18.4.1 EUSART SYNCHRONOUS SLAVE TRANSMIT

The operation of the Synchronous Master and Slave modes are identical, except in the case of the Sleep mode.

If two words are written to the TXREG and then the SLEEP instruction is executed, the following will occur:

- a) The first word will immediately transfer to the TSR register and transmit.

- b) The second word will remain in the TXREG register.

- c) Flag bit TXIF will not be set.

- d) When the first word has been shifted out of TSR, the TXREG register will transfer the second word to the TSR and flag bit TXIF will now be set.

- e) If enable bit TXIE is set, the interrupt will wake the chip from Sleep. If the global interrupt is enabled, the program will branch to the interrupt vector.

To set up a Synchronous Slave Transmission:

- 1. Enable the synchronous slave serial port by setting bits SYNC and SPEN and clearing bit CSRC.

- 2. Clear bits CREN and SREN.

- 3. If interrupts are desired, set enable bit TXIE.

- 4. If 9-bit transmission is desired, set bit TX9.

- 5. Enable the transmission by setting enable bit TXEN.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- 7. Start transmission by loading data to the TXREGx register.

- If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

| Name    | Bit 7                                         | Bit 6        | Bit 5        | Bit 4        | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

|---------|-----------------------------------------------|--------------|--------------|--------------|-------|--------|--------|--------|----------------------------|

| INTCON  | <b>GIE/GIEH</b>                               | PEIE/GIEL    | TMR0IE       | INT0IE       | RBIE  | TMR0IF | INT0IF | RBIF   | 49                         |

| PIR1    | PSPIF <sup>(1)</sup>                          | ADIF         | RCIF         | TXIF         | SSPIF | CCP1IF | TMR2IF | TMR1IF | 52                         |

| PIE1    | PSPIE <sup>(1)</sup>                          | ADIE         | RCIE         | TXIE         | SSPIE | CCP1IE | TMR2IE | TMR1IE | 52                         |

| IPR1    | PSPIP <sup>(1)</sup>                          | ADIP         | RCIP         | TXIP         | SSPIP | CCP1IP | TMR2IP | TMR1IP | 52                         |

| RCSTA   | SPEN                                          | RX9          | SREN         | CREN         | ADDEN | FERR   | OERR   | RX9D   | 51                         |

| TXREG   | EUSART T                                      | ransmit Regi | ster         |              |       |        |        |        | 51                         |

| TXSTA   | CSRC                                          | TX9          | TXEN         | SYNC         | SENDB | BRGH   | TRMT   | TX9D   | 51                         |

| BAUDCON | ABDOVF                                        | RCIDL        |              | SCKP         | BRG16 | —      | WUE    | ABDEN  | 51                         |

| SPBRGH  | EUSART Baud Rate Generator Register High Byte |              |              |              |       |        |        |        |                            |

| SPBRG   | EUSART B                                      | aud Rate Ge  | enerator Reg | gister Low E | Byte  |        |        |        | 51                         |

### TABLE 18-9: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE TRANSMISSION

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used for synchronous slave transmission.

**Note 1:** Reserved in PIC18F2X8X devices; always maintain these bits clear.

### 20.0 COMPARATOR MODULE

The analog comparator module contains two comparators that can be configured in a variety of ways. The inputs can be selected from the analog inputs multiplexed with pins RA0 through RA5, as well as the on-chip voltage reference (see **Section 21.0 "Comparator Voltage Reference Module**"). The digital outputs (normal or inverted) are available at the pin level and can also be read through the control register. The CMCON register (Register 20-1) selects the comparator input and output configuration. Block diagrams of the various comparator configurations are shown in Figure 20-1.

#### REGISTER 20-1: CMCON: COMPARATOR CONTROL REGISTER

| R-0   | R-0   | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| C2OUT | C10UT | C2INV | C1INV | CIS   | CM2   | CM1   | CM0   |

| bit 7 |       |       |       |       |       |       | bit 0 |

|       |       |       |       |       |       |       |       |

bit 7 C2OUT: Comparator 2 Output bit When C2INV = 0: 1 = C2 VIN+ > C2 VIN-0 = C2 VIN + < C2 VIN-When C2INV = 1: 1 = C2 VIN + < C2 VIN -0 = C2 VIN + > C2 VIN bit 6 C1OUT: Comparator 1 Output bit When C1INV = 0: 1 = C1 VIN + > C1 VIN -0 = C1 VIN + < C1 VIN-When C1INV = 1: 1 = C1 VIN + < C1 VIN-0 = C1 VIN + > C1 VIN bit 5 C2INV: Comparator 2 Output Inversion bit 1 = C2 output inverted 0 = C2 output not inverted bit 4 C1INV: Comparator 1 Output Inversion bit 1 = C1 Output inverted 0 = C1 Output not inverted bit 3 CIS: Comparator Input Switch bit When CM2:CM0 = 110: 1 = C1 VIN- connects to RD0/PSP0/C1IN+ C2 VIN- connects to RD2/PSP2/C2IN+ 0 = C1 VIN- connects to RD1/PSP1/C1IN-C2 VIN- connects to RD3/PSP3/C2INbit 2-0 CM2:CM0: Comparator Mode bits Figure 20-1 shows the Comparator modes and the CM2:CM0 bit settings.

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented b  | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### EXAMPLE 23-1: CHANGING TO CONFIGURATION MODE

```

; Request Configuration mode.

MOVLW B'1000000'

; Set to Configuration Mode.

MOVWF CANCON

; A request to switch to Configuration mode may not be immediately honored.

; Module will wait for CAN bus to be idle before switching to Configuration Mode.

; Request for other modes such as Loopback, Disable etc. may be honored immediately.

; It is always good practice to wait and verify before continuing.

ConfigWait:

MOVF CANSTAT, W

; Read current mode state.

ANDLW B'1000000'

; Interested in OPMODE bits only.

TSTFSZ WREG

; Is it Configuration mode yet?

; No. Continue to wait...

BRA ConfigWait

; Module is in Configuration mode now.

; Modify configuration registers as required.

; Switch back to Normal mode to be able to communicate.

```

### EXAMPLE 23-2: WIN AND ICODE BITS USAGE IN INTERRUPT SERVICE ROUTINE TO ACCESS TX/RX BUFFERS

```

; Save application required context.

; Poll interrupt flags and determine source of interrupt

; This was found to be CAN interrupt

; TempCANCON and TempCANSTAT are variables defined in Access Bank low

MOVFF CANCON, TempCANCON

; Save CANCON.WIN bits

; This is required to prevent CANCON

; from corrupting CAN buffer access

; in-progress while this interrupt

; occurred

MOVFF CANSTAT, TempCANSTAT

; Save CANSTAT register

; This is required to make sure that

; we use same CANSTAT value rather

; than one changed by another CAN

; interrupt.

; Retrieve ICODE bits

MOVF

TempCANSTAT, W

ANDLW B'00001110'

ADDWF PCL, F

; Perform computed GOTO

; to corresponding interrupt cause

; 000 = No interrupt

BRA

NoInterrupt

; 001 = Error interrupt

; 010 = TXB2 interrupt

ErrorInterrupt

BRA

TXB2Interrupt

BRA

BRA TXB1Interrupt

; 011 = TXB1 interrupt

BRA TXB0Interrupt

; 100 = TXB0 interrupt

BRA RXB1Interrupt

; 101 = RXB1 interrupt

BRA RXB0Interrupt

; 110 = RXB0 interrupt

; 111 = Wake-up on interrupt

WakeupInterrupt

BCF PIR3, WAKIF

; Clear the interrupt flag

; User code to handle wake-up procedure

;

;

; Continue checking for other interrupt source or return from here

NoInterrupt

; PC should never vector here. User may

; place a trap such as infinite loop or pin/port

; indication to catch this error.

```

# PIC18F2585/2680/4585/4680

### **REGISTER 23-28:** BnEIDH: TX/RX BUFFER n EXTENDED IDENTIFIER REGISTERS, HIGH BYTE IN RECEIVE MODE $[0 \le n \le 5, TXnEN (BSEL0<n>) = 0]^{(1)}$

| R-x   | R-x   | R-x   | -<br>R-x | R-x   | R-x   | R-x  | R-x   |

|-------|-------|-------|----------|-------|-------|------|-------|

| EID15 | EID14 | EID13 | EID12    | EID11 | EID10 | EID9 | EID8  |

| bit 7 |       |       |          |       |       |      | bit 0 |

bit 7-0

EID15:EID8: Extended Identifier bits

Note 1: These registers are available in Mode 1 and 2 only.

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | l bit, read as '0' |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

###

| F   | R/W-x |

|-----|-------|-------|-------|-------|-------|-------|-------|-------|

| E   | EID15 | EID14 | EID13 | EID12 | EID11 | EID10 | EID9  | EID8  |

| bit | 7     |       |       |       |       |       |       | bit 0 |

bit 7-0 EID15:EID8: Extended Identifier bits

**Note 1:** These registers are available in Mode 1 and 2 only.

| Legend:           |                  |                                          |

|-------------------|------------------|------------------------------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0'       |

| -n = Value at POR | '1' = Bit is set | 0' = Bit is cleared $x = Bit is unknown$ |

### **REGISTER 23-30:** BnEIDL: TX/RX BUFFER n EXTENDED IDENTIFIER REGISTERS, LOW BYTE IN RECEIVE MODE $[0 \le n \le 5, TXnEN (BSEL<n>) = 0]^{(1)}$

| R-x   | R-x  | R-x  | R-x  | R-x  | R-x  | R-x  | R-x   |

|-------|------|------|------|------|------|------|-------|

| EID7  | EID6 | EID5 | EID4 | EID3 | EID2 | EID1 | EID0  |

| bit 7 |      |      |      |      |      |      | bit 0 |

bit 7-0

EID7:EID0: Extended Identifier bits

**Note 1:** These registers are available in Mode 1 and 2 only.

| Legend:           |                  |                                          |

|-------------------|------------------|------------------------------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0'       |

| -n = Value at POR | '1' = Bit is set | 0' = Bit is cleared $x = Bit is unknown$ |

### 23.10 Synchronization

To compensate for phase shifts between the oscillator frequencies of each of the nodes on the bus, each CAN controller must be able to synchronize to the relevant signal edge of the incoming signal. When an edge in the transmitted data is detected, the logic will compare the location of the edge to the expected time (Sync\_Seg). The circuit will then adjust the values of Phase Segment 1 and Phase Segment 2 as necessary. There are two mechanisms used for synchronization.

### 23.10.1 HARD SYNCHRONIZATION

Hard synchronization is only done when there is a recessive to dominant edge during a bus Idle condition, indicating the start of a message. After hard synchronization, the bit time counters are restarted with Sync\_Seg. Hard synchronization forces the edge which has occurred to lie within the synchronization segment of the restarted bit time. Due to the rules of synchronization, if a hard synchronization occurs, there will not be a resynchronization within that bit time.

### 23.10.2 RESYNCHRONIZATION

As a result of resynchronization, Phase Segment 1 may be lengthened or Phase Segment 2 may be shortened. The amount of lengthening or shortening of the phase buffer segments has an upper bound given by the Synchronization Jump Width (SJW). The value of the SJW will be added to Phase Segment 1 (see Figure 23-6) or subtracted from Phase Segment 2 (see Figure 23-7). The SJW is programmable between 1 TQ and 4 TQ.

Clocking information will only be derived from recessive to dominant transitions. The property, that only a fixed maximum number of successive bits have the same value, ensures resynchronization to the bit stream during a frame.

The phase error of an edge is given by the position of the edge relative to Sync\_Seg, measured in Tq. The phase error is defined in magnitude of Tq as follows:

- e = 0 if the edge lies within Sync\_Seg.

- e > 0 if the edge lies before the sample point.

- e < 0 if the edge lies after the sample point of the previous bit.

If the magnitude of the phase error is less than, or equal to, the programmed value of the Synchronization Jump Width, the effect of a resynchronization is the same as that of a hard synchronization.

If the magnitude of the phase error is larger than the Synchronization Jump Width and if the phase error is positive, then Phase Segment 1 is lengthened by an amount equal to the Synchronization Jump Width.

If the magnitude of the phase error is larger than the resynchronization jump width and if the phase error is negative, then Phase Segment 2 is shortened by an amount equal to the Synchronization Jump Width.

### 23.10.3 SYNCHRONIZATION RULES

- Only one synchronization within one bit time is allowed.

- An edge will be used for synchronization only if the value detected at the previous sample point (previously read bus value) differs from the bus value immediately after the edge.

- All other recessive to dominant edges fulfilling rules 1 and 2 will be used for resynchronization, with the exception that a node transmitting a dominant bit will not perform a resynchronization as a result of a recessive to dominant edge with a positive phase error.

# PIC18F2585/2680/4585/4680

| COMF                  | Complem                                                          | ent f                                |                      | CPF   | SEQ                    | Compare                                       | f with W, SI                     | kip if f = W     |

|-----------------------|------------------------------------------------------------------|--------------------------------------|----------------------|-------|------------------------|-----------------------------------------------|----------------------------------|------------------|

| Syntax:               | COMF f                                                           | {,d {,a}}                            |                      | Synta | ax:                    | CPFSEQ                                        | f {,a}                           |                  |

| Operands:             | 0 ≤ f ≤ 255                                                      |                                      |                      | Oper  | ands:                  | $0 \leq f \leq 255$                           |                                  |                  |

|                       | $d \in [0,1]$                                                    |                                      |                      |       |                        | a ∈ [0,1]                                     |                                  |                  |

|                       | a ∈ [0,1]                                                        |                                      |                      | Oper  | ation:                 | (f) – (W),                                    | (1.1.1)                          |                  |

| Operation:            | $(\overline{f}) \rightarrow des$                                 | st                                   |                      |       |                        | skip if (f) =                                 | . ,                              |                  |

| Status Affected:      | N, Z                                                             |                                      |                      | Statu | s Affected:            | (unsigned comparison)<br>None                 |                                  |                  |

| Encoding:             | 0001                                                             | 11da ff                              | ff ffff              |       | is Allected.<br>iding: | 0110                                          | 001a ff                          | ff ffff          |

| Description:          | The conten                                                       | ts of register "                     | f' are               |       | Description:           |                                               |                                  | f data memory    |

| ·                     |                                                                  | nted. If 'd' is '1                   |                      | Desc  | inpuon.                |                                               | o the contents                   |                  |

|                       |                                                                  | '. If 'd' is 'o', th                 |                      |       |                        |                                               | an unsigned s                    |                  |

|                       |                                                                  | ( in register 'f'                    | . ,                  |       |                        | lf 'f' = W, th                                | en the fetched                   | l instruction is |

|                       | -                                                                |                                      | nk is selected.      |       |                        |                                               | nd a NOP is e                    |                  |

|                       | If 'a' is '1', the BSR is used to select the GPR bank (default). |                                      |                      |       |                        | instead, making this a two-cycle instruction. |                                  |                  |

|                       |                                                                  | nd the extend                        |                      |       |                        | lf 'a' is 'o', t                              | he Access Ba                     | nk is selected.  |

|                       |                                                                  | led, this instru<br>Literal Offset / | ction operates       |       |                        |                                               |                                  | d to select the  |

|                       |                                                                  | never $f \le 95$ (5                  | 0                    |       |                        | GPR bank                                      | . ,                              |                  |

|                       |                                                                  | .2.3 "Byte-Or                        |                      |       |                        |                                               | nd the extend<br>ed, this instru | ction operates   |

|                       |                                                                  | ed Instruction<br>set Mode" for      |                      |       |                        |                                               | Literal Offset A                 | •                |

|                       |                                                                  |                                      | uelans.              |       |                        |                                               | ever f $\leq$ 95 (5              | ,                |

| Words:                | 1                                                                |                                      |                      |       |                        |                                               | .2.3 "Byte-Or<br>d Instruction   |                  |

| Cycles:               | 1                                                                |                                      |                      |       |                        |                                               | set Mode" for                    |                  |

| Q Cycle Activity:     |                                                                  |                                      |                      | Word  | ls:                    | 1                                             |                                  |                  |

| Q1                    | Q2                                                               | Q3                                   | Q4                   | Cycle | es:                    | 1(2)                                          |                                  |                  |

| Decode                | Read<br>register 'f'                                             | Process<br>Data                      | Write to destination | ,     |                        |                                               | cles if skip an                  | d followed       |

|                       | register i                                                       | Dala                                 | destination          |       |                        | by a                                          | 2-word instru                    | ction.           |

| Example:              | COMF                                                             | REG, 0, 0                            |                      | QC    | ycle Activity:         |                                               |                                  |                  |

|                       |                                                                  | REG, 0, 0                            |                      |       | Q1                     | Q2                                            | Q3                               | Q4               |

| Before Instruc<br>REG | = 13h                                                            |                                      |                      |       | Decode                 | Read                                          | Process                          | No               |

| After Instruction     |                                                                  |                                      |                      | lf sk | in <sup>.</sup>        | register 'f'                                  | Data                             | operation        |

| REG                   | = 13h<br>= ECh                                                   |                                      |                      | 11 51 | Q1                     | Q2                                            | Q3                               | Q4               |

| W                     | = ECh                                                            |                                      |                      |       | No                     | No                                            | No                               | No               |

|                       |                                                                  |                                      |                      |       | operation              | operation                                     | operation                        | operation        |

|                       |                                                                  |                                      |                      | lf sk | ip and followe         |                                               |                                  |                  |

|                       |                                                                  |                                      |                      |       | Q1                     | Q2                                            | Q3                               | Q4               |

|                       |                                                                  |                                      |                      |       | No<br>operation        | No<br>operation                               | No<br>operation                  | No<br>operation  |

|                       |                                                                  |                                      |                      |       | No                     | No                                            | No                               | No               |

|                       |                                                                  |                                      |                      |       | operation              | operation                                     | operation                        | operation        |

|                       |                                                                  |                                      |                      | Exan  | nnle:                  | HERE                                          | CPFSEQ REC                       | - 0              |

|                       |                                                                  |                                      |                      |       | ipic.                  | NEQUAL                                        | :                                | , 0              |

|                       |                                                                  |                                      |                      |       |                        | EQUAL                                         | :                                |                  |

|                       |                                                                  |                                      |                      |       | Before Instruc         | tion                                          |                                  |                  |

|                       |                                                                  |                                      |                      |       | PC Addr                |                                               | RE                               |                  |

|                       |                                                                  |                                      |                      |       | W<br>REG               | = ?<br>= ?                                    |                                  |                  |

|                       |                                                                  |                                      |                      |       | After Instruction      | on                                            |                                  |                  |

|                       |                                                                  |                                      |                      |       |                        | _ \\/·                                        |                                  |                  |

=

# PIC18F2585/2680/4585/4680

| GOT   | ю                                        | Uncondit                                                                 | tional B                            | ranch                      |                                        |  |  |  |  |

|-------|------------------------------------------|--------------------------------------------------------------------------|-------------------------------------|----------------------------|----------------------------------------|--|--|--|--|

| Synta | ax:                                      | GOTO k                                                                   |                                     |                            |                                        |  |  |  |  |

| Oper  | ands:                                    | $0 \le k \le 104$                                                        | $0 \leq k \leq 1048575$             |                            |                                        |  |  |  |  |

| Oper  | ation:                                   | $k \rightarrow PC < 20$                                                  | $k \rightarrow PC<20:1>$            |                            |                                        |  |  |  |  |

| Statu | is Affected:                             | None                                                                     |                                     |                            |                                        |  |  |  |  |

| 1st w | oding:<br>/ord (k<7:0>)<br>word(k<19:8>) | 1110<br>1111                                                             | 1111<br>k <sub>19</sub> kkk         | k <sub>7</sub> kkk<br>kkkk | kkkk <sub>0</sub><br>kkkk <sub>8</sub> |  |  |  |  |

| Word  | te.                                      | anywhere<br>2-Mbyte m<br>value 'k' is<br>GOTO is al<br>instruction.<br>2 | emory rai<br>loaded ir<br>ways a tv | nge. The<br>ito PC<20      |                                        |  |  |  |  |

| Cycle |                                          | 2                                                                        |                                     |                            |                                        |  |  |  |  |

| -     | ycle Activity:                           | -                                                                        |                                     |                            |                                        |  |  |  |  |

|       | Q1                                       | Q2                                                                       | Q3                                  |                            | Q4                                     |  |  |  |  |

|       | Decode                                   | Read literal<br>'k'<7:0>,                                                | No<br>operat                        | ion 'k                     | ad literal<br><19:8>,<br>ite to PC     |  |  |  |  |

|       | No                                       | No                                                                       | No                                  |                            | No                                     |  |  |  |  |

|       | operation                                | operation                                                                | operat                              | ion o                      | peration                               |  |  |  |  |

Example: GOTO THERE

After Instruction

PC = Address (THERE)

| INCF                                                                                                                    | Incremen                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | t f                                                                                        |                                                             | Increment f                                                                  |  |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|-------------------------------------------------------------|------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:                                                                                                                 | INCF f{,c                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | d {,a}}                                                                                    |                                                             |                                                                              |  |  |  |  |  |

| Operands:                                                                                                               | $0 \le f \le 255$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                            |                                                             |                                                                              |  |  |  |  |  |

|                                                                                                                         | d∈[0,1]<br>a∈[0,1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | d ∈ [0,1]<br>a ∈ [0,1]                                                                     |                                                             |                                                                              |  |  |  |  |  |

| Operation:                                                                                                              | • • •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | $a \in [0, 1]$<br>(f) + 1 $\rightarrow$ dest                                               |                                                             |                                                                              |  |  |  |  |  |