# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                               |

|----------------------------|----------------------------------------------------------------------|

| Core Processor             | STM8                                                                 |

| Core Size                  | 8-Bit                                                                |

| Speed                      | 16MHz                                                                |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                    |

| Peripherals                | Infrared, POR, PWM, WDT                                              |

| Number of I/O              | 18                                                                   |

| Program Memory Size        | 4KB (4K x 8)                                                         |

| Program Memory Type        | FLASH                                                                |

| EEPROM Size                | -                                                                    |

| RAM Size                   | 1.5K x 8                                                             |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 3.6V                                                         |

| Data Converters            | -                                                                    |

| Oscillator Type            | Internal                                                             |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                   |

| Mounting Type              | Surface Mount                                                        |

| Package / Case             | 20-TSSOP (0.173", 4.40mm Width)                                      |

| Supplier Device Package    | 20-TSSOP                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm8l101f2p3 |

|                            |                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 9  | Electr | rical par | ameters                                    | 37   |

|----|--------|-----------|--------------------------------------------|------|

|    | 9.1    | Parame    | ter conditions                             | 37   |

|    |        | 9.1.1     | Minimum and maximum values                 | . 37 |

|    |        | 9.1.2     | Typical values                             | . 37 |

|    |        | 9.1.3     | Typical curves                             | . 37 |

|    |        | 9.1.4     | Loading capacitor                          | . 37 |

|    |        | 9.1.5     | Pin input voltage                          | . 38 |

|    | 9.2    | Absolute  | e maximum ratings                          | 38   |

|    | 9.3    | Operatir  | ng conditions                              | 40   |

|    |        | 9.3.1     | General operating conditions               | . 40 |

|    |        | 9.3.2     | Power-up / power-down operating conditions | . 41 |

|    |        | 9.3.3     | Supply current characteristics             | . 41 |

|    |        | 9.3.4     | Clock and timing characteristics           | . 45 |

|    |        | 9.3.5     | Memory characteristics                     | . 47 |

|    |        | 9.3.6     | I/O port pin characteristics               | . 48 |

|    |        | 9.3.7     | Communication interfaces                   | . 55 |

|    |        | 9.3.8     | Comparator characteristics                 |      |

|    |        | 9.3.9     | EMC characteristics                        |      |

|    | 9.4    | Thermal   | characteristics                            | 62   |

| 10 | Packa  | age info  | rmation                                    | 64   |

|    | 10.1   | UFQFPI    | N32 package information                    | 64   |

|    | 10.2   | LQFP32    | 2 package information                      | 67   |

|    | 10.3   | UFQFPI    | N28 package information                    | 70   |

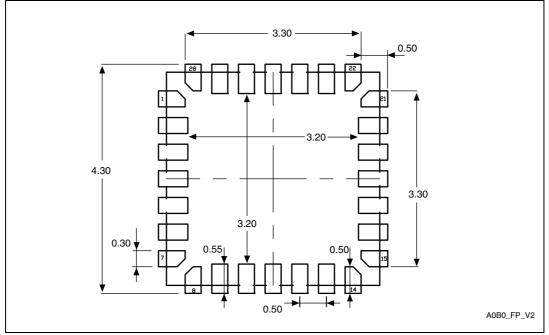

|    | 10.4   | UFQFPI    | N20 package information                    | 73   |

|    | 10.5   | TSSOP     | 20 package information                     | 76   |

| 11 | Devic  | e orderi  | ing information                            | 79   |

| 12 | STM8   | develo    | pment tools                                | 80   |

|    | 12.1   | Emulatio  | on and in-circuit debugging tools          | 80   |

|    | 12.2   | Software  | e tools                                    | 81   |

|    |        | 12.2.1    | STM8 toolset                               | . 81 |

|    |        | 12.2.2    | C and assembly toolchains                  | . 81 |

|    | 12.3   | Program   | nming tools                                | 81   |

## 1 Introduction

This datasheet provides the STM8L101x1 STM8L101x2 STM8L101x3 pinout, ordering information, mechanical and electrical device characteristics.

For complete information on the STM8L101x1 STM8L101x2 STM8L101x3 microcontroller memory, registers and peripherals, please refer to the STM8L reference manual. The STM8L101x1 STM8L101x2 STM8L101x3devices are members of the STM8L low-power 8-bit family. They are

referred to as low-density devices in the STM8L101x1 STM8L101x2 STM8L101x3 microcontroller family reference manual (RM0013) and in the STM8L Flash programming manual (PM0054).

All devices of the SM8L product line provide the following benefits:

- Reduced system cost

- Up to 8 Kbytes of low-density embedded Flash program memory including up to 2 Kbytes of data EEPROM

- High system integration level with internal clock oscillators and watchdogs.

- Smaller battery and cheaper power supplies.

- Low power consumption and advanced features

- Up to 16 MIPS at 16 MHz CPU clock frequency

- Less than 150 μA/MH, 0.8 μA in Active-halt mode, and 0.3 μA in Halt mode

- Clock gated system and optimized power management

- Short development cycles

- Application scalability across a common family product architecture with compatible pinout, memory map and modular peripherals.

- Full documentation and a wide choice of development tools

- Product longevity

- Advanced core and peripherals made in a state-of-the art technology

- Product family operating from 1.65 V to 3.6 V supply.

## 2 Description

The STM8L101x1 STM8L101x2 STM8L101x3 low-power family features the enhanced STM8 CPU core providing increased processing power (up to 16 MIPS at 16 MHz) while maintaining the advantages of a CISC architecture with improved code density, a 24-bit linear addressing space and an optimized architecture for low power operations.

The family includes an integrated debug module with a hardware interface (SWIM) which allows non-intrusive in-application debugging and ultrafast Flash programming.

All STM8L101xx microcontrollers feature low power low-voltage single-supply program Flash memory. The 8-Kbyte devices embed data EEPROM.

The STM8L101xx low power family is based on a generic set of state-of-the-art peripherals. The modular design of the peripheral set allows the same peripherals to be found in different ST microcontroller families including 32-bit families. This makes any transition to a different family very easy, and simplified even more by the use of a common set of development tools.

All STM8L low power products are based on the same architecture with the same memory mapping and a coherent pinout.

| Features              | STM8L101xx                                                                                                                                                                                                                                                      |                                                                                |                                                    |  |  |  |  |  |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|----------------------------------------------------|--|--|--|--|--|

| Flash                 | 2 Kbytes of Flash program memory                                                                                                                                                                                                                                | 8 Kbytes of Flash program<br>memory including up to<br>2 Kbytes of Data EEPROM |                                                    |  |  |  |  |  |

| RAM                   |                                                                                                                                                                                                                                                                 | 1.5 Kbytes                                                                     |                                                    |  |  |  |  |  |

| Peripheral functions  | Independent watchdog (IWDG), Auto-wakeup unit (AWU), Beep,<br>Serial peripheral interface (SPI), Inter-integrated circuit (I <sup>2</sup> C),<br>Universal synchronous / asynchronous receiver / transmitter (USART),<br>2 comparators, Infrared (IR) interface |                                                                                |                                                    |  |  |  |  |  |

| Timers                | Т                                                                                                                                                                                                                                                               | wo 16-bit timers, one 8-bit time                                               | er                                                 |  |  |  |  |  |

| Operating voltage     |                                                                                                                                                                                                                                                                 | 1.65 to 3.6 V                                                                  |                                                    |  |  |  |  |  |

| Operating temperature | -40 to                                                                                                                                                                                                                                                          | +85 °C                                                                         | -40 to +85 °C or<br>-40 to +125 °C                 |  |  |  |  |  |

| Packages              | UFQFPN20 3x3                                                                                                                                                                                                                                                    | UFQFPN28 4x 4<br>UFQFPN20 3x3<br>TSSOP20 4.4 x 6.4                             | UFQFPN28 4x4<br>UFQFPN20 3x3<br>UFQFPN32<br>LQFP32 |  |  |  |  |  |

#### Table 2. STM8L101xx device feature summary

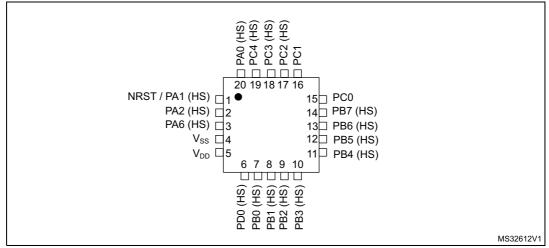

#### Figure 3. 20-pin UFQFPN package pinout for STM8L101F1U6ATR, STM8L101F2U6ATR and STM8L101F3U6ATR part numbers

1. Please refer to the warning below.

2. HS corresponds to 20 mA high sink/source capability.

3. High sink LED driver capability available on PA0. Refer to the description of the IR\_CR register in the STM8L reference manual (RM0013).

Warning: For the STM8L101F1U6ATR, STM8L101F2U6ATR and STM8L101F3U6ATR part numbers (devices with COMP\_REF pin), all ports available on 32-pin packages must be considered as active ports. To avoid spurious effects, the user has to configure them as input pull-up. A small increase in consumption (typ. < 300 μA) may occur during the power up and reset phase until these ports are properly configured.

|                   | Pi                                    | n nu    | ımb               | er                                    |                    |                                           |      |                         | Input            |                |                  | utput            |    | ,                              |                                                           |

|-------------------|---------------------------------------|---------|-------------------|---------------------------------------|--------------------|-------------------------------------------|------|-------------------------|------------------|----------------|------------------|------------------|----|--------------------------------|-----------------------------------------------------------|

| standard UFQFPN20 | UFQFPN20 with COMP_REF <sup>(1)</sup> | TSSOP20 | standard UFQFPN28 | UFQFPN28 with COMP_REF <sup>(1)</sup> | UFQFPN32 or LQFP32 | Pin name                                  | Type | floating                | ndw              | Ext. interrupt | High sink/source | Q                | dd | Main function<br>(after reset) | Alternate function                                        |

| 7                 | 7                                     | 10      | 12                | 12                                    | 13                 | PB0/TIM2_CH1/<br>COMP1_CH1 <sup>(3)</sup> | I/O  | <b>X</b> <sup>(3)</sup> | X <sup>(3)</sup> | х              | HS               | х                | х  | Port B0                        | Timer 2 - channel 1 /<br>Comparator 1 -<br>channel 1      |

| 8                 | 8                                     | 11      | 13                | 13                                    | 14                 | PB1/TIM3_CH1/<br>COMP1_CH2                | I/O  | x                       | х                | х              | HS               | x                | х  | Port B1                        | Timer 3 - channel 1 /<br>Comparator 1 -<br>channel 2      |

| 9                 | 9                                     | 12      | 14                | 14                                    | 15                 | PB2/ TIM2_CH2/<br>COMP2_CH1/              | I/O  | x                       | х                | х              | HS               | x                | х  | Port B2                        | Timer 2 - channel 2 /<br>Comparator 2 -<br>channel 1      |

| 10                | 10                                    | 13      | 15                | 15                                    | 16                 | PB3/TIM2_ETR/<br>COMP2_CH2                | I/O  | x                       | х                | х              | HS               | x                | х  | Port B3                        | Timer 2 - trigger /<br>Comparator 2 -<br>channel 2        |

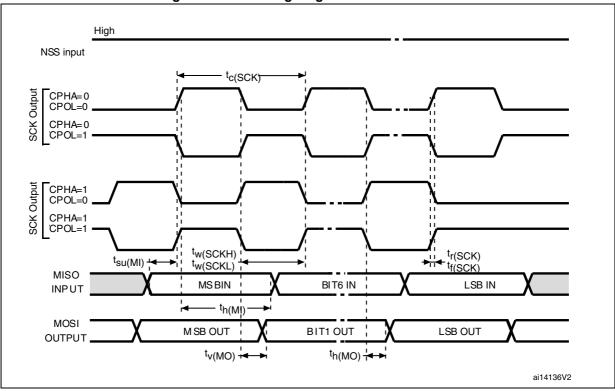

| 11                | 11                                    | 14      | 16                | 16                                    | 17                 | PB4/SPI_NSS <sup>(3)</sup>                | I/O  | <b>X</b> <sup>(3)</sup> | X <sup>(3)</sup> | х              | HS               | х                | х  | Port B4                        | SPI master/slave select                                   |

| 12                | 12                                    | 15      | 17                | 17                                    | 18                 | PB5/SPI_SCK                               | I/O  | Х                       | Х                | Х              | HS               | Х                | Х  | Port B5                        | SPI clock                                                 |

| 13                | 13                                    | 16      | 18                | 18                                    | 19                 | PB6/SPI_MOSI                              | I/O  | x                       | х                | х              | HS               | х                | х  | Port B6                        | SPI master out/ slave in                                  |

| 14                | 14                                    | 17      | 19                | 19                                    | 20                 | PB7/SPI_MISO                              | I/O  | x                       | х                | Х              | HS               | х                | х  | Port B7                        | SPI master in/ slave<br>out                               |

| -                 | -                                     | -       | 20                | 20                                    | 21                 | PD4                                       | I/O  | X                       | Х                | Х              | HS               | Х                | х  | Port D4                        | -                                                         |

| -                 | -                                     | -       | -                 | -                                     | 22                 | PD5                                       | I/O  | X                       | Х                | Х              | HS               | Х                | Х  | Port D5                        | -                                                         |

| -                 | -                                     | -       | -                 | -                                     | 23                 | PD6                                       | I/O  | X                       | Х                | Х              | HS               | Х                | Х  | Port D6                        | -                                                         |

| -                 | -                                     | -       | -                 | -                                     | 24                 | PD7                                       | I/O  | X                       | Х                | Х              | HS               | Х                | Х  | Port D7                        | -                                                         |

| 15                | 15                                    | 18      | 21                | 21                                    | 25                 | PC0/I2C_SDA                               | I/O  | X                       | -                | Х              | -                | T <sup>(4)</sup> |    | Port C0                        | I2C data                                                  |

| 16                | 16                                    | 19      | 22                | 22                                    | 26                 | PC1/I2C_SCL                               | I/O  | Х                       | -                | Х              | -                | T <sup>(4)</sup> |    | Port C1                        | I2C clock                                                 |

| 17                | 17                                    | 20      | 23                | 23                                    | 27                 | PC2/USART_RX                              | I/O  | Х                       | Х                | Х              | HS               | Х                | Х  | Port C2                        | USART receive                                             |

| 18                | 18                                    | 1       | 24                | 24                                    | 28                 | PC3/USART_TX                              | I/O  | Х                       | Х                | Х              | HS               | Х                | Х  | Port C3                        | USART transmit                                            |

| 19                | 19                                    | 2       | 25                | 25                                    | 29                 | PC4/USART_CK/<br>CCO                      | I/O  | x                       | х                | х              | HS               | х                | х  | Port C4                        | USART synchronous<br>clock / Configurable<br>clock output |

Table 4. STM8L101xx pin description (continued)

|                              | Table 7. General hardware register map (continued) |                             |                                        |                 |  |  |  |  |  |

|------------------------------|----------------------------------------------------|-----------------------------|----------------------------------------|-----------------|--|--|--|--|--|

| Address                      | Block                                              | Register label              | Register name                          | Reset<br>status |  |  |  |  |  |

| 0x00 5280                    |                                                    | TIM3_CR1                    | TIM3 control register 1                | 0x00            |  |  |  |  |  |

| 0x00 5281                    |                                                    | TIM3_CR2                    | TIM3 control register 2                | 0x00            |  |  |  |  |  |

| 0x00 5282                    |                                                    | TIM3_SMCR                   | TIM3 slave mode control register       | 0x00            |  |  |  |  |  |

| 0x00 5283                    |                                                    | TIM3_ETR                    | TIM3 external trigger register         | 0x00            |  |  |  |  |  |

| 0x00 5284                    |                                                    | TIM3_IER                    | TIM3 interrupt enable register         | 0x00            |  |  |  |  |  |

| 0x00 5285                    |                                                    | TIM3_SR1                    | TIM3 status register 1                 | 0x00            |  |  |  |  |  |

| 0x00 5286                    |                                                    | TIM3_SR2                    | TIM3 status register 2                 | 0x00            |  |  |  |  |  |

| 0x00 5287                    |                                                    | TIM3_EGR                    | TIM3 event generation register         | 0x00            |  |  |  |  |  |

| 0x00 5288                    |                                                    | TIM3_CCMR1                  | TIM3 capture/compare mode register 1   | 0x00            |  |  |  |  |  |

| 0x00 5289                    |                                                    | TIM3_CCMR2                  | TIM3 capture/compare mode register 2   | 0x00            |  |  |  |  |  |

| 0x00 528A                    | ТІМЗ                                               | TIM3_CCER1                  | TIM3 capture/compare enable register 1 | 0x00            |  |  |  |  |  |

| 0x00 528B                    | TIMO                                               | TIM3_CNTRH                  | TIM3 counter high                      | 0x00            |  |  |  |  |  |

| 0x00 528C                    |                                                    | TIM3_CNTRL TIM3 counter low |                                        |                 |  |  |  |  |  |

| 0x00 528D                    |                                                    | TIM3_PSCR                   | TIM3 prescaler register                | 0x00            |  |  |  |  |  |

| 0x00 528E                    |                                                    | TIM3_ARRH                   | TIM3 auto-reload register high         | 0xFF            |  |  |  |  |  |

| 0x00 528F                    |                                                    | TIM3_ARRL                   | TIM3 auto-reload register low          | 0xFF            |  |  |  |  |  |

| 0x00 5290                    |                                                    | TIM3_CCR1H                  | TIM3 capture/compare register 1 high   | 0x00            |  |  |  |  |  |

| 0x00 5291                    |                                                    | TIM3_CCR1L                  | TIM3 capture/compare register 1 low    | 0x00            |  |  |  |  |  |

| 0x00 5292                    |                                                    | TIM3_CCR2H                  | TIM3 capture/compare register 2 high   | 0x00            |  |  |  |  |  |

| 0x00 5293                    |                                                    | TIM3_CCR2L                  | TIM3 capture/compare register 2 low    | 0x00            |  |  |  |  |  |

| 0x00 5294                    |                                                    | TIM3_BKR                    | TIM3 break register                    | 0x00            |  |  |  |  |  |

| 0x00 5295                    |                                                    | TIM3_OISR                   | TIM3 output idle state register        | 0x00            |  |  |  |  |  |

| 0x00 5296<br>to<br>0x00 52DF |                                                    | F                           | Reserved area (74 bytes)               |                 |  |  |  |  |  |

| 0x00 52E0                    |                                                    | TIM4_CR1                    | TIM4 control register 1                | 0x00            |  |  |  |  |  |

| 0x00 52E1                    |                                                    | TIM4_CR2                    | TIM4 control register 2                | 0x00            |  |  |  |  |  |

| 0x00 52E2                    |                                                    | TIM4_SMCR                   | TIM4 Slave mode control register       | 0x00            |  |  |  |  |  |

| 0x00 52E3                    |                                                    | TIM4_IER                    | TIM4 interrupt enable register         | 0x00            |  |  |  |  |  |

| 0x00 52E4                    | TIM4                                               | TIM4_SR1                    | TIM4 Status register 1                 | 0x00            |  |  |  |  |  |

| 0x00 52E5                    |                                                    | TIM4_EGR                    | TIM4 event generation register         | 0x00            |  |  |  |  |  |

| 0x00 52E6                    |                                                    | TIM4_CNTR                   | TIM4 counter                           | 0x00            |  |  |  |  |  |

| 0x00 52E7                    |                                                    | TIM4_PSCR                   | TIM4 prescaler register                | 0x00            |  |  |  |  |  |

| 0x00 52E8                    |                                                    | TIM4_ARR                    | TIM4 auto-reload register low          | 0xFF            |  |  |  |  |  |

Table 7. General hardware register map (continued)

6 Interrupt vector mapping

|            | Table 9. Interrupt mapping |                                   |                             |                                       |                                      |                                      |                         |  |  |  |  |

|------------|----------------------------|-----------------------------------|-----------------------------|---------------------------------------|--------------------------------------|--------------------------------------|-------------------------|--|--|--|--|

| IRQ<br>No. | Source<br>block            | Description                       | Wakeup<br>from Halt<br>mode | Wakeup<br>from<br>Active-halt<br>mode | Wakeup<br>from Wait<br>(WFI<br>mode) | Wakeup<br>from Wait<br>(WFE<br>mode) | Vector<br>address       |  |  |  |  |

| -          | RESET                      | Reset                             | Yes                         | Yes                                   | Yes                                  | Yes                                  | 0x00 8000               |  |  |  |  |

| -          | TRAP                       | Software interrupt                | -                           | -                                     | -                                    | -                                    | 0x00 8004               |  |  |  |  |

| 0          | -                          | Reserved                          | -                           | -                                     | -                                    | -                                    | 0x00 8008               |  |  |  |  |

| 1          | FLASH                      | EOP/WR_PG_DIS                     | -                           | -                                     | Yes                                  | Yes <sup>(1)</sup>                   | 0x00 800C               |  |  |  |  |

| 2-3        | -                          | Reserved                          | -                           | -                                     | -                                    | -                                    | 0x00 8010<br>-0x00 8017 |  |  |  |  |

| 4          | AWU                        | Auto wakeup from Halt             | -                           | Yes                                   | Yes                                  | Yes <sup>(1)</sup>                   | 0x00 8018               |  |  |  |  |

| 5          | -                          | Reserved                          | -                           | -                                     | -                                    | -                                    | 0x00 801C               |  |  |  |  |

| 6          | EXTIB                      | External interrupt port B         | Yes                         | Yes                                   | Yes                                  | Yes                                  | 0x00 8020               |  |  |  |  |

| 7          | EXTID                      | External interrupt port D         | Yes                         | Yes                                   | Yes                                  | Yes                                  | 0x00 8024               |  |  |  |  |

| 8          | EXTI0                      | External interrupt 0              | Yes                         | Yes                                   | Yes                                  | Yes                                  | 0x00 8028               |  |  |  |  |

| 9          | EXTI1                      | External interrupt 1              | Yes                         | Yes                                   | Yes                                  | Yes                                  | 0x00 802C               |  |  |  |  |

| 10         | EXTI2                      | External interrupt 2              | Yes                         | Yes                                   | Yes                                  | Yes                                  | 0x00 8030               |  |  |  |  |

| 11         | EXTI3                      | External interrupt 3              | Yes                         | Yes                                   | Yes                                  | Yes                                  | 0x00 8034               |  |  |  |  |

| 12         | EXTI4                      | External interrupt 4              | Yes                         | Yes                                   | Yes                                  | Yes                                  | 0x00 8038               |  |  |  |  |

| 13         | EXTI5                      | External interrupt 5              | Yes                         | Yes                                   | Yes                                  | Yes                                  | 0x00 803C               |  |  |  |  |

| 14         | EXTI6                      | External interrupt 6              | Yes                         | Yes                                   | Yes                                  | Yes                                  | 0x00 8040               |  |  |  |  |

| 15         | EXTI7                      | External interrupt 7              | Yes                         | Yes                                   | Yes                                  | Yes                                  | 0x00 8044               |  |  |  |  |

| 16         | -                          | Reserved                          | -                           | -                                     | -                                    | -                                    | 0x00 8048               |  |  |  |  |

| 17         | -                          | Reserved                          | -                           | -                                     | -                                    | -                                    | 0x00 804C<br>-0x00 804F |  |  |  |  |

| 18         | COMP                       | Comparators                       | -                           | -                                     | Yes                                  | Yes <sup>(1)</sup>                   | 0x00 8050               |  |  |  |  |

| 19         | TIM2                       | Update<br>/Overflow/Trigger/Break | -                           | -                                     | Yes                                  | Yes                                  | 0x00 8054               |  |  |  |  |

| 20         | TIM2                       | Capture/Compare                   | -                           | -                                     | Yes                                  | Yes                                  | 0x00 8058               |  |  |  |  |

| 21         | TIM3                       | Update /Overflow/Break            | -                           | -                                     | Yes                                  | Yes <sup>(1)</sup>                   | 0x00 805C               |  |  |  |  |

| 22         | TIM3                       | Capture/Compare                   | -                           | -                                     | Yes                                  | Yes <sup>(1)</sup>                   | 0x00 8060               |  |  |  |  |

| 23-<br>24  | -                          | Reserved                          | -                           | -                                     | -                                    | -                                    | 0x00 8064-<br>0x00 806B |  |  |  |  |

| 25         | TIM4                       | Update /Trigger                   | -                           | -                                     | Yes                                  | Yes <sup>(1)</sup>                   | 0x00 806C               |  |  |  |  |

| 26         | SPI                        | End of Transfer                   | Yes                         | Yes                                   | Yes                                  | Yes <sup>(1)</sup>                   | 0x00 8070               |  |  |  |  |

Table 9. Interrupt mapping

## 7 Option bytes

Option bytes contain configurations for device hardware features as well as the memory protection of the device. They are stored in a dedicated row of the memory.

All option bytes can be modified only in ICP mode (with SWIM) by accessing the EEPROM address. See *Table 10* for details on option byte addresses.

Refer to the STM8L Flash programming manual (PM0054) and STM8 SWIM and Debug Manual (UM0470) for information on SWIM programming procedures.

| Addr.  | Ontion nome                       | Option        | • |                            |    |        |   |   |               | Option bits |                    |  |  |  |  |  |  |

|--------|-----------------------------------|---------------|---|----------------------------|----|--------|---|---|---------------|-------------|--------------------|--|--|--|--|--|--|

|        | Option name                       | byte<br>No.   | 7 | 6                          | 5  | 4      | 3 | 2 | 1             | 0           | default<br>setting |  |  |  |  |  |  |

| 0x4800 | Read-out<br>protection<br>(ROP)   | OPT1          |   | ROP[7:0]                   |    |        |   |   |               |             | 0x00               |  |  |  |  |  |  |

| 0x4807 | -                                 | -             |   | Must be programmed to 0x00 |    |        |   |   |               |             |                    |  |  |  |  |  |  |

| 0x4802 | UBC (User<br>Boot code size)      | OPT2          |   | UBC[7:0]                   |    |        |   |   |               |             |                    |  |  |  |  |  |  |

| 0x4803 | DATASIZE                          | OPT3          |   | DATASIZE[7:0]              |    |        |   |   |               |             | 0x00               |  |  |  |  |  |  |

| 0x4808 | Independent<br>watchdog<br>option | OPT4<br>[1:0] |   |                            | Re | served |   |   | IWDG<br>_HALT | IWDG<br>_HW | 0x00               |  |  |  |  |  |  |

#### Table 11. Option byte description

| OPT1 | <b>ROP[7:0]</b> <i>Memory readout protection (ROP)</i><br>0xAA: Enable readout protection (write access via SWIM protocol)<br>Refer to <i>Read-out protection</i> section in the STM8L reference manual<br>(RM0013) for details.                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| OPT2 | <ul> <li>UBC[7:0] Size of the user boot code area</li> <li>0x00: no UBC</li> <li>0x01-0x02: UBC contains only the interrupt vectors.</li> <li>0x03: Page 0 and 1 reserved for the interrupt vectors. Page 2 is available to store user boot code. Memory is write protected</li> <li></li> <li>0x7F - Page 0 to 126 reserved for UBC, memory is write protected</li> <li>Refer to User boot area (UBC) section in the STM8L reference manual (RM0013) for more details.</li> <li>UBC[7] is forced to 0 internally by HW.</li> </ul> |  |  |  |  |  |

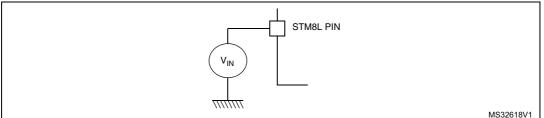

## 9.1.5 Pin input voltage

The input voltage measurement on a pin of the device is described in Figure 10.

#### Figure 10. Pin input voltage

## 9.2 Absolute maximum ratings

Stresses above the absolute maximum ratings listed in *Table 13: Voltage characteristics*, *Table 14: Current characteristics* and *Table 15: Thermal characteristics* may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability. The device mission profile is compliant with the JEDEC JESD47 qualification standard; extended mission profiles are available on demand.

| Symbol                            | Ratings                                                            | Min                                      | Max                   | Unit |

|-----------------------------------|--------------------------------------------------------------------|------------------------------------------|-----------------------|------|

| V <sub>DD</sub> - V <sub>SS</sub> | External supply voltage                                            | -0.3                                     | 4.0                   |      |

| V <sub>IN</sub>                   | Input voltage on true open drain pins (PC0 and PC1) <sup>(1)</sup> | V <sub>SS</sub> -0.3                     | V <sub>DD</sub> + 4.0 | v    |

|                                   | Input voltage on any other pin <sup>(2)</sup>                      | V <sub>SS</sub> -0.3                     | 4.0                   |      |

| V <sub>ESD</sub>                  | Electrostatic discharge voltage                                    | see Absolut<br>ratings (electri<br>on pa | • •                   | -    |

#### Table 13. Voltage characteristics

1. Positive injection is not possible on these I/Os.  $V_{\rm IN}$  maximum must always be respected.  $I_{\rm INJ(PIN)}$  must never be exceeded. A negative injection is induced by  $V_{\rm IN}{<}V_{SS}$ .

I<sub>INJ(PIN)</sub> must never be exceeded. This is implicitly insured if V<sub>IN</sub> maximum is respected. If V<sub>IN</sub> maximum cannot be respected, the injection current must be limited externally to the I<sub>INJ(PIN)</sub> value. A positive injection is induced by V<sub>IN</sub>>V<sub>DD</sub> while a negative injection is induced by V<sub>IN</sub><V<sub>SS</sub>.

## 9.3 Operating conditions

Subject to general operating conditions for  $V_{\text{DD}}$  and  $T_{\text{A}}.$

## 9.3.1 General operating conditions

| Symbol                             | Parameter                                                            | Conditions                                            | Min  | Мах | Unit |  |

|------------------------------------|----------------------------------------------------------------------|-------------------------------------------------------|------|-----|------|--|

| f <sub>MASTER</sub> <sup>(1)</sup> | Master clock frequency                                               | 1.65 V ≤V <sub>DD</sub> < 3.6 V                       | 2    | 16  | MHz  |  |

| V <sub>DD</sub>                    | Standard operating voltage                                           | -                                                     | 1.65 | 3.6 | V    |  |

|                                    |                                                                      | LQFP32                                                | -    | 288 |      |  |

|                                    |                                                                      | UFQFPN32                                              | -    | 288 |      |  |

|                                    | Power dissipation at T <sub>A</sub> = 85 °C<br>for suffix 6 devices  | UFQFPN28                                              | _    | 250 |      |  |

|                                    |                                                                      | TSSOP20                                               | -    | 181 |      |  |

| D (2)                              |                                                                      | UFQFPN20                                              | -    | 196 |      |  |

| P <sub>D</sub> <sup>(2)</sup>      |                                                                      | LQFP32                                                | -    | 83  | mW   |  |

|                                    |                                                                      | UFQFPN32                                              | -    | 185 |      |  |

|                                    | Power dissipation at T <sub>A</sub> = 125 °C<br>for suffix 3 devices | UFQFPN28                                              | -    | 62  |      |  |

|                                    |                                                                      | TSSOP20                                               | -    | 45  |      |  |

|                                    |                                                                      | UFQFPN20                                              | -    | 49  |      |  |

| Ŧ                                  | T                                                                    | 1.65 V ≤V <sub>DD</sub> < 3.6 V<br>(6 suffix version) | -40  | 85  | - °C |  |

| T <sub>A</sub>                     | Temperature range                                                    | 1.65 V ≤V <sub>DD</sub> < 3.6 V<br>(3 suffix version) | -40  | 125 |      |  |

| т                                  |                                                                      | -40 °C ≤T <sub>A</sub> ≤85 °C<br>(6 suffix version)   | - 40 | 105 | °C   |  |

| Τ <sub>J</sub>                     | Junction temperature range                                           | -40 °C ≤T <sub>A</sub> ≤125 °C<br>(3 suffix version)  | -40  | 130 | °C   |  |

## Table 16. General operating conditions

1.  $f_{MASTER} = f_{CPU}$

2. To calculate  $P_{Dmax}(T_A)$  use the formula given in thermal characteristics  $P_{Dmax}=(T_{Jmax} - T_A)/\Theta_{JA}$  with  $T_{Jmax}$  in this table and  $\Theta_{JA}$  in table "Thermal characteristics"

| Symbol           | Parameter                                                                                  | Conditions                                      | Min                   | Тур | Max<br>(1) | Unit    |

|------------------|--------------------------------------------------------------------------------------------|-------------------------------------------------|-----------------------|-----|------------|---------|

| 1                | Programming/ erasing consumption                                                           | T <sub>A</sub> =+25 °C, V <sub>DD</sub> = 3.0 V | -                     | 0.7 | -          | mA      |

| Iprog            |                                                                                            | T <sub>A</sub> =+25 °C, V <sub>DD</sub> = 1.8 V | -                     | 0.7 | -          | ШA      |

|                  | Data retention (program memory)<br>after 10k erase/write cycles<br>at $T_A = +85$ °C       | T <sub>RET</sub> = 55 °C                        | 20 <sup>(1)</sup>     | -   | -          |         |

| t <sub>RET</sub> | Data retention (data memory)<br>after 10k erase/write cycles<br>at T <sub>A</sub> = +85 °C | T <sub>RET</sub> = 55 °C                        | 20 <sup>(1)</sup>     | -   | -          | years   |

|                  | Data retention (data memory)<br>after 300k erase/write cycles<br>at $T_A = +125$ °C        | T <sub>RET</sub> = 85 °C                        | 1 <sup>(1)</sup>      | -   | -          |         |

| Ν                | Erase/write cycles (program memory)                                                        | See notes <sup>(1)(2)</sup>                     | 10 <sup>(1)</sup>     | -   | -          | kovolca |

| N <sub>RW</sub>  | Erase/write cycles (data memory)                                                           | See notes <sup>(1)(3)</sup>                     | 300 <sup>(1)(4)</sup> | -   | -          | kcycles |

| Table 25. | Flash | program memory | (continued) |

|-----------|-------|----------------|-------------|

|-----------|-------|----------------|-------------|

1. Data based on characterization results, not tested in production.

2. Retention guaranteed after cycling is 10 years at 55 °C.

3. Retention guaranteed after cycling is 1 year at 55 °C.

4. Data based on characterization performed on the whole data memory (2 Kbytes).

## 9.3.6 I/O port pin characteristics

### **General characteristics**

Subject to general operating conditions for  $V_{DD}$  and  $T_A$  unless otherwise specified. All unused pins must be kept at a fixed voltage: using the output mode of the I/O for example or an external pull-up or pull-down resistor.

| Symbol           | Parameter                               | Conditions                                    | Min                    | Тур | Мах                   | Unit |

|------------------|-----------------------------------------|-----------------------------------------------|------------------------|-----|-----------------------|------|

| V                | Input low lovel veltage <sup>(2)</sup>  | Standard I/Os                                 | V <sub>SS</sub> -0.3   | -   | 0.3 x V <sub>DD</sub> | v    |

| V <sub>IL</sub>  | Input low level voltage <sup>(2)</sup>  | True open drain I/Os                          | V <sub>SS</sub> -0.3   | -   | 0.3 x V <sub>DD</sub> | v    |

|                  |                                         | Standard I/Os                                 | 0.70 x V <sub>DD</sub> | -   | V <sub>DD</sub> +0.3  | V    |

| V <sub>IH</sub>  | Input high level voltage <sup>(2)</sup> | True open drain I/Os<br>V <sub>DD</sub> < 2 V | 0.70 x V <sub>DD</sub> | -   | 5.2                   |      |

|                  |                                         | True open drain I/Os $V_{DD} \ge 2 V$         | 0.70 X V <sub>DD</sub> |     | 5.5                   |      |

| V                | Schmitt trigger voltage hysteresis (3)  | Standard I/Os                                 | -                      | 200 | -                     | mV   |

| V <sub>hys</sub> |                                         | True open drain I/Os                          | -                      | 250 | -                     |      |

| Table 26. I/O static characteristics (1) | ) |

|------------------------------------------|---|

|------------------------------------------|---|

### **Output driving current**

Subject to general operating conditions for  $V_{DD}$  and  $T_A$  unless otherwise specified.

| l/O<br>Type                    | Symbol                         | Parameter                                | Conditions                                           | Min                   | Мах  | Unit |

|--------------------------------|--------------------------------|------------------------------------------|------------------------------------------------------|-----------------------|------|------|

|                                |                                |                                          | I <sub>IO</sub> = +2 mA,<br>V <sub>DD</sub> = 3.0 V  | -                     | 0.45 | ۷    |

|                                | V <sub>OL</sub> <sup>(1)</sup> | Output low level voltage for an I/O pin  | I <sub>IO</sub> = +2 mA,<br>V <sub>DD</sub> = 1.8 V  | -                     | 0.45 | V    |

| dard                           |                                |                                          | I <sub>IO</sub> = +10 mA,<br>V <sub>DD</sub> = 3.0 V | -                     | 1.2  | V    |

| Standard                       |                                |                                          | I <sub>IO</sub> = -2 mA,<br>V <sub>DD</sub> = 3.0 V  | V <sub>DD</sub> -0.45 | -    | V    |

| V <sub>OH</sub> <sup>(2)</sup> | V <sub>OH</sub> <sup>(2)</sup> | Output high level voltage for an I/O pin | I <sub>IO</sub> = -1 mA,<br>V <sub>DD</sub> = 1.8 V  | V <sub>DD</sub> -0.45 | -    | V    |

|                                |                                |                                          | I <sub>IO</sub> = -10 mA,<br>V <sub>DD</sub> = 3.0 V | V <sub>DD</sub> -1.2  | -    | V    |

| Table 27. Output | driving | current | (High | sink ports) |

|------------------|---------|---------|-------|-------------|

|------------------|---------|---------|-------|-------------|

1. The I<sub>IO</sub> current sunk must always respect the absolute maximum rating specified in *Table 14* and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VSS</sub>.

2. The I<sub>IQ</sub> current sourced must always respect the absolute maximum rating specified in *Table 14* and the sum of I<sub>IQ</sub> (I/O ports and control pins) must not exceed I<sub>VDD</sub>.

| l/O<br>Type                          | Symbol                                  | Parameter                                           | Conditions                                          | Min  | Мах  | Unit |

|--------------------------------------|-----------------------------------------|-----------------------------------------------------|-----------------------------------------------------|------|------|------|

| drain                                | V <sup>(1)</sup>                        | (1) Output low lowely of the set for any 1/O min    | I <sub>IO</sub> = +3 mA,<br>V <sub>DD</sub> = 3.0 V | -    | 0.45 | V    |

| pundo V <sub>OL</sub> <sup>(1)</sup> | Output low level voltage for an I/O pin | I <sub>IO</sub> = +1 mA,<br>V <sub>DD</sub> = 1.8 V | _                                                   | 0.45 | ۷    |      |

#### Table 28. Output driving current (true open drain ports)

1. The I<sub>IO</sub> current sunk must always respect the absolute maximum rating specified in *Table 14* and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VSS</sub>.

| l/O<br>Type | Symbol                         | Parameter                               | Conditions                                           | Min | Max | Unit |

|-------------|--------------------------------|-----------------------------------------|------------------------------------------------------|-----|-----|------|

| R           | V <sub>OL</sub> <sup>(1)</sup> | Output low level voltage for an I/O pin | I <sub>IO</sub> = +20 mA,<br>V <sub>DD</sub> = 2.0 V | -   | 0.9 | ۷    |

#### Table 29. Output driving current (PA0 with high sink LED driver capability)

1. The I<sub>IO</sub> current sunk must always respect the absolute maximum rating specified in *Table 14* and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VSS</sub>.

1. Measurement points are done at CMOS levels:  $0.3V_{DD}$  and  $0.7V_{DD}$ .

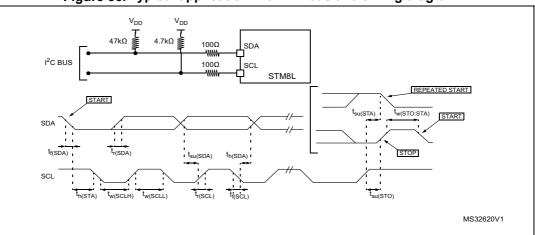

### Inter IC control interface (I2C)

Subject to general operating conditions for  $V_{\text{DD}},\,f_{\text{MASTER}},$  and  $T_{\text{A}}$  unless otherwise specified.

The STM8L I<sup>2</sup>C interface meets the requirements of the Standard I<sup>2</sup>C communication protocol described in the following table with the restriction mentioned below:

Refer to I/O port characteristics for more details on the input/output alternate function characteristics (SDA and SCL).

| Symbol                                     | Parameter                               |                    | rd mode<br>:C      | Fast mo            | Unit               |    |

|--------------------------------------------|-----------------------------------------|--------------------|--------------------|--------------------|--------------------|----|

|                                            |                                         | Min <sup>(2)</sup> | Max <sup>(2)</sup> | Min <sup>(2)</sup> | Max <sup>(2)</sup> |    |

| t <sub>w(SCLL)</sub>                       | SCL clock low time                      | 4.7                | -                  | 1.3                | -                  |    |

| t <sub>w(SCLH)</sub>                       | SCL clock high time                     | 4.0                | -                  | 0.6                | -                  | μs |

| t <sub>su(SDA)</sub>                       | SDA setup time                          | 250                | -                  | 100                | -                  |    |

| t <sub>h(SDA)</sub>                        | SDA data hold time                      | 0 (3)              | -                  | 0 (4)              | 900 <sup>(3)</sup> |    |

| t <sub>r(SDA)</sub><br>t <sub>r(SCL)</sub> | SDA and SCL rise time                   | -                  | 1000               | -                  | 300                | ns |

| t <sub>f(SDA)</sub><br>t <sub>f(SCL)</sub> | SDA and SCL fall time                   | -                  | 300                | -                  | 300                |    |

| t <sub>h(STA)</sub>                        | START condition hold time               | 4.0                | -                  | 0.6                | -                  |    |

| t <sub>su(STA)</sub>                       | Repeated START condition setup time     | 4.7                | -                  | 0.6                | -                  | μs |

| t <sub>su(STO)</sub>                       | STOP condition setup time               | 4.0                | -                  | 0.6                | -                  | μs |

| t <sub>w(STO:STA)</sub>                    | STOP to START condition time (bus free) | 4.7                | -                  | 1.3                | -                  | μs |

| Cb                                         | Capacitive load for each bus line       | -                  | 400                | -                  | 400                | pF |

| Table 32 | . I2C | characteristics |

|----------|-------|-----------------|

|----------|-------|-----------------|

1. f<sub>SCK</sub> must be at least 8 MHz to achieve max fast I<sup>2</sup>C speed (400 kHz).

2. Data based on standard I<sup>2</sup>C protocol requirement, not tested in production.

3. The maximum hold time of the START condition has only to be met if the interface does not stretch the low period of SCL signal.

4. The device must internally provide a hold time of at least 300 ns for the SDA signal in order to bridge the undefined region of the falling edge of SCL).

Note:

For speeds around 200 kHz, achieved speed can have  $\pm$ 5% tolerance For other speed ranges, achieved speed can have  $\pm$ 2% tolerance The above variations depend on the accuracy of the external components used.

Figure 36. Typical application with I2C bus and timing diagram<sup>1)</sup>

1. Measurement points are done at CMOS levels: 0.3 x  $V_{\text{DD}}$  and 0.7 x  $V_{\text{DD}}$

#### 9.3.8 **Comparator characteristics**

| Symbol                                                          | Parameter                                       | Conditions                                                          | Min <sup>(1)</sup> | Тур | Max <sup>(1)</sup>    | Unit |

|-----------------------------------------------------------------|-------------------------------------------------|---------------------------------------------------------------------|--------------------|-----|-----------------------|------|

| V <sub>IN(COMP_REF)</sub>                                       | Comparator external reference                   | -                                                                   | -0.1               | -   | V <sub>DD</sub> -1.25 | V    |

| V <sub>IN</sub>                                                 | Comparator input voltage range                  | -                                                                   | -0.25              | -   | V <sub>DD</sub> +0.25 | V    |

| V <sub>offset</sub> <sup>(2)</sup>                              | Comparator offset error -                       |                                                                     | -                  | -   | ±20                   | mV   |

| t <sub>START</sub>                                              | Startup time (after BIAS_EN)                    | -                                                                   | -                  | -   | 3 <sup>(1)</sup>      | μs   |

|                                                                 | Analog comparator consumption                   | -                                                                   | -                  | -   | 25 <sup>(1)</sup>     | μA   |

| I <sub>DD(COMP)</sub>                                           | Analog comparator consumption during power-down | -                                                                   | -                  | -   | 60 <sup>(1)</sup>     | nA   |

| t <sub>propag</sub> <sup>(2)</sup> Comparator propagation delay |                                                 | 100-mV input step<br>with 5-mV overdrive,<br>input rise time = 1 ns | -                  | -   | 2 <sup>(1)</sup>      | μs   |

Table 33. Comparator characteristics

1. Data guaranteed by design, not tested in production.

The comparator accuracy depends on the environment. In particular, the following cases may reduce the accuracy of the 2. comparator and must be avoided:

- Negative injection current on the I/Os close to the comparator inputs

Switching on I/Os close to the comparator inputs

Negative injection current on not used comparator input.

Switching with a high dV/dt on not used comparator input.

These phenomena are even more critical when a big external serial resistor is added on the inputs.

## 10 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK® packages, depending on their level of environmental compliance. ECOPACK® specifications, grade definitions and product status are available at: *www.st.com*. ECOPACK® is an ST trademark.

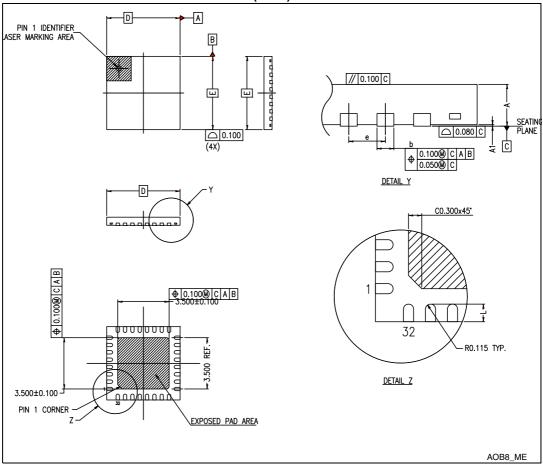

## 10.1 UFQFPN32 package information

Figure 37. UFQFPN32 - 32-lead ultra thin fine pitch quad flat no-lead package outline (5 x 5)

1. Drawing is not to scale.

2. All leads/pads should be soldered to the PCB to improve the lead/pad solder joint life.

3. There is an exposed die pad on the underside of the UFQFPN package. It is recommended to connect and solder this back-side pad to PCB ground.

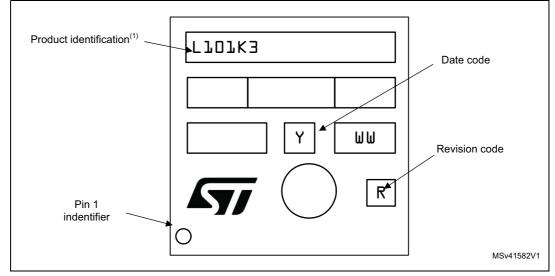

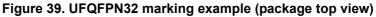

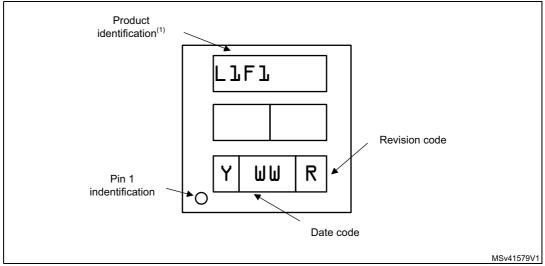

### **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

| package mechanical data |       |       |       |                       |        |        |

|-------------------------|-------|-------|-------|-----------------------|--------|--------|

| Dim                     | mm    |       |       | inches <sup>(1)</sup> |        |        |

| Dim.                    | Min   | Тур   | Max   | Min                   | Тур    | Мах    |

| A                       | 0.500 | 0.550 | 0.600 | 0.0197                | 0.0217 | 0.0236 |

| A1                      | 0     | 0.020 | 0.050 | 0                     | 0.0008 | 0.002  |

| A3                      | -     | 0.152 | -     | -                     | 0.0060 | -      |

| b                       | 0.180 | 0.250 | 0.300 | 0.0071                | 0.0098 | 0.0118 |

| D                       | -     | 4.000 | -     | -                     | 0.1575 | -      |

| E                       | -     | 4.000 | -     | -                     | 0.1575 | -      |

| е                       | -     | 0.500 | -     | -                     | 0.0197 | -      |

| L1                      | 0.250 | 0.350 | 0.450 | 0.0098                | 0.0138 | 0.0177 |

| L2                      | 0.300 | 0.400 | 0.500 | 0.0118                | 0.0157 | 0.0197 |

| ddd                     | -     | 0.080 | -     | -                     | 0.0031 | -      |

| -                       |       |       | Numbe | r of pins             |        | •      |

| Ν                       |       |       | 2     | 28                    |        |        |

## Table 41. UFQFPN28 - 28-lead ultra thin fine pitch quad flat no-lead package (4 x 4),package mechanical data

1. Values in inches are converted from mm and rounded to 4 decimal digits.

## Figure 44. UFQFPN28 recommended footprint

1. Dimensions are expressed in millimeters.

### **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

1. Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                 |

|-------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 18-Dec-2014 | 14       | <ul> <li>Updated:</li> <li>Figure 46: UFQFPN20 - 20-lead ultra thin fine pitch quad flat package outline (3x3 mm),</li> <li>Table 42: UFQFPN20 - 20-lead ultra thin fine pitch quad flat package (3 x 3 mm) mechanical data.</li> </ul>                                                                                                                                 |

| 02-Aug-2016 | 15       | Added:<br>- Figure 39: UFQFPN32 marking example (package top view)<br>- Figure 42: LQFP32 marking example (package top view)<br>- Figure 45: UFQFPN28 marking example (package top view)<br>- Figure 48: UFQFPN20 marking example (package top view)<br>- Figure 51: TSSOP20 marking example (package top view)<br>Updated:<br>- Section 9.2: Absolute maximum ratings. |

| Table 44 | Document | revision  | history | (continued) | ١ |

|----------|----------|-----------|---------|-------------|---|

|          | Document | 164131011 | matory  | (continueu) |   |