# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | STM8                                                                   |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 16MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                      |

| Peripherals                | Infrared, POR, PWM, WDT                                                |

| Number of I/O              | 18                                                                     |

| Program Memory Size        | 8KB (8K x 8)                                                           |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | 2K x 8                                                                 |

| RAM Size                   | 1.5K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 3.6V                                                           |

| Data Converters            | -                                                                      |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 20-TSSOP (0.173", 4.40mm Width)                                        |

| Supplier Device Package    | 20-TSSOP                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm8l101f3p6tr |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Contents

| 1 | Intro | duction                                            |

|---|-------|----------------------------------------------------|

| 2 | Desc  | ription                                            |

| 3 | Prod  | uct overview                                       |

|   | 3.1   | Central processing unit STM811                     |

|   | 3.2   | Development tools                                  |

|   | 3.3   | Single wire data interface (SWIM) and debug module |

|   | 3.4   | Interrupt controller                               |

|   | 3.5   | Memory                                             |

|   | 3.6   | Low power modes                                    |

|   | 3.7   | Voltage regulators                                 |

|   | 3.8   | Clock control                                      |

|   | 3.9   | Independent watchdog 12                            |

|   | 3.10  | Auto-wakeup counter 13                             |

|   | 3.11  | General purpose and basic timers                   |

|   | 3.12  | Beeper                                             |

|   | 3.13  | Infrared (IR) interface                            |

|   | 3.14  | Comparators                                        |

|   | 3.15  | USART                                              |

|   | 3.16  | SPI 14                                             |

|   | 3.17  | I <sup>2</sup> C 14                                |

| 4 | Pin d | lescription                                        |

| 5 | Mem   | ory and register map                               |

| 6 | Inter | rupt vector mapping                                |

| 7 | Optic | on bytes                                           |

| 8 | Uniq  | ue ID                                              |

# List of figures

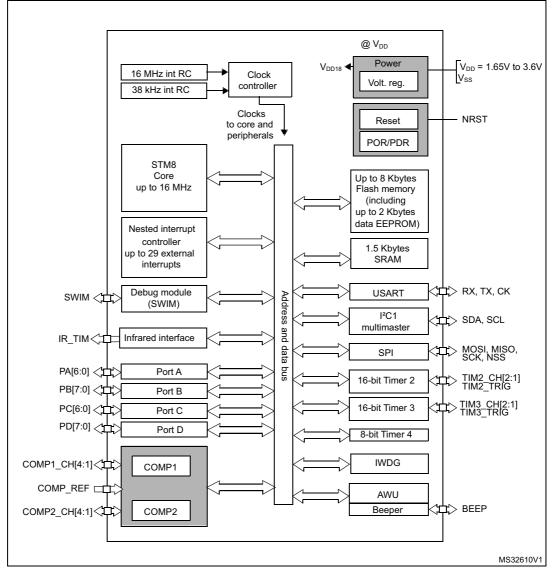

| Figure 1.                | STM8L101xx device block diagram                                                        | . 10 |

|--------------------------|----------------------------------------------------------------------------------------|------|

| Figure 2.                | Standard 20-pin UFQFPN package pinout                                                  | . 15 |

| Figure 3.                | 20-pin UFQFPN package pinout for STM8L101F1U6ATR,                                      |      |

|                          | STM8L101F2U6ATR and STM8L101F3U6ATR part numbers.                                      | . 16 |

| Figure 4.                | 20-pin TSSOP package pinout                                                            | . 17 |

| Figure 5.                | Standard 28-pin UFQFPN package pinout                                                  | . 17 |

| Figure 6.                | 28-pin UFQFPN package pinout for STM8L101G3U6ATR and                                   |      |

| -                        | STM8L101G2U6ATR part numbers                                                           | . 18 |

| Figure 7.                | 32-pin package pinout                                                                  | . 19 |

| Figure 8.                | Memory map.                                                                            |      |

| Figure 9.                | Pin loading conditions.                                                                | . 37 |

| Figure 10.               | Pin input voltage                                                                      | . 38 |

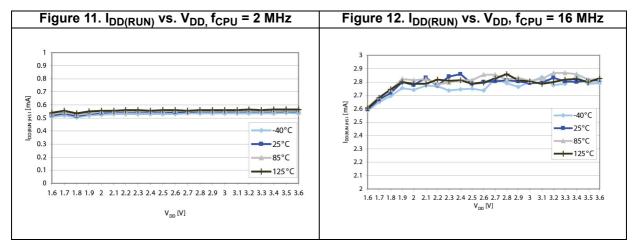

| Figure 11.               | IDD(RUN) vs. VDD, fCPU = 2 MHz                                                         | . 42 |

| Figure 12.               | IDD(RUN) vs. VDD, fCPU = 16 MHz                                                        | . 42 |

| Figure 13.               | IDD(WAIT) vs. VDD, fCPU = 2 MHz                                                        |      |

| Figure 14.               | IDD(WAIT) vs. VDD, fCPU = 16 MHz                                                       |      |

| Figure 15.               | Typ. IDD(Halt) vs. VDD, fCPU = 2 MHz and 16 MHz                                        |      |

| Figure 16.               | Typical HSI frequency vs. V <sub>DD</sub>                                              |      |

| Figure 17.               | Typical HSI accuracy vs. temperature, V <sub>DD</sub> = 3 V                            |      |

| Figure 18.               | Typical HSI accuracy vs. temperature, VDD = 1.65 V to 3.6 V.                           | . 46 |

| Figure 19.               | Typical LSI RC frequency vs. VDD.                                                      |      |

| Figure 20.               | Typical VIL and VIH vs. VDD (High sink I/Os)                                           |      |

| Figure 21.               | Typical VIL and VIH vs. VDD (true open drain I/Os).                                    |      |

| Figure 22.               | Typical pull-up resistance $R_{PU}$ vs. $V_{DD}$ with VIN=VSS.                         |      |

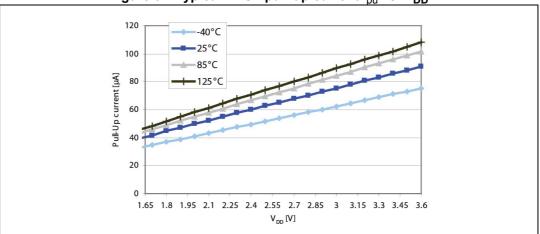

| Figure 23.               | Typical pull-up current $I_{PU}$ vs. $V_{DD}$ with VIN=VSS                             |      |

| Figure 24.               | Typ. VOL at VDD = $3.0 \text{ V}$ (High sink ports)                                    |      |

| Figure 25.               | Typ. VOL at VDD = $1.8 \text{ V}$ (High sink ports)                                    |      |

| Figure 26.               | Typ. VOL at VDD = $3.0 \text{ V}$ (true open drain ports)                              |      |

| Figure 27.               | Typ. VOL at VDD = $1.8 \text{ V}$ (true open drain ports)                              |      |

| Figure 28.               | Typ. VDD - VOH at VDD = $3.0 \text{ V}$ (High sink ports)                              |      |

| Figure 29.               | Typ. VDD - VOH at VDD = $1.8 \text{ V}$ (High sink ports).                             |      |

| Figure 30.               | Typical NRST pull-up resistance $R_{PU}$ vs. $V_{DD}$                                  |      |

| Figure 31.               | Typical NRST pull-up current $I_{pu}$ vs. $V_{DD}$                                     |      |

| Figure 32.               | Recommended NRST pin configuration                                                     |      |

| Figure 33.               | SPI timing diagram - slave mode and CPHA = 0                                           |      |

| Figure 34.               | SPI timing diagram - slave mode and CPHA = $1^{(1)}$                                   |      |

| Figure 35.               | SPI timing diagram - master mode <sup>(1)</sup>                                        | . 00 |

| Figure 36.               | Typical application with I2C bus and timing diagram 1)                                 | 59   |

| Figure 37.               | UFQFPN32 - 32-lead ultra thin fine pitch quad flat no-lead package outline (5 x 5)     |      |

| Figure 38.               | UFQFPN32 recommended footprint.                                                        |      |

| Figure 39.               | UFQFPN32 marking example (package top view)                                            | 66   |

| Figure 40.               | LQFP32 - 32-pin low profile quad flat package outline (7 x 7)                          |      |

| Figure 41.               | LQFP32 recommended footprint                                                           |      |

| Figure 42.               | LQFP32 marking example (package top view).                                             |      |

| Figure 42.               | UFQFPN28 - 28-lead ultra thin fine pitch quad flat no-lead package outline (4 x 4 mm). |      |

| Figure 43.               | UFQFPN28 recommended footprint.                                                        |      |

| Figure 44.               | UFQFPN28 marking example (package top view)                                            |      |

| Figure 45.<br>Figure 46. | UFQFPN20 - 20-lead ultra thin fine pitch quad flat package outline (3x3 mm).           |      |

| i iyule 40.              | $\sqrt{20}$ $\sqrt{20}$ $\sqrt{20}$                                                    | . 13 |

#### 3 **Product overview**

Legend:

AWU: Auto-wakeup unit Int. RC: internal RC oscillator I<sup>2</sup>C: Inter-integrated circuit multimaster interface POR/PDR: Power on reset / power down reset

SPI: Serial peripheral interface

- SWIM: Single wire interface module USART: Universal synchronous / asynchronous receiver / transmitter

- IWDG: Independent watchdog

Δ7/

| Address                      | Block                    | Register label           | Register name              | Reset<br>status |  |  |  |

|------------------------------|--------------------------|--------------------------|----------------------------|-----------------|--|--|--|

| 0x00 521E<br>to<br>0x00 522F |                          | Reserved area (18 bytes) |                            |                 |  |  |  |

| 0x00 5230                    |                          | USART_SR                 | USART status register      | 0xC0            |  |  |  |

| 0x00 5231                    |                          | USART_DR                 | USART data register        | 0xXX            |  |  |  |

| 0x00 5232                    |                          | USART_BRR1               | USART baud rate register 1 | 0x00            |  |  |  |

| 0x00 5233                    | USART                    | USART_BRR2               | USART baud rate register 2 | 0x00            |  |  |  |

| 0x00 5234                    | USARI                    | USART_CR1                | USART control register 1   | 0x00            |  |  |  |

| 0x00 5235                    |                          | USART_CR2                | USART control register 2   | 0x00            |  |  |  |

| 0x00 5236                    |                          | USART_CR3                | USART control register 3   | 0x00            |  |  |  |

| 0x00 5237                    |                          | USART_CR4                | USART control register 4   | 0x00            |  |  |  |

| 0x00 5238<br>to<br>0x00 524F | Reserved area (18 bytes) |                          |                            |                 |  |  |  |

|               |                         | / / N           |

|---------------|-------------------------|-----------------|

| Table 7. Gene | ral hardware register i | map (continued) |

| Address                      | Block                   | Register label           | Register name                          | Reset<br>status |  |  |

|------------------------------|-------------------------|--------------------------|----------------------------------------|-----------------|--|--|

| 0x00 7F78<br>to<br>0x00 7F79 | Reserved area (2 bytes) |                          |                                        |                 |  |  |

| 0x00 7F80                    | SWIM                    | SWIM_CSR                 | SWIM control status register           | 0x00            |  |  |

| 0x00 7F81<br>to<br>0x00 7F8F |                         | Reserved area (15 bytes) |                                        |                 |  |  |

| 0x00 7F90                    |                         | DM_BK1RE                 | Breakpoint 1 register extended byte    | 0xFF            |  |  |

| 0x00 7F91                    |                         | DM_BK1RH                 | Breakpoint 1 register high byte        | 0xFF            |  |  |

| 0x00 7F92                    |                         | DM_BK1RL                 | Breakpoint 1 register low byte         | 0xFF            |  |  |

| 0x00 7F93                    |                         | DM_BK2RE                 | Breakpoint 2 register extended byte    | 0xFF            |  |  |

| 0x00 7F94                    |                         | DM_BK2RH                 | Breakpoint 2 register high byte        | 0xFF            |  |  |

| 0x00 7F95                    | DM                      | DM_BK2RL                 | Breakpoint 2 register low byte         | 0xFF            |  |  |

| 0x00 7F96                    |                         | DM_CR1                   | Debug module control register 1        | 0x00            |  |  |

| 0x00 7F97                    |                         | DM_CR2                   | Debug module control register 2        | 0x00            |  |  |

| 0x00 7F98                    |                         | DM_CSR1                  | Debug module control/status register 1 | 0x10            |  |  |

| 0x00 7F99                    |                         | DM_CSR2                  | Debug module control/status register 2 | 0x00            |  |  |

| 0x00 7F9A                    |                         | DM_ENFCTR                | Enable function register               | 0xFF            |  |  |

#### Table 8. CPU/SWIM/debug module/interrupt controller registers (continued)

1. Refer to Table 7: General hardware register map on page 25 (addresses 0x00 50A0 to 0x00 50A5) for a list of external interrupt registers.

# 7 Option bytes

Option bytes contain configurations for device hardware features as well as the memory protection of the device. They are stored in a dedicated row of the memory.

All option bytes can be modified only in ICP mode (with SWIM) by accessing the EEPROM address. See *Table 10* for details on option byte addresses.

Refer to the STM8L Flash programming manual (PM0054) and STM8 SWIM and Debug Manual (UM0470) for information on SWIM programming procedures.

| Addr.  | Option name                       | Option        |   | Option bits                |    |        |   |      | Factory default |             |         |

|--------|-----------------------------------|---------------|---|----------------------------|----|--------|---|------|-----------------|-------------|---------|

| Auui.  | Option name                       | byte<br>No.   | 7 | 6                          | 5  | 4      | 3 | 2    | 1               | 0           | setting |

| 0x4800 | Read-out<br>protection<br>(ROP)   | OPT1          |   | ROP[7:0]                   |    |        |   | 0x00 |                 |             |         |

| 0x4807 | -                                 | -             |   | Must be programmed to 0x00 |    |        |   |      | 0x00            |             |         |

| 0x4802 | UBC (User<br>Boot code size)      | OPT2          |   | UBC[7:0]                   |    |        |   | 0x00 |                 |             |         |

| 0x4803 | DATASIZE                          | OPT3          |   | DATASIZE[7:0]              |    |        |   | 0x00 |                 |             |         |

| 0x4808 | Independent<br>watchdog<br>option | OPT4<br>[1:0] |   |                            | Re | served |   |      | IWDG<br>_HALT   | IWDG<br>_HW | 0x00    |

#### Table 11. Option byte description

| OPT1 | <b>ROP[7:0]</b> <i>Memory readout protection (ROP)</i><br>0xAA: Enable readout protection (write access via SWIM protocol)<br>Refer to <i>Read-out protection</i> section in the STM8L reference manual<br>(RM0013) for details.                                                                                                                                                                                                                                                                                                    |  |  |  |  |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| OPT2 | <ul> <li>UBC[7:0] Size of the user boot code area</li> <li>0x00: no UBC</li> <li>0x01-0x02: UBC contains only the interrupt vectors.</li> <li>0x03: Page 0 and 1 reserved for the interrupt vectors. Page 2 is available to store user boot code. Memory is write protected</li> <li></li> <li>0x7F - Page 0 to 126 reserved for UBC, memory is write protected</li> <li>Refer to User boot area (UBC) section in the STM8L reference manual (RM0013) for more details.</li> <li>UBC[7] is forced to 0 internally by HW.</li> </ul> |  |  |  |  |

# 9 Electrical parameters

# 9.1 Parameter conditions

Unless otherwise specified, all voltages are referred to V<sub>SS</sub>.

## 9.1.1 Minimum and maximum values

Unless otherwise specified the minimum and maximum values are guaranteed in the worst conditions of ambient temperature, supply voltage and frequencies by tests in production on 100% of the devices with an ambient temperature at  $T_A$ = 25 °C and  $T_A$  =  $T_A$  max (given by the selected temperature range).

### Note: The values given at 85 °C < $T_A \le 125$ °C are only valid for suffix 3 versions.

Data based on characterization results, design simulation and/or technology characteristics are indicated in the table footnotes and are not tested in production. Based on characterization, the minimum and maximum values refer to sample tests and represent the mean value plus or minus three times the standard deviation (mean $\pm 3\Sigma$ ).

## 9.1.2 Typical values

Unless otherwise specified, typical data are based on  $T_A = 25$  °C,  $V_{DD} = 3$  V. They are given only as design guidelines and are not tested.

# 9.1.3 Typical curves

Unless otherwise specified, all typical curves are given only as design guidelines and are not tested.

### 9.1.4 Loading capacitor

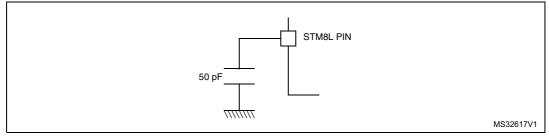

The loading conditions used for pin parameter measurement are shown in *Figure 9*.

#### Figure 9. Pin loading conditions

| Symbol                 | Ratings                                                                  | Max. | Unit |

|------------------------|--------------------------------------------------------------------------|------|------|

| I <sub>VDD</sub>       | Total current into V <sub>DD</sub> power line (source)                   | 80   |      |

| I <sub>VSS</sub>       | Total current out of V <sub>SS</sub> ground line (sink)                  | 80   |      |

|                        | Output current sunk by IR_TIM pin (with high sink LED driver capability) | 80   |      |

| Ι <sub>ΙΟ</sub>        | Output current sunk by any other I/O and control pin                     | 25   | mA   |

|                        | Output current sourced by any I/Os and control pin                       | -25  |      |

|                        | Injected current on true open-drain pins (PC0 and PC1) <sup>(1)</sup>    | -5   |      |

| I <sub>INJ</sub> (PIN) | Injected current on any other pin <sup>(2)</sup>                         | ±5   |      |

| ΣΙ <sub>INJ(PIN)</sub> | Total injected current (sum of all I/O and control pins) <sup>(3)</sup>  | ±25  |      |

#### Table 14. Current characteristics

Positive injection is not possible on these I/Os. V<sub>IN</sub> maximum must always be respected. I<sub>INJ(PIN)</sub> must never be exceeded. A negative injection is induced by V<sub>IN</sub><V<sub>SS</sub>.

I<sub>INJ(PIN)</sub> must never be exceeded. This is implicitly insured if V<sub>IN</sub> maximum is respected. If V<sub>IN</sub> maximum cannot be respected, the injection current must be limited externally to the I<sub>INJ(PIN)</sub> value. A positive injection is induced by V<sub>IN</sub>>V<sub>DD</sub> while a negative injection is induced by V<sub>IN</sub><V<sub>SS</sub>.

When several inputs are submitted to a current injection, the maximum Σl<sub>INJ(PIN)</sub> is the absolute sum of the positive and negative injected currents (instantaneous values). These results are based on characterization with Σl<sub>INJ(PIN)</sub> maximum current injection on four I/O port pins of the device.

| Table ' | 15. | Thermal | characteristics |

|---------|-----|---------|-----------------|

|         |     |         |                 |

| Symbol           | Ratings                      | Value       | Unit |  |  |

|------------------|------------------------------|-------------|------|--|--|

| T <sub>STG</sub> | Storage temperature range    | -65 to +150 | °C   |  |  |

| TJ               | Maximum junction temperature | 150         | C    |  |  |

| Symbol    | Parameter                                                                               | Conditions <sup>(2)</sup>          |                              | Тур  | Max <sup>(3)</sup>  | Unit |

|-----------|-----------------------------------------------------------------------------------------|------------------------------------|------------------------------|------|---------------------|------|

|           |                                                                                         |                                    | f <sub>MASTER</sub> = 2 MHz  | 0.39 | 0.60                |      |

|           |                                                                                         | Code executed from                 | f <sub>MASTER</sub> = 4 MHz  | 0.55 | 0.70                |      |

|           | D (Run)<br>D (Run)<br>D (Run)<br>Supply<br>current in<br>Run<br>mode <sup>(4) (5)</sup> | RAM<br>Code executed from<br>Flash | f <sub>MASTER</sub> = 8 MHz  | 0.90 | 1.20                |      |

|           |                                                                                         |                                    | f <sub>MASTER</sub> = 16 MHz | 1.60 | 2.10 <sup>(6)</sup> | mA   |

| IDD (Run) |                                                                                         |                                    | f <sub>MASTER</sub> = 2 MHz  | 0.55 | 0.70                | mA   |

|           | mode                                                                                    |                                    | f <sub>MASTER</sub> = 4 MHz  | 0.88 | 1.80                |      |

|           |                                                                                         |                                    | f <sub>MASTER</sub> = 8 MHz  | 1.50 | 2.50                |      |

|           |                                                                                         |                                    | f <sub>MASTER</sub> = 16 MHz | 2.70 | 3.50                |      |

Table 18. Total current consumption in Run mode <sup>(1)</sup>

1. Based on characterization results, unless otherwise specified.

- 2. All peripherals off, V\_{DD} from 1.65 V to 3.6 V, HSI internal RC osc.,  $f_{CPU}=f_{MASTER}$

- 3. Maximum values are given for  $T_A$  = –40 to 125  $^\circ C.$

- 4. CPU executing typical data processing.

- 5. An approximate value of I<sub>DD(Run)</sub> can be given by the following formula: I<sub>DD(Run)</sub> = f<sub>MASTER</sub> x 150  $\mu$ A/MHz +215  $\mu$ A.

- 6. Tested in production.

1. Typical current consumption measured with code executed from Flash.

| Symbol           | Parameter                                                                                  | Parameter Conditions                            |                       | Тур | Max<br>(1) | Unit    |

|------------------|--------------------------------------------------------------------------------------------|-------------------------------------------------|-----------------------|-----|------------|---------|

| 1                | Programming/ erasing consumption                                                           | T <sub>A</sub> =+25 °C, V <sub>DD</sub> = 3.0 V | -                     | 0.7 | -          | mA      |

| Iprog            |                                                                                            | T <sub>A</sub> =+25 °C, V <sub>DD</sub> = 1.8 V | -                     | 0.7 | -          | ШA      |

|                  | Data retention (program memory)<br>after 10k erase/write cycles<br>at $T_A = +85$ °C       | T <sub>RET</sub> = 55 °C                        | 20 <sup>(1)</sup>     | -   | -          |         |

| t <sub>RET</sub> | Data retention (data memory)<br>after 10k erase/write cycles<br>at T <sub>A</sub> = +85 °C | T <sub>RET</sub> = 55 °C                        | 20 <sup>(1)</sup>     | -   | -          | years   |

|                  | Data retention (data memory)<br>after 300k erase/write cycles<br>at $T_A = +125$ °C        | T <sub>RET</sub> = 85 °C                        | 1 <sup>(1)</sup>      | -   | -          |         |

| Ν                | Erase/write cycles (program memory)                                                        | See notes <sup>(1)(2)</sup>                     | 10 <sup>(1)</sup>     | -   | -          | kovolca |

| N <sub>RW</sub>  | Erase/write cycles (data memory)                                                           | See notes <sup>(1)(3)</sup>                     | 300 <sup>(1)(4)</sup> | -   | -          | kcycles |

| Table 25. | Flash | program memory | (continued) |

|-----------|-------|----------------|-------------|

|-----------|-------|----------------|-------------|

1. Data based on characterization results, not tested in production.

2. Retention guaranteed after cycling is 10 years at 55 °C.

3. Retention guaranteed after cycling is 1 year at 55 °C.

4. Data based on characterization performed on the whole data memory (2 Kbytes).

# 9.3.6 I/O port pin characteristics

### **General characteristics**

Subject to general operating conditions for  $V_{DD}$  and  $T_A$  unless otherwise specified. All unused pins must be kept at a fixed voltage: using the output mode of the I/O for example or an external pull-up or pull-down resistor.

| Symbol           | Parameter                                         | Conditions                                    | Min                    | Тур | Мах                   | Unit |

|------------------|---------------------------------------------------|-----------------------------------------------|------------------------|-----|-----------------------|------|

| V                | Input low level voltage <sup>(2)</sup>            | Standard I/Os                                 | V <sub>SS</sub> -0.3   | -   | 0.3 x V <sub>DD</sub> | v    |

| V <sub>IL</sub>  | Input low level voltage                           | True open drain I/Os                          | V <sub>SS</sub> -0.3   | -   | 0.3 x V <sub>DD</sub> | v    |

|                  |                                                   | Standard I/Os                                 | 0.70 x V <sub>DD</sub> | -   | V <sub>DD</sub> +0.3  |      |

| V <sub>IH</sub>  | Input high level voltage <sup>(2)</sup>           | True open drain I/Os<br>V <sub>DD</sub> < 2 V | 0.70 x V <sub>DD</sub> |     | 5.2                   | V    |

|                  |                                                   | True open drain I/Os $V_{DD} \ge 2 V$         | 0.70 X V <sub>DD</sub> | -   | 5.5                   |      |

| V                | Schmitt trigger voltage hysteresis <sup>(3)</sup> | Standard I/Os                                 | -                      | 200 | -                     | mV   |

| V <sub>hys</sub> |                                                   | True open drain I/Os                          | -                      | 250 | -                     |      |

| Table 26. I/O static characteristics (1) | ) |

|------------------------------------------|---|

|------------------------------------------|---|

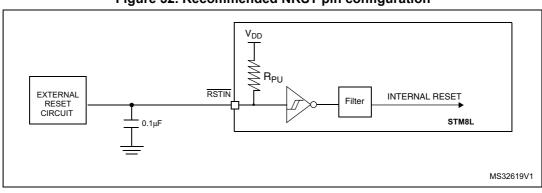

Figure 31. Typical NRST pull-up current I<sub>pu</sub> vs. V<sub>DD</sub>

The reset network shown in *Figure 32* protects the device against parasitic resets. The user must ensure that the level on the NRST pin can go below the  $V_{IL}$  max. level specified in *Table 30*. Otherwise the reset is not taken into account internally. For power consumption-sensitive applications, the capacity of the external reset capacitor can be reduced to limit the charge/discharge current. If the NRST signal is used to reset the external circuitry, the user must pay attention to the charge/discharge time of the external capacitor to meet the reset timing conditions of the external devices. The minimum recommended capacity is 10 nF.

#### Figure 32. Recommended NRST pin configuration

1. Correct device reset during power on sequence is guaranteed when t<sub>VDD[max]</sub> is respected.

External reset circuit is recommended to ensure correct device reset during power down, when V<sub>PDR</sub> < V<sub>DD</sub> < V<sub>DD[min]</sub>.

### Inter IC control interface (I2C)

Subject to general operating conditions for  $V_{\text{DD}},\,f_{\text{MASTER}},$  and  $T_{\text{A}}$  unless otherwise specified.

The STM8L I<sup>2</sup>C interface meets the requirements of the Standard I<sup>2</sup>C communication protocol described in the following table with the restriction mentioned below:

Refer to I/O port characteristics for more details on the input/output alternate function characteristics (SDA and SCL).

| Symbol                                     | Parameter                               |                    | rd mode<br>:C      | Fast mo            | Unit               |    |

|--------------------------------------------|-----------------------------------------|--------------------|--------------------|--------------------|--------------------|----|

|                                            |                                         | Min <sup>(2)</sup> | Max <sup>(2)</sup> | Min <sup>(2)</sup> | Max <sup>(2)</sup> |    |

| t <sub>w(SCLL)</sub>                       | SCL clock low time                      | 4.7                | -                  | 1.3                | -                  |    |

| t <sub>w(SCLH)</sub>                       | SCL clock high time                     | 4.0                | -                  | 0.6                | -                  | μs |

| t <sub>su(SDA)</sub>                       | SDA setup time                          | 250                | -                  | 100                | -                  |    |

| t <sub>h(SDA)</sub>                        | SDA data hold time                      | 0 (3)              | -                  | 0 (4)              | 900 <sup>(3)</sup> |    |

| t <sub>r(SDA)</sub><br>t <sub>r(SCL)</sub> | SDA and SCL rise time                   | -                  | 1000               | -                  | 300                | ns |

| t <sub>f(SDA)</sub><br>t <sub>f(SCL)</sub> | SDA and SCL fall time                   | -                  | 300                | -                  | 300                |    |

| t <sub>h(STA)</sub>                        | START condition hold time               | 4.0                | -                  | 0.6                | -                  |    |

| t <sub>su(STA)</sub>                       | Repeated START condition setup time     | 4.7                | -                  | 0.6                | -                  | μs |

| t <sub>su(STO)</sub>                       | STOP condition setup time               | 4.0                | -                  | 0.6                | -                  | μs |

| t <sub>w(STO:STA)</sub>                    | STOP to START condition time (bus free) | 4.7                | -                  | 1.3                | -                  | μs |

| Cb                                         | Capacitive load for each bus line       | -                  | 400                | -                  | 400                | pF |

| Table 32 | . I2C | characteristics |

|----------|-------|-----------------|

|----------|-------|-----------------|

1. f<sub>SCK</sub> must be at least 8 MHz to achieve max fast I<sup>2</sup>C speed (400 kHz).

2. Data based on standard I<sup>2</sup>C protocol requirement, not tested in production.

3. The maximum hold time of the START condition has only to be met if the interface does not stretch the low period of SCL signal.

4. The device must internally provide a hold time of at least 300 ns for the SDA signal in order to bridge the undefined region of the falling edge of SCL).

Note:

For speeds around 200 kHz, achieved speed can have  $\pm$ 5% tolerance For other speed ranges, achieved speed can have  $\pm$ 2% tolerance The above variations depend on the accuracy of the external components used.

#### Static latch-up

• LU: 2 complementary static tests are required on 10 parts to assess the latch-up performance. A supply overvoltage (applied to each power supply pin) and a current injection (applied to each input, output and configurable I/O pin) are performed on each sample. This test conforms to the EIA/JESD 78 IC latch-up standard. For more details, refer to the application note AN1181.

| Tahlo | 37  | Floctrical | sensitivities  |

|-------|-----|------------|----------------|

| Iable | 31. | Electrical | Selisilivilles |

| Symbol | Parameter             | Class |

|--------|-----------------------|-------|

| LU     | Static latch-up class | II    |

# 9.4 Thermal characteristics

The maximum chip junction temperature  $(T_{Jmax})$  must never exceed the values given in *Table 16: General operating conditions on page 40.*

The maximum chip-junction temperature,  $T_{Jmax}$ , in degrees Celsius, may be calculated using the following equation:

$\mathsf{T}_{\mathsf{Jmax}} = \mathsf{T}_{\mathsf{Amax}} + (\mathsf{P}_{\mathsf{Dmax}} \times \Theta_{\mathsf{JA}})$

Where:

- T<sub>Amax</sub> is the maximum ambient temperature in °C

- $\Theta_{JA}$  is the package junction-to-ambient thermal resistance in ° C/W

- P<sub>Dmax</sub> is the sum of P<sub>INTmax</sub> and P<sub>I/Omax</sub> (P<sub>Dmax</sub> = P<sub>INTmax</sub> + P<sub>I/Omax</sub>)

- P<sub>INTmax</sub> is the product of I<sub>DD</sub> and V<sub>DD</sub>, expressed in watts. This is the maximum chip internal power.

- P<sub>I/Omax</sub> represents the maximum power dissipation on output pins where:

$\mathsf{P}_{\mathsf{I}/\mathsf{Omax}} = \Sigma (\mathsf{V}_{\mathsf{OL}} * \mathsf{I}_{\mathsf{OL}}) + \Sigma ((\mathsf{V}_{\mathsf{DD}} - \mathsf{V}_{\mathsf{OH}}) * \mathsf{I}_{\mathsf{OH}}),$

taking into account the actual  $V_{OL}/I_{OL and} V_{OH}/I_{OH}$  of the I/Os at low and high level in the application.

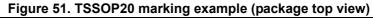

# **Device marking**

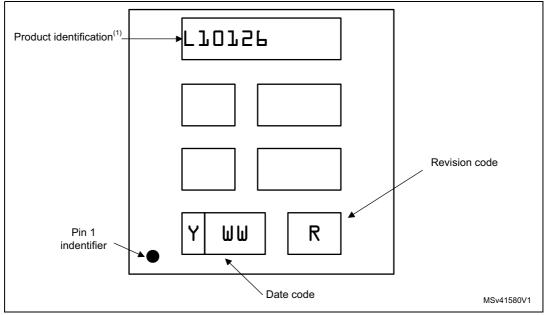

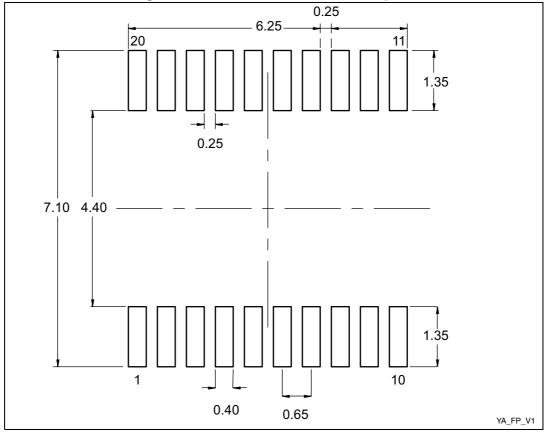

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

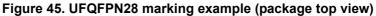

| Dim            | mm  |     |       |     | inches <sup>(1)</sup> |        |  |

|----------------|-----|-----|-------|-----|-----------------------|--------|--|

| Dim.           | Min | Тур | Мах   | Min | Тур                   | Max    |  |

| k              | 0°  | -   | 8°    | 0°  | -                     | 8°     |  |

| aaa            | -   | -   | 0.100 | -   | -                     | 0.0039 |  |

| Number of pins | 20  |     |       |     |                       |        |  |

#### Table 43. TSSOP20 - 20-lead thin shrink small package mechanical data (continued)

1. Values in inches are converted from mm and rounded to 4 decimal digits.

Dimension "D" does not include mold flash, protrusions or gate burrs. Mold flash, protrusions or gate burrs shall not exceed 0.15mm per side.

3. Dimension "E1" does not include interlead flash or protrusions. Interlead flash or protrusions shall not exceed 0.25mm per side.

#### Figure 50. TSSOP20 recommended footprint

1. Dimensions are in millimeters.

# **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

# **11** Device ordering information

| Example:                                                                                   | STM8     | L    | 101 | F | 3 | U | 6 | А | TR |

|--------------------------------------------------------------------------------------------|----------|------|-----|---|---|---|---|---|----|

| Product class<br>STM8 microcontroller                                                      |          |      |     |   |   |   |   |   |    |

| <b>Family type</b><br>L = Low power                                                        | <br>     |      |     |   |   |   |   |   |    |

| Sub-family type                                                                            |          |      |     |   |   |   |   |   |    |

| 101 = sub-family                                                                           |          |      |     |   |   |   |   |   |    |

| Pin count<br>K = 32 pins<br>G = 28 pins<br>F = 20 pins                                     | <br>     |      |     |   |   |   |   |   |    |

| <b>Program memory size</b><br>1 = 2 Kbytes<br>2 = 4 Kbytes                                 |          |      |     |   |   |   |   |   |    |

| 3 = 8 Kbytes                                                                               |          |      |     |   |   |   |   |   |    |

| <b>Package</b><br>U = UFQFPN<br>T = LQFP<br>P = TSSOP                                      |          |      |     |   |   |   |   |   |    |

| <b>Temperature range</b><br>3 = -40 °C to 125 °C<br>6 = -40 °C to 85 °C                    | <br>     |      |     |   |   |   |   |   |    |

| <b>COMP_REF availability on U</b><br>A = COMP_REF available<br>Blank = COMP_REF not availa | 0 and UF | QFPI | N28 |   |   |   |   |   |    |

| <b>Shipping</b><br>TR = Tape and reel<br>Blank = Tray                                      |          |      |     |   |   |   |   |   |    |

#### Figure 52. STM8L101xx ordering information scheme

For a list of available options (e.g. memory size, package) and order-able part numbers or for further information on any aspect of this device, please go to www.st.com or contact the ST Sales Office nearest to you.

# 12 STM8 development tools

Development tools for the STM8 microcontrollers include the full-featured STice emulation system supported by a complete software tool package including C compiler, assembler and integrated development environment with high-level language debugger. In addition, the STM8 is to be supported by a complete range of tools including starter kits, evaluation boards and a low-cost in-circuit debugger/programmer.

# 12.1 Emulation and in-circuit debugging tools

The STice emulation system offers a complete range of emulation and in-circuit debugging features on a platform that is designed for versatility and cost-effectiveness. In addition, STM8 application development is supported by a low-cost in-circuit debugger/programmer.

The STice is the fourth generation of full featured emulators from STMicroelectronics. It offers new advanced debugging capabilities including profiling and coverage to help detect and eliminate bottlenecks in application execution and dead code when fine tuning an application.

In addition, STice offers in-circuit debugging and programming of STM8 microcontrollers via the STM8 single wire interface module (SWIM), which allows non-intrusive debugging of an application while it runs on the target microcontroller.

For improved cost effectiveness, STice is based on a modular design that allows the users to order exactly what they need to meet their development requirements and to adapt their emulation system to support existing and future ST microcontrollers.

#### STice key features

- Occurrence and time profiling and code coverage (new features)

- Program and data trace recording up to 128 KB records

- Read/write on the fly of memory during emulation

- In-circuit debugging/programming via SWIM protocol

- 8-bit probe analyzer

- Power supply follower managing application voltages between 1.62 to 5.5 V

- Modularity that allows the users to specify the components that they need to meet their development requirements and adapt to future requirements

- Supported by free software tools that include integrated development environment (IDE), programming software interface and assembler for STM8.

# 12.2 Software tools

STM8 development tools are supported by a complete, free software package from STMicroelectronics that includes ST Visual Develop (STVD) IDE and the ST Visual Programmer (STVP) software interface. STVD provides seamless integration of the Cosmic and Raisonance C compilers for STM8. A free version that outputs up to 32 Kbytes of code is available.

# 12.2.1 STM8 toolset

**STM8** toolset with STVD integrated development environment and STVP programming software is available for free download at *www.st.com*. This package includes:

ST Visual Develop - Full-featured integrated development environment from ST, featuring

- Seamless integration of C and ASM toolsets

- Full-featured debugger

- Project management

- Syntax highlighting editor

- Integrated programming interface

- Support of advanced emulation features for STice such as code profiling and coverage

**ST Visual Programmer (STVP)** – Easy-to-use, unlimited graphical interface allowing read, write and verify of the STM8 microcontroller Flash program memory, data EEPROM and option bytes. STVP also offers project mode for saving programming configurations and automating programming sequences.

# 12.2.2 C and assembly toolchains

Control of C and assembly toolchains is seamlessly integrated into the STVD integrated development environment, making it possible to configure and control the building of user application directly from an easy-to-use graphical interface.

Available toolchains include:

- Cosmic C compiler for STM8 One free version that outputs up to 32 Kbytes of code is available. For more information, see www.cosmic-software.com.

- Raisonance C compiler for STM8 One free version that outputs up to 32 Kbytes of code. For more information, see www.raisonance.com.

- **STM8 assembler linker** Free assembly toolchain included in the STVD toolset, which allows the user to assemble and link their application source code.

# 12.3 Programming tools

During the development cycle, STice provides in-circuit programming of the STM8 Flash microcontroller on the user's application board via the SWIM protocol. Additional tools are to include a low-cost in-circuit programmer as well as ST socket boards, which provide dedicated programming platforms with sockets for programming the STM8.

For production environments, programmers will include a complete range of gang and automated programming solutions from third-party tool developers already supplying programmers for the STM8 family.

# 13 Revision history

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 19-Dec-2008 | 1        | Initial release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 22-Apr-2009 | 2        | Added TSSOP28 package<br>Modified packages on first page<br>COMPx_OUT pins removed<br>Added <i>Figure 6: 28-pin TSSOP package pinout on page 17</i><br>Modified <i>Section 9: Electrical parameters on page 37</i> .<br>Updated UBC[7:0] description in <i>Section 7: Option bytes</i> .<br>Updated low power current consumption on cover page.<br>Updated <i>Table 13: Voltage characteristics, Table 20: Total current</i><br><i>consumption and timing in Halt and Active-halt mode at VDD = 1.65</i><br>V to 3.6 V, <i>Table 26: I/O static characteristics, Table 30: NRST pin</i><br><i>characteristics, and Section 9.3.9: EMC characteristics.</i><br>Updated PA1/NRST, PC0 and PC1 in <i>Table 4: STM8L101xx pin</i><br><i>description.</i><br>Added ECC feature.<br>Changed internal RC frequency to 38 kHz.<br>Updated electrical characteristics in <i>Table 16, Table 18, Table 19,</i><br><i>Table 20, Table 22, Table 23,</i> and <i>Table 26.</i> |

| 24-Apr-2009 | 3        | Corrected title on cover page.<br>Changed VFQFPN32 to WFQFPN32 and updated <i>Table 39:</i><br><i>UFQFPN32 - 32-lead ultra thin fine pitch quad flat no-lead package</i><br>(5 x 5), package mechanical data.<br>Updated <i>Table 13, Table 26,</i> and <i>Table 33.</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 14-May-2009 | 4        | Replaced WFQFPN20 3 x 3 mm 0.8 mm package by UFQFPN20<br>3 x 3 mm 0.6 mm package (first page, <i>Table 16: General operating</i><br><i>conditions on page 40, Table 38: Thermal characteristics on</i><br><i>page 63, Section 10.2: Package mechanical data on page 67</i> )<br>Added one UFQFPN20 version with COMP_REF<br>Modified <i>Figure 40: LQFP32 recommended footprint</i> <sup>(1)</sup> <i>on page 69</i><br>Added I <sub>PROG</sub> values in <i>Table 25: Flash program memory on page 47</i><br>Updated <i>Table 31: SPI characteristics on page 55</i>                                                                                                                                                                                                                                                                                                                                                                                              |

| 15-May-2009 | 5        | Added STM8L101F3U6ATR part number in <i>Section 4: Pin</i><br>description on page 15 and in Figure 47: STM8L101xx ordering<br>information scheme on page 74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

# Table 44. Document revision history