Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | STM8                                                                   |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 16MHz                                                                  |

| Connectivity               | I²C, SPI, UART/USART                                                   |

| Peripherals                | Infrared, POR, PWM, WDT                                                |

| Number of I/O              | 18                                                                     |

| Program Memory Size        | 8KB (8K x 8)                                                           |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | 2K x 8                                                                 |

| RAM Size                   | 1.5K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 3.6V                                                           |

| Data Converters            | -                                                                      |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 20-UFQFN                                                               |

| Supplier Device Package    | 20-UFQFPN (3x3)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm8l101f3u6tr |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Contents

| 1 |       |                                                    |  |  |

|---|-------|----------------------------------------------------|--|--|

| 2 | Desc  | ription                                            |  |  |

| 3 | Prod  | uct overview                                       |  |  |

|   | 3.1   | Central processing unit STM811                     |  |  |

|   | 3.2   | Development tools                                  |  |  |

|   | 3.3   | Single wire data interface (SWIM) and debug module |  |  |

|   | 3.4   | Interrupt controller                               |  |  |

|   | 3.5   | Memory                                             |  |  |

|   | 3.6   | Low power modes                                    |  |  |

|   | 3.7   | Voltage regulators                                 |  |  |

|   | 3.8   | Clock control                                      |  |  |

|   | 3.9   | Independent watchdog 12                            |  |  |

|   | 3.10  | Auto-wakeup counter 13                             |  |  |

|   | 3.11  | General purpose and basic timers                   |  |  |

|   | 3.12  | Beeper                                             |  |  |

|   | 3.13  | Infrared (IR) interface                            |  |  |

|   | 3.14  | Comparators                                        |  |  |

|   | 3.15  | USART                                              |  |  |

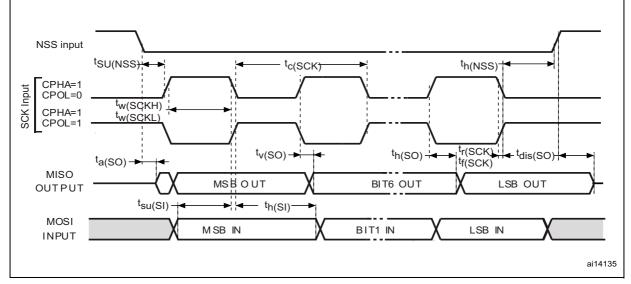

|   | 3.16  | SPI 14                                             |  |  |

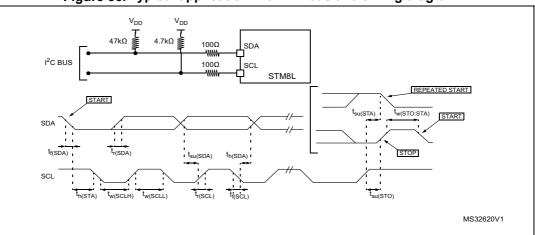

|   | 3.17  | I <sup>2</sup> C 14                                |  |  |

| 4 | Pin d | lescription                                        |  |  |

| 5 | Mem   | ory and register map                               |  |  |

| 6 | Inter | rupt vector mapping                                |  |  |

| 7 | Optic | on bytes                                           |  |  |

| 8 | Uniq  | ue ID                                              |  |  |

| 13 | <b>Revision history</b> |  | 82 |

|----|-------------------------|--|----|

|----|-------------------------|--|----|

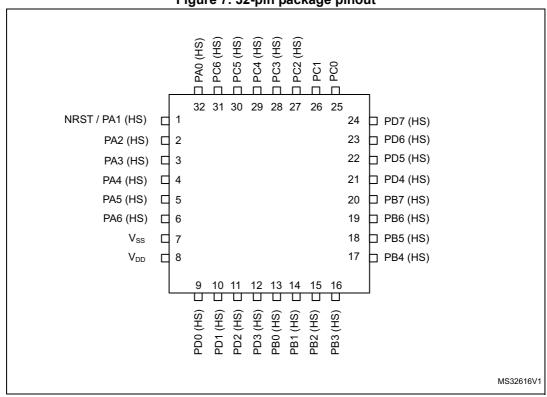

Figure 7. 32-pin package pinout

1. Example given for the UFQFPN32 package. The pinout is the same for the LQFP32 package.

2. HS corresponds to 20 mA high sink/source capability.

High sink LED driver capability available on PA0. Refer to the description of the IR\_CR register in the STM8L reference manual (RM0013).

| Table 7. General hardware register map (continued) |       |                |                                        |                 |  |

|----------------------------------------------------|-------|----------------|----------------------------------------|-----------------|--|

| Address                                            | Block | Register label | Register name                          | Reset<br>status |  |

| 0x00 5280                                          |       | TIM3_CR1       | TIM3 control register 1                | 0x00            |  |

| 0x00 5281                                          |       | TIM3_CR2       | TIM3 control register 2                | 0x00            |  |

| 0x00 5282                                          |       | TIM3_SMCR      | TIM3 slave mode control register       | 0x00            |  |

| 0x00 5283                                          |       | TIM3_ETR       | TIM3 external trigger register         | 0x00            |  |

| 0x00 5284                                          |       | TIM3_IER       | TIM3 interrupt enable register         | 0x00            |  |

| 0x00 5285                                          |       | TIM3_SR1       | TIM3 status register 1                 | 0x00            |  |

| 0x00 5286                                          |       | TIM3_SR2       | TIM3 status register 2                 | 0x00            |  |

| 0x00 5287                                          |       | TIM3_EGR       | TIM3 event generation register         | 0x00            |  |

| 0x00 5288                                          |       | TIM3_CCMR1     | TIM3 capture/compare mode register 1   | 0x00            |  |

| 0x00 5289                                          |       | TIM3_CCMR2     | TIM3 capture/compare mode register 2   | 0x00            |  |

| 0x00 528A                                          | ТІМЗ  | TIM3_CCER1     | TIM3 capture/compare enable register 1 | 0x00            |  |

| 0x00 528B                                          | TIMO  | TIM3_CNTRH     | TIM3 counter high                      | 0x00            |  |

| 0x00 528C                                          |       | TIM3_CNTRL     | TIM3 counter low                       | 0x00            |  |

| 0x00 528D                                          |       | TIM3_PSCR      | TIM3 prescaler register                | 0x00            |  |

| 0x00 528E                                          |       | TIM3_ARRH      | TIM3 auto-reload register high         | 0xFF            |  |

| 0x00 528F                                          |       | TIM3_ARRL      | TIM3 auto-reload register low          | 0xFF            |  |

| 0x00 5290                                          |       | TIM3_CCR1H     | TIM3 capture/compare register 1 high   | 0x00            |  |

| 0x00 5291                                          |       | TIM3_CCR1L     | TIM3 capture/compare register 1 low    | 0x00            |  |

| 0x00 5292                                          |       | TIM3_CCR2H     | TIM3 capture/compare register 2 high   | 0x00            |  |

| 0x00 5293                                          |       | TIM3_CCR2L     | TIM3 capture/compare register 2 low    | 0x00            |  |

| 0x00 5294                                          |       | TIM3_BKR       | TIM3 break register                    | 0x00            |  |

| 0x00 5295                                          |       | TIM3_OISR      | TIM3 output idle state register        | 0x00            |  |

| 0x00 5296<br>to<br>0x00 52DF                       |       | F              | Reserved area (74 bytes)               |                 |  |

| 0x00 52E0                                          |       | TIM4_CR1       | TIM4 control register 1                | 0x00            |  |

| 0x00 52E1                                          |       | TIM4_CR2       | TIM4 control register 2                | 0x00            |  |

| 0x00 52E2                                          |       | TIM4_SMCR      | TIM4 Slave mode control register       | 0x00            |  |

| 0x00 52E3                                          |       | TIM4_IER       | TIM4 interrupt enable register         | 0x00            |  |

| 0x00 52E4                                          | TIM4  | TIM4_SR1       | TIM4 Status register 1                 | 0x00            |  |

| 0x00 52E5                                          |       | TIM4_EGR       | TIM4 event generation register         | 0x00            |  |

| 0x00 52E6                                          |       | TIM4_CNTR      | TIM4 counter                           | 0x00            |  |

| 0x00 52E7                                          |       | TIM4_PSCR      | TIM4 prescaler register                | 0x00            |  |

| 0x00 52E8                                          |       | TIM4_ARR       | TIM4 auto-reload register low          | 0xFF            |  |

Table 7. General hardware register map (continued)

| IRQ<br>No. | Source<br>block | Description                                                              | Wakeup<br>from Halt<br>mode | Wakeup<br>from<br>Active-halt<br>mode | Wakeup<br>from Wait<br>(WFI<br>mode) | Wakeup<br>from Wait<br>(WFE<br>mode) | Vector<br>address |  |

|------------|-----------------|--------------------------------------------------------------------------|-----------------------------|---------------------------------------|--------------------------------------|--------------------------------------|-------------------|--|

| 27         | USART           | Transmission<br>complete/transmit data<br>register empty                 | -                           | -                                     | Yes                                  | Yes <sup>(1)</sup>                   | 0x00 8074         |  |

| 28         | USART           | Receive Register DATA<br>FULL/overrun/idle line<br>detected/parity error | -                           | -                                     | Yes                                  | Yes <sup>(1)</sup>                   | 0x00 8078         |  |

| 29         | I2C             | I2C interrupt <sup>(2)</sup>                                             | Yes                         | Yes                                   | Yes                                  | Yes <sup>(1)</sup>                   | 0x00 807C         |  |

Table 9. Interrupt mapping (continued)

1. In WFE mode, this interrupt is served if it has been previously enabled. After processing the interrupt, the processor goes back to WFE mode. Refer to Section *Wait for event (WFE) mode* in the RM0013 reference manual.

2. The device is woken up from Halt or Active-halt mode only when the address received matches the interface address.

|      | DATASIZE[7:0] Size of the data EEPROM area                                                          |

|------|-----------------------------------------------------------------------------------------------------|

|      | 0x00: no data EEPROM area <sup>(1)</sup>                                                            |

|      | 0x01: 1 page reserved for data storage from 0x9FC0 to 0x9FFF <sup>(1)</sup>                         |

| OPT3 | 0x02: 2 pages reserved for data storage from 0x9F80 to 0x9FFF <sup>(1)</sup> <sup>(1)</sup>         |

| 0110 | 0x20: 32 pages reserved for data storage from 0x9800 to 0x9FFF <sup>(1)</sup>                       |

|      | Refer to <i>Data EEPROM (DATA)</i> section in the STM8L reference manual (RM0013) for more details. |

|      | DATASIZE[7:6] are forced to 0 internal by HW.                                                       |

|      | IWDG_HW: Independent watchdog                                                                       |

|      | 0: Independent watchdog activated by software                                                       |

| OPT4 | 1: Independent watchdog activated by hardware                                                       |

| 0114 | IWDG_HALT: Independent window watchdog reset on Halt/Active-halt                                    |

|      | 0: Independent watchdog continues running in Halt/Active-halt mode                                  |

|      | 1: Independent watchdog stopped in Halt/Active-halt mode                                            |

| ,    |                                                                                                     |

### Table 11. Option byte description (continued)

1. 0x00 is the only allowed value for 4 Kbyte STM8L101xx devices.

**Caution:** After a device reset, read access to the program memory is not guaranteed if address 0x4807 is not programmed to 0x00.

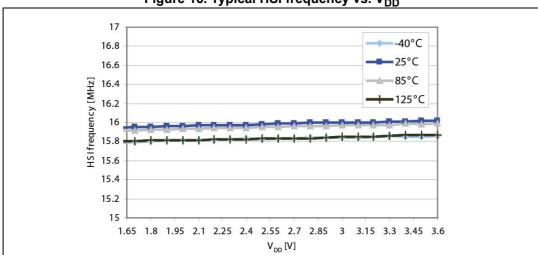

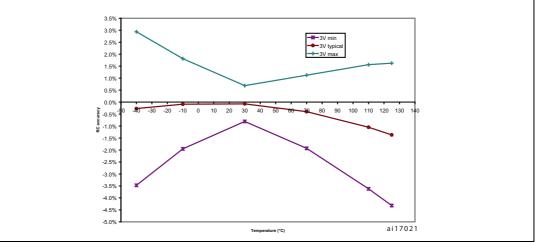

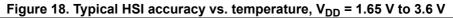

Figure 16. Typical HSI frequency vs. V<sub>DD</sub>

DocID15275 Rev 15

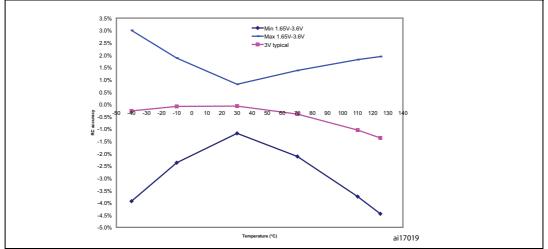

## Low speed internal RC oscillator (LSI)

| Symbol                  | Parameter                                     | Conditions                   | Min | Тур | Max | Unit |

|-------------------------|-----------------------------------------------|------------------------------|-----|-----|-----|------|

| f <sub>LSI</sub>        | Frequency                                     | -                            | 26  | 38  | 56  | kHz  |

| f <sub>drift(LSI)</sub> | LSI oscillator frequency drift <sup>(2)</sup> | 0 °C ≤T <sub>A</sub> ≤ 85 °C | -12 | -   | 11  | %    |

| Table 23, LSI o | oscillator | characteristics | (1) |

|-----------------|------------|-----------------|-----|

|-----------------|------------|-----------------|-----|

1.  $V_{DD}$  = 1.65 V to 3.6 V, T<sub>A</sub> = -40 to 125 °C unless otherwise specified.

2. For each individual part, this value is the frequency drift from the initial measured frequency.

## Figure 19. Typical LSI RC frequency vs. $\mathrm{V}_{\mathrm{DD}}$

## 9.3.5 Memory characteristics

$T_A$  = -40 to 125 °C unless otherwise specified.

#### Table 24. RAM and hardware registers

| Symbol          | Parameter                          | Conditions           | Min | Тур | Max | Unit |

|-----------------|------------------------------------|----------------------|-----|-----|-----|------|

| V <sub>RM</sub> | Data retention mode <sup>(1)</sup> | Halt mode (or Reset) | 1.4 | -   | -   | V    |

1. Minimum supply voltage without losing data stored in RAM (in Halt mode or under Reset) or in hardware registers (only in Halt mode). Guaranteed by characterization, not tested in production.

#### Flash memory

| Symbol          | Parameter                                                                             | Conditions                   | Min  | Тур | Max<br>(1) | Unit |

|-----------------|---------------------------------------------------------------------------------------|------------------------------|------|-----|------------|------|

| V <sub>DD</sub> | Operating voltage<br>(all modes, read/write/erase)                                    | f <sub>MASTER</sub> = 16 MHz | 1.65 | -   | 3.6        | V    |

| +               | Programming time for 1- or 64-byte (block)<br>erase/write cycles (on programmed byte) | -                            | -    | 6   | -          | ms   |

| Lprog           | Programming time for 1- to 64-byte (block)<br>write cycles (on erased byte)           | -                            | -    | 3   | -          | ms   |

Table 25. Flash program memory

| Symbol           | Parameter                                                                                  | Conditions                                      | Min                   | Тур | Max<br>(1) | Unit    |

|------------------|--------------------------------------------------------------------------------------------|-------------------------------------------------|-----------------------|-----|------------|---------|

| 1                | Programming/ erasing consumption                                                           | T <sub>A</sub> =+25 °C, V <sub>DD</sub> = 3.0 V | -                     | 0.7 | -          | mA      |

| Iprog            |                                                                                            | T <sub>A</sub> =+25 °C, V <sub>DD</sub> = 1.8 V | -                     | 0.7 | -          | ШA      |

|                  | Data retention (program memory)<br>after 10k erase/write cycles<br>at $T_A = +85$ °C       | T <sub>RET</sub> = 55 °C                        | 20 <sup>(1)</sup>     | -   | -          |         |

| t <sub>RET</sub> | Data retention (data memory)<br>after 10k erase/write cycles<br>at T <sub>A</sub> = +85 °C | T <sub>RET</sub> = 55 °C                        | 20 <sup>(1)</sup>     | -   | -          | years   |

|                  | Data retention (data memory)<br>after 300k erase/write cycles<br>at $T_A = +125$ °C        | T <sub>RET</sub> = 85 °C                        | 1 <sup>(1)</sup>      | -   | -          |         |

| Ν                | Erase/write cycles (program memory)                                                        | See notes <sup>(1)(2)</sup>                     | 10 <sup>(1)</sup>     | -   | -          | kovolca |

| N <sub>RW</sub>  | Erase/write cycles (data memory)                                                           | See notes <sup>(1)(3)</sup>                     | 300 <sup>(1)(4)</sup> | -   | -          | kcycles |

| Table 25. | Flash | program memory | (continued) |

|-----------|-------|----------------|-------------|

|-----------|-------|----------------|-------------|

1. Data based on characterization results, not tested in production.

2. Retention guaranteed after cycling is 10 years at 55 °C.

3. Retention guaranteed after cycling is 1 year at 55 °C.

4. Data based on characterization performed on the whole data memory (2 Kbytes).

# 9.3.6 I/O port pin characteristics

## **General characteristics**

Subject to general operating conditions for  $V_{DD}$  and  $T_A$  unless otherwise specified. All unused pins must be kept at a fixed voltage: using the output mode of the I/O for example or an external pull-up or pull-down resistor.

| Symbol           | Parameter                                         | Conditions                                    | Min                    | Тур | Мах                   | Unit |  |

|------------------|---------------------------------------------------|-----------------------------------------------|------------------------|-----|-----------------------|------|--|

| V <sub>IL</sub>  | Input low level voltage <sup>(2)</sup>            | Standard I/Os                                 | V <sub>SS</sub> -0.3   | -   | 0.3 x V <sub>DD</sub> | V    |  |

|                  |                                                   | True open drain I/Os                          | V <sub>SS</sub> -0.3   | -   | 0.3 x V <sub>DD</sub> | v    |  |

|                  |                                                   | Standard I/Os                                 | 0.70 x V <sub>DD</sub> | -   | V <sub>DD</sub> +0.3  |      |  |

| V <sub>IH</sub>  | Input high level voltage <sup>(2)</sup>           | True open drain I/Os<br>V <sub>DD</sub> < 2 V | 0.70 x V <sub>DD</sub> |     | 5.2                   | v    |  |

|                  |                                                   | True open drain I/Os $V_{DD} \ge 2 V$         | 0.70 X V <sub>DD</sub> | -   | 5.5                   |      |  |

| V <sub>hys</sub> | Schmitt trigger voltage hysteresis <sup>(3)</sup> | Standard I/Os                                 | -                      | 200 | -                     | mV   |  |

|                  |                                                   | True open drain I/Os                          | -                      | 250 | -                     |      |  |

| Table 26. I/O static characteristics (1) | ) |

|------------------------------------------|---|

|------------------------------------------|---|

## **NRST** pin

The NRST pin input driver is CMOS. A permanent pull-up is present.  $R_{PU(NRST)}$  has the same value as  $R_{PU}$  (see *Table 26 on page 48*).

Subject to general operating conditions for  $V_{\text{DD}}$  and  $T_{\text{A}}$  unless otherwise specified.

| Symbol                | Parameter                                       | Conditions             | Min      | Тур <sup>(1)</sup> | Мах                  | Unit |

|-----------------------|-------------------------------------------------|------------------------|----------|--------------------|----------------------|------|

| V <sub>IL(NRST)</sub> | NRST input low level voltage <sup>(1)</sup>     | -                      | $V_{SS}$ | -                  | 0.8                  |      |

| V <sub>IH(NRST)</sub> | NRST input high level voltage <sup>(1)</sup>    | -                      | 1.4      | -                  | V <sub>DD</sub>      | V    |

| V <sub>OL(NRST)</sub> | NRST output low level voltage                   | I <sub>OL</sub> = 2 mA | -        | -                  | V <sub>DD</sub> -0.8 |      |

| R <sub>PU(NRST)</sub> | NRST pull-up equivalent resistor <sup>(2)</sup> | -                      | 30       | 45                 | 60                   | kΩ   |

| V <sub>F(NRST)</sub>  | NRST input filtered pulse <sup>(3)</sup>        | -                      | -        | -                  | 50                   | ns   |

| t <sub>OP(NRST)</sub> | NRST output pulse width                         | -                      | 20       | -                  | -                    | ns   |

| V <sub>NF(NRST)</sub> | NRST input not filtered pulse <sup>(3)</sup>    | -                      | 300      | -                  | _                    | ns   |

Table 30. NRST pin characteristics

1. Data based on characterization results, not tested in production.

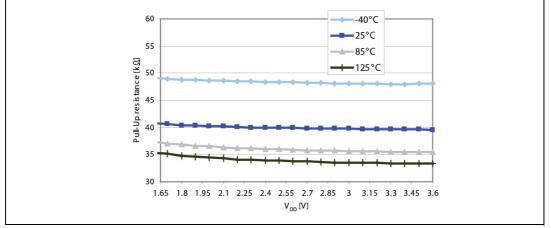

The R<sub>PU</sub> pull-up equivalent resistor is based on a resistive transistor (*Figure 30*). Corresponding I<sub>PU</sub> current characteristics are described in *Figure 31*.

3. Data guaranteed by design, not tested in production.

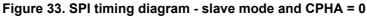

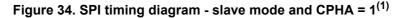

1. Measurement points are done at CMOS levels:  $0.3V_{\text{DD}}$  and  $0.7V_{\text{DD}}$

Figure 36. Typical application with I2C bus and timing diagram<sup>1)</sup>

1. Measurement points are done at CMOS levels: 0.3 x  $V_{\text{DD}}$  and 0.7 x  $V_{\text{DD}}$

#### 9.3.8 **Comparator characteristics**

| Symbol                             | Parameter                                       | Conditions                                                          | Min <sup>(1)</sup> | Тур | Max <sup>(1)</sup>    | Unit |

|------------------------------------|-------------------------------------------------|---------------------------------------------------------------------|--------------------|-----|-----------------------|------|

| V <sub>IN(COMP_REF)</sub>          | Comparator external reference                   | -                                                                   | -0.1               | -   | V <sub>DD</sub> -1.25 | V    |

| V <sub>IN</sub>                    | Comparator input voltage range                  | -                                                                   | -0.25              | -   | V <sub>DD</sub> +0.25 | V    |

| V <sub>offset</sub> <sup>(2)</sup> | Comparator offset error                         | -                                                                   | -                  | -   | ±20                   | mV   |

| t <sub>START</sub>                 | Startup time (after BIAS_EN)                    | -                                                                   | -                  | -   | 3 <sup>(1)</sup>      | μs   |

|                                    | Analog comparator consumption                   | -                                                                   | -                  | -   | 25 <sup>(1)</sup>     | μA   |

| I <sub>DD(COMP)</sub>              | Analog comparator consumption during power-down | -                                                                   | -                  | -   | 60 <sup>(1)</sup>     | nA   |

| t <sub>propag</sub> <sup>(2)</sup> | Comparator propagation delay                    | 100-mV input step<br>with 5-mV overdrive,<br>input rise time = 1 ns | -                  | -   | 2 <sup>(1)</sup>      | μs   |

Table 33. Comparator characteristics

1. Data guaranteed by design, not tested in production.

The comparator accuracy depends on the environment. In particular, the following cases may reduce the accuracy of the 2. comparator and must be avoided:

- Negative injection current on the I/Os close to the comparator inputs

Switching on I/Os close to the comparator inputs

Negative injection current on not used comparator input.

Switching with a high dV/dt on not used comparator input.

These phenomena are even more critical when a big external serial resistor is added on the inputs.

## 9.3.9 EMC characteristics

Susceptibility tests are performed on a sample basis during product characterization.

## Functional EMS (electromagnetic susceptibility)

Based on a simple running application on the product (toggling 2 LEDs through I/O ports), the product is stressed by two electromagnetic events until a failure occurs (indicated by the LEDs).

- **ESD**: Electrostatic discharge (positive and negative) is applied on all pins of the device until a functional disturbance occurs. This test conforms with the IEC 61000-4-2 standard.

- FTB: A burst of fast transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100 pF capacitor, until a functional disturbance occurs. This test conforms with the IEC 61000-4-4 standard.

A device reset allows normal operations to be resumed. The test results are given in the table below based on the EMS levels and classes defined in application note AN1709.

## Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

Prequalification trials:

Most of the common failures (unexpected reset and program counter corruption) can be reproduced by manually forcing a low state on the NRST pin or the oscillator pins for 1 second.

To complete these trials, ESD stress can be applied directly on the device, over the range of specification values. When unexpected behavior is detected, the software can be hardened to prevent unrecoverable errors occurring. Refer to application note *Software techniques for improving microcontrollers EMC performance* (AN1015).

| Symbol            | Parameter                                                                               | Conditions                                           | Level/<br>Class |

|-------------------|-----------------------------------------------------------------------------------------|------------------------------------------------------|-----------------|

| V <sub>FESD</sub> | Voltage limits to be applied on any I/O pin to induce a functional disturbance          | LQFP32, V <sub>DD</sub> = 3.3 V                      | 3B              |

|                   | Fast transient voltage burst limits to be                                               | LQFP32, V <sub>DD</sub> = 3.3 V, f <sub>HSI</sub>    | 3B              |

| V <sub>EFTB</sub> | applied through 100 pF on $V_{DD}$ and $V_{SS}$ pins to induce a functional disturbance | LQFP32, V <sub>DD</sub> = 3.3 V, f <sub>HSI</sub> /2 | 4A              |

#### Table 34. EMS data

## Static latch-up

• LU: 2 complementary static tests are required on 10 parts to assess the latch-up performance. A supply overvoltage (applied to each power supply pin) and a current injection (applied to each input, output and configurable I/O pin) are performed on each sample. This test conforms to the EIA/JESD 78 IC latch-up standard. For more details, refer to the application note AN1181.

| Tahlo | 37  | Floctrical | sensitivities  |

|-------|-----|------------|----------------|

| Iable | 31. | Electrical | Selisitivities |

| Symbol | Parameter             | Class |

|--------|-----------------------|-------|

| LU     | Static latch-up class | II    |

# 9.4 Thermal characteristics

The maximum chip junction temperature  $(T_{Jmax})$  must never exceed the values given in *Table 16: General operating conditions on page 40.*

The maximum chip-junction temperature,  $T_{Jmax}$ , in degrees Celsius, may be calculated using the following equation:

$\mathsf{T}_{\mathsf{Jmax}} = \mathsf{T}_{\mathsf{Amax}} + (\mathsf{P}_{\mathsf{Dmax}} \times \Theta_{\mathsf{JA}})$

Where:

- T<sub>Amax</sub> is the maximum ambient temperature in °C

- $\Theta_{JA}$  is the package junction-to-ambient thermal resistance in ° C/W

- P<sub>Dmax</sub> is the sum of P<sub>INTmax</sub> and P<sub>I/Omax</sub> (P<sub>Dmax</sub> = P<sub>INTmax</sub> + P<sub>I/Omax</sub>)

- P<sub>INTmax</sub> is the product of I<sub>DD</sub> and V<sub>DD</sub>, expressed in watts. This is the maximum chip internal power.

- P<sub>I/Omax</sub> represents the maximum power dissipation on output pins where:

$\mathsf{P}_{\mathsf{I}/\mathsf{Omax}} = \Sigma (\mathsf{V}_{\mathsf{OL}} * \mathsf{I}_{\mathsf{OL}}) + \Sigma ((\mathsf{V}_{\mathsf{DD}} - \mathsf{V}_{\mathsf{OH}}) * \mathsf{I}_{\mathsf{OH}}),$

taking into account the actual  $V_{OL}/I_{OL and} V_{OH}/I_{OH}$  of the I/Os at low and high level in the application.

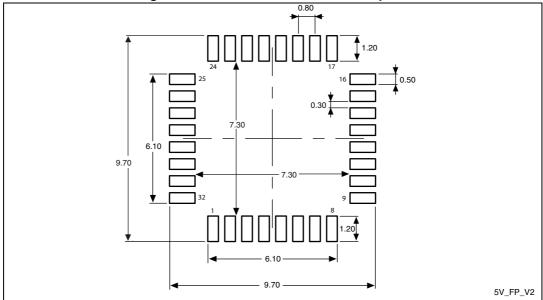

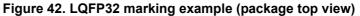

#### Figure 41. LQFP32 recommended footprint

1. Dimensions are expressed in millimeters.

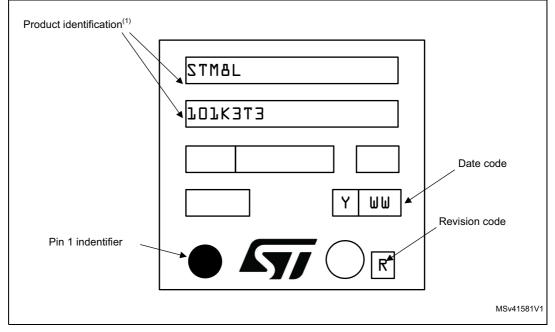

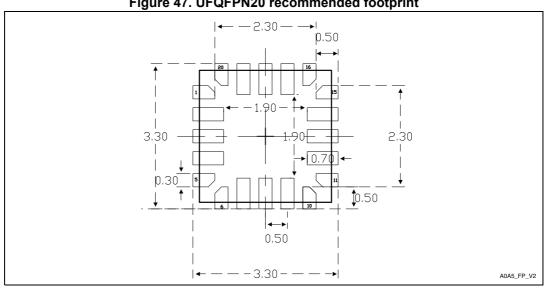

## **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

# 10.4 UFQFPN20 package information

Figure 46. UFQFPN20 - 20-lead ultra thin fine pitch quad flat package outline (3x3 mm)

1. Drawing is not to scale.

| Symbol |       | millimeters |       |        | inches <sup>(1)</sup> |        |

|--------|-------|-------------|-------|--------|-----------------------|--------|

|        | Min   | Тур         | Мах   | Min    | Тур                   | Max    |

| D      | -     | 3.000       | -     | -      | 0.1181                | -      |

| E      | -     | 3.000       | -     | -      | 0.1181                | -      |

| А      | 0.500 | 0.550       | 0.600 | 0.0197 | 0.0217                | 0.0236 |

| A1     | 0.000 | 0.020       | 0.050 | 0.0000 | 0.0008                | 0.0020 |

| A3     | -     | 0.152       | -     | -      | 0.0060                | -      |

| е      | -     | 0.500       | -     | -      | 0.0197                | -      |

| L1     | 0.500 | 0.550       | 0.600 | 0.0197 | 0.0217                | 0.0236 |

| L2     | 0.300 | 0.350       | 0.400 | 0.0118 | 0.0138                | 0.0157 |

| L3     | -     | 0.375       | -     | -      | 0.0148                | -      |

| L4     | -     | 0.200       | -     | -      | 0.0079                | -      |

| L5     | -     | 0.150       | -     | -      | 0.0059                | -      |

| b      | 0.180 | 0.250       | 0.300 | 0.0071 | 0.0098                | 0.0118 |

| ddd    | -     | 0.050       | -     | -      | 0.0020                | -      |

## Table 42. UFQFPN20 - 20-lead ultra thin fine pitch quad flat package (3 x 3 mm) mechanical data

1. Values in inches are rounded to 4 decimal digits

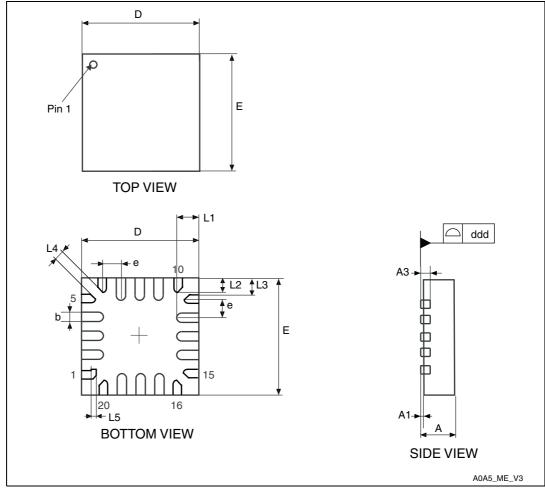

## Figure 47. UFQFPN20 recommended footprint

1. Dimensions are in millimeters.

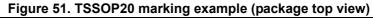

## **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

# 12.2 Software tools

STM8 development tools are supported by a complete, free software package from STMicroelectronics that includes ST Visual Develop (STVD) IDE and the ST Visual Programmer (STVP) software interface. STVD provides seamless integration of the Cosmic and Raisonance C compilers for STM8. A free version that outputs up to 32 Kbytes of code is available.

## 12.2.1 STM8 toolset

**STM8** toolset with STVD integrated development environment and STVP programming software is available for free download at *www.st.com*. This package includes:

ST Visual Develop - Full-featured integrated development environment from ST, featuring

- Seamless integration of C and ASM toolsets

- Full-featured debugger

- Project management

- Syntax highlighting editor

- Integrated programming interface

- Support of advanced emulation features for STice such as code profiling and coverage

**ST Visual Programmer (STVP)** – Easy-to-use, unlimited graphical interface allowing read, write and verify of the STM8 microcontroller Flash program memory, data EEPROM and option bytes. STVP also offers project mode for saving programming configurations and automating programming sequences.

## 12.2.2 C and assembly toolchains

Control of C and assembly toolchains is seamlessly integrated into the STVD integrated development environment, making it possible to configure and control the building of user application directly from an easy-to-use graphical interface.

Available toolchains include:

- Cosmic C compiler for STM8 One free version that outputs up to 32 Kbytes of code is available. For more information, see www.cosmic-software.com.

- Raisonance C compiler for STM8 One free version that outputs up to 32 Kbytes of code. For more information, see www.raisonance.com.

- **STM8 assembler linker** Free assembly toolchain included in the STVD toolset, which allows the user to assemble and link their application source code.

# 12.3 Programming tools

During the development cycle, STice provides in-circuit programming of the STM8 Flash microcontroller on the user's application board via the SWIM protocol. Additional tools are to include a low-cost in-circuit programmer as well as ST socket boards, which provide dedicated programming platforms with sockets for programming the STM8.

For production environments, programmers will include a complete range of gang and automated programming solutions from third-party tool developers already supplying programmers for the STM8 family.

#### IMPORTANT NOTICE – PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2016 STMicroelectronics – All rights reserved

DocID15275 Rev 15