Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                      |

|----------------------------|----------------------------------------------------------------------|

| Product Status             | Active                                                               |

| Core Processor             | STM8                                                                 |

| Core Size                  | 8-Bit                                                                |

| Speed                      | 16MHz                                                                |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                    |

| Peripherals                | Infrared, POR, PWM, WDT                                              |

| Number of I/O              | 30                                                                   |

| Program Memory Size        | 8KB (8K x 8)                                                         |

| Program Memory Type        | FLASH                                                                |

| EEPROM Size                | 2K x 8                                                               |

| RAM Size                   | 1.5K x 8                                                             |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 3.6V                                                         |

| Data Converters            | -                                                                    |

| Oscillator Type            | Internal                                                             |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                   |

| Mounting Type              | Surface Mount                                                        |

| Package / Case             | 32-LQFP                                                              |

| Supplier Device Package    | 32-LQFP (7x7)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm8l101k3t3 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **List of figures**

| Figure 1.                | STM8L101xx device block diagram                                                       | . 10         |

|--------------------------|---------------------------------------------------------------------------------------|--------------|

| Figure 2.                | Standard 20-pin UFQFPN package pinout                                                 | . 15         |

| Figure 3.                | 20-pin UFQFPN package pinout for STM8L101F1U6ATR,                                     |              |

| Ü                        | STM8L101F2U6ATR and STM8L101F3U6ATR part numbers                                      | . 16         |

| Figure 4.                | 20-pin TSSOP package pinout                                                           |              |

| Figure 5.                | Standard 28-pin UFQFPN package pinout                                                 |              |

| Figure 6.                | 28-pin UFQFPN package pinout for STM8L101G3U6ATR and                                  |              |

| J                        | STM8L101G2U6ATR part numbers                                                          | . 18         |

| Figure 7.                | 32-pin package pinout                                                                 |              |

| Figure 8.                | Memory map                                                                            |              |

| Figure 9.                | Pin loading conditions                                                                |              |

| Figure 10.               | Pin input voltage                                                                     |              |

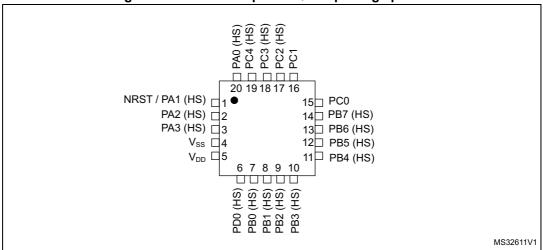

| Figure 11.               | IDD(RUN) vs. VDD, fCPU = 2 MHz                                                        |              |

| Figure 12.               | IDD(RUN) vs. VDD, fCPU = 16 MHz                                                       |              |

| Figure 13.               | IDD(WAIT) vs. VDD, fCPU = 2 MHz                                                       |              |

| Figure 14.               | IDD(WAIT) vs. VDD, fCPU = 16 MHz                                                      |              |

| Figure 15.               | Typ. IDD(Halt) vs. VDD, fCPU = 2 MHz and 16 MHz                                       |              |

| Figure 16.               | Typical HSI frequency vs. V <sub>DD</sub>                                             |              |

| Figure 17.               | Typical HSI accuracy vs. temperature, V <sub>DD</sub> = 3 V                           |              |

| Figure 18.               | Typical HSI accuracy vs. temperature, VDD = 1.65 V to 3.6 V                           |              |

| Figure 19.               | Typical LSI RC frequency vs. VDD                                                      |              |

| Figure 20.               | Typical VIL and VIH vs. VDD (High sink I/Os)                                          |              |

| Figure 21.               | Typical VIL and VIH vs. VDD (true open drain I/Os)                                    |              |

| Figure 22.               | Typical pull-up resistance R <sub>PU</sub> vs. V <sub>DD</sub> with VIN=VSS           |              |

| Figure 23.               | Typical pull-up current I <sub>PU</sub> vs. V <sub>DD</sub> with VIN=VSS              | . 50<br>50   |

| Figure 24.               | Typ. VOL at VDD = 3.0 V (High sink ports)                                             |              |

| Figure 25.               | Typ. VOL at VDD = 1.8 V (High sink ports)                                             |              |

| Figure 26.               | Typ. VOL at VDD = 3.0 V (true open drain ports)                                       |              |

| Figure 27.               | Typ. VOL at VDD = 1.8 V (true open drain ports)                                       |              |

| Figure 28.               | Typ. VDD - VOH at VDD = 3.0 V (High sink ports)                                       |              |

| Figure 29.               | Typ. VDD - VOH at VDD = 1.8 V (High sink ports)                                       |              |

| Figure 30.               | Typical NRST pull-up resistance R <sub>PU</sub> vs. V <sub>DD</sub>                   |              |

| Figure 31.               | Typical NRST pull-up current I <sub>pu</sub> vs. V <sub>DD</sub>                      |              |

| Figure 32.               | Recommended NRST pin configuration                                                    |              |

| Figure 33.               | SPI timing diagram - slave mode and CPHA = 0                                          |              |

| Figure 34.               | SPI timing diagram - slave mode and CPHA = 1 <sup>(1)</sup>                           | . 56         |

| Figure 35.               | SPI timing diagram - master mode <sup>(1)</sup>                                       | . 57         |

| Figure 36.               | Typical application with I2C bus and timing diagram 1)                                | . 57<br>59   |

| Figure 37.               | UFQFPN32 - 32-lead ultra thin fine pitch quad flat no-lead package outline (5 x 5)    |              |

| Figure 38.               | UFQFPN32 recommended footprint                                                        |              |

| Figure 39.               | UFQFPN32 marking example (package top view)                                           |              |

| Figure 40.               | LQFP32 - 32-pin low profile quad flat package outline (7 x 7)                         | . 67         |

| Figure 41.               | LQFP32 recommended footprint                                                          |              |

| Figure 42.               | LQFP32 marking example (package top view)                                             | . 03<br>60   |

| Figure 43.               | UFQFPN28 - 28-lead ultra thin fine pitch quad flat no-lead package outline (4 x 4 mm) | . ∪∂<br>7∩   |

| Figure 44.               | UFQFPN28 recommended footprint                                                        |              |

| Figure 45.               | UFQFPN28 marking example (package top view)                                           |              |

| Figure 46.               | UFQFPN20 - 20-lead ultra thin fine pitch quad flat package outline (3x3 mm)           |              |

| ı iyul <del>e 4</del> 0. | Of Grining - 20-lead uitta tilli lille pitch quad liat package dutille (3x3 lilli)    | . <i>1</i> 3 |

#### 3 **Product overview**

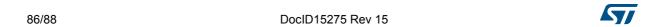

Figure 1. STM8L101xx device block diagram

### Legend:

AWU: Auto-wakeup unit Int. RC: internal RC oscillator I²C: Inter-integrated circuit multimaster interface POR/PDR: Power on reset / power down reset

SPI: Serial peripheral interface

SWIM: Single wire interface module USART: Universal synchronous / asynchronous receiver / transmitter

IWDG: Independent watchdog

## 3.5 Memory

The STM8L101xx devices have the following main features:

- 1.5 Kbytes of RAM

- The EEPROM is divided into two memory arrays (see the STM8L reference manual for details on the memory mapping):

- Up to 8 Kbytes of low-density embedded Flash program including up to 2 Kbytes of data EEPROM. Data EEPROM and Flash program areas can be write protected independently by using the memory access security mechanism (MASS).

- 64 option bytes (one block) of which 5 bytes are already used for the device.

Error correction code is implemented on the EEPROM.

## 3.6 Low power modes

To minimize power consumption, the product features three low power modes:

- Wait mode: CPU clock stopped, selected peripherals at full clock speed.

- Active-halt mode: CPU and peripheral clocks are stopped. The programmable wakeup time is controlled by the AWU unit.

- Halt mode: CPU and peripheral clocks are stopped, the device remains powered on. The RAM content is preserved. Wakeup is triggered by an external interrupt.

## 3.7 Voltage regulators

The STM8L101xx embeds an internal voltage regulator for generating the 1.8 V power supply for the core and peripherals.

This regulator has two different modes: main voltage regulator mode (MVR) and low power voltage regulator mode (LPVR). When entering Halt or Active-halt modes, the system automatically switches from the MVR to the LPVR in order to reduce current consumption.

### 3.8 Clock control

The STM8L101xx embeds a robust clock controller. It is used to distribute the system clock to the core and the peripherals and to manage clock gating for low power modes. This system clock is a 16-MHz High Speed Internal RC oscillator (HSI RC), followed by a programmable prescaler.

In addition, a 38 kHz low speed internal RC oscillator is used by the independent watchdog (IWDG) and Auto-wakeup unit (AWU).

## 3.9 Independent watchdog

The independent watchdog (IWDG) peripheral can be used to resolve processor malfunctions due to hardware or software failures.

It is clocked by the 38 kHz LSI internal RC clock source, and thus stays active even in case of a CPU clock failure.

## 4 Pin description

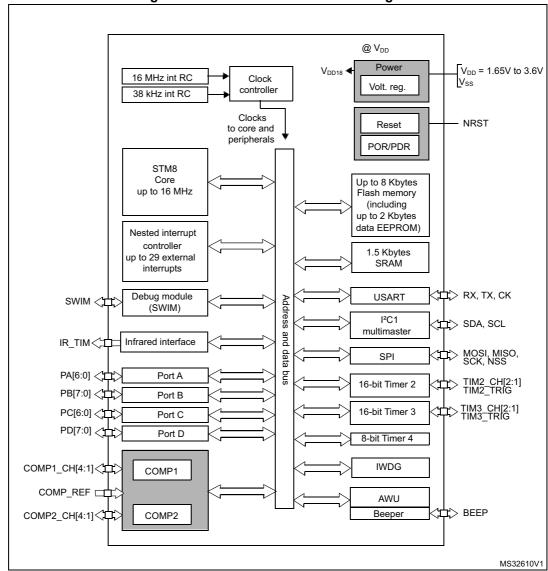

Figure 2. Standard 20-pin UFQFPN package pinout

- 1. HS corresponds to 20 mA high sink/source capability.

- High sink LED driver capability available on PA0. Refer to the description of the IR\_CR register in the STM8L reference manual (RM0013).

Note:

The COMP\_REF pin is not available in this standard 20-pin UFQFPN package. It is available on Port A6 in the Figure 3: 20-pin UFQFPN package pinout for STM8L101F1U6ATR, STM8L101F2U6ATR and STM8L101F3U6ATR part numbers.

PA0 (HS) PC4 (HS) PC3 (HS) PC2 (HS) PC1 20 19 18 17 16 NRST / PA1 (HS) ☐1 ● 15 PC0 PA2 (HS) □2 14 PB7 (HS) PA6 (HS) 3 13 PB6 (HS) V<sub>SS</sub> □4 12 PB5 (HS) V<sub>DD</sub> □5 11 PB4 (HS) 6 7 8 9 10 PD0 (HS) PB0 (HS) PB1 (HS) PB2 (HS) MS32612V1

Figure 3. 20-pin UFQFPN package pinout for STM8L101F1U6ATR, STM8L101F2U6ATR and STM8L101F3U6ATR part numbers

- 1. Please refer to the warning below.

- 2. HS corresponds to 20 mA high sink/source capability.

- High sink LED driver capability available on PA0. Refer to the description of the IR\_CR register in the STM8L reference manual (RM0013).

### Warning:

For the STM8L101F1U6ATR, STM8L101F2U6ATR and STM8L101F3U6ATR part numbers (devices with COMP\_REF pin), all ports available on 32-pin packages must be considered as active ports. To avoid spurious effects, the user has to configure them as input pull-up. A small increase in consumption (typ. < 300  $\mu$ A) may occur during the power up and reset phase until these ports are properly configured.

|                   | Pi                                    | n nı    | ımb               | er                                    |      |                                                         |      |          | Input                   |                | O                 | utput |    |                                |                                                          |

|-------------------|---------------------------------------|---------|-------------------|---------------------------------------|------|---------------------------------------------------------|------|----------|-------------------------|----------------|-------------------|-------|----|--------------------------------|----------------------------------------------------------|

| standard UFQFPN20 | UFQFPN20 with COMP_REF <sup>(1)</sup> | TSSOP20 | standard UFQFPN28 | UFQFPN28 with COMP_REF <sup>(1)</sup> | ı o∟ | Pin name                                                | Type | floating | ndw                     | Ext. interrupt | High sink/source  | ФО    | dd | Main function<br>(after reset) | Alternate function                                       |

| -                 | -                                     | -       | 26                | 26                                    | 30   | PC5                                                     | I/O  | X        | Х                       | Х              | HS                | Х     | Х  | Port C5                        | -                                                        |

| -                 | -                                     | -       | 27                | 27                                    | 31   | PC6                                                     | I/O  | X        | Х                       | Х              | HS                | Х     | Х  | Port C6                        | -                                                        |

| 20                | 20                                    | 3       | 28                | 28                                    | 32   | PA0 <sup>(5)</sup> /SWIM/<br>BEEP/IR_TIM <sup>(6)</sup> | I/O  | х        | <b>X</b> <sup>(5)</sup> | Х              | HS <sup>(6)</sup> | Х     | Х  | Port A0                        | SWIM input and output /Beep output/Timer Infrared output |

Table 4. STM8L101xx pin description (continued)

- 1. Please refer to the warning below.

- 2. At power-up, the PA1/NRST pin is a reset input pin with pull-up. To be used as a general purpose pin (PA1), it can be configured only as a general purpose pin (PA1), it can be configured only as output push-pull, not neither as output opendrain nor as a general purpose input. Refer to Section *Configuring NRST/PA1 pin as general purpose output* in the STM8L reference manual (RM0013).

- 3. A pull-up is applied to PB0 and PB4 during the reset phase. These two pins are input floating after reset release.

- In the open-drain output column, 'T' defines a true open-drain I/O (P-buffer, weak pull-up and protection diode to V<sub>DD</sub> are not implemented).

- 5. The PA0 pin is in input pull-up during the reset phase and after reset release.

- 6. High sink LED driver capability available on PA0.

Slope control of all GPIO pins can be programmed except true open drain pins and by default is limited to 2 MHz.

Warning: For the STM8L101F1U6ATR, STM8L101F2U6ATR,

STM8L101F3U6ATR, STM8L101G2U6ATR and STM8L101G3U6ATR part numbers (devices with COMP\_REF

pin), all ports available on 32-pin packages must be considered as active ports. To avoid spurious effects, the user has to configure them as input pull-up. A small increase in consumption (typ. < 300 µA) may occur during the power

up and reset phase until these ports are properly configured.

Table 5. Flash and RAM boundary addresses

| Memory area          | Size       | Start address | End address |

|----------------------|------------|---------------|-------------|

| RAM                  | 1.5 Kbytes | 0x00 0000     | 0x00 05FF   |

|                      | 2 Kbytes   | 0x00 8000     | 0x00 87FF   |

| Flash program memory | 4 Kbytes   | 0x00 8000     | 0x00 8FFF   |

|                      | 8 Kbytes   | 0x00 8000     | 0x00 9FFF   |

Note:

2 Kbytes of Data EEPROM is only available on devices with 8 Kbytes flash program memory.

Table 6. I/O Port hardware register map

| Address   | Block  | Register label | Register name                     | Reset<br>status |

|-----------|--------|----------------|-----------------------------------|-----------------|

| 0x00 5000 |        | PA_ODR         | Port A data output latch register | 0x00            |

| 0x00 5001 |        | PA_IDR         | Port A input pin value register   | 0xxx            |

| 0x00 5002 | Port A | PA_DDR         | Port A data direction register    | 0x00            |

| 0x00 5003 |        | PA_CR1         | Port A control register 1         | 0x00            |

| 0x00 5004 |        | PA_CR2         | Port A control register 2         | 0x00            |

| 0x00 5005 |        | PB_ODR         | Port B data output latch register | 0x00            |

| 0x00 5006 |        | PB_IDR         | Port B input pin value register   | 0xxx            |

| 0x00 5007 | Port B | PB_DDR         | Port B data direction register    | 0x00            |

| 0x00 5008 |        | PB_CR1         | Port B control register 1         | 0x00            |

| 0x00 5009 |        | PB_CR2         | Port B control register 2         | 0x00            |

| 0x00 500A |        | PC_ODR         | Port C data output latch register | 0x00            |

| 0x00 500B |        | PC_IDR         | Port C input pin value register   | 0xxx            |

| 0x00 500C | Port C | PC_DDR         | Port C data direction register    | 0x00            |

| 0x00 500D |        | PC_CR1         | Port C control register 1         | 0x00            |

| 0x00 500E |        | PC_CR2         | Port C control register 2         | 0x00            |

| 0x00 500F |        | PD_ODR         | Port D data output latch register | 0x00            |

| 0x00 5010 |        | PD_IDR         | Port D input pin value register   | 0xxx            |

| 0x00 5011 | Port D | PD_DDR         | Port D data direction register    | 0x00            |

| 0x00 5012 |        | PD_CR1         | Port D control register 1         | 0x00            |

| 0x00 5013 |        | PD_CR2         | Port D control register 2         | 0x00            |

Table 7. General hardware register map (continued)

| Address                      | Block | Register label | Register name              | Reset<br>status |

|------------------------------|-------|----------------|----------------------------|-----------------|

| 0x00 521E<br>to<br>0x00 522F |       | R              | teserved area (18 bytes)   |                 |

| 0x00 5230                    |       | USART_SR       | USART status register      | 0xC0            |

| 0x00 5231                    |       | USART_DR       | USART data register        | 0xXX            |

| 0x00 5232                    |       | USART_BRR1     | USART baud rate register 1 | 0x00            |

| 0x00 5233                    | USART | USART_BRR2     | USART baud rate register 2 | 0x00            |

| 0x00 5234                    | USART | USART_CR1      | USART control register 1   | 0x00            |

| 0x00 5235                    |       | USART_CR2      | USART control register 2   | 0x00            |

| 0x00 5236                    |       | USART_CR3      | USART control register 3   | 0x00            |

| 0x00 5237                    |       | USART_CR4      | USART control register 4   | 0x00            |

| 0x00 5238<br>to<br>0x00 524F |       | R              | teserved area (18 bytes)   |                 |

Table 7. General hardware register map (continued)

| Address                      | Block  | Register label           | Register name                          | Reset<br>status |  |  |  |  |

|------------------------------|--------|--------------------------|----------------------------------------|-----------------|--|--|--|--|

| 0x00 5250                    |        | TIM2_CR1                 | TIM2 control register 1                | 0x00            |  |  |  |  |

| 0x00 5251                    |        | TIM2_CR2                 | TIM2 control register 2                | 0x00            |  |  |  |  |

| 0x00 5252                    |        | TIM2_SMCR                | TIM2 slave mode control register       | 0x00            |  |  |  |  |

| 0x00 5253                    |        | TIM2_ETR                 | TIM2 external trigger register         | 0x00            |  |  |  |  |

| 0x00 5254                    |        | TIM2_IER                 | TIM2 interrupt enable register         | 0x00            |  |  |  |  |

| 0x00 5255                    |        | TIM2_SR1                 | TIM2 status register 1                 | 0x00            |  |  |  |  |

| 0x00 5256                    |        | TIM2_SR2                 | TIM2 status register 2                 | 0x00            |  |  |  |  |

| 0x00 5257                    |        | TIM2_EGR                 | TIM2 event generation register         | 0x00            |  |  |  |  |

| 0x00 5258                    |        | TIM2_CCMR1               | TIM2 capture/compare mode register 1   | 0x00            |  |  |  |  |

| 0x00 5259                    |        | TIM2_CCMR2               | TIM2 capture/compare mode register 2   | 0x00            |  |  |  |  |

| 0x00 525A                    | TIM2   | TIM2_CCER1               | TIM2 capture/compare enable register 1 | 0x00            |  |  |  |  |

| 0x00 525B                    | TIIVI∠ | TIM2_CNTRH               | TIM2 counter high                      | 0x00            |  |  |  |  |

| 0x00 525C                    |        | TIM2_CNTRL               | TIM2 counter low                       | 0x00            |  |  |  |  |

| 0x00 525D                    |        | TIM2_PSCR                | TIM2 prescaler register                | 0x00            |  |  |  |  |

| 0x00 525E                    |        | TIM2_ARRH                | TIM2 auto-reload register high         | 0xFF            |  |  |  |  |

| 0x00 525F                    |        | TIM2_ARRL                | TIM2 auto-reload register low          | 0xFF            |  |  |  |  |

| 0x00 5260                    |        | TIM2_CCR1H               | TIM2 capture/compare register 1 high   | 0x00            |  |  |  |  |

| 0x00 5261                    |        | TIM2_CCR1L               | TIM2 capture/compare register 1 low    | 0x00            |  |  |  |  |

| 0x00 5262                    |        | TIM2_CCR2H               | TIM2 capture/compare register 2 high   | 0x00            |  |  |  |  |

| 0x00 5263                    |        | TIM2_CCR2L               | TIM2 capture/compare register 2 low    | 0x00            |  |  |  |  |

| 0x00 5264                    |        | TIM2_BKR                 | TIM2 break register                    | 0x00            |  |  |  |  |

| 0x00 5265                    |        | TIM2_OISR                | TIM2 output idle state register        | 0x00            |  |  |  |  |

| 0x00 5266<br>to<br>0x00 527F |        | Reserved area (26 bytes) |                                        |                 |  |  |  |  |

Table 9. Interrupt mapping (continued)

| IRQ<br>No. | Source<br>block | Description                                                              | Wakeup<br>from Halt<br>mode | Wakeup<br>from<br>Active-halt<br>mode | Wakeup<br>from Wait<br>(WFI<br>mode) | Wakeup<br>from Wait<br>(WFE<br>mode) | Vector<br>address |

|------------|-----------------|--------------------------------------------------------------------------|-----------------------------|---------------------------------------|--------------------------------------|--------------------------------------|-------------------|

| 27         | USART           | Transmission complete/transmit data register empty                       | -                           | -                                     | Yes                                  | Yes <sup>(1)</sup>                   | 0x00 8074         |

| 28         | USART           | Receive Register DATA<br>FULL/overrun/idle line<br>detected/parity error | -                           | -                                     | Yes                                  | Yes <sup>(1)</sup>                   | 0x00 8078         |

| 29         | I2C             | I2C interrupt <sup>(2)</sup>                                             | Yes                         | Yes                                   | Yes                                  | Yes <sup>(1)</sup>                   | 0x00 807C         |

In WFE mode, this interrupt is served if it has been previously enabled. After processing the interrupt, the processor goes back to WFE mode. Refer to Section Wait for event (WFE) mode in the RM0013 reference manual.

<sup>2.</sup> The device is woken up from Halt or Active-halt mode only when the address received matches the interface address.

## 8 Unique ID

STM8L101xx devices feature a 96-bit unique device identifier which provides a reference number that is unique for any device and in any context. The 96 bits of the identifier can never be altered by the user.

The unique device identifier can be read in single bytes and may then be concatenated using a custom algorithm.

The unique device identifier is ideally suited:

- For use as serial numbers

- For use as security keys to increase the code security in the program memory while using and combining this unique ID with software cryptographic primitives and protocols before programming the internal memory

- To activate secure boot processes.

Table 12. Unique ID registers (96 bits)

| A -l -l | Content          | Unique ID bits |             |   |     |          |   |   |   |  |  |

|---------|------------------|----------------|-------------|---|-----|----------|---|---|---|--|--|

| Address | description      | 7              | 6           | 5 | 4   | 3        | 2 | 1 | 0 |  |  |

| 0x4925  | X co-ordinate on | U_ID[7:0]      |             |   |     |          |   |   |   |  |  |

| 0x4926  | the wafer        | U_ID[15:8]     |             |   |     |          |   |   |   |  |  |

| 0x4927  | Y co-ordinate on |                |             |   | U_I | D[23:16] |   |   |   |  |  |

| 0x4928  | the wafer        |                | U_ID[31:24] |   |     |          |   |   |   |  |  |

| 0x4929  | Wafer number     | U_ID[39:32]    |             |   |     |          |   |   |   |  |  |

| 0x492A  |                  | U_ID[47:40]    |             |   |     |          |   |   |   |  |  |

| 0x492B  |                  | U_ID[55:48]    |             |   |     |          |   |   |   |  |  |

| 0x492C  |                  | U_ID[63:56]    |             |   |     |          |   |   |   |  |  |

| 0x492D  | Lot number       | U_ID[71:64]    |             |   |     |          |   |   |   |  |  |

| 0x492E  |                  | U_ID[79:72]    |             |   |     |          |   |   |   |  |  |

| 0x492F  |                  | U_ID[87:80]    |             |   |     |          |   |   |   |  |  |

| 0x4930  |                  | U_ID[95:88]    |             |   |     |          |   |   |   |  |  |

#### **Electrical parameters** 9

#### 9.1 **Parameter conditions**

Unless otherwise specified, all voltages are referred to V<sub>SS</sub>.

#### 9.1.1 Minimum and maximum values

Unless otherwise specified the minimum and maximum values are guaranteed in the worst conditions of ambient temperature, supply voltage and frequencies by tests in production on 100% of the devices with an ambient temperature at  $T_A$  = 25 °C and  $T_A$  =  $T_A$  max (given by the selected temperature range).

Note: The values given at 85 °C < $T_A \le 125$  °C are only valid for suffix 3 versions.

> Data based on characterization results, design simulation and/or technology characteristics are indicated in the table footnotes and are not tested in production. Based on characterization, the minimum and maximum values refer to sample tests and represent the mean value plus or minus three times the standard deviation (mean $\pm 3\Sigma$ ).

#### 9.1.2 Typical values

Unless otherwise specified, typical data are based on  $T_A = 25$  °C,  $V_{DD} = 3$  V. They are given only as design guidelines and are not tested.

#### 9.1.3 **Typical curves**

Unless otherwise specified, all typical curves are given only as design guidelines and are not tested.

#### 9.1.4 Loading capacitor

The loading conditions used for pin parameter measurement are shown in Figure 9.

STM8L PIN MS32617V1

Figure 9. Pin loading conditions

| Symbol    | Parameter         | Conditions <sup>(2)</sup> |                              | Тур  | Max <sup>(3)</sup>  | Unit          |

|-----------|-------------------|---------------------------|------------------------------|------|---------------------|---------------|

|           |                   |                           | f <sub>MASTER</sub> = 2 MHz  | 0.39 | 0.60                |               |

|           |                   | Code executed from        | f <sub>MASTER</sub> = 4 MHz  | 0.55 | 0.70                |               |

|           | 0                 | RAM                       | f <sub>MASTER</sub> = 8 MHz  | 0.90 | 1.20                |               |

|           | Supply current in | rrent in                  | f <sub>MASTER</sub> = 16 MHz | 1.60 | 2.10 <sup>(6)</sup> | mA            |

| IDD (Run) | Run               |                           | f <sub>MASTER</sub> = 2 MHz  | 0.55 | 0.70                | - IIIA  <br>- |

|           | mode              |                           | f <sub>MASTER</sub> = 4 MHz  | 0.88 | 1.80                |               |

|           |                   |                           | f <sub>MASTER</sub> = 8 MHz  | 1.50 | 2.50                |               |

|           |                   |                           | f <sub>MASTER</sub> = 16 MHz | 2.70 | 3.50                |               |

Table 18. Total current consumption in Run mode (1)

- 1. Based on characterization results, unless otherwise specified.

- 2. All peripherals off,  $V_{DD}$  from 1.65 V to 3.6 V, HSI internal RC osc.,  $f_{CPU} = f_{MASTER}$

- 3. Maximum values are given for  $T_A = -40$  to 125 °C.

- 4. CPU executing typical data processing.

- 5. An approximate value of  $I_{DD(Run)}$  can be given by the following formula:  $I_{DD(Run)}$  =  $f_{MASTER}$  x 150  $\mu A/MHz$  +215  $\mu A.$

- 6. Tested in production.

1. Typical current consumption measured with code executed from Flash.

## 10.2 LQFP32 package information

SEATING PLANE С Ą 0.25 mm GAUGE PLANE С CCC D F D1 D3 25 16 Ш ----Ш ---╼ <del>III</del> ₽₽ 珊 <del>\_\_\_\_</del>9 PIN 1 IDENTIFICATION <u>e</u> 5V\_ME\_V2

Figure 40. LQFP32 - 32-pin low profile quad flat package outline (7 x 7)

1. Drawing is not to scale.

Table 41. UFQFPN28 - 28-lead ultra thin fine pitch quad flat no-lead package (4 x 4), package mechanical data

| Dim.   |                | mm    | <u> </u> | inches <sup>(1)</sup> |        |        |  |  |  |  |

|--------|----------------|-------|----------|-----------------------|--------|--------|--|--|--|--|

| Dilli. | Min            | Тур   | Max      | Min                   | Тур    | Max    |  |  |  |  |

| А      | 0.500          | 0.550 | 0.600    | 0.0197                | 0.0217 | 0.0236 |  |  |  |  |

| A1     | 0              | 0.020 | 0.050    | 0                     | 0.0008 | 0.002  |  |  |  |  |

| A3     | -              | 0.152 | -        | -                     | 0.0060 | -      |  |  |  |  |

| b      | 0.180          | 0.250 | 0.300    | 0.0071                | 0.0098 | 0.0118 |  |  |  |  |

| D      | -              | 4.000 | -        | -                     | 0.1575 | -      |  |  |  |  |

| Е      | -              | 4.000 | -        | -                     | 0.1575 | -      |  |  |  |  |

| е      | -              | 0.500 | -        | -                     | 0.0197 | -      |  |  |  |  |

| L1     | 0.250          | 0.350 | 0.450    | 0.0098                | 0.0138 | 0.0177 |  |  |  |  |

| L2     | 0.300          | 0.400 | 0.500    | 0.0118                | 0.0157 | 0.0197 |  |  |  |  |

| ddd    | -              | 0.080 | -        | -                     | 0.0031 | -      |  |  |  |  |

| -      | Number of pins |       |          |                       |        |        |  |  |  |  |

| N      |                | 28    |          |                       |        |        |  |  |  |  |

<sup>1.</sup> Values in inches are converted from mm and rounded to 4 decimal digits.

4.30 3.30 3.20 0.50 A0B0\_FP\_V2

Figure 44. UFQFPN28 recommended footprint

1. Dimensions are expressed in millimeters.

Table 42. UFQFPN20 - 20-lead ultra thin fine pitch quad flat package (3 x 3 mm) mechanical data

| Cumbal |       | millimeters |       | inches <sup>(1)</sup> |        |        |  |  |

|--------|-------|-------------|-------|-----------------------|--------|--------|--|--|

| Symbol | Min   | Тур         | Max   | Min                   | Тур    | Max    |  |  |

| D      | -     | 3.000       | -     | -                     | 0.1181 | -      |  |  |

| Е      | -     | 3.000       | -     | -                     | 0.1181 | -      |  |  |

| А      | 0.500 | 0.550       | 0.600 | 0.0197                | 0.0217 | 0.0236 |  |  |

| A1     | 0.000 | 0.020       | 0.050 | 0.0000                | 0.0008 | 0.0020 |  |  |

| A3     | -     | 0.152       | -     | -                     | 0.0060 | -      |  |  |

| е      | -     | 0.500       | -     | -                     | 0.0197 | -      |  |  |

| L1     | 0.500 | 0.550       | 0.600 | 0.0197                | 0.0217 | 0.0236 |  |  |

| L2     | 0.300 | 0.350       | 0.400 | 0.0118                | 0.0138 | 0.0157 |  |  |

| L3     | -     | 0.375       | -     | -                     | 0.0148 | -      |  |  |

| L4     | -     | 0.200       | -     | -                     | 0.0079 | -      |  |  |

| L5     | -     | 0.150       | -     | -                     | 0.0059 | -      |  |  |

| b      | 0.180 | 0.250       | 0.300 | 0.0071                | 0.0098 | 0.0118 |  |  |

| ddd    | -     | 0.050       | -     | -                     | 0.0020 | -      |  |  |

<sup>1.</sup> Values in inches are rounded to 4 decimal digits

0.50 2.30 0.50 0.50 -3.30 - -A0A5\_FP\_V2

Figure 47. UFQFPN20 recommended footprint

1. Dimensions are in millimeters.

## 10.5 TSSOP20 package information

Figure 49. TSSOP20 - 20-lead thin shrink small package outline

1. Drawing is not to scale.

Table 43. TSSOP20 - 20-lead thin shrink small package mechanical data

| Dim.              | mm    |       |       | inches <sup>(1)</sup> |        |        |

|-------------------|-------|-------|-------|-----------------------|--------|--------|

|                   | Min   | Тур   | Max   | Min                   | Тур    | Max    |

| А                 | -     | -     | 1.200 | -                     | -      | 0.0472 |

| A1                | 0.050 | -     | 0.150 | 0.0020                | -      | 0.0059 |

| A2                | 0.800 | 1.000 | 1.050 | 0.0315                | 0.0394 | 0.0413 |

| b                 | 0.190 | -     | 0.300 | 0.0075                | -      | 0.0118 |

| CP                | -     | -     | 0.100 | -                     | -      | 0.0039 |

| С                 | 0.090 | -     | 0.200 | 0.0035                | -      | 0.0079 |

| D <sup>(2)</sup>  | 6.400 | 6.500 | 6.600 | 0.2520                | 0.2559 | 0.2598 |

| E                 | 6.200 | 6.400 | 6.600 | 0.2441                | 0.2520 | 0.2598 |

| E1 <sup>(3)</sup> | 4.300 | 4.400 | 4.500 | 0.1693                | 0.1732 | 0.1772 |

| е                 | -     | 0.650 | -     | 0.1693                | 0.0256 | -      |

| L                 | 0.450 | 0.600 | 0.750 | 0.1693                | 0.0236 | 0.0295 |

| L1                | -     | 1.000 | -     | -                     | 0.0394 | -      |

Table 43. TSSOP20 - 20-lead thin shrink small package mechanical data (continued)

| Dim.           | mm  |     |       |     | inches <sup>(1)</sup> |        |

|----------------|-----|-----|-------|-----|-----------------------|--------|

|                | Min | Тур | Max   | Min | Тур                   | Max    |

| k              | 0°  | -   | 8°    | 0°  | -                     | 8°     |

| aaa            | -   | -   | 0.100 | -   | -                     | 0.0039 |

| Number of pins | 20  |     |       |     |                       |        |

- 1. Values in inches are converted from mm and rounded to 4 decimal digits.

- Dimension "D" does not include mold flash, protrusions or gate burrs. Mold flash, protrusions or gate burrs shall not exceed 0.15mm per side.

- 3. Dimension "E1" does not include interlead flash or protrusions. Interlead flash or protrusions shall not exceed 0.25mm per side

Dimensions are in millimeters.

### 12.2 Software tools

STM8 development tools are supported by a complete, free software package from STMicroelectronics that includes ST Visual Develop (STVD) IDE and the ST Visual Programmer (STVP) software interface. STVD provides seamless integration of the Cosmic and Raisonance C compilers for STM8. A free version that outputs up to 32 Kbytes of code is available.

### 12.2.1 STM8 toolset

**STM8 toolset** with STVD integrated development environment and STVP programming software is available for free download at <a href="https://www.st.com">www.st.com</a>. This package includes:

ST Visual Develop - Full-featured integrated development environment from ST, featuring

- Seamless integration of C and ASM toolsets

- Full-featured debugger

- Project management

- Syntax highlighting editor

- Integrated programming interface

- Support of advanced emulation features for STice such as code profiling and coverage

**ST Visual Programmer (STVP)** – Easy-to-use, unlimited graphical interface allowing read, write and verify of the STM8 microcontroller Flash program memory, data EEPROM and option bytes. STVP also offers project mode for saving programming configurations and automating programming sequences.

### 12.2.2 C and assembly toolchains

Control of C and assembly toolchains is seamlessly integrated into the STVD integrated development environment, making it possible to configure and control the building of user application directly from an easy-to-use graphical interface.

Available toolchains include:

- **Cosmic C compiler for STM8** One free version that outputs up to 32 Kbytes of code is available. For more information, see www.cosmic-software.com.

- Raisonance C compiler for STM8 One free version that outputs up to 32 Kbytes of code. For more information, see www.raisonance.com.

- **STM8 assembler linker** Free assembly toolchain included in the STVD toolset, which allows the user to assemble and link their application source code.

## 12.3 Programming tools

During the development cycle, STice provides in-circuit programming of the STM8 Flash microcontroller on the user's application board via the SWIM protocol. Additional tools are to include a low-cost in-circuit programmer as well as ST socket boards, which provide dedicated programming platforms with sockets for programming the STM8.

For production environments, programmers will include a complete range of gang and automated programming solutions from third-party tool developers already supplying programmers for the STM8 family.

Table 44. Document revision history (continued)

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14-Oct-2010 | 11       | Added STM8L101F1 devices:  Modified Table 1: Device summary on page 1, Table 2:  STM8L101xx device feature summary on page 9 and Table 5:  Flash and RAM boundary addresses on page 24  Modified warning below Figure 3 on page 16 and belowTable 4:  STM8L101xx pin description on page 20  Modified Figure 52: STM8L101xx ordering information scheme on page 79  Modified text above Figure 32: Recommended NRST pin configuration on page 54  Modified Figure 32 on page 54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 02-Aug-2013 | 12       | Added "The RAM content is preserved" in halt mode Section 3.6: Low power modes Reformatted Figure 2: Standard 20-pin UFQFPN package pinout, Figure 3: 20-pin UFQFPN package pinout for STM8L101F1U6ATR, STM8L101F2U6ATR and STM8L101F3U6ATR part numbers, Figure 4: 20-pin TSSOP package pinout, Figure 4: 20-pin TSSOP package pinout, Figure 5: Standard 28-pin UFQFPN package pinout, Figure 6: 28-pin UFQFPN package pinout for STM8L101G3U6ATR and STM8L101G2U6ATR part numbers and Figure 7: 32-pin package pinout Corrected NRST/PA1 pin OD output capability in Table 4: STM8L101xx pin description and corrected note 2. and 4. Added note "Slope control of all GPIO can be programmed except" in Table 4: STM8L101xx pin description Added note under Table 5: Flash and RAM boundary addresses Replaced UM0320 with UM0470 in Section 7: Option bytes Updated OPT2 and OPT3 in Table 10: Option bytes Added additional note 2. references in Table 22: HSI oscillator characteristics Added note 2. under Table 17: Operating conditions at power-up / power-down and under Figure 32: Recommended NRST pin configuration Corrected 'SCK output' in Figure 35: SPI timing diagram - master mode(1) Added top view in Figure 43: UFQFPN20 3 x 3 mm 0.6 mm package outline Repositioned the package layout and footprint for all packages. Replaced "Standard ports" with "High sink ports" Replaced all "Data guaranteed, each individual device tested in production" notes with "Tested in production" |

| 31-Mar-2014 | 13       | Updated L3 value on <i>Table 42</i> , added note 2) and 3) on <i>Table 43</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |