Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                               |

|----------------------------|----------------------------------------------------------------------|

| Core Processor             | STM8                                                                 |

| Core Size                  | 8-Bit                                                                |

| Speed                      | 16MHz                                                                |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                    |

| Peripherals                | Infrared, POR, PWM, WDT                                              |

| Number of I/O              | 30                                                                   |

| Program Memory Size        | 8KB (8K x 8)                                                         |

| Program Memory Type        | FLASH                                                                |

| EEPROM Size                | 2K x 8                                                               |

| RAM Size                   | 1.5K x 8                                                             |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 3.6V                                                         |

| Data Converters            | -                                                                    |

| Oscillator Type            | Internal                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                        |

| Package / Case             | 32-UFQFN Exposed Pad                                                 |

| Supplier Device Package    | 32-UFQFPN (5x5)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm8l101k3u6 |

|                            |                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# List of tables

| Table 1.  | Device summary                                                                         | . 1 |

|-----------|----------------------------------------------------------------------------------------|-----|

| Table 2.  | STM8L101xx device feature summary                                                      | . 9 |

| Table 3.  | Legend/abbreviation for table 4                                                        | 20  |

| Table 4.  | STM8L101xx pin description                                                             | 20  |

| Table 5.  | Flash and RAM boundary addresses                                                       | 24  |

| Table 6.  | I/O Port hardware register map                                                         | 24  |

| Table 7.  | General hardware register map                                                          | 25  |

| Table 8.  | CPU/SWIM/debug module/interrupt controller registers                                   | 30  |

| Table 9.  | Interrupt mapping                                                                      | 32  |

| Table 10. | Option bytes                                                                           | 34  |

| Table 11. | Option byte description                                                                | 34  |

| Table 12. | Unique ID registers (96 bits)                                                          | 36  |

| Table 13. | Voltage characteristics                                                                | 38  |

| Table 14. | Current characteristics                                                                | 39  |

| Table 15. | Thermal characteristics.                                                               | 39  |

| Table 16. | General operating conditions                                                           | 40  |

| Table 17. | Operating conditions at power-up / power-down                                          | 41  |

| Table 18. | Total current consumption in Run mode                                                  | 42  |

| Table 19. | Total current consumption in Wait mode                                                 | 43  |

| Table 20. | Total current consumption and timing in Halt and Active-halt mode at                   |     |

|           | VDD = 1.65 V to 3.6 V                                                                  | 44  |

| Table 21. | Peripheral current consumption                                                         |     |

| Table 22. | HSI oscillator characteristics                                                         | 45  |

| Table 23. | LSI oscillator characteristics                                                         | 47  |

| Table 24. | RAM and hardware registers                                                             | 47  |

| Table 25. | Flash program memory                                                                   | 47  |

| Table 26. | I/O static characteristics                                                             | 48  |

| Table 27. | Output driving current (High sink ports)                                               | 51  |

| Table 28. | Output driving current (true open drain ports)                                         |     |

| Table 29. | Output driving current (PA0 with high sink LED driver capability)                      | 51  |

| Table 30. | NRST pin characteristics                                                               | 53  |

| Table 31. | SPI characteristics                                                                    | 55  |

| Table 32. | I2C characteristics                                                                    | 58  |

| Table 33. | Comparator characteristics                                                             | 59  |

| Table 34. | EMS data                                                                               |     |

| Table 35. | EMI data                                                                               | 61  |

| Table 36. | ESD absolute maximum ratings                                                           |     |

| Table 37. | Electrical sensitivities                                                               | 62  |

| Table 38. | Thermal characteristics.                                                               | 63  |

| Table 39. | UFQFPN32 - 32-lead ultra thin fine pitch quad flat no-lead package (5 x 5),            |     |

|           | package mechanical data                                                                |     |

| Table 40. | LQFP32- 32-pin low profile quad flat package (7x7), package mechanical data            | 68  |

| Table 41. | UFQFPN28 - 28-lead ultra thin fine pitch quad flat no-lead package (4 x 4),            |     |

|           | package mechanical data                                                                |     |

| Table 42. | UFQFPN20 - 20-lead ultra thin fine pitch quad flat package (3 x 3 mm) mechanical data. |     |

| Table 43. | TSSOP20 - 20-lead thin shrink small package mechanical data                            |     |

| Table 44. | Document revision history                                                              | 82  |

## 3.1 Central processing unit STM8

The 8-bit STM8 core is designed for code efficiency and performance.

It features 21 internal registers, 20 addressing modes including indexed, indirect and relative addressing, and 80 instructions.

## 3.2 Development tools

Development tools for the STM8 microcontrollers include:

- The STice emulation system offering tracing and code profiling

- The STVD high-level language debugger including C compiler, assembler and integrated development environment

- The STVP Flash programming software

The STM8 also comes with starter kits, evaluation boards and low-cost in-circuit debugging/programming tools.

## 3.3 Single wire data interface (SWIM) and debug module

The debug module with its single wire data interface (SWIM) permits non-intrusive real-time in-circuit debugging and fast memory programming.

The Single wire interface is used for direct access to the debugging module and memory programming. The interface can be activated in all device operation modes.

The non-intrusive debugging module features a performance close to a full-featured emulator. Beside memory and peripherals, also CPU operation can be monitored in real-time by means of shadow registers.

## 3.4 Interrupt controller

The STM8L101xx features a nested vectored interrupt controller:

- Nested interrupts with 3 software priority levels

- 26 interrupt vectors with hardware priority

- Up to 29 external interrupt sources on 10 vectors

- Trap and reset interrupts.

## 3.5 Memory

The STM8L101xx devices have the following main features:

- 1.5 Kbytes of RAM

- The EEPROM is divided into two memory arrays (see the STM8L reference manual for details on the memory mapping):

- Up to 8 Kbytes of low-density embedded Flash program including up to 2 Kbytes of data EEPROM. Data EEPROM and Flash program areas can be write protected independently by using the memory access security mechanism (MASS).

- 64 option bytes (one block) of which 5 bytes are already used for the device.

Error correction code is implemented on the EEPROM.

## 3.6 Low power modes

To minimize power consumption, the product features three low power modes:

- Wait mode: CPU clock stopped, selected peripherals at full clock speed.

- Active-halt mode: CPU and peripheral clocks are stopped. The programmable wakeup time is controlled by the AWU unit.

- Halt mode: CPU and peripheral clocks are stopped, the device remains powered on. The RAM content is preserved. Wakeup is triggered by an external interrupt.

## 3.7 Voltage regulators

The STM8L101xx embeds an internal voltage regulator for generating the 1.8 V power supply for the core and peripherals.

This regulator has two different modes: main voltage regulator mode (MVR) and low power voltage regulator mode (LPVR). When entering Halt or Active-halt modes, the system automatically switches from the MVR to the LPVR in order to reduce current consumption.

## 3.8 Clock control

The STM8L101xx embeds a robust clock controller. It is used to distribute the system clock to the core and the peripherals and to manage clock gating for low power modes. This system clock is a 16-MHz High Speed Internal RC oscillator (HSI RC), followed by a programmable prescaler.

In addition, a 38 kHz low speed internal RC oscillator is used by the independent watchdog (IWDG) and Auto-wakeup unit (AWU).

## 3.9 Independent watchdog

The independent watchdog (IWDG) peripheral can be used to resolve processor malfunctions due to hardware or software failures.

It is clocked by the 38 kHz LSI internal RC clock source, and thus stays active even in case of a CPU clock failure.

## 3.15 USART

The USART interface (USART) allows full duplex, asynchronous communications with external devices requiring an industry standard NRZ asynchronous serial data format. It offers a very wide range of baud rates.

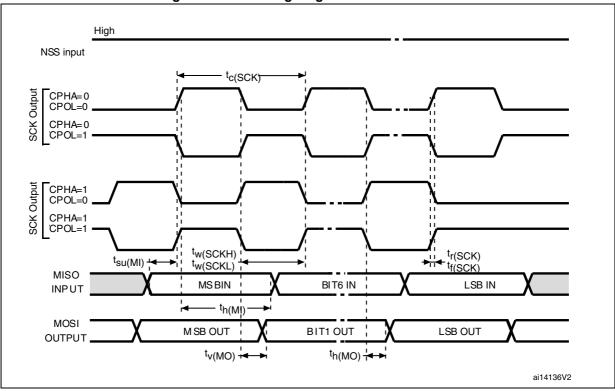

## 3.16 SPI

The serial peripheral interface (SPI) provides half/ full duplex synchronous serial communication with external devices. It can be configured as the master and in this case it provides the communication clock (SCK) to the external slave device. The interface can also operate in multi-master configuration.

## 3.17 I<sup>2</sup>C

The inter-integrated circuit (I2C) bus interface is designed to serve as an interface between the microcontroller and the serial  $I^2C$  bus. It provides multi-master capability, and controls all  $I^2C$  bus-specific sequencing, protocol, arbitration and timing. It manages standard and fast speed modes.

|                   | Pi                                    | n nu    | ımb               | er                                    |                    |                                                         |      |          | Input                   |                |                   | utput |    | ,                              |                                                                   |

|-------------------|---------------------------------------|---------|-------------------|---------------------------------------|--------------------|---------------------------------------------------------|------|----------|-------------------------|----------------|-------------------|-------|----|--------------------------------|-------------------------------------------------------------------|

| standard UFQFPN20 | UFQFPN20 with COMP_REF <sup>(1)</sup> | TSSOP20 | standard UFQFPN28 | UFQFPN28 with COMP_REF <sup>(1)</sup> | UFQFPN32 or LQFP32 | Pin name                                                | Type | floating | ndw                     | Ext. interrupt | High sink/source  | QO    | ЬP | Main function<br>(after reset) | Alternate function                                                |

| -                 | -                                     | -       | 26                | 26                                    | 30                 | PC5                                                     | I/O  | Х        | Х                       | Х              | HS                | Х     | Х  | Port C5                        | -                                                                 |

| -                 | -                                     | -       | 27                | 27                                    | 31                 | PC6                                                     | I/O  | Х        | Х                       | Х              | HS                | Х     | Х  | Port C6                        | -                                                                 |

| 20                | 20                                    | 3       | 28                | 28                                    | 32                 | PA0 <sup>(5)</sup> /SWIM/<br>BEEP/IR_TIM <sup>(6)</sup> | I/O  | x        | <b>X</b> <sup>(5)</sup> | x              | HS <sup>(6)</sup> | x     | x  | Port A0                        | SWIM input and<br>output /Beep<br>output/Timer Infrared<br>output |

#### Table 4. STM8L101xx pin description (continued)

1. Please refer to the warning below.

At power-up, the PA1/NRST pin is a reset input pin with pull-up. To be used as a general purpose pin (PA1), it can be configured only as a general purpose pin (PA1), it can be configured only as output push-pull, not neither as output opendrain nor as a general purpose input. Refer to Section *Configuring NRST/PA1 pin as general purpose output* in the STM8L reference manual (RM0013).

3. A pull-up is applied to PB0 and PB4 during the reset phase. These two pins are input floating after reset release.

4. In the open-drain output column, 'T' defines a true open-drain I/O (P-buffer, weak pull-up and protection diode to V<sub>DD</sub> are not implemented).

5. The PA0 pin is in input pull-up during the reset phase and after reset release.

6. High sink LED driver capability available on PA0.

Slope control of all GPIO pins can be programmed except true open drain pins and by default is limited to 2 MHz.

| Warning: | For the STM8L101F1U6ATR, STM8L101F2U6ATR,<br>STM8L101F3U6ATR, STM8L101G2U6ATR and<br>STM8L101G3U6ATR part numbers (devices with COMP_REF                                                                                                                                                                               |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | pin), all ports available on 32-pin packages must be<br>considered as active ports. To avoid spurious effects, the<br>user has to configure them as input pull-up. A small increase<br>in consumption (typ. < 300 $\mu$ A) may occur during the power<br>up and reset phase until these ports are properly configured. |

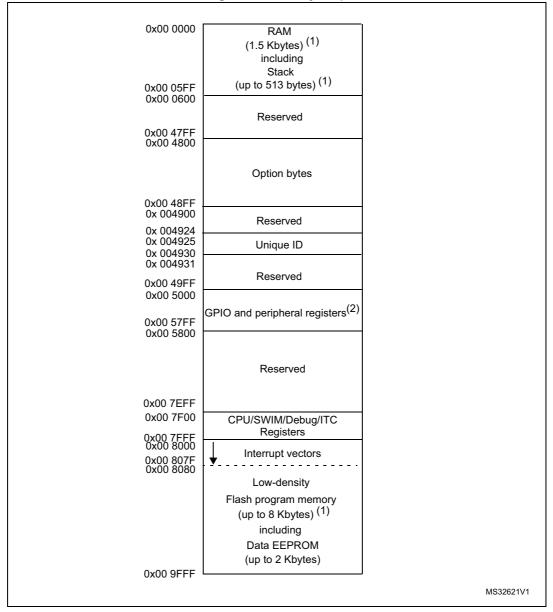

# 5 Memory and register map

Figure 8. Memory map

1. *Table 5* lists the boundary addresses for each memory size. The top of the stack is at the RAM end address.

2. Refer to *Table 7* for an overview of hardware register mapping, to *Table 6* for details on I/O port hardware registers, and to *Table 8* for information on CPU/SWIM/debug module controller registers.

| Memory area          | Size       | Start address | End address |  |  |  |  |

|----------------------|------------|---------------|-------------|--|--|--|--|

| RAM                  | 1.5 Kbytes | 0x00 0000     | 0x00 05FF   |  |  |  |  |

|                      | 2 Kbytes   | 0x00 8000     | 0x00 87FF   |  |  |  |  |

| Flash program memory | 4 Kbytes   | 0x00 8000     | 0x00 8FFF   |  |  |  |  |

|                      | 8 Kbytes   | 0x00 8000     | 0x00 9FFF   |  |  |  |  |

### Table 5. Flash and RAM boundary addresses

Note:

2 Kbytes of Data EEPROM is only available on devices with 8 Kbytes flash program memory.

|      | Table 6. I/O Port hardware register map |               |  |  |

|------|-----------------------------------------|---------------|--|--|

| lock | Register label                          | Register name |  |  |

|      |                                         |               |  |  |

| Address   | Block  | Register label | Register name                     | Reset<br>status |

|-----------|--------|----------------|-----------------------------------|-----------------|

| 0x00 5000 |        | PA_ODR         | Port A data output latch register | 0x00            |

| 0x00 5001 |        | PA_IDR         | Port A input pin value register   | 0xxx            |

| 0x00 5002 | Port A | PA_DDR         | Port A data direction register    | 0x00            |

| 0x00 5003 |        | PA_CR1         | Port A control register 1         | 0x00            |

| 0x00 5004 |        | PA_CR2         | Port A control register 2         | 0x00            |

| 0x00 5005 |        | PB_ODR         | Port B data output latch register | 0x00            |

| 0x00 5006 |        | PB_IDR         | Port B input pin value register   | 0xxx            |

| 0x00 5007 | Port B | PB_DDR         | Port B data direction register    | 0x00            |

| 0x00 5008 |        | PB_CR1         | Port B control register 1         | 0x00            |

| 0x00 5009 |        | PB_CR2         | Port B control register 2         | 0x00            |

| 0x00 500A |        | PC_ODR         | Port C data output latch register | 0x00            |

| 0x00 500B |        | PC_IDR         | Port C input pin value register   | 0xxx            |

| 0x00 500C | Port C | PC_DDR         | Port C data direction register    | 0x00            |

| 0x00 500D |        | PC_CR1         | Port C control register 1         | 0x00            |

| 0x00 500E |        | PC_CR2         | Port C control register 2         | 0x00            |

| 0x00 500F |        | PD_ODR         | Port D data output latch register | 0x00            |

| 0x00 5010 |        | PD_IDR         | Port D input pin value register   | 0xxx            |

| 0x00 5011 | Port D | PD_DDR         | Port D data direction register    | 0x00            |

| 0x00 5012 |        | PD_CR1         | Port D control register 1         | 0x00            |

| 0x00 5013 |        | PD_CR2         | Port D control register 2         | 0x00            |

| Table 7. General hardware register map |                          |                |                                                  |                 |  |

|----------------------------------------|--------------------------|----------------|--------------------------------------------------|-----------------|--|

| Address                                | Block                    | Register label | Register name                                    | Reset<br>status |  |

| 0x00 5050                              |                          | FLASH_CR1      | Flash control register 1                         | 0x00            |  |

| 0x00 5051                              |                          | FLASH_CR2      | Flash control register 2                         | 0x00            |  |

| 0x00 5052                              | Flash                    | FLASH_PUKR     | Flash Program memory unprotection register       | 0x00            |  |

| 0x00 5053                              |                          | FLASH_DUKR     | Data EEPROM unprotection register                | 0x00            |  |

| 0x00 5054                              |                          | FLASH_IAPSR    | Flash in-application programming status register | 0xX0            |  |

| 0x00 5055<br>to<br>0x00 509F           |                          | Я              | Reserved area (75 bytes)                         |                 |  |

| 0x00 50A0                              |                          | EXTI_CR1       | External interrupt control register 1            | 0x00            |  |

| 0x00 50A1                              |                          | EXTI_CR2       | External interrupt control register 2            | 0x00            |  |

| 0x00 50A2                              | ITC-EXTI                 | EXTI_CR3       | External interrupt control register 3            | 0x00            |  |

| 0x00 50A3                              | IIC-EAII                 | EXTI_SR1       | External interrupt status register 1             | 0x00            |  |

| 0x00 50A4                              |                          | EXTI_SR2       | External interrupt status register 2             | 0x00            |  |

| 0x00 50A5                              |                          | EXTI_CONF      | External interrupt port select register          | 0x00            |  |

| 0x00 50A6                              | WFE                      | WFE_CR1        | WFE control register 1                           | 0x00            |  |

| 0x00 50A7                              |                          | WFE_CR2        | WFE control register 2                           | 0x00            |  |

| 0x00 50A8<br>to<br>0x00 50AF           |                          | F              | Reserved area (8 bytes)                          |                 |  |

| 0x00 50B0                              | RST                      | RST_CR         | Reset control register                           | 0x00            |  |

| 0x00 50B1                              | ROI                      | RST_SR         | Reset status register                            | 0x01            |  |

| 0x00 50B2<br>to<br>0x00 50BF           |                          | R              | Reserved area (14 bytes)                         |                 |  |

| 0x00 50C0                              |                          | CLK_CKDIVR     | Clock divider register                           | 0x03            |  |

| 0x00 50C1<br>to<br>0x00 50C2           | CLK                      |                | Reserved area (2 bytes)                          |                 |  |

| 0x00 50C3                              |                          | CLK_PCKENR     | Peripheral clock gating register                 | 0x00            |  |

| 0x00 50C4                              | 1                        |                | Reserved (1 byte)                                |                 |  |

| 0x00 50C5                              | 1                        | CLK_CCOR       | Configurable clock control register              | 0x00            |  |

| 0x00 50C6<br>to<br>0x00 50DF           | Reserved area (25 bytes) |                |                                                  |                 |  |

Table 7. General hardware register map

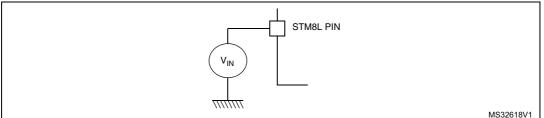

### 9.1.5 Pin input voltage

The input voltage measurement on a pin of the device is described in Figure 10.

#### Figure 10. Pin input voltage

## 9.2 Absolute maximum ratings

Stresses above the absolute maximum ratings listed in *Table 13: Voltage characteristics*, *Table 14: Current characteristics* and *Table 15: Thermal characteristics* may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability. The device mission profile is compliant with the JEDEC JESD47 qualification standard; extended mission profiles are available on demand.

| Symbol                            | Ratings                                                            | Min                                                                    | Max                   | Unit |

|-----------------------------------|--------------------------------------------------------------------|------------------------------------------------------------------------|-----------------------|------|

| V <sub>DD</sub> - V <sub>SS</sub> | External supply voltage                                            | -0.3                                                                   | 4.0                   |      |

| V <sub>IN</sub>                   | Input voltage on true open drain pins (PC0 and PC1) <sup>(1)</sup> | V <sub>SS</sub> -0.3                                                   | V <sub>DD</sub> + 4.0 | v    |

|                                   | Input voltage on any other pin <sup>(2)</sup>                      | V <sub>SS</sub> -0.3                                                   | 4.0                   |      |

| V <sub>ESD</sub>                  | Electrostatic discharge voltage                                    | see Absolute maximum<br>ratings (electrical sensitivity)<br>on page 61 |                       | -    |

#### Table 13. Voltage characteristics

1. Positive injection is not possible on these I/Os.  $V_{\rm IN}$  maximum must always be respected.  $I_{\rm INJ(PIN)}$  must never be exceeded. A negative injection is induced by  $V_{\rm IN}{<}V_{SS}$ .

I<sub>INJ(PIN)</sub> must never be exceeded. This is implicitly insured if V<sub>IN</sub> maximum is respected. If V<sub>IN</sub> maximum cannot be respected, the injection current must be limited externally to the I<sub>INJ(PIN)</sub> value. A positive injection is induced by V<sub>IN</sub>>V<sub>DD</sub> while a negative injection is induced by V<sub>IN</sub><V<sub>SS</sub>.

### 9.3.2 Power-up / power-down operating conditions

| r                                  |                                |                        |      |     |                     |      |  |  |

|------------------------------------|--------------------------------|------------------------|------|-----|---------------------|------|--|--|

| Symbol                             | Parameter                      | Conditions             | Min  | Тур | Max                 | Unit |  |  |

| t <sub>VDD</sub>                   | V <sub>DD</sub> rise time rate | -                      | 20   | -   | 1300                | µs/V |  |  |

| t <sub>TEMP</sub>                  | Reset release delay            | V <sub>DD</sub> rising | -    | 1   | -                   | ms   |  |  |

| V <sub>POR</sub> <sup>(1)(2)</sup> | Power on reset threshold       | -                      | 1.35 | -   | 1.65 <sup>(3)</sup> | V    |  |  |

| V <sub>PDR</sub> <sup>(1)(2)</sup> | Power down reset threshold     | -                      | 1.40 | -   | 1.60                | V    |  |  |

Table 17. Operating conditions at power-up / power-down

1. Data based on characterization results, not tested in production.

2. Correct device reset during power on sequence is guaranteed when  $t_{VDD[max]}$  is respected. External reset circuit is recommended to ensure correct device reset during power down, when  $V_{PDR} < V_{DD} < V_{DD[min]}$ .

3. Tested in production.

### 9.3.3 Supply current characteristics

### **Total current consumption**

The MCU is placed under the following conditions:

- All I/O pins in input mode with a static value at V<sub>DD</sub> or V<sub>SS</sub> (no load)

- All peripherals are disabled except if explicitly mentioned.

Subject to general operating conditions for  $V_{DD}$  and  $T_A$ .

### Current consumption of on-chip peripherals

Measurement made for f<sub>MASTER</sub> = from 2 MHz to 16 MHz

| Symbol                           | Parameter                                | Typ. V <sub>DD</sub> = 3.0 V | Unit   |

|----------------------------------|------------------------------------------|------------------------------|--------|

| I <sub>DD(TIM2)</sub>            | TIM2 supply current <sup>(1)</sup>       | 9                            |        |

| I <sub>DD(TIM3)</sub>            | TIM3 supply current <sup>(1)</sup>       | 9                            |        |

| I <sub>DD(TIM4)</sub>            | TIM4 timer supply current <sup>(1)</sup> | 4                            |        |

| I <sub>DD(USART)</sub>           | USART supply current <sup>(2)</sup>      | 7                            | µA/MHz |

| I <sub>DD(SPI)</sub>             | SPI supply current <sup>(2)</sup>        | 4                            |        |

| I <sub>DD(I<sup>2</sup>C1)</sub> | I2C supply current <sup>(2)</sup>        | 4                            |        |

| I <sub>DD(COMP)</sub>            | Comparator supply current <sup>(2)</sup> | 20                           | μA     |

Data based on a differential I<sub>DD</sub> measurement between all peripherals off and a timer counter running at 16 MHz. The CPU is in Wait mode in both cases. No IC/OC programmed, no I/O pin toggling. Not tested in production.

Data based on a differential I<sub>DD</sub> measurement between the on-chip peripheral when kept under reset and not clocked and the on-chip peripheral when clocked and not kept under reset. The CPU is in Wait mode in both cases. No I/O pin toggling. Not tested in production.

### 9.3.4 Clock and timing characteristics

### Internal clock sources

Subject to general operating conditions for  $V_{\text{DD}}$  and  $T_{\text{A}}.$

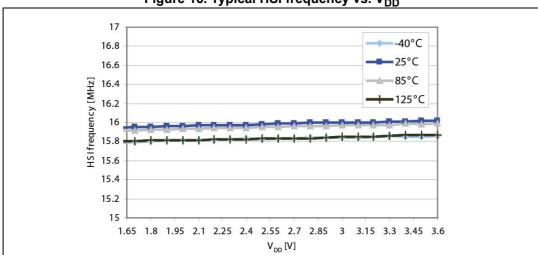

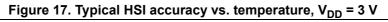

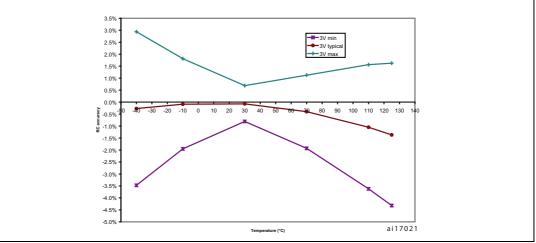

### High speed internal RC oscillator (HSI)

| Table 22. HSI oscillato | r characteristics <sup>(1)</sup> |

|-------------------------|----------------------------------|

|-------------------------|----------------------------------|

| Symbol               | Parameter                          | Conditions                                                           | Min                 | Тур | Max                | Unit |

|----------------------|------------------------------------|----------------------------------------------------------------------|---------------------|-----|--------------------|------|

| f <sub>HSI</sub>     | Frequency                          | V <sub>DD</sub> = 3.0 V                                              | -                   | 16  | -                  | MHz  |

|                      |                                    | V <sub>DD</sub> = 3.0 V, T <sub>A</sub> = 25 °C                      | -1                  | -   | 1                  | %    |

|                      |                                    | V <sub>DD</sub> = 3.0 V, -10 °C ≤T <sub>A</sub> ≤85 °C               | -2.5 <sup>(2)</sup> | -   | 2 <sup>(2)</sup>   | %    |

| ACC <sub>HSI</sub>   | Accuracy of HSI                    | V <sub>DD</sub> = 3.0 V, -10 °C ≤T <sub>A</sub> ≤ 125 °C             | -4.5 <sup>(2)</sup> | -   | 2 <sup>(2)</sup>   | %    |

| ACCHSI               | oscillator<br>(factory calibrated) | V <sub>DD</sub> = 3.0 V, 0 °C ≤T <sub>A</sub> ≤ 55 °C                | -1.5 <sup>(2)</sup> | -   | 1.5 <sup>(2)</sup> | %    |

|                      |                                    | V <sub>DD</sub> = 3.0 V, -10 °C ≤T <sub>A</sub> ≤ 70 °C              | -2 <sup>(2)</sup>   | -   | 2 <sup>(2)</sup>   | %    |

|                      |                                    | 1.65 V ≤ V <sub>DD</sub> ≤ 3.6 V,<br>-40 °C ≤ T <sub>A</sub> ≤125 °C | -4.5 <sup>(2)</sup> | -   | 3 <sup>(2)</sup>   | %    |

| I <sub>DD(HSI)</sub> | HSI oscillator power consumption   | -                                                                    | -                   | 70  | 100 <sup>(2)</sup> | μA   |

1.  $V_{DD}$  = 3.0 V,  $T_A$  = -40 to 125 °C unless otherwise specified.

2. Data based on characterization results, not tested in production.

Figure 16. Typical HSI frequency vs. V<sub>DD</sub>

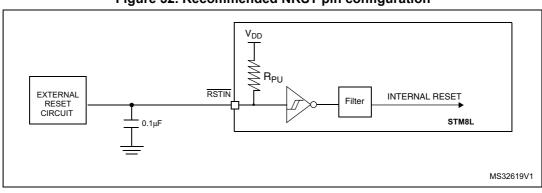

### **NRST** pin

The NRST pin input driver is CMOS. A permanent pull-up is present.  $R_{PU(NRST)}$  has the same value as  $R_{PU}$  (see *Table 26 on page 48*).

Subject to general operating conditions for  $V_{\text{DD}}$  and  $T_{\text{A}}$  unless otherwise specified.

| Symbol                | Parameter                                       | Conditions             | Min      | Тур <sup>(1)</sup> | Мах                  | Unit |

|-----------------------|-------------------------------------------------|------------------------|----------|--------------------|----------------------|------|

| V <sub>IL(NRST)</sub> | NRST input low level voltage <sup>(1)</sup>     | -                      | $V_{SS}$ | -                  | 0.8                  |      |

| V <sub>IH(NRST)</sub> | NRST input high level voltage <sup>(1)</sup>    | -                      | 1.4      | -                  | V <sub>DD</sub>      | V    |

| V <sub>OL(NRST)</sub> | NRST output low level voltage                   | I <sub>OL</sub> = 2 mA | -        | -                  | V <sub>DD</sub> -0.8 |      |

| R <sub>PU(NRST)</sub> | NRST pull-up equivalent resistor <sup>(2)</sup> | -                      | 30       | 45                 | 60                   | kΩ   |

| V <sub>F(NRST)</sub>  | NRST input filtered pulse <sup>(3)</sup>        | -                      | -        | -                  | 50                   | ns   |

| t <sub>OP(NRST)</sub> | NRST output pulse width                         | -                      | 20       | -                  | -                    | ns   |

| V <sub>NF(NRST)</sub> | NRST input not filtered pulse <sup>(3)</sup>    | -                      | 300      | -                  | _                    | ns   |

Table 30. NRST pin characteristics

1. Data based on characterization results, not tested in production.

The R<sub>PU</sub> pull-up equivalent resistor is based on a resistive transistor (*Figure 30*). Corresponding I<sub>PU</sub> current characteristics are described in *Figure 31*.

3. Data guaranteed by design, not tested in production.

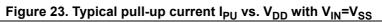

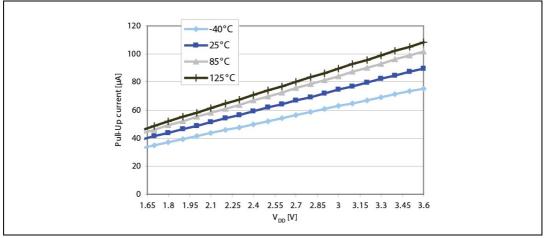

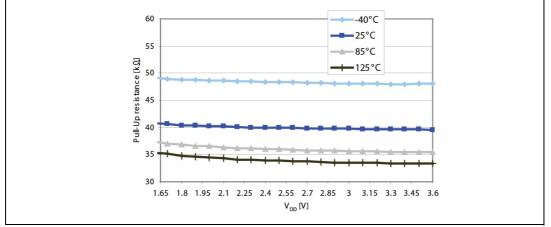

Figure 31. Typical NRST pull-up current I<sub>pu</sub> vs. V<sub>DD</sub>

The reset network shown in *Figure 32* protects the device against parasitic resets. The user must ensure that the level on the NRST pin can go below the  $V_{IL}$  max. level specified in *Table 30*. Otherwise the reset is not taken into account internally. For power consumption-sensitive applications, the capacity of the external reset capacitor can be reduced to limit the charge/discharge current. If the NRST signal is used to reset the external circuitry, the user must pay attention to the charge/discharge time of the external capacitor to meet the reset timing conditions of the external devices. The minimum recommended capacity is 10 nF.

#### Figure 32. Recommended NRST pin configuration

1. Correct device reset during power on sequence is guaranteed when t<sub>VDD[max]</sub> is respected.

External reset circuit is recommended to ensure correct device reset during power down, when V<sub>PDR</sub> < V<sub>DD</sub> < V<sub>DD[min]</sub>.

1. Measurement points are done at CMOS levels:  $0.3V_{DD}$  and  $0.7V_{DD}$ .

### Inter IC control interface (I2C)

Subject to general operating conditions for  $V_{\text{DD}},\,f_{\text{MASTER}},$  and  $T_{\text{A}}$  unless otherwise specified.

The STM8L I<sup>2</sup>C interface meets the requirements of the Standard I<sup>2</sup>C communication protocol described in the following table with the restriction mentioned below:

Refer to I/O port characteristics for more details on the input/output alternate function characteristics (SDA and SCL).

| Symbol                                     | Parameter                               |                    | rd mode<br>:C      | Fast mo            | Unit               |    |

|--------------------------------------------|-----------------------------------------|--------------------|--------------------|--------------------|--------------------|----|

|                                            |                                         | Min <sup>(2)</sup> | Max <sup>(2)</sup> | Min <sup>(2)</sup> | Max (2)            |    |

| t <sub>w(SCLL)</sub>                       | SCL clock low time                      | 4.7                | -                  | 1.3                | -                  |    |

| t <sub>w(SCLH)</sub>                       | SCL clock high time                     | 4.0                | -                  | 0.6                | -                  | μs |

| t <sub>su(SDA)</sub>                       | SDA setup time                          | 250                | -                  | 100                | -                  |    |

| t <sub>h(SDA)</sub>                        | SDA data hold time                      | 0 (3)              | -                  | 0 (4)              | 900 <sup>(3)</sup> |    |

| t <sub>r(SDA)</sub><br>t <sub>r(SCL)</sub> | SDA and SCL rise time                   | -                  | 1000               | -                  | 300                | ns |

| t <sub>f(SDA)</sub><br>t <sub>f(SCL)</sub> | SDA and SCL fall time                   | -                  | 300                | -                  | 300                |    |

| t <sub>h(STA)</sub>                        | START condition hold time               | 4.0                | -                  | 0.6                | -                  |    |

| t <sub>su(STA)</sub>                       | Repeated START condition setup time     | 4.7                | -                  | 0.6                | -                  | μs |

| t <sub>su(STO)</sub>                       | STOP condition setup time               | 4.0                | -                  | 0.6                | -                  | μs |

| t <sub>w(STO:STA)</sub>                    | STOP to START condition time (bus free) | 4.7                | -                  | 1.3                | -                  | μs |

| Cb                                         | Capacitive load for each bus line       | -                  | 400                | -                  | 400                | pF |

| Table 32 | . I2C | characteristics |

|----------|-------|-----------------|

|----------|-------|-----------------|

1. f<sub>SCK</sub> must be at least 8 MHz to achieve max fast I<sup>2</sup>C speed (400 kHz).

2. Data based on standard I<sup>2</sup>C protocol requirement, not tested in production.

3. The maximum hold time of the START condition has only to be met if the interface does not stretch the low period of SCL signal.

4. The device must internally provide a hold time of at least 300 ns for the SDA signal in order to bridge the undefined region of the falling edge of SCL).

Note:

For speeds around 200 kHz, achieved speed can have  $\pm$ 5% tolerance For other speed ranges, achieved speed can have  $\pm$ 2% tolerance The above variations depend on the accuracy of the external components used.

| Symbol | millimeters |       |       | inches <sup>(1)</sup> |        |        |  |

|--------|-------------|-------|-------|-----------------------|--------|--------|--|

|        | Min         | Тур   | Мах   | Min                   | Тур    | Max    |  |

| D      | -           | 3.000 | -     | -                     | 0.1181 | -      |  |

| E      | -           | 3.000 | -     | -                     | 0.1181 | -      |  |

| А      | 0.500       | 0.550 | 0.600 | 0.0197                | 0.0217 | 0.0236 |  |

| A1     | 0.000       | 0.020 | 0.050 | 0.0000                | 0.0008 | 0.0020 |  |

| A3     | -           | 0.152 | -     | -                     | 0.0060 | -      |  |

| е      | -           | 0.500 | -     | -                     | 0.0197 | -      |  |

| L1     | 0.500       | 0.550 | 0.600 | 0.0197                | 0.0217 | 0.0236 |  |

| L2     | 0.300       | 0.350 | 0.400 | 0.0118                | 0.0138 | 0.0157 |  |

| L3     | -           | 0.375 | -     | -                     | 0.0148 | -      |  |

| L4     | -           | 0.200 | -     | -                     | 0.0079 | -      |  |

| L5     | -           | 0.150 | -     | -                     | 0.0059 | -      |  |

| b      | 0.180       | 0.250 | 0.300 | 0.0071                | 0.0098 | 0.0118 |  |

| ddd    | -           | 0.050 | -     | -                     | 0.0020 | -      |  |

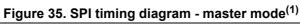

### Table 42. UFQFPN20 - 20-lead ultra thin fine pitch quad flat package (3 x 3 mm) mechanical data

1. Values in inches are rounded to 4 decimal digits

### Figure 47. UFQFPN20 recommended footprint

1. Dimensions are in millimeters.

## 12.2 Software tools

STM8 development tools are supported by a complete, free software package from STMicroelectronics that includes ST Visual Develop (STVD) IDE and the ST Visual Programmer (STVP) software interface. STVD provides seamless integration of the Cosmic and Raisonance C compilers for STM8. A free version that outputs up to 32 Kbytes of code is available.

### 12.2.1 STM8 toolset

**STM8** toolset with STVD integrated development environment and STVP programming software is available for free download at *www.st.com*. This package includes:

ST Visual Develop - Full-featured integrated development environment from ST, featuring

- Seamless integration of C and ASM toolsets

- Full-featured debugger

- Project management

- Syntax highlighting editor

- Integrated programming interface

- Support of advanced emulation features for STice such as code profiling and coverage

**ST Visual Programmer (STVP)** – Easy-to-use, unlimited graphical interface allowing read, write and verify of the STM8 microcontroller Flash program memory, data EEPROM and option bytes. STVP also offers project mode for saving programming configurations and automating programming sequences.

### 12.2.2 C and assembly toolchains

Control of C and assembly toolchains is seamlessly integrated into the STVD integrated development environment, making it possible to configure and control the building of user application directly from an easy-to-use graphical interface.

Available toolchains include:

- Cosmic C compiler for STM8 One free version that outputs up to 32 Kbytes of code is available. For more information, see www.cosmic-software.com.

- Raisonance C compiler for STM8 One free version that outputs up to 32 Kbytes of code. For more information, see www.raisonance.com.

- **STM8 assembler linker** Free assembly toolchain included in the STVD toolset, which allows the user to assemble and link their application source code.

## 12.3 Programming tools

During the development cycle, STice provides in-circuit programming of the STM8 Flash microcontroller on the user's application board via the SWIM protocol. Additional tools are to include a low-cost in-circuit programmer as well as ST socket boards, which provide dedicated programming platforms with sockets for programming the STM8.

For production environments, programmers will include a complete range of gang and automated programming solutions from third-party tool developers already supplying programmers for the STM8 family.

#### IMPORTANT NOTICE – PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2016 STMicroelectronics – All rights reserved