Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

# **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                               |

|--------------------------------|---------------------------------------------------------------|

| Product Status                 | Active                                                        |

| Number of LABs/CLBs            | 1920                                                          |

| Number of Logic Elements/Cells | 17280                                                         |

| Total RAM Bits                 | 442368                                                        |

| Number of I/O                  | 221                                                           |

| Number of Gates                | 1000000                                                       |

| Voltage - Supply               | 1.14V ~ 1.26V                                                 |

| Mounting Type                  | Surface Mount                                                 |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                               |

| Package / Case                 | 320-BGA                                                       |

| Supplier Device Package        | 320-FBGA (19x19)                                              |

| Purchase URL                   | https://www.e-xfl.com/product-detail/xilinx/xc3s1000-4fgg320c |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

According to Figure 7, the clock line OTCLK1 connects the CK inputs of the upper registers on the output and three-state paths. Similarly, OTCLK2 connects the CK inputs for the lower registers on the output and three-state paths. The upper and lower registers on the input path have independent clock lines: ICLK1 and ICLK2. The enable line OCE connects the CE inputs of the upper and lower registers on the output path. Similarly, TCE connects the CE inputs for the register pair on the three-state path and ICE does the same for the register pair on the input path. The Set/Reset (SR) line entering the IOB is common to all six registers, as is the Reverse (REV) line.

Each storage element supports numerous options in addition to the control over signal polarity described in the IOB Overview section. These are described in Table 6.

Table 6: Storage Element Options

| Option Switch | Function                                                                                                                                                                                                                                     | Specificity                                                                                                                                                                               |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FF/Latch      | Chooses between an edge-sensitive flip-flop or a level-sensitive latch                                                                                                                                                                       | Independent for each storage element.                                                                                                                                                     |

| SYNC/ASYNC    | Determines whether SR is synchronous or asynchronous                                                                                                                                                                                         | Independent for each storage element.                                                                                                                                                     |

| SRHIGH/SRLOW  | Determines whether SR acts as a Set, which forces the storage element to a logic "1" (SRHIGH) or a Reset, which forces a logic "0" (SRLOW).                                                                                                  | Independent for each storage element, except when using FDDR. In the latter case, the selection for the upper element (OFF1 or TFF2) applies to both elements.                            |

| INIT1/INIT0   | In the event of a Global Set/Reset, after configuration or upon activation of the GSR net, this switch decides whether to set or reset a storage element. By default, choosing SRLOW also selects INIT0; choosing SRHIGH also selects INIT1. | Independent for each storage element, except when using FDDR. In the latter case, selecting INIT0 for one element applies to both elements (even though INIT1 is selected for the other). |

### **Double-Data-Rate Transmission**

Double-Data-Rate (DDR) transmission describes the technique of synchronizing signals to both the rising and falling edges of the clock signal. Spartan-3 devices use register-pairs in all three IOB paths to perform DDR operations.

The pair of storage elements on the IOB's Output path (OFF1 and OFF2), used as registers, combine with a special multiplexer to form a DDR D-type flip-flop (FDDR). This primitive permits DDR transmission where output data bits are synchronized to both the rising and falling edges of a clock. It is possible to access this function by placing either an FDDRRSE or an FDDRCPE component or symbol into the design. DDR operation requires two clock signals (50% duty cycle), one the inverted form of the other. These signals trigger the two registers in alternating fashion, as shown in Figure 8. Commonly, the Digital Clock Manager (DCM) generates the two clock signals by mirroring an incoming signal, then shifting it 180 degrees. This approach ensures minimal skew between the two signals.

The storage-element-pair on the Three-State path (TFF1 and TFF2) can also be combined with a local multiplexer to form an FDDR primitive. This permits synchronizing the output enable to both the rising and falling edges of a clock. This DDR operation is realized in the same way as for the output path.

The storage-element-pair on the input path (IFF1 and IFF2) allows an I/O to receive a DDR signal. An incoming DDR clock signal triggers one register and the inverted clock signal triggers the other register. In this way, the registers take turns capturing bits of the incoming DDR data signal.

Table 13: Block RAM Port Signals (Cont'd)

| Signal<br>Description    | Port A<br>Signal Name | Port B<br>Signal Name | Direction | Function                                                                                                                                                                                                                                                                                                                                                          |

|--------------------------|-----------------------|-----------------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Data Output Bus          | DOA                   | DOB                   | Output    | Basic data access occurs whenever WE is inactive. The DO outputs mirror the data stored in the addressed memory location.                                                                                                                                                                                                                                         |

|                          |                       |                       |           | Data access with WE asserted is also possible if one of the following two attributes is chosen: WRITE_FIRST and READ_FIRST. WRITE_FIRST simultaneously presents the new input data on the DO output port and writes the data to the address RAM location. READ_FIRST presents the previously stored RAM data on the DO output port while writing new data to RAM. |

|                          |                       |                       |           | A third attribute, NO_CHANGE, latches the DO outputs upon the assertion of WE.                                                                                                                                                                                                                                                                                    |

|                          |                       |                       |           | It is possible to configure a port's total data path width (w) to be 1, 2, 4, 9, 18, or 36 bits. This selection applies to both the DI and DO paths. See the DI signal description.                                                                                                                                                                               |

| Parity Data<br>Output(s) | DOPA                  | DOPB                  | Output    | Parity inputs represent additional bits included in the data input path to support error detection. The number of parity bits "p" included in the DI (same as for the DO bus) depends on a port's total data path width (w). See Table 14.                                                                                                                        |

| Write Enable             | WEA                   | WEB                   | Input     | When asserted together with EN, this input enables the writing of data to the RAM. In this case, the data access attributes WRITE_FIRST, READ_FIRST or NO_CHANGE determines if and how data is updated on the DO outputs. See the DO signal description.  When WE is inactive with EN asserted, read operations are still                                         |

|                          |                       |                       |           | possible. In this case, a transparent latch passes data from the addressed memory location to the DO outputs.                                                                                                                                                                                                                                                     |

| Clock Enable             | ENA                   | ENB                   | Input     | When asserted, this input enables the CLK signal to synchronize Block RAM functions as follows: the writing of data to the DI inputs (when WE is also asserted), the updating of data at the DO outputs as well as the setting/resetting of the DO output latches.                                                                                                |

|                          |                       |                       |           | When de-asserted, the above functions are disabled.                                                                                                                                                                                                                                                                                                               |

| Set/Reset                | SSRA                  | SSRB                  | Input     | When asserted, this pin forces the DO output latch to the value that the SRVAL attribute is set to. A Set/Reset operation on one port has no effect on the other ports functioning, nor does it disturb the memory's data contents. It is synchronized to the CLK signal.                                                                                         |

| Clock                    | CLKA                  | CLKB                  | Input     | This input accepts the clock signal to which read and write operations are synchronized. All associated port inputs are required to meet setup times with respect to the clock signal's active edge. The data output bus responds after a clock-to-out delay referenced to the clock signal's active edge.                                                        |

# **Port Aspect Ratios**

On a given port, it is possible to select a number of different possible widths (w - p) for the DI/DO buses as shown in Table 14. These two buses always have the same width. This data bus width selection is independent for each port. If the data bus width of Port A differs from that of Port B, the Block RAM automatically performs a bus-matching function. When data are written to a port with a narrow bus, then read from a port with a wide bus, the latter port will effectively combine "narrow" words to form "wide" words. Similarly, when data are written into a port with a wide bus, then read from a port with a narrow bus, the latter port will divide "wide" words to form "narrow" words. When the data bus width is eight bits or greater, extra parity bits become available. The width of the total data path (w) is the sum of the DI/DO bus width and any parity bits (p).

The width selection made for the DI/DO bus determines the number of address lines according to the relationship expressed below:

$$r = 14 - [\log(w-p)/\log(2)]$$

Equation 1

In turn, the number of address lines delimits the total number (n) of addressable locations or depth according to the following equation:

$n = 2^r$  Equation 2

#### Notes:

1. There are two ways to use the DONE line. First, one may set the BitGen option DriveDone to "Yes" only for the last FPGA to be configured in the chain shown above (or for the single FPGA as may be the case). This enables the DONE pin to drive High; thus, no pull-up resistor is necessary. DriveDone is set to "No" for the remaining FPGAs in the chain. Second, DriveDone can be set to "No" for all FPGAs. Then all DONE lines are open-drain and require the pull-up resistor shown in grey. In most cases, a value between  $3.3K\Omega$  to  $4.7K\Omega$  is sufficient. However, when using DONE synchronously with a long chain of FPGAs, cumulative capacitance may necessitate lower resistor values (e.g. down to  $330\Omega$ ) in order to ensure a rise time within one clock cycle.

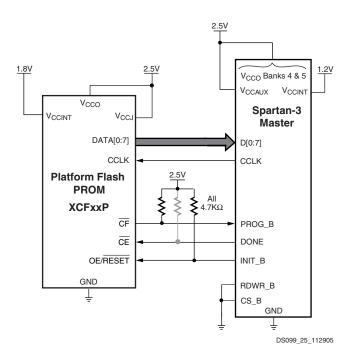

Figure 28: Connection Diagram for Master Parallel Configuration

#### **Master Parallel Mode**

In this mode, the FPGA configures from byte-wide data, and the FPGA supplies the CCLK configuration clock. In Master configuration modes, CCLK behaves as a bidirectional I/O pin. Timing is similar to the Slave Parallel mode except that CCLK is supplied by the FPGA. The device connections are shown in Figure 28.

### **Boundary-Scan (JTAG) Mode**

In Boundary-Scan mode, dedicated pins are used for configuring the FPGA. The configuration is done entirely through the IEEE 1149.1 Test Access Port (TAP). FPGA configuration using the Boundary-Scan mode is compatible with the IEEE Std 1149.1-1993 standard and IEEE Std 1532 for In-System Configurable (ISC) devices.

Configuration through the boundary-scan port is always available, regardless of the selected configuration mode. In some cases, however, the mode pin setting may affect proper programming of the device due to various interactions. For example, if the mode pins are set to Master Serial or Master Parallel mode, and the associated PROM is already programmed with a valid configuration image, then there is potential for configuration interference between the JTAG and PROM data. Selecting the Boundary-Scan mode disables the other modes and is the most reliable mode when programming via JTAG.

### **Configuration Sequence**

The configuration of Spartan-3 devices is a three-stage process that occurs after Power-On Reset or the assertion of PROG\_B. POR occurs after the  $V_{CCINT}$ ,  $V_{CCAUX}$ , and  $V_{CCO}$  Bank 4 supplies have reached their respective maximum input threshold levels (see Table 29, page 59). After POR, the three-stage process begins.

First, the configuration memory is cleared. Next, configuration data is loaded into the memory, and finally, the logic is activated by a start-up process. A flow diagram for the configuration sequence of the Serial and Parallel modes is shown in Figure 29. The flow diagram for the Boundary-Scan configuration sequence appears in Figure 30.

# PRODUCT NOT RECOMMENDED FOR NEW DESIGNS

Initial Spartan-3 FPGA mask revisions have a limit on how fast the  $V_{CCO}$  supply can ramp. The minimum allowed  $V_{CCO}$  ramp rate appears as  $T_{CCO}$  in Table 30, page 60. The minimum rate is affected by the package inductance. Consequently, the ball grid array and chip-scale packages (CP132, FT256, FG456, FG676, and FG900) allow a faster ramp rate than the quad-flat packages (VQ100, TQ144, and PQ208).

# **Configuration Data Retention, Brown-Out**

The FPGA's configuration data is stored in robust CMOS configuration latches. The data in these latches is retained even when the voltages drop to the minimum levels necessary to preserve RAM contents. This is specified in Table 31, page 60.

If, after configuration, the  $V_{CCAUX}$  or  $V_{CCINT}$  supply drops below its data retention voltage, clear the current device configuration using one of the following methods:

- Force the V<sub>CCAUX</sub> or V<sub>CCINT</sub> supply voltage below the minimum Power On Reset (POR) voltage threshold Table 29, page 59).

- Assert PROG\_B Low.

The POR circuit does not monitor the VCCO\_4 supply after configuration. Consequently, dropping the VCCO\_4 voltage does not reset the device by triggering a Power-On Reset (POR) event.

# No Internal Charge Pumps or Free-Running Oscillators

Some system applications are sensitive to sources of analog noise. Spartan-3 FPGA circuitry is fully static and does not employ internal charge pumps.

The CCLK configuration clock is active during the FPGA configuration process. After configuration completes, the CCLK oscillator is automatically disabled unless the Bitstream Generator (BitGen) option *Persist=Yes*. See Module 4: Table 80, page 125.

Spartan-3 FPGAs optionally support a featured called <u>Digitally Controlled Impedance</u> (DCI). When used in an application, the DCI logic uses an internal oscillator. The DCI logic is only enabled if the FPGA application specifies an I/O standard that requires DCI (LVDCI\_33, LVDCI\_25, etc.). If DCI is not used, the associated internal oscillator is also disabled.

In summary, unless an application uses the **Persist=Yes** option or specifies a DCI I/O standard, an FPGA with no external switching remains fully static.

# PRODUCT NOT RECOMMENDED FOR NEW DESIGNS

Spartan-3 FPGA Family: DC and Switching Characteristics

# **Switching Characteristics**

All Spartan-3 devices are available in two speed grades: -4 and the higher performance -5. Switching characteristics in this document may be designated as Advance, Preliminary, or Production. Each category is defined as follows:

Advance: These specifications are based on simulations only and are typically available soon after establishing FPGA specifications. Although speed grades with this designation are considered relatively stable and conservative, some under-reported delays may still occur.

Preliminary: These specifications are based on complete early silicon characterization. Devices and speed grades with this designation are intended to give a better indication of the expected performance of production silicon. The probability of under-reporting preliminary delays is greatly reduced compared to Advance data.

**Production**: These specifications are approved once enough production silicon of a particular device family member has been characterized to provide full correlation between speed files and devices over numerous production lots. There is no under-reporting of delays, and customers receive formal notification of any subsequent changes. Typically, the slowest speed grades transition to Production before faster speed grades.

Production-quality systems must use FPGA designs compiled using a Production status speed file. FPGAs designs using a less mature speed file designation may only be used during system prototyping or preproduction qualification. FPGA designs using Advance or Preliminary status speed files should never be used in a production-quality system.

Whenever a speed file designation changes, as a device matures toward Production status, rerun the Xilinx ISE software on the FPGA design to ensure that the FPGA design incorporates the latest timing information and software updates.

Xilinx ISE Software Updates: http://www.xilinx.com/support/download/index.htm

All specified limits are representative of worst-case supply voltage and junction temperature conditions. Unless otherwise noted, the following applies: Parameter values apply to all Spartan-3 devices. All parameters representing voltages are measured with respect to GND.

Selected timing parameters and their representative values are included below either because they are important as general design requirements or they indicate fundamental device performance characteristics. The Spartan-3 FPGA v1.38 speed files are the original source for many but not all of the values. The v1.38 speed files are available in Xilinx Integrated Software Environment (ISE) software version 8.2i.

The speed grade designations for these files are shown in Table 39. For more complete, more precise, and worst-case data, use the values reported by the Xilinx static timing analyzer (TRACE in the Xilinx development software) and back-annotated to the simulation netlist.

Table 39: Spartan-3 FPGA Speed Grade Designations (ISE v8.2i or Later)

| Device   | Advance | Preliminary | Production               |

|----------|---------|-------------|--------------------------|

| XC3S50   |         |             | -4, -5 (v1.37 and later) |

| XC3S200  |         |             |                          |

| XC3S400  |         |             |                          |

| XC3S1000 |         |             |                          |

| XC3S1500 |         |             |                          |

| XC3S2000 |         |             |                          |

| XC3S4000 |         |             |                          |

| XC3S5000 |         |             | -4, -5 (v1.38 and later) |

Table 41: System-Synchronous Pin-to-Pin Setup and Hold Times for the IOB Input Path (Cont'd)

|                   |                                                                                                         |                                |          | Speed Grade |       |       |

|-------------------|---------------------------------------------------------------------------------------------------------|--------------------------------|----------|-------------|-------|-------|

| Symbol            | Description                                                                                             | Conditions                     | Device   | -5          | -4    | Units |

|                   |                                                                                                         |                                |          | Min         | Min   |       |

| T <sub>PHFD</sub> | When writing to IFF, the time from                                                                      | LVCMOS25 <sup>(3)</sup> ,      | XC3S50   | -0.98       | -0.93 | ns    |

|                   | the active transition at the Global Clock pin to the point when data must be held at the Input pin. The | IOBDELAY = IFD,<br>without DCM | XC3S200  | -0.40       | -0.35 | ns    |

|                   |                                                                                                         |                                | XC3S400  | -0.27       | -0.22 | ns    |

|                   | DCM is not in use. The Input Delay is programmed.                                                       |                                | XC3S1000 | -1.19       | -1.14 | ns    |

|                   | Boldy to programmed.                                                                                    |                                | XC3S1500 | -1.43       | -1.38 | ns    |

|                   |                                                                                                         |                                | XC3S2000 | -2.33       | -2.28 | ns    |

|                   |                                                                                                         |                                | XC3S4000 | -2.47       | -2.42 | ns    |

|                   |                                                                                                         |                                | XC3S5000 | -2.66       | -2.61 | ns    |

#### Notes:

- 1. The numbers in this table are tested using the methodology presented in Table 48 and are based on the operating conditions set forth in Table 32 and Table 35.

- This setup time requires adjustment whenever a signal standard other than LVCMOS25 is assigned to the Global Clock Input or the data Input. If this is true of the Global Clock Input, subtract the appropriate adjustment from Table 44. If this is true of the data Input, add the appropriate Input adjustment from the same table.

- 3. This hold time requires adjustment whenever a signal standard other than LVCMOS25 is assigned to the Global Clock Input or the data Input. If this is true of the Global Clock Input, add the appropriate Input adjustment from Table 44. If this is true of the data Input, subtract the appropriate Input adjustment from the same table. When the hold time is negative, it is possible to change the data before the clock's active edge.

- 4. DCM output jitter is included in all measurements.

Table 42: Setup and Hold Times for the IOB Input Path

|                      |                                                                                                                               |                                             |          | Speed | Grade |       |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|----------|-------|-------|-------|

| Symbol               | Description                                                                                                                   | Conditions                                  | Device   | -5    | -4    | Units |

|                      |                                                                                                                               |                                             |          | Min   | Min   |       |

| Setup Times          |                                                                                                                               |                                             |          | '     |       |       |

| T <sub>IOPICK</sub>  | Time from the setup of data at the Input pin                                                                                  | LVCMOS25 <sup>(2)</sup> ,                   | XC3S50   | 1.65  | 1.89  | ns    |

|                      | to the active transition at the ICLK input of<br>the Input Flip-Flop (IFF). No Input Delay is                                 | IOBDELAY = NONE                             | XC3S200  | 1.37  | 1.57  | ns    |

|                      | programmed.                                                                                                                   |                                             | XC3S400  | 1.37  | 1.57  | ns    |

|                      |                                                                                                                               |                                             | XC3S1000 | 1.65  | 1.89  | ns    |

|                      |                                                                                                                               |                                             | XC3S1500 | 1.65  | 1.89  | ns    |

|                      |                                                                                                                               |                                             | XC3S2000 | 1.65  | 1.89  | ns    |

|                      |                                                                                                                               |                                             | XC3S4000 | 1.73  | 1.99  | ns    |

|                      |                                                                                                                               |                                             | XC3S5000 | 1.82  | 2.09  | ns    |

| T <sub>IOPICKD</sub> | Time from the setup of data at the Input pin to the active transition at the IFF's ICLK input. The Input Delay is programmed. | LVCMOS25 <sup>(2)</sup> ,<br>IOBDELAY = IFD | XC3S50   | 4.39  | 5.04  | ns    |

|                      |                                                                                                                               |                                             | XC3S200  | 4.76  | 5.47  | ns    |

|                      |                                                                                                                               |                                             | XC3S400  | 4.63  | 5.32  | ns    |

|                      |                                                                                                                               |                                             | XC3S1000 | 5.02  | 5.76  | ns    |

|                      |                                                                                                                               |                                             | XC3S1500 | 5.40  | 6.20  | ns    |

|                      |                                                                                                                               |                                             | XC3S2000 | 6.68  | 7.68  | ns    |

|                      |                                                                                                                               |                                             | XC3S4000 | 7.16  | 8.24  | ns    |

|                      |                                                                                                                               |                                             | XC3S5000 | 7.33  | 8.42  | ns    |

Table 70: Spartan-3 FPGA Pin Definitions (Cont'd)

| Pin Name                     | Direction             | Description                                                                                                                                                                                                                           |

|------------------------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TDI                          | Input                 | JTAG Test Data Input:  TDI is the serial data input for all JTAG instruction and data registers. This pin has an internal pull-up resistor to VCCAUX during configuration.                                                            |

| TMS                          | Input                 | JTAG Test Mode Select: The serial TMS input controls the operation of the JTAG port. This pin has an internal pull-up resistor to VCCAUX during configuration.                                                                        |

| TDO                          | Output                | JTAG Test Data Output:  TDO is the serial data output for all JTAG instruction and data registers.  This pin has an internal pull-up resistor to VCCAUX during configuration.                                                         |

| VCCO: I/O bank output        | t voltage supply pins |                                                                                                                                                                                                                                       |

| VCCO_#                       | Supply                | Power Supply for Output Buffer Drivers (per bank): These pins power the output drivers within a specific I/O bank.                                                                                                                    |

| VCCAUX: Auxiliary vo         | Itage supply pins     |                                                                                                                                                                                                                                       |

| VCCAUX                       | Supply                | Power Supply for Auxiliary Circuits: +2.5V power pins for auxiliary circuits, including the Digital Clock Managers (DCMs), the dedicated configuration pins (CONFIG), and the dedicated JTAG pins. All VCCAUX pins must be connected. |

| <b>VCCINT: Internal core</b> | voltage supply pins   |                                                                                                                                                                                                                                       |

| VCCINT                       | Supply                | Power Supply for Internal Core Logic:<br>+1.2V power pins for the internal logic. All pins must be connected.                                                                                                                         |

| GND: Ground supply           | oins                  |                                                                                                                                                                                                                                       |

| GND                          | Supply                | <b>Ground:</b> Ground pins, which are connected to the power supply's return path. All pins must be connected.                                                                                                                        |

| N.C.: Unconnected pa         | ckage pins            |                                                                                                                                                                                                                                       |

| N.C.                         |                       | Unconnected Package Pin: These package pins are unconnected.                                                                                                                                                                          |

#### Notes:

- 1. All unused inputs and bidirectional pins must be tied either High or Low. For unused enable inputs, apply the level that disables the associated function. One common approach is to activate internal pull-up or pull-down resistors. An alternative approach is to externally connect the pin to either VCCO or GND.

- 2. All outputs are of the totem-pole type i.e., they can drive High as well as Low logic levels except for the cases where "Open Drain" is indicated. The latter can only drive a Low logic level and require a pull-up resistor to produce a High logic level.

# **Detailed, Functional Pin Descriptions**

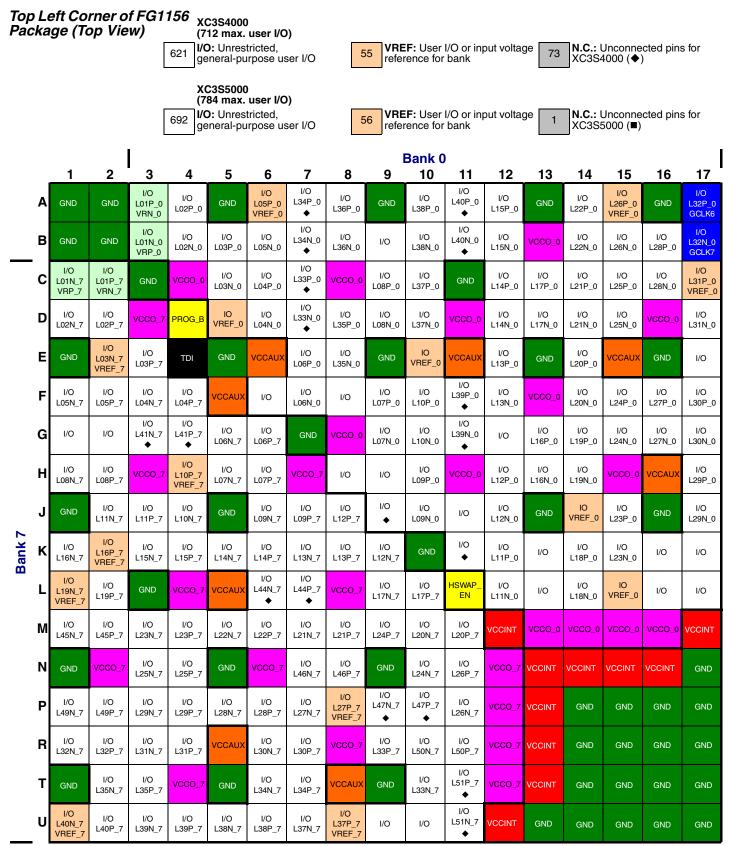

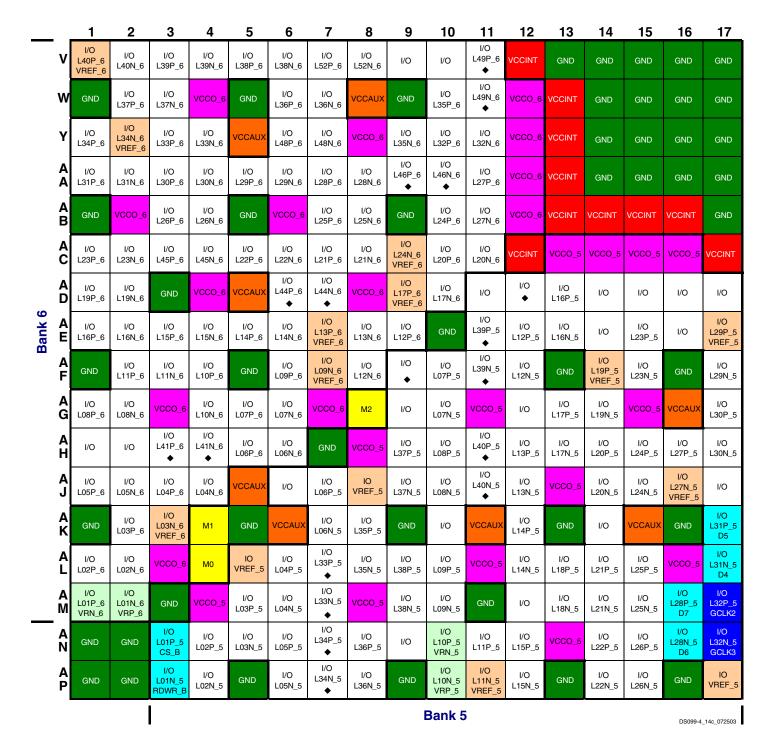

# I/O Type: Unrestricted, General-purpose I/O Pins

After configuration, I/O-type pins are inputs, outputs, bidirectional I/O, three-state outputs, open-drain outputs, or open-source outputs, as defined in the application

Pins labeled "IO" support all SelectIO™ interface signal standards except differential standards. A given device at most only has a few of these pins.

A majority of the general-purpose I/O pins are labeled in the format "IO\_Lxxy\_#". These pins support all SelectIO signal standards, including the differential standards such as LVDS, ULVDS, BLVDS, RSDS, or LDT.

For additional information, see IOBs, page 10

Table 71: Dual-Purpose Pins Used in Master or Slave Serial Mode

| Pin Name | Direction     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DIN      | Input         | Serial Data Input:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|          |               | During the Master or Slave Serial configuration modes, DIN is the serial configuration data input, and all data is synchronized to the rising CCLK edge. After configuration, this pin is available as a user I/O.                                                                                                                                                                                                                                                                                                                  |

|          |               | This signal is located in Bank 4 and its output voltage determined by VCCO_4.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|          |               | The BitGen option <i>Persist</i> permits this pin to retain its configuration function in the User mode.                                                                                                                                                                                                                                                                                                                                                                                                                            |

| DOUT     | Output        | Serial Data Output:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|          |               | In a multi-FPGA design where all the FPGAs use serial mode, connect the DOUT output of one FPGA—in either Master or Slave Serial mode—to the DIN input of the next FPGA—in Slave Serial mode—so that configuration data passes from one to the next, in daisy-chain fashion. This "daisy chain" permits sequential configuration of multiple FPGAs.                                                                                                                                                                                 |

|          |               | This signal is located in Bank 4 and its output voltage determined by VCCO_4.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|          |               | The BitGen option <i>Persist</i> permits this pin to retain its configuration function in the User mode.                                                                                                                                                                                                                                                                                                                                                                                                                            |

| INIT_B   | Bidirectional | Initializing Configuration Memory/Configuration Error:                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|          | (open-drain)  | Just after power is applied, the FPGA produces a Low-to-High transition on this pin indicating that initialization ( <i>i.e.</i> , clearing) of the configuration memory has finished. Before entering the User mode, this pin functions as an open-drain output, which requires a pull-up resistor in order to produce a High logic level. In a multi-FPGA design, tie (wire AND) the INIT_B pins from all FPGAs together so that the common node transitions High only after all of the FPGAs have been successfully initialized. |

|          |               | Externally holding this pin Low beyond the initialization phase delays the start of configuration. This action stalls the FPGA at the configuration step just before the mode select pins are sampled.                                                                                                                                                                                                                                                                                                                              |

|          |               | During configuration, the FPGA indicates the occurrence of a data (i.e., CRC) error by asserting INIT_B Low.                                                                                                                                                                                                                                                                                                                                                                                                                        |

|          |               | This signal is located in Bank 4 and its output voltage determined by VCCO_4.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|          |               | The BitGen option <i>Persist</i> permits this pin to retain its configuration function in the User mode.                                                                                                                                                                                                                                                                                                                                                                                                                            |

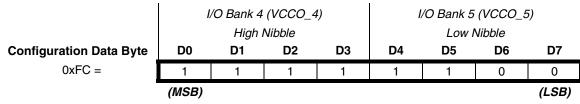

Figure 41: Configuration Data Byte Mapping to D0-D7 Bits

# Parallel Configuration Modes (SelectMAP)

This section describes the dual-purpose configuration pins used during the Master and Slave Parallel configuration modes, sometimes also called the SelectMAP modes. In both Master and Slave Parallel configuration modes, D0-D7 form the byte-wide configuration data input. See Table 75 for Mode Select pin settings required for Parallel modes.

As shown in Figure 41, D0 is the most-significant bit while D7 is the least-significant bit. Bits D0-D3 form the high nibble of the byte and bits D4-D7 form the low nibble.

In the Parallel configuration modes, both the VCCO\_4 and VCCO\_5 voltage supplies are required and must both equal the voltage of the attached configuration device, typically either 2.5V or 3.3V.

Assert Low both the chip-select pin, CS\_B, and the read/write control pin, RDWR\_B, to write the configuration data byte presented on the D0-D7 pins to the FPGA on a rising-edge of the configuration clock, CCLK. The order of CS\_B and RDWR\_B does not matter, although RDWR\_B must be asserted throughout the configuration process. If RDWR\_B is de-asserted during configuration, the FPGA aborts the configuration operation.

After configuration, these pins are available as general-purpose user I/O. However, the SelectMAP configuration interface is optionally available for debugging and dynamic reconfiguration. To use these SelectMAP pins after configuration, set the Persist bitstream generation option.

The Readback debugging option, for example, requires the Persist bitstream generation option. During Readback mode, assert CS\_B Low, along with RDWR\_B High, to read a configuration data byte from the FPGA to the D0-D7 bus on a rising CCLK edge. During Readback mode, D0-D7 are output pins.

In all the cases, the configuration data and control signals are synchronized to the rising edge of the CCLK clock signal.

Table 72: Dual-Purpose Configuration Pins for Parallel (SelectMAP) Configuration Modes (Cont'd)

| Pin Name | Direction                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Description                                                                                                                     |  |  |  |  |

|----------|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| BUSY     | Output                        | Configuration Data Rate Control for Parallel Mode: In the Slave and Master Parallel modes, BUSY throttles the rate at which configuration data is loaded. BUSY is only necessary if CCLK operates at greater than 50 MHz. Ignore BUSY for frequencies of 50 MHz and below.  When BUSY is Low, the FPGA accepts the next configuration data byte on the next rising CCLK edge for which CS_B and RDWR_B are Low. When BUSY is High, the FPGA ignores the next configuration data byte. The next configuration data value must be held or reloaded until the next rising CCLK edge when BUSY is Low. When CS_B is High, BUSY is in a high impedance state. |                                                                                                                                 |  |  |  |  |

|          |                               | BUSY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Function                                                                                                                        |  |  |  |  |

|          |                               | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | The FPGA is ready to accept the next configuration data byte.                                                                   |  |  |  |  |

|          |                               | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | The FPGA is busy processing the current configuration data byte and is not ready to accept the next byte.                       |  |  |  |  |

|          |                               | Hi-Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | If CS_B is High, then BUSY is high impedance.                                                                                   |  |  |  |  |

|          |                               | This signal is located in Bank 4 and its output voltage is determined by VCCO_4. The BitGen of Persist permits this pin to retain its configuration function in the User mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                 |  |  |  |  |

| INIT_B   | Bidirectional<br>(open-drain) | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Initializing Configuration Memory/Configuration Error (active-Low): See description under Serial Configuration Modes, page 112. |  |  |  |  |

### **JTAG Configuration Mode**

In the JTAG configuration mode all dual-purpose configuration pins are unused and behave exactly like user-I/O pins, as shown in Table 79. See Table 75 for Mode Select pin settings required for JTAG mode.

### **Dual-Purpose Pin I/O Standard During Configuration**

During configuration, the dual-purpose pins default to CMOS input and output levels for the associated VCCO voltage supply pins. For example, in the Parallel configuration modes, both VCCO\_4 and VCCO\_5 are required. If connected to +2.5V, then the associated pins conform to the LVCMOS25 I/O standard. If connected to +3.3V, then the pins drive LVCMOS output levels and accept either LVTTL or LVCMOS input levels.

### **Dual-Purpose Pin Behavior After Configuration**

After the configuration process completes, these pins, if they were borrowed during configuration, become user-I/O pins available to the application. If a dual-purpose configuration pin is not used during the configuration process—*i.e.*, the parallel configuration pins when using serial mode—then the pin behaves exactly like a general-purpose I/O. See I/O Type: Unrestricted, General-purpose I/O Pins section.

### DCI: User I/O or Digitally Controlled Impedance Resistor Reference Input

These pins are individual user-I/O pins unless one of the I/O standards used in the bank requires the Digitally Controlled Impedance (DCI) feature. If DCI is used, then 1% precision resistors connected to the VRP\_# and VRN\_# pins match the impedance on the input or output buffers of the I/O standards that use DCI within the bank. The '#' character in the pin name indicates the associated I/O bank and is an integer, 0 through 7.

There are two DCI pins per I/O bank, except in the CP132 and TQ144 packages, which do not have any DCI inputs for Bank 5.

### **VRP and VRN Impedance Resistor Reference Inputs**

The 1% precision impedance-matching resistor attached to the VRP\_# pin controls the pull-up impedance of PMOS transistor in the input or output buffer. Consequently, the VRP\_# pin must connect to ground. The 'P' character in "VRP" indicates that this pin controls the I/O buffer's PMOS transistor impedance. The VRP\_# pin is used for both single and split termination.

Table 87: VQ100 Package Pinout (Cont'd)

| Bank   | XC3S50<br>XC3S200<br>Pin Name | VQ100<br>Pin<br>Number | Туре   |

|--------|-------------------------------|------------------------|--------|

| 6      | IO_L40P_6/VREF_6              | P13                    | VREF   |

| 6      | VCCO_6                        | P19                    | VCCO   |

| 7      | IO_L01N_7/VRP_7               | P2                     | DCI    |

| 7      | IO_L01P_7/VRN_7               | P1                     | DCI    |

| 7      | IO_L21N_7                     | P5                     | I/O    |

| 7      | IO_L21P_7                     | P4                     | I/O    |

| 7      | IO_L23N_7                     | P9                     | I/O    |

| 7      | IO_L23P_7                     | P8                     | I/O    |

| 7      | IO_L40N_7/VREF_7              | P12                    | VREF   |

| 7      | IO_L40P_7                     | P11                    | I/O    |

| 7      | VCCO_7                        | P6                     | VCCO   |

| N/A    | GND                           | Р3                     | GND    |

| N/A    | GND                           | P10                    | GND    |

| N/A    | GND                           | P20                    | GND    |

| N/A    | GND                           | P29                    | GND    |

| N/A    | GND                           | P41                    | GND    |

| N/A    | GND                           | P56                    | GND    |

| N/A    | GND                           | P66                    | GND    |

| N/A    | GND                           | P73                    | GND    |

| N/A    | GND                           | P82                    | GND    |

| N/A    | GND                           | P95                    | GND    |

| N/A    | VCCAUX                        | P7                     | VCCAUX |

| N/A    | VCCAUX                        | P33                    | VCCAUX |

| N/A    | VCCAUX                        | P58                    | VCCAUX |

| N/A    | VCCAUX                        | P84                    | VCCAUX |

| N/A    | VCCINT                        | P18                    | VCCINT |

| N/A    | VCCINT                        | P45                    | VCCINT |

| N/A    | VCCINT                        | P69                    | VCCINT |

| N/A    | VCCINT                        | P93                    | VCCINT |

| VCCAUX | CCLK                          | P52                    | CONFIG |

| VCCAUX | DONE                          | P51                    | CONFIG |

| VCCAUX | HSWAP_EN                      | P98                    | CONFIG |

| VCCAUX | MO                            | P25                    | CONFIG |

| VCCAUX | M1                            | P24                    | CONFIG |

| VCCAUX | M2                            | P26                    | CONFIG |

| VCCAUX | PROG_B                        | P99                    | CONFIG |

| VCCAUX | TCK                           | P77                    | JTAG   |

| VCCAUX | TDI                           | P100                   | JTAG   |

Table 93: PQ208 Package Pinout (Cont'd)

| Bank | XC3S50<br>Pin Name | XC3S200, XC3S400<br>Pin Names | PQ208 Pin<br>Number | Туре |

|------|--------------------|-------------------------------|---------------------|------|

| 5    | IO_L10P_5/VRN_5    | IO_L10P_5/VRN_5               | P61                 | DCI  |

| 5    | IO_L27N_5/VREF_5   | IO_L27N_5/VREF_5              | P65                 | VREF |

| 5    | IO_L27P_5          | IO_L27P_5                     | P64                 | I/O  |

| 5    | IO_L28N_5/D6       | IO_L28N_5/D6                  | P68                 | DUAL |

| 5    | IO_L28P_5/D7       | IO_L28P_5/D7                  | P67                 | DUAL |

| 5    | IO_L31N_5/D4       | IO_L31N_5/D4                  | P74                 | DUAL |

| 5    | IO_L31P_5/D5       | IO_L31P_5/D5                  | P72                 | DUAL |

| 5    | IO_L32N_5/GCLK3    | IO_L32N_5/GCLK3               | P77                 | GCLK |

| 5    | IO_L32P_5/GCLK2    | IO_L32P_5/GCLK2               | P76                 | GCLK |

| 5    | VCCO_5             | VCCO_5                        | P60                 | VCCO |

| 5    | VCCO_5             | VCCO_5                        | P73                 | VCCO |

| 6    | N.C. (♦)           | IO/VREF_6                     | P50                 | VREF |

| 6    | IO_L01N_6/VRP_6    | IO_L01N_6/VRP_6               | P52                 | DCI  |

| 6    | IO_L01P_6/VRN_6    | IO_L01P_6/VRN_6               | P51                 | DCI  |

| 6    | IO_L19N_6          | IO_L19N_6                     | P48                 | I/O  |

| 6    | IO_L19P_6          | IO_L19P_6                     | P46                 | I/O  |

| 6    | IO_L20N_6          | IO_L20N_6                     | P45                 | I/O  |

| 6    | IO_L20P_6          | IO_L20P_6                     | P44                 | I/O  |

| 6    | IO_L21N_6          | IO_L21N_6                     | P43                 | I/O  |

| 6    | IO_L21P_6          | IO_L21P_6                     | P42                 | I/O  |

| 6    | IO_L22N_6          | IO_L22N_6                     | P40                 | I/O  |

| 6    | IO_L22P_6          | IO_L22P_6                     | P39                 | I/O  |

| 6    | IO_L23N_6          | IO_L23N_6                     | P37                 | I/O  |

| 6    | IO_L23P_6          | IO_L23P_6                     | P36                 | I/O  |

| 6    | IO_L24N_6/VREF_6   | IO_L24N_6/VREF_6              | P35                 | VREF |

| 6    | IO_L24P_6          | IO_L24P_6                     | P34                 | I/O  |

| 6    | N.C. (♦)           | IO_L39N_6                     | P33                 | I/O  |

| 6    | N.C. (♦)           | IO_L39P_6                     | P31                 | I/O  |

| 6    | IO_L40N_6          | IO_L40N_6                     | P29                 | I/O  |

| 6    | IO_L40P_6/VREF_6   | IO_L40P_6/VREF_6              | P28                 | VREF |

| 6    | VCCO_6             | VCCO_6                        | P32                 | VCCO |

| 6    | VCCO_6             | VCCO_6                        | P49                 | VCCO |

| 7    | IO_L01N_7/VRP_7    | IO_L01N_7/VRP_7               | P3                  | DCI  |

| 7    | IO_L01P_7/VRN_7    | IO_L01P_7/VRN_7               | P2                  | DCI  |

| 7    | N.C. (♠)           | IO_L16N_7                     | P5                  | I/O  |

| 7    | N.C. (♠)           | IO_L16P_7/VREF_7              | P4                  | VREF |

| 7    | IO_L19N_7/VREF_7   | IO_L19N_7/VREF_7              | P9                  | VREF |

| 7    | IO_L19P_7          | IO_L19P_7                     | P7                  | I/O  |

| 7    | IO_L20N_7          | IO_L20N_7                     | P11                 | I/O  |

| 7    | IO_L20P_7          | IO_L20P_7                     | P10                 | I/O  |

# User I/Os by Bank

Table 94 indicates how the available user-I/O pins are distributed between the eight I/O banks for the XC3S50 in the PQ208 package. Similarly, Table 95 shows how the available user-I/O pins are distributed between the eight I/O banks for the XC3S200 and XC3S400 in the PQ208 package.

Table 94: User I/Os Per Bank for XC3S50 in PQ208 Package

| Dookono Edno | I/O Bank Maximum I |             | All Possible I/O Pins by Type |      |     |      |      |

|--------------|--------------------|-------------|-------------------------------|------|-----|------|------|

| Package Edge | I/O Bank           | Maximum I/O | I/O                           | DUAL | DCI | VREF | GCLK |

| Тор          | 0                  | 15          | 9                             | 0    | 2   | 2    | 2    |

| Юр           | 1                  | 15          | 9                             | 0    | 2   | 2    | 2    |

| Right        | 2                  | 16          | 13                            | 0    | 2   | 2    | 0    |

| nigiii       | 3                  | 16          | 12                            | 0    | 2   | 2    | 0    |

| Bottom       | 4                  | 15          | 3                             | 6    | 2   | 2    | 2    |

| DOLLOTTI     | 5                  | 15          | 3                             | 6    | 2   | 2    | 2    |

| Left         | 6                  | 16          | 12                            | 0    | 2   | 2    | 0    |

|              | 7                  | 16          | 12                            | 0    | 2   | 2    | 0    |

Table 95: User I/Os Per Bank for XC3S200 and XC3S400 in PQ208 Package

| Package Edge | I/O Bank | Maximum I/O | All Possible I/O Pins by Type |      |     |      |      |

|--------------|----------|-------------|-------------------------------|------|-----|------|------|

|              |          |             | I/O                           | DUAL | DCI | VREF | GCLK |

| Тор          | 0        | 16          | 9                             | 0    | 2   | 3    | 2    |

| юр           | 1        | 15          | 9                             | 0    | 2   | 2    | 2    |

| Right        | 2        | 19          | 14                            | 0    | 2   | 3    | 0    |

| rugitt       | 3        | 20          | 15                            | 0    | 2   | 3    | 0    |

| Bottom       | 4        | 17          | 4                             | 6    | 2   | 3    | 2    |

| DOLLOTTI     | 5        | 15          | 3                             | 6    | 2   | 2    | 2    |

| Left         | 6        | 19          | 14                            | 0    | 2   | 3    | 0    |

|              | 7        | 20          | 15                            | 0    | 2   | 3    | 0    |

Table 98: FG320 Package Pinout (Cont'd)

| Bank | XC3S400, XC3S1000, XC3S1500<br>Pin Name | FG320<br>Pin Number | Туре |

|------|-----------------------------------------|---------------------|------|

| 2    | IO_L20N_2                               | E17                 | I/O  |

| 2    | IO_L20P_2                               | E18                 | I/O  |

| 2    | IO_L21N_2                               | F15                 | I/O  |

| 2    | IO_L21P_2                               | E15                 | I/O  |

| 2    | IO_L22N_2                               | F14                 | I/O  |

| 2    | IO_L22P_2                               | G14                 | I/O  |

| 2    | IO_L23N_2/VREF_2                        | G18                 | VREF |

| 2    | IO_L23P_2                               | F17                 | I/O  |

| 2    | IO_L24N_2                               | G15                 | I/O  |

| 2    | IO_L24P_2                               | G16                 | I/O  |

| 2    | IO_L27N_2                               | H13                 | I/O  |

| 2    | IO_L27P_2                               | H14                 | I/O  |

| 2    | IO_L34N_2/VREF_2                        | H16                 | VREF |

| 2    | IO_L34P_2                               | H15                 | I/O  |

| 2    | IO_L35N_2                               | H17                 | I/O  |

| 2    | IO_L35P_2                               | H18                 | I/O  |

| 2    | IO_L39N_2                               | J18                 | I/O  |

| 2    | IO_L39P_2                               | J17                 | I/O  |

| 2    | IO_L40N_2                               | J15                 | I/O  |

| 2    | IO_L40P_2/VREF_2                        | J14                 | VREF |

| 2    | VCCO_2                                  | F16                 | VCCO |

| 2    | VCCO_2                                  | H12                 | VCCO |

| 2    | VCCO_2                                  | J12                 | VCCO |

| 3    | Ю                                       | K15                 | I/O  |

| 3    | IO_L01N_3/VRP_3                         | T17                 | DCI  |

| 3    | IO_L01P_3/VRN_3                         | T16                 | DCI  |

| 3    | IO_L16N_3                               | T18                 | I/O  |

| 3    | IO_L16P_3                               | U18                 | I/O  |

| 3    | IO_L17N_3                               | P16                 | I/O  |

| 3    | IO_L17P_3/VREF_3                        | R16                 | VREF |

| 3    | IO_L19N_3                               | R17                 | I/O  |

| 3    | IO_L19P_3                               | R18                 | I/O  |

| 3    | IO_L20N_3                               | P18                 | I/O  |

| 3    | IO_L20P_3                               | P17                 | I/O  |

| 3    | IO_L21N_3                               | P15                 | I/O  |

| 3    | IO_L21P_3                               | N15                 | I/O  |

| 3    | IO_L22N_3                               | M14                 | I/O  |

| 3    | IO_L22P_3                               | N14                 | I/O  |

| 3    | IO_L23N_3                               | M15                 | I/O  |

| 3    | IO_L23P_3/VREF_3                        | M16                 | VREF |

Table 103: FG676 Package Pinout (Cont'd)

| Bank | XC3S1000<br>Pin Name | XC3S1500<br>Pin Name | XC3S2000<br>Pin Name | XC3S4000<br>Pin Name | XC3S5000<br>Pin Name | FG676 Pin<br>Number | Туре |

|------|----------------------|----------------------|----------------------|----------------------|----------------------|---------------------|------|

| 2    | IO_L34N_2/VREF_2     | IO_L34N_2/VREF_2     | IO_L34N_2/VREF_2     | IO_L34N_2/VREF_2     | IO_L34N_2/VREF_2     | M25                 | VREF |

| 2    | IO_L34P_2            | IO_L34P_2            | IO_L34P_2            | IO_L34P_2            | IO_L34P_2            | M26                 | I/O  |

| 2    | IO_L35N_2            | IO_L35N_2            | IO_L35N_2            | IO_L35N_2            | IO_L35N_2            | N19                 | I/O  |

| 2    | IO_L35P_2            | IO_L35P_2            | IO_L35P_2            | IO_L35P_2            | IO_L35P_2            | N20                 | I/O  |

| 2    | IO_L38N_2            | IO_L38N_2            | IO_L38N_2            | IO_L38N_2            | IO_L38N_2            | N21                 | I/O  |

| 2    | IO_L38P_2            | IO_L38P_2            | IO_L38P_2            | IO_L38P_2            | IO_L38P_2            | N22                 | I/O  |

| 2    | IO_L39N_2            | IO_L39N_2            | IO_L39N_2            | IO_L39N_2            | IO_L39N_2            | N23                 | I/O  |

| 2    | IO_L39P_2            | IO_L39P_2            | IO_L39P_2            | IO_L39P_2            | IO_L39P_2            | N24                 | I/O  |

| 2    | IO_L40N_2            | IO_L40N_2            | IO_L40N_2            | IO_L40N_2            | IO_L40N_2            | N25                 | I/O  |

| 2    | IO_L40P_2/VREF_2     | IO_L40P_2/VREF_2     | IO_L40P_2/VREF_2     | IO_L40P_2/VREF_2     | IO_L40P_2/VREF_2     | N26                 | VREF |

| 2    | VCCO_2               | VCCO_2               | VCCO_2               | VCCO_2               | VCCO_2               | G24                 | vcco |

| 2    | VCCO_2               | VCCO_2               | VCCO_2               | VCCO_2               | VCCO_2               | J19                 | VCCO |

| 2    | VCCO_2               | VCCO_2               | VCCO_2               | VCCO_2               | VCCO_2               | K19                 | vcco |

| 2    | VCCO_2               | VCCO_2               | VCCO_2               | VCCO_2               | VCCO_2               | L18                 | VCCO |

| 2    | VCCO_2               | VCCO_2               | VCCO_2               | VCCO_2               | VCCO_2               | L24                 | vcco |

| 2    | VCCO_2               | VCCO_2               | VCCO_2               | VCCO_2               | VCCO_2               | M18                 | VCCO |

| 2    | VCCO_2               | VCCO_2               | VCCO_2               | VCCO_2               | VCCO_2               | N17                 | VCCO |

| 2    | VCCO_2               | VCCO_2               | VCCO_2               | VCCO_2               | VCCO_2               | N18                 | VCCO |

| 3    | IO_L01N_3/VRP_3      | IO_L01N_3/VRP_3      | IO_L01N_3/VRP_3      | IO_L01N_3/VRP_3      | IO_L01N_3/VRP_3      | AA22                | DCI  |

| 3    | IO_L01P_3/VRN_3      | IO_L01P_3/VRN_3      | IO_L01P_3/VRN_3      | IO_L01P_3/VRN_3      | IO_L01P_3/VRN_3      | AA21                | DCI  |

| 3    | IO_L02N_3/VREF_3     | IO_L02N_3/VREF_3     | IO_L02N_3/VREF_3     | IO_L02N_3/VREF_3     | IO_L02N_3/VREF_3     | AB24                | VREF |

| 3    | IO_L02P_3            | IO_L02P_3            | IO_L02P_3            | IO_L02P_3            | IO_L02P_3            | AB23                | I/O  |

| 3    | IO_L03N_3            | IO_L03N_3            | IO_L03N_3            | IO_L03N_3            | IO_L03N_3            | AC26                | I/O  |

| 3    | IO_L03P_3            | IO_L03P_3            | IO_L03P_3            | IO_L03P_3            | IO_L03P_3            | AC25                | I/O  |

| 3    | N.C. (♠)             | IO_L05N_3            | IO_L05N_3            | IO_L05N_3            | IO_L05N_3            | Y21                 | I/O  |

| 3    | N.C. (♠)             | IO_L05P_3            | IO_L05P_3            | IO_L05P_3            | IO_L05P_3            | Y20                 | I/O  |

| 3    | N.C. (♦)             | IO_L06N_3            | IO_L06N_3            | IO_L06N_3            | IO_L06N_3            | AB26                | I/O  |

| 3    | N.C. (♦)             | IO_L06P_3            | IO_L06P_3            | IO_L06P_3            | IO_L06P_3            | AB25                | I/O  |

| 3    | N.C. (♠)             | IO_L07N_3            | IO_L07N_3            | IO_L07N_3            | IO_L07N_3            | AA24                | I/O  |

| 3    | N.C. (♠)             | IO_L07P_3            | IO_L07P_3            | IO_L07P_3            | IO_L07P_3            | AA23                | I/O  |

| 3    | N.C. (♠)             | IO_L08N_3            | IO_L08N_3            | IO_L08N_3            | IO_L08N_3            | Y23                 | I/O  |

| 3    | N.C. (♦)             | IO_L08P_3            | IO_L08P_3            | IO_L08P_3            | IO_L08P_3            | Y22                 | I/O  |

| 3    | N.C. (♦)             | IO_L09N_3            | IO_L09N_3            | IO_L09N_3            | IO_L09N_3            | AA26                | I/O  |

| 3    | N.C. (♦)             | IO_L09P_3/VREF_3     | IO_L09P_3/VREF_3     | IO_L09P_3/VREF_3     | IO_L09P_3/VREF_3     | AA25                | VREF |

| 3    | N.C. (◆)             | IO_L10N_3            | IO_L10N_3            | IO_L10N_3            | IO_L10N_3            | W21                 | I/O  |

|      |                      |                      |                      |                      |                      |                     |      |

| 3    | N.C. (♠)             | IO_L10P_3            | IO_L10P_3            | IO_L10P_3            | IO_L10P_3            | W20                 | 1/0  |

| 3    | IO_L14N_3            | IO_L14N_3            | IO_L14N_3            | IO_L14N_3            | IO_L14N_3            | Y26                 | 1/0  |

| 3    | IO_L14P_3            | IO_L14P_3            | IO_L14P_3            | IO_L14P_3            | IO_L14P_3            | Y25                 | 1/0  |

| 3    | IO_L16N_3            | IO_L16N_3            | IO_L16N_3            | IO_L16N_3            | IO_L16N_3            | V21                 | 1/0  |