Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Product Status                 | Active                                                        |  |

|--------------------------------|---------------------------------------------------------------|--|

| Number of LABs/CLBs            | 1920                                                          |  |

| Number of Logic Elements/Cells | 17280                                                         |  |

| Total RAM Bits                 | 442368                                                        |  |

| Number of I/O                  | 221                                                           |  |

| Number of Gates                | 1000000                                                       |  |

| Voltage - Supply               | 1.14V ~ 1.26V                                                 |  |

| Mounting Type                  | Surface Mount                                                 |  |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                            |  |

| Package / Case                 | 320-BGA                                                       |  |

| Supplier Device Package        | 320-FBGA (19x19)                                              |  |

| Purchase URL                   | https://www.e-xfl.com/product-detail/xilinx/xc3s1000-4fgg320i |  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### Table 4: Example Ordering Information

| Device   |    | Speed Grade                     | l                        | Package Type/Number of Pins                      | T | emperature Range (T <sub>j</sub> ) |

|----------|----|---------------------------------|--------------------------|--------------------------------------------------|---|------------------------------------|

| XC3S50   | -4 | Standard Performance            | VQ(G)100                 | 100-pin Very Thin Quad Flat Pack (VQFP)          | С | Commercial (0°C to 85°C)           |

| XC3S200  | -5 | High Performance <sup>(1)</sup> | CP(G)132 <sup>(2)</sup>  | 132-pin Chip-Scale Package (CSP)                 | Ι | Industrial (-40°C to 100°C)        |

| XC3S400  |    |                                 | TQ(G)144                 | 144-pin Thin Quad Flat Pack (TQFP)               |   | ·                                  |

| XC3S1000 |    |                                 | PQ(G)208                 | 208-pin Plastic Quad Flat Pack (PQFP)            |   |                                    |

| XC3S1500 |    |                                 | FT(G)256                 | 256-ball Fine-Pitch Thin Ball Grid Array (FTBGA) |   |                                    |

| XC3S2000 |    |                                 | FG(G)320                 | 320-ball Fine-Pitch Ball Grid Array (FBGA)       |   |                                    |

| XC3S4000 |    |                                 | FG(G)456                 | 456-ball Fine-Pitch Ball Grid Array (FBGA)       |   |                                    |

| XC3S5000 |    |                                 | FG(G)676                 | 676-ball Fine-Pitch Ball Grid Array (FBGA)       |   |                                    |

|          |    |                                 | FG(G)900                 | 900-ball Fine-Pitch Ball Grid Array (FBGA)       |   |                                    |

|          |    |                                 | FG(G)1156 <sup>(2)</sup> | 1156-ball Fine-Pitch Ball Grid Array (FBGA)      |   |                                    |

#### Notes:

1. The -5 speed grade is exclusively available in the Commercial temperature range.

2. The CP132, CPG132, FG1156, and FGG1156 packages are discontinued. See http://www.xilinx.com/support/documentation/spartan-3\_customer\_notices.htm.

## **Revision History**

| Date     | Version | Description                                                                                                                                                                                                                                                                                                                                                                   |

|----------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 04/11/03 | 1.0     | Initial Xilinx release.                                                                                                                                                                                                                                                                                                                                                       |

| 04/24/03 | 1.1     | Updated block RAM, DCM, and multiplier counts for the XC3S50.                                                                                                                                                                                                                                                                                                                 |

| 12/24/03 | 1.2     | Added the FG320 package.                                                                                                                                                                                                                                                                                                                                                      |

| 07/13/04 | 1.3     | Added information on Pb-free packaging options.                                                                                                                                                                                                                                                                                                                               |

| 01/17/05 | 1.4     | Referenced Spartan-3 XA Automotive FPGA families in Table 1. Added XC3S50CP132, XC3S2000FG456, XC3S4000FG676 options to Table 3. Updated Package Marking to show mask revision code, fabrication facility code, and process technology code.                                                                                                                                  |

| 08/19/05 | 1.5     | Added package markings for BGA packages (Figure 3) and CP132/CPG132 packages (Figure 4).<br>Added differential (complementary single-ended) HSTL and SSTL I/O standards.                                                                                                                                                                                                      |

| 04/03/06 | 2.0     | Increased number of supported single-ended and differential I/O standards.                                                                                                                                                                                                                                                                                                    |

| 04/26/06 | 2.1     | Updated document links.                                                                                                                                                                                                                                                                                                                                                       |

| 05/25/07 | 2.2     | Updated Package Marking to allow for dual-marking.                                                                                                                                                                                                                                                                                                                            |

| 11/30/07 | 2.3     | Added XC3S5000 FG(G)676 to Table 3. Noted that FG(G)1156 package is being discontinued and updated max I/O count.                                                                                                                                                                                                                                                             |

| 06/25/08 | 2.4     | Updated max I/O counts based on FG1156 discontinuation. Clarified dual mark in Package Marking.<br>Updated formatting and links.                                                                                                                                                                                                                                              |

| 12/04/09 | 2.5     | CP132 and CPG132 packages are being discontinued. Added link to Spartan-3 FPGA customer notices. Updated Table 3 with package footprint dimensions.                                                                                                                                                                                                                           |

| 10/29/12 | 3.0     | Added Notice of Disclaimer section. Per <u>XCN07022</u> , updated the discontinued FG1156 and FGG1156 package discussion throughout document. Per <u>XCN08011</u> , updated the discontinued CP132 and CPG132 package discussion throughout document. Although the package is discontinued, updated the marking on Figure 4. This product is not recommended for new designs. |

# ESD Protection

Clamp diodes protect all device pads against damage from Electro-Static Discharge (ESD) as well as excessive voltage transients. Each I/O has two clamp diodes: One diode extends P-to-N from the pad to  $V_{CCO}$  and a second diode extends N-to-P from the pad to GND. During operation, these diodes are normally biased in the off state. These clamp diodes are always connected to the pad, regardless of the signal standard selected. The presence of diodes limits the ability of Spartan-3 FPGA I/Os to tolerate high signal voltages. The V<sub>IN</sub> absolute maximum rating in Table 28, page 58 specifies the voltage range that I/Os can tolerate.

# Slew Rate Control and Drive Strength

Two options, FAST and SLOW, control the output slew rate. The FAST option supports output switching at a high rate. The SLOW option reduces bus transients. These options are only available when using one of the LVCMOS or LVTTL standards, which also provide up to seven different levels of current drive strength: 2, 4, 6, 8, 12, 16, and 24 mA. Choosing the appropriate drive strength level is yet another means to minimize bus transients.

Table 7 shows the drive strengths that the LVCMOS and LVTTL standards support.

| Signal Standard | Current Drive (mA) |   |   |   |    |    |    |  |  |

|-----------------|--------------------|---|---|---|----|----|----|--|--|

| (IOSTANDARD)    | 2                  | 4 | 6 | 8 | 12 | 16 | 24 |  |  |

| LVTTL           | 1                  | 1 | 1 | 1 | 1  | 1  | 1  |  |  |

| LVCMOS33        | 1                  | 1 | 1 | 1 | 1  | 1  | ~  |  |  |

| LVCMOS25        | 1                  | 1 | 1 | 1 | 1  | 1  | 1  |  |  |

| LVCMOS18        | 1                  | 1 | 1 | 1 | 1  | 1  | -  |  |  |

| LVCMOS15        | 1                  | 1 | 1 | 1 | 1  | _  | -  |  |  |

| LVCMOS12        | 1                  | 1 | 1 | - | -  | -  | -  |  |  |

Table 7: Programmable Output Drive Current

## **Boundary-Scan Capability**

All Spartan-3 FPGA IOBs support boundary-scan testing compatible with IEEE 1149.1 standards. During boundary- scan operations such as EXTEST and HIGHZ the I/O pull-down resistor is active. For more information, see Boundary-Scan (JTAG) Mode, page 50, and refer to the "Using Boundary-Scan and BSDL Files" chapter in <u>UG331</u>.

## SelectIO Interface Signal Standards

The IOBs support 18 different single-ended signal standards, as listed in Table 8. Furthermore, the majority of IOBs can be used in specific pairs supporting any of eight differential signal standards, as shown in Table 9.

To define the SelectIO<sup>™</sup> interface signaling standard in a design, set the IOSTANDARD attribute to the appropriate setting. Xilinx provides a variety of different methods for applying the IOSTANDARD for maximum flexibility. For a full description of different methods of applying attributes to control IOSTANDARD, refer to the "Using I/O Resources" chapter in <u>UG331</u>.

Together with placing the appropriate I/O symbol, two externally applied voltage levels,  $V_{CCO}$  and  $V_{REF}$ , select the desired signal standard. The  $V_{CCO}$  lines provide current to the output driver. The voltage on these lines determines the output voltage swing for all standards except GTL and GTLP.

All single-ended standards except the LVCMOS, LVTTL, and PCI varieties require a Reference Voltage ( $V_{REF}$ ) to bias the input-switching threshold. Once a configuration data file is loaded into the FPGA that calls for the I/Os of a given bank to use such a signal standard, a few specifically reserved I/O pins on the same bank automatically convert to  $V_{REF}$  inputs. When using one of the LVCMOS standards, these pins remain I/Os because the  $V_{CCO}$  voltage biases the input-switching threshold, so there is no need for  $V_{REF}$ . Select the  $V_{CCO}$  and  $V_{REF}$  levels to suit the desired single-ended standard according to Table 8.

In contrast, the 144-pin Thin Quad Flat Pack (TQ144) package and the 132-pin Chip-Scale Package (CP132) tie  $V_{CCO}$  together internally for the pair of banks on each side of the device. For example, the  $V_{CCO}$  Bank 0 and the  $V_{CCO}$  Bank 1 lines are tied together. The interconnected bank-pairs are 0/1, 2/3, 4/5, and 6/7. As a result, Spartan-3 devices in the CP132 and TQ144 packages support four independent  $V_{CCO}$  supplies.

*Note:* The CP132 package is discontinued. See <a href="http://www.xilinx.com/support/documentation/spartan-3\_customer\_notices.htm">http://www.xilinx.com/support/documentation/spartan-3\_customer\_notices.htm</a>.

## Spartan-3 FPGA Compatibility

Within the Spartan-3 family, all devices are pin-compatible by package. When the need for future logic resources outgrows the capacity of the Spartan-3 device in current use, a larger device in the same package can serve as a direct replacement. Larger devices may add extra  $V_{REF}$  and  $V_{CCO}$  lines to support a greater number of I/Os. In the larger device, more pins can convert from user I/Os to  $V_{REF}$  lines. Also, additional  $V_{CCO}$  lines are bonded out to pins that were "not connected" in the smaller device. Thus, it is important to plan for future upgrades at the time of the board's initial design by laying out connections to the extra pins.

The Spartan-3 family is not pin-compatible with any previous Xilinx FPGA family or with other platforms among the Spartan-3 Generation FPGAs.

## **Rules Concerning Banks**

When assigning I/Os to banks, it is important to follow the following  $V_{CCO}$  rules:

- Leave no V<sub>CCO</sub> pins unconnected on the FPGA.

- Set all V<sub>CCO</sub> lines associated with the (interconnected) bank to the same voltage level.

- The V<sub>CCO</sub> levels used by all standards assigned to the I/Os of the (interconnected) bank(s) must agree. The Xilinx development software checks for this. Tables 8, 9, and 10 describe how different standards use the V<sub>CCO</sub> supply.

- Only one of the following standards is allowed on outputs per bank: LVDS, LDT, LVDS\_EXT, or RSDS. This restriction is

for the eight banks in each device, even if the V<sub>CCO</sub> levels are shared across banks, as in the CP132 and TQ144

packages.

- If none of the standards assigned to the I/Os of the (interconnected) bank(s) uses V<sub>CCO</sub>, tie all associated V<sub>CCO</sub> lines to 2.5V.

- In general, apply 2.5V to V<sub>CCO</sub> Bank 4 from power-on to the end of configuration. Apply the same voltage to V<sub>CCO</sub> Bank 5 during parallel configuration or a Readback operation. For information on how to program the FPGA using 3.3V signals and power, see the 3.3V-Tolerant Configuration Interface section.

If any of the standards assigned to the Inputs of the bank use V<sub>REF</sub> then observe the following additional rules:

- Connect all V<sub>REF</sub> pins within the bank to the same voltage level.

- The V<sub>REF</sub> levels used by all standards assigned to the Inputs of the bank must agree. The Xilinx development software checks for this. Tables 8 and 10 describe how different standards use the V<sub>REF</sub> supply.

If none of the standards assigned to the Inputs of a bank use V<sub>REF</sub> for biasing input switching thresholds, all associated V<sub>REF</sub> pins function as User I/Os.

### Exceptions to Banks Supporting I/O Standards

Bank 5 of any Spartan-3 device in a VQ100, CP132, or TQ144 package does not support DCI signal standards. In this case, bank 5 has neither VRN nor VRP pins.

Furthermore, banks 4 and 5 of any Spartan-3 device in a VQ100 package do not support signal standards using  $V_{REF}$  (see Table 8). In this case, the two banks do not have any  $V_{REF}$  pins.

## Arrangement of RAM Blocks on Die

The XC3S50 has one column of block RAM. The Spartan-3 devices ranging from the XC3S200 to XC3S2000 have two columns of block RAM. The XC3S4000 and XC3S5000 have four columns. The position of the columns on the die is shown in Figure 1, page 3. For a given device, the total available RAM blocks are distributed equally among the columns. Table 12 shows the number of RAM blocks, the data storage capacity, and the number of columns for each device.

| •        |                               |                                       |                      |  |  |  |  |

|----------|-------------------------------|---------------------------------------|----------------------|--|--|--|--|

| Device   | Total Number<br>of RAM Blocks | Total Addressable<br>Locations (Bits) | Number of<br>Columns |  |  |  |  |

| XC3S50   | 4                             | 73,728                                | 1                    |  |  |  |  |

| XC3S200  | 12                            | 221,184                               | 2                    |  |  |  |  |

| XC3S400  | 16                            | 294,912                               | 2                    |  |  |  |  |

| XC3S1000 | 24                            | 442,368                               | 2                    |  |  |  |  |

| XC3S1500 | 32                            | 589,824                               | 2                    |  |  |  |  |

| XC3S2000 | 40                            | 737,280                               | 2                    |  |  |  |  |

| XC3S4000 | 96                            | 1,769,472                             | 4                    |  |  |  |  |

| XC3S5000 | 104                           | 1,916,928                             | 4                    |  |  |  |  |

Table 12: Number of RAM Blocks by Device

Block RAM and multipliers have interconnects between them that permit simultaneous operation; however, since the multiplier shares inputs with the upper data bits of block RAM, the maximum data path width of the block RAM is 18 bits in this case.

## The Internal Structure of the Block RAM

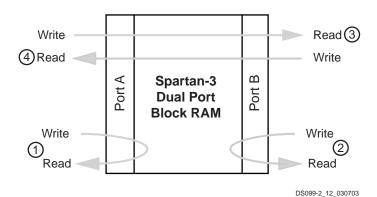

The block RAM has a dual port structure. The two identical data ports called A and B permit independent access to the common RAM block, which has a maximum capacity of 18,432 bits—or 16,384 bits when no parity lines are used. Each port has its own dedicated set of data, control and clock lines for synchronous read and write operations. There are four basic data paths, as shown in Figure 13: (1) write to and read from Port A, (2) write to and read from Port B, (3) data transfer from Port A to Port B, and (4) data transfer from Port B to Port A.

Figure 13: Block RAM Data Paths

# **Block RAM Port Signal Definitions**

Representations of the dual-port primitive RAMB16\_S[ $w_A$ ]\_S[ $w_B$ ] and the single-port primitive RAMB16\_S[w] with their associated signals are shown in Figure 14. These signals are defined in Table 13.

### Table 13: Block RAM Port Signals (Cont'd)

| Signal<br>Description    | Port A<br>Signal Name | Port B<br>Signal Name | Direction | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------------------------|-----------------------|-----------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Data Output Bus          | DOA                   | DOB                   | Output    | Basic data access occurs whenever WE is inactive. The DO outputs mirror the data stored in the addressed memory location.                                                                                                                                                                                                                                                                                                                                |

|                          |                       |                       |           | Data access with WE asserted is also possible if one of the following two attributes is chosen: WRITE_FIRST and READ_FIRST. WRITE_FIRST simultaneously presents the new input data on the DO output port and writes the data to the address RAM location. READ_FIRST presents the previously stored RAM data on the DO output port while writing new data to RAM.                                                                                        |

|                          |                       |                       |           | A third attribute, NO_CHANGE, latches the DO outputs upon the assertion of WE.                                                                                                                                                                                                                                                                                                                                                                           |

|                          |                       |                       |           | It is possible to configure a port's total data path width (w) to be 1, 2, 4, 9, 18, or 36 bits. This selection applies to both the DI and DO paths. See the DI signal description.                                                                                                                                                                                                                                                                      |

| Parity Data<br>Output(s) | DOPA                  | DOPB                  | Output    | Parity inputs represent additional bits included in the data input path to support error detection. The number of parity bits "p" included in the DI (same as for the DO bus) depends on a port's total data path width (w). See Table 14.                                                                                                                                                                                                               |

| Write Enable             | WEA                   | WEB                   | Input     | When asserted together with EN, this input enables the writing of data<br>to the RAM. In this case, the data access attributes WRITE_FIRST,<br>READ_FIRST or NO_CHANGE determines if and how data is updated<br>on the DO outputs. See the DO signal description.<br>When WE is inactive with EN asserted, read operations are still<br>possible. In this case, a transparent latch passes data from the<br>addressed memory location to the DO outputs. |

| Clock Enable             | ENA                   | ENB                   | Input     | When asserted, this input enables the CLK signal to synchronize Block<br>RAM functions as follows: the writing of data to the DI inputs (when WE<br>is also asserted), the updating of data at the DO outputs as well as the<br>setting/resetting of the DO output latches.<br>When de-asserted, the above functions are disabled.                                                                                                                       |

| Set/Reset                | SSRA                  | SSRB                  | Input     | When asserted, this pin forces the DO output latch to the value that the SRVAL attribute is set to. A Set/Reset operation on one port has no effect on the other ports functioning, nor does it disturb the memory's data contents. It is synchronized to the CLK signal.                                                                                                                                                                                |

| Clock                    | CLKA                  | CLKB                  | Input     | This input accepts the clock signal to which read and write operations<br>are synchronized. All associated port inputs are required to meet setup<br>times with respect to the clock signal's active edge. The data output bus<br>responds after a clock-to-out delay referenced to the clock signal's<br>active edge.                                                                                                                                   |

### **Port Aspect Ratios**

On a given port, it is possible to select a number of different possible widths (w - p) for the DI/DO buses as shown in Table 14. These two buses always have the same width. This data bus width selection is independent for each port. If the data bus width of Port A differs from that of Port B, the Block RAM automatically performs a bus-matching function. When data are written to a port with a narrow bus, then read from a port with a wide bus, the latter port will effectively combine "narrow" words to form "wide" words. Similarly, when data are written into a port with a wide bus, then read from a port with a narrow bus, the latter port will divide "wide" words to form "narrow" words. When the data bus width is eight bits or greater, extra parity bits become available. The width of the total data path (*w*) is the sum of the DI/DO bus width and any parity bits (*p*).

The width selection made for the DI/DO bus determines the number of address lines according to the relationship expressed below:

$$r = 14 - [\log(w - p)/\log(2)]$$

In turn, the number of address lines delimits the total number (n) of addressable locations or depth according to the following equation:

$$n = 2^r$$

Equation 2

Equation 1

## DLL Clock Input Connections

An external clock source enters the FPGA using a Global Clock Input Buffer (IBUFG), which directly accesses the global clock network or an Input Buffer (IBUF). Clock signals within the FPGA drive a global clock net using a Global Clock Multiplexer Buffer (BUFGMUX). The global clock net connects directly to the CLKIN input. The internal and external connections are shown in the [a] and [c] sections, respectively, of Figure 21. A differential clock (e.g., LVDS) can serve as an input to CLKIN.

### **DLL Clock Output and Feedback Connections**

As many as four of the nine DCM clock outputs can simultaneously drive the four BUFGMUX buffers on the same die edge (top or bottom). All DCM clock outputs can simultaneously drive general routing resources, including interconnect leading to OBUF buffers.

The feedback loop is essential for DLL operation and is established by driving the CLKFB input with either the CLK0 or the CLK2X signal so that any undesirable clock distribution delay is included in the loop. It is possible to use either of these two signals for synchronizing any of the seven DLL outputs: CLK0, CLK90, CLK180, CLK270, CLKDV, CLK2X, or CLK2X180. The value assigned to the CLK\_FEEDBACK attribute must agree with the physical feedback connection: a value of 1X for the CLK0 case, 2X for the CLK2X case. If the DCM is used in an application that does not require the DLL—i.e., only the DFS is used—then there is no feedback loop so CLK\_FEEDBACK is set to NONE.

CLK2X feedback is only supported on all mask revision 'E' and later devices (see Mask and Fab Revisions, page 58), on devices with the "GQ" fabrication code, and on all versions of the XC3S50 and XC3S1000.

There are two basic cases that determine how to connect the DLL clock outputs and feedback connections: on-chip synchronization and off-chip synchronization, which are illustrated in Figure 21.

## Configuration

Spartan-3 devices are configured by loading application specific configuration data into the internal configuration memory. Configuration is carried out using a subset of the device pins, some of which are "Dedicated" to one function only, while others, indicated by the term "Dual-Purpose", can be re-used as general-purpose User I/Os once configuration is complete.

Depending on the system design, several configuration modes are supported, selectable via mode pins. The mode pins M0, M1, and M2 are Dedicated pins. The mode pin settings are shown in Table 26.

| Configuration Mode <sup>(1)</sup> | МО | M1 | M2 | Synchronizing Clock | Data Width | Serial DOUT <sup>(2)</sup> |

|-----------------------------------|----|----|----|---------------------|------------|----------------------------|

| Master Serial                     | 0  | 0  | 0  | CCLK Output         | 1          | Yes                        |

| Slave Serial                      | 1  | 1  | 1  | CCLK Input          | 1          | Yes                        |

| Master Parallel                   | 1  | 1  | 0  | CCLK Output         | 8          | No                         |

| Slave Parallel                    | 0  | 1  | 1  | CCLK Input          | 8          | No                         |

| JTAG                              | 1  | 0  | 1  | TCK Input           | 1          | No                         |

### Table 26: Spartan-3 FPGAs Configuration Mode Pin Settings

#### Notes:

1. The voltage levels on the M0, M1, and M2 pins select the configuration mode.

2. The daisy chain is possible only in the Serial modes when DOUT is used.

The HSWAP\_EN input pin defines whether the I/O pins that are not actively used during configuration have pull-up resistors during configuration. By default, HSWAP\_EN is tied High (via an internal pull-up resistor if left floating) which shuts off the pull-up resistors on the user I/O pins during configuration. When HSWAP\_EN is tied Low, user I/Os have pull-ups during configuration. The Dedicated configuration pins (CCLK, DONE, PROG\_B, M2, M1, M0, HSWAP\_EN) and the JTAG pins (TDI, TMS, TCK, and TDO) always have a pull-up resistor to VCCAUX during configuration, regardless of the value on the HSWAP\_EN pin. Similarly, the dual-purpose INIT\_B pin has an internal pull-up resistor to VCCO\_4 or VCCO\_BOTTOM, depending on the package style.

Depending on the chosen configuration mode, the FPGA either generates a CCLK output, or CCLK is an input accepting an externally generated clock.

A persist option is available which can be used to force the configuration pins to retain their configuration function even after device configuration is complete. If the persist option is not selected then the configuration pins with the exception of CCLK, PROG\_B, and DONE can be used as user I/O in normal operation. The persist option does not apply to the boundary-scan related pins. The persist feature is valuable in applications that readback configuration data after entering the User mode.

| Table 27: Spartan-3 FPGA Configuration Data |

|---------------------------------------------|

|---------------------------------------------|

| Device   | File Sizes | Xilinx Platfor       | n Flash PROM           |

|----------|------------|----------------------|------------------------|

| Device   | File Sizes | Serial Configuration | Parallel Configuration |

| XC3S50   | 439,264    | XCF01S               | XCF08P                 |

| XC3S200  | 1,047,616  | XCF01S               | XCF08P                 |

| XC3S400  | 1,699,136  | XCF02S               | XCF08P                 |

| XC3S1000 | 3,223,488  | XCF04S               | XCF08P                 |

| XC3S1500 | 5,214,784  | XCF08P               | XCF08P                 |

| XC3S2000 | 7,673,024  | XCF08P               | XCF08P                 |

| XC3S4000 | 11,316,864 | XCF16P               | XCF16P                 |

| XC3S5000 | 13,271,936 | XCF16P               | XCF16P                 |

The maximum bitstream length that Spartan-3 FPGAs support in serial daisy-chains is 4,294,967,264 bits (4 Gbits), roughly equivalent to a daisy-chain with 323 XC3S5000 FPGAs. This is a limit only for serial daisy-chains where configuration data is passed via the FPGA's DOUT pin. There is no such limit for JTAG chains.

### Table 36: DC Characteristics of User I/Os Using Single-Ended Standards (Cont'd)

| Signal Sta                                       | andard | Test Co                                      | nditions | Logic Level C              | haracteristics             |  |

|--------------------------------------------------|--------|----------------------------------------------|----------|----------------------------|----------------------------|--|

| (IOSTANDARD) and Current<br>Drive Attribute (mA) |        | I <sub>OL</sub> I <sub>OH</sub><br>(mA) (mA) |          | V <sub>OL</sub><br>Max (V) | V <sub>OH</sub><br>Min (V) |  |

| /CMOS33 <sup>(4)</sup> 2                         |        | 2                                            | -2       | 0.4                        | V <sub>CCO</sub> – 0.4     |  |

|                                                  | 4      | 4                                            | -4       | _                          |                            |  |

|                                                  | 6      | 6                                            | 6        | _                          |                            |  |

|                                                  | 8      | 8                                            | -8       |                            |                            |  |

|                                                  | 12     | 12                                           | -12      |                            |                            |  |

|                                                  | 16     | 16                                           | -16      | _                          |                            |  |

|                                                  | 24     | 24                                           | -24      | _                          |                            |  |

| LVDCI_33,<br>LVDCI_DV2_33                        |        | Note 3                                       | Note 3   | _                          |                            |  |

| LVTTL <sup>(4)</sup>                             | 2      | 2                                            | -2       | 0.4                        | 2.4                        |  |

|                                                  | 4      | 4                                            | -4       |                            |                            |  |

|                                                  | 6      | 6                                            | 6        |                            |                            |  |

|                                                  | 8      | 8                                            | 8        |                            |                            |  |

|                                                  | 12     | 12                                           | -12      |                            |                            |  |

|                                                  | 16     | 16                                           | -16      |                            |                            |  |

|                                                  | 24     | 24                                           | -24      |                            |                            |  |

| PCI33_3                                          |        | Note 6                                       | Note 6   | 0.10V <sub>CCO</sub>       | 0.90V <sub>CCO</sub>       |  |

| SSTL18_I                                         |        | 6.7                                          | -6.7     | V <sub>TT</sub> – 0.475    | V <sub>TT</sub> + 0.475    |  |

| SSTL18_I_DCI                                     |        | Note 3                                       | Note 3   |                            |                            |  |

| SSTL18_II                                        |        | 13.4                                         | -13.4    | V <sub>TT</sub> – 0.475    | V <sub>TT</sub> + 0.475    |  |

| SSTL2_I                                          |        | 8.1                                          | -8.1     | V <sub>TT</sub> – 0.61     | V <sub>TT</sub> + 0.61     |  |

| SSTL2_I_DCI                                      |        | Note 3                                       | Note 3   |                            |                            |  |

| SSTL2_II <sup>(7)</sup>                          |        | 16.2                                         | -16.2    | V <sub>TT</sub> – 0.81     | V <sub>TT</sub> + 0.81     |  |

| SSTL2_II_DCI <sup>(7)</sup>                      |        | Note 3                                       | Note 3   |                            |                            |  |

#### Notes:

2.

The numbers in this table are based on the conditions set forth in Table 32 and Table 35. 1.

The numbers in this table are based on the conditions set for Descriptions of the symbols used in this table are as follows:  $I_{OL}$  – the output current condition under which VOL is tested  $V_{OL}$  – the output current condition under which VOH is tested  $V_{OL}$  – the output voltage that indicates a Low logic level  $V_{H}$  – the input voltage that indicates a High logic level  $V_{H}$  – the input voltage that indicates a High logic level  $V_{H}$  – the input voltage that indicates a High logic level  $V_{H}$  – the supply voltage for output drivers as well as LVCM

$V_{CCO}$  – the supply voltage for output drivers as well as LVCMOS, LVTTL, and PCI inputs  $V_{REF}$  – the reference voltage for setting the input switching threshold  $V_{TT}$  – the voltage applied to a resistor termination

Tested according to the standard's relevant specifications. When using the DCI version of a standard on a given I/O bank, that bank will consume more power than if the non-DCI version had been used instead. The additional power is drawn for the purpose of impedance-matching at the I/O pins. A portion of this power is dissipated in the two RREF resistors. 3.

For the LVCMOS and LVTTL standards: the same V<sub>OL</sub> and V<sub>OH</sub> limits apply for both the Fast and Slow slew attributes. 4.

All dedicated output pins (CCLK, DONE, and TDO) and dual-purpose totem-pole output pins (D0-D7 and BUSY/DOUT) exhibit the characteristics of 5. LVCMOS25 with 12 mA drive and slow slew rate. For information concerning the use of 3.3V signals, see 3.3V-Tolerant Configuration Interface, page 47.

Tested according to the relevant PCI specifications. For more information, see XAPP457. 6.

7. The minimum usable V<sub>TT</sub> voltage is 1.25V.

### Table 52: CLB Distributed RAM Switching Characteristics

| Symbol                                            | Description                                                                                                                                                      | -4   | 5    | -4   |      | Units |

|---------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|-------|

| Symbol                                            | Description                                                                                                                                                      | Min  | Max  | Min  | Max  | Units |

| Clock-to-Output                                   | Times                                                                                                                                                            | ·    |      |      |      |       |

| Т <sub>SHCKO</sub>                                | Time from the active edge at the CLK input to data appearing on the distributed RAM output                                                                       |      | 1.87 | -    | 2.15 | ns    |

| Setup Times                                       |                                                                                                                                                                  |      |      |      |      |       |

| T <sub>DS</sub>                                   | Setup time of data at the BX or BY input before the active transition at the CLK input of the distributed RAM                                                    |      | -    | 0.52 | -    | ns    |

| T <sub>AS</sub>                                   | Setup time of the F/G address inputs before the active transition at the CLK input of the distributed RAM                                                        |      | -    | 0.53 | -    | ns    |

| T <sub>WS</sub>                                   | Setup time of the write enable input before the active transition at the CLK input of the distributed RAM                                                        |      | -    | 0.37 | -    | ns    |

| Hold Times                                        |                                                                                                                                                                  |      |      |      |      |       |

| T <sub>DH,</sub> T <sub>AH,</sub> T <sub>WH</sub> | Hold time of the BX, BY data inputs, the F/G address inputs, or<br>the write enable input after the active transition at the CLK input<br>of the distributed RAM |      | -    | 0    | -    | ns    |

| Clock Pulse Wid                                   | Ith                                                                                                                                                              | 1    |      |      |      |       |

| T <sub>WPH</sub> , T <sub>WPL</sub>               | Minimum High or Low pulse width at CLK input                                                                                                                     | 0.85 | -    | 0.97 | -    | ns    |

### Table 53: CLB Shift Register Switching Characteristics

| Symbol                              | Description                                                                                                  |      | 5    | -4   |      | Units |

|-------------------------------------|--------------------------------------------------------------------------------------------------------------|------|------|------|------|-------|

| Symbol                              |                                                                                                              | Min  | Max  | Min  | Max  | Units |

| Clock-to-Output                     | t Times                                                                                                      |      |      |      |      |       |

| T <sub>REG</sub>                    | Time from the active edge at the CLK input to data appearing on the shift register output                    |      | 3.30 | -    | 3.79 | ns    |

| Setup Times                         |                                                                                                              |      |      |      |      |       |

| T <sub>SRLDS</sub>                  | Setup time of data at the BX or BY input before the active transition at the CLK input of the shift register |      | -    | 0.52 | -    | ns    |

| Hold Times                          |                                                                                                              | L    | -    |      | I    |       |

| T <sub>SRLDH</sub>                  | Hold time of the BX or BY data input after the active transition at the CLK input of the shift register      |      | -    | 0    | _    | ns    |

| Clock Pulse Wig                     | dth                                                                                                          | 1    |      | u    |      |       |

| T <sub>WPH</sub> , T <sub>WPL</sub> | Minimum High or Low pulse width at CLK input                                                                 | 0.85 | -    | 0.97 | -    | ns    |

www.xilinx.com

# Digital Clock Manager (DCM) Timing

For specification purposes, the DCM consists of three key components: the Delay-Locked Loop (DLL), the Digital Frequency Synthesizer (DFS), and the Phase Shifter (PS).

Aspects of DLL operation play a role in all DCM applications. All such applications inevitably use the CLKIN and the CLKFB inputs connected to either the CLK0 or the CLK2X feedback, respectively. Thus, specifications in the DLL tables (Table 58 and Table 59) apply to any application that only employs the DLL component. When the DFS and/or the PS components are used together with the DLL, then the specifications listed in the DFS and PS tables (Table 60 through Table 63) supersede any corresponding ones in the DLL tables. DLL specifications that do not change with the addition of DFS or PS functions are presented in Table 58 and Table 59.

Period jitter and cycle-cycle jitter are two (of many) different ways of characterizing clock jitter. Both specifications describe statistical variation from a mean value.

Period jitter is the worst-case deviation from the average clock period of all clock cycles in the collection of clock periods sampled (usually from 100,000 to more than a million samples for specification purposes). In a histogram of period jitter, the mean value is the clock period.

Cycle-cycle jitter is the worst-case difference in clock period between adjacent clock cycles in the collection of clock periods sampled. In a histogram of cycle-cycle jitter, the mean value is zero.

### Delay-Locked Loop (DLL)

### Table 58: Recommended Operating Conditions for the DLL

| Symbol                |                           |                                                                                             |                                             | Speed Grade         |                      |                     |                       |       |

|-----------------------|---------------------------|---------------------------------------------------------------------------------------------|---------------------------------------------|---------------------|----------------------|---------------------|-----------------------|-------|

|                       |                           | Description                                                                                 | Frequency Mode/<br>F <sub>CLKIN</sub> Range | -5                  |                      | -4                  |                       | Units |

|                       |                           |                                                                                             |                                             | Min                 | Max                  | Min                 | Max                   |       |

| Input Fi              | requency Ranges           |                                                                                             |                                             |                     |                      |                     |                       |       |

| F <sub>CLKIN</sub>    | CLKIN_FREQ_DLL_LF         | Frequency for the CLKIN input                                                               | Low                                         | 18 <mark>(2)</mark> | 167 <mark>(3)</mark> | 18 <mark>(2)</mark> | 167 <mark>(3)</mark>  | MHz   |

|                       | CLKIN_FREQ_DLL_HF         |                                                                                             | High                                        | 48                  | 280 <sup>(3)</sup>   | 48                  | 280 <sup>(3)(4)</sup> | MHz   |

| Input P               | ulse Requirements         |                                                                                             |                                             |                     |                      |                     |                       |       |

| CLKIN_                | PULSE                     | CLKIN pulse width as a percentage of the CLKIN period                                       | $F_{CLKIN} \le 100 \text{ MHz}$             | 40%                 | 60%                  | 40%                 | 60%                   | -     |

|                       |                           |                                                                                             | F <sub>CLKIN</sub> > 100 MHz                | 45%                 | 55%                  | 45%                 | 55%                   | -     |

| Input C               | lock Jitter Tolerance and | Delay Path Variation <sup>(5)</sup>                                                         |                                             |                     |                      |                     |                       |       |

| CLKIN_                | CYC_JITT_DLL_LF           | Cycle-to-cycle jitter at the CLKIN                                                          | Low                                         | -                   | ±300                 | -                   | ±300                  | ps    |

| CLKIN_                | CYC_JITT_DLL_HF           | input                                                                                       | High                                        | -                   | ±150                 | -                   | ±150                  | ps    |

| CLKIN_PER_JITT_DLL_LF |                           | Period jitter at the CLKIN input                                                            | All                                         | -                   | ±1                   | -                   | ±1                    | ns    |

| CLKIN_PER_JITT_DLL_HF |                           |                                                                                             |                                             | -                   |                      | -                   |                       |       |

| CLKFB_DELAY_VAR_EXT   |                           | Allowable variation of off-chip<br>feedback delay from the DCM<br>output to the CLKFB input | All                                         | -                   | ±1                   | -                   | ±1                    | ns    |

#### Notes:

1. DLL specifications apply when any of the DLL outputs (CLK0, CLK90, CLK180, CLK270, CLK2X, CLK2X180, or CLKDV) are in use.

2. The DFS, when operating independently of the DLL, supports lower F<sub>CLKIN</sub> frequencies. See Table 60.

The CLKIN\_DIVIDE\_BY\_2 attribute can be used to increase the effective input frequency range up to F<sub>BUFG</sub>. When set to TRUE, CLKIN\_DIVIDE\_BY\_2 divides the incoming clock frequency by two as it enters the DCM.

4. Industrial temperature range devices have additional requirements for continuous clocking, as specified in Table 64.

5. CLKIN input jitter beyond these limits may cause the DCM to lose lock. See UG331 for more details.

### **Miscellaneous DCM Timing**

### Table 64: Miscellaneous DCM Timing

| 0 miliol                           | Barrista                                                                                       | DLL               | Temperatu  |            |                 |

|------------------------------------|------------------------------------------------------------------------------------------------|-------------------|------------|------------|-----------------|

| Symbol                             | Description                                                                                    | Frequency<br>Mode | Commercial | Industrial | Units           |

| DCM_INPUT_CLOCK_STOP               | Maximum duration that the CLKIN and CLKFB signals can be stopped <sup><math>(1,2)</math></sup> | Any               | 100        | 100        | ms              |

| DCM_RST_PW_MIN                     | Minimum duration of a RST pulse width                                                          | Any               | 3          | 3          | CLKIN<br>cycles |

| DCM_RST_PW_MAX <sup>(3)</sup>      | Maximum duration of a RST pulse width <sup>(1,2)</sup>                                         | Low               | N/A        | N/A        | seconds         |

|                                    |                                                                                                | High              | N/A        | 10         | seconds         |

| DCM_CONFIG_LAG_TIME <sup>(4)</sup> | Maximum duration from V <sub>CCINT</sub> applied to FPGA configuration successfully completed  | Low               | N/A        | N/A        | minutes         |

|                                    | (DONE pin goes High) and clocks applied to DCM DLL <sup>(1,2)</sup>                            | High              | N/A        | 10         | minutes         |

#### Notes:

These limits only apply to applications that use the DCM DLL outputs (CLK0, CLK90, CLK180, CLK270, CLK2X, CLK2X180, and CLKDV). The DCM DFS outputs (CLKFX, CLKFX180) are unaffected. Required due to effects of device cooling: see "Momentarily Stopping CLKIN" in Chapter 3 of UG331.

2. Industrial-temperature applications that use the DLL in High-Frequency mode must use a continuous or increasing operating frequency. The DLL under these conditions does not support reducing the operating frequency once establishing an initial operating frequency.

3. This specification is equivalent to the Virtex-4 FPGA DCM\_RESET specification.

4. This specification is equivalent to the Virtex-4 FPGA TCONFIG specification.

## VREF: User I/O or Input Buffer Reference Voltage for Special Interface Standards

These pins are individual user-I/O pins unless collectively they supply an input reference voltage, VREF\_#, for any SSTL, HSTL, GTL, or GTLP I/Os implemented in the associated I/O bank. The '#' character in the pin name represents an integer, 0 through 7, that indicates the associated I/O bank.

The VREF function becomes active for this pin whenever a signal standard requiring a reference voltage is used in the associated bank. If used as a user I/O, then each pin behaves as an independent I/O described in the I/O type section. If used for a reference voltage within a bank, then *all* VREF pins within the bank must be connected to the same reference voltage.

Spartan-3 devices are designed and characterized to support certain I/O standards when VREF is connected to +1.25V, +1.10V, +1.00V, +0.90V, +0.80V, and +0.75V. During configuration, the VREF pins behave exactly like user-I/O pins.

If designing for footprint compatibility across the range of devices in a specific package, and if the VREF\_# pins within a bank connect to an input reference voltage, then also connect any N.C. (not connected) pins on the smaller devices in that package to the input reference voltage. More details are provided later for each package type.

## N.C. Type: Unconnected Package Pins

Pins marked as "N.C." are unconnected for the specific device/package combination. For other devices in this same package, this pin may be used as an I/O or VREF connection. In both the pinout tables and the footprint diagrams, unconnected pins are noted with either a black diamond symbol ( $\blacklozenge$ ) or a black square symbol ( $\blacksquare$ ).

If designing for footprint compatibility across multiple device densities, check the pin types of the other Spartan-3 devices available in the same footprint. If the N.C. pin matches to VREF pins in other devices, and the VREF pins are used in the associated I/O bank, then connect the N.C. to the VREF voltage source.

# VCCO Type: Output Voltage Supply for I/O Bank

Each I/O bank has its own set of voltage supply pins that determines the output voltage for the output buffers in the I/O bank. Furthermore, for some I/O standards such as LVCMOS, LVCMOS25, LVTTL, etc., VCCO sets the input threshold voltage on the associated input buffers.

Spartan-3 devices are designed and characterized to support various I/O standards for VCCO values of +1.2V, +1.5V, +1.8V, +2.5V, and +3.3V.

Most VCCO pins are labeled as VCCO\_# where the '#' symbol represents the associated I/O bank number, an integer ranging from 0 to 7. In the 144-pin TQFP package (TQ144) however, the VCCO pins along an edge of the device are combined into a single VCCO input. For example, the VCCO inputs for Bank 0 and Bank 1 along the top edge of the package are combined and relabeled VCCO\_TOP. The bottom, left, and right edges are similarly combined.

In Serial configuration mode, VCCO\_4 must be at a level compatible with the attached configuration memory or data source. In Parallel configuration mode, both VCCO\_4 and VCCO\_5 must be at the same compatible voltage level.

All VCCO inputs to a bank must be connected together and to the voltage supply. Furthermore, there must be sufficient supply decoupling to guarantee problem-free operation, as described in <u>XAPP623</u>: *Power Distribution System (PDS) Design: Using Bypass/Decoupling Capacitors*.

# VCCINT Type: Voltage Supply for Internal Core Logic

Internal core logic circuits such as the configurable logic blocks (CLBs) and programmable interconnect operate from the VCCINT voltage supply inputs. VCCINT must be +1.2V.

All VCCINT inputs must be connected together and to the +1.2V voltage supply. Furthermore, there must be sufficient supply decoupling to guarantee problem-free operation, as described in <u>XAPP623</u>.

# VCCAUX Type: Voltage Supply for Auxiliary Logic

The VCCAUX pins supply power to various auxiliary circuits, such as to the Digital Clock Managers (DCMs), the JTAG pins, and to the dedicated configuration pins (CONFIG type). VCCAUX must be +2.5V.

### Table 86: Spartan-3 FPGA Package Thermal Characteristics (Cont'd)

|                          |          | Junction-to-           |                         | Junction-to-A        |         |         |         |         |

|--------------------------|----------|------------------------|-------------------------|----------------------|---------|---------|---------|---------|

| Package                  | Device   | Case ( $\theta_{JC}$ ) | oard (θ <sub>JB</sub> ) | Still Air<br>(0 LFM) | 250 LFM | 500 LFM | 750 LFM | Units   |

| FG(G)1156 <sup>(1)</sup> | XC3S4000 | 1.9                    | -                       | 14.7                 | 11.4    | 10.1    | 9.0     | °C/Watt |

| FG(G)1150(9)             | XC3S5000 | 1.9                    | 8.9                     | 14.5                 | 11.3    | 10.0    | 8.9     | °C/Watt |

#### Notes:

1. The CP132, CPG132, FG1156, and FGG1156 packages are discontinued. See http://www.xilinx.com/support/documentation/spartan-3\_customer\_notices.htm.

## VQ100: 100-lead Very-Thin Quad Flat Package

The XC3S50 and the XC3S200 devices are available in the 100-lead very-thin quad flat package, VQ100. Both devices share a common footprint for this package as shown in Table 87 and Figure 44.

All the package pins appear in Table 87 and are sorted by bank number, then by pin name. Pairs of pins that form a differential I/O pair appear together in the table. The table also shows the pin number for each pin and the pin type, as defined earlier.

An electronic version of this package pinout table and footprint diagram is available for download from the Xilinx website at <a href="http://www.xilinx.com/support/documentation/data\_sheets/s3\_pin.zip">http://www.xilinx.com/support/documentation/data\_sheets/s3\_pin.zip</a>.

### **Pinout Table**

#### Table 87: VQ100 Package Pinout

| Bank | XC3S50<br>XC3S200<br>Pin Name | VQ100<br>Pin<br>Number | Туре |

|------|-------------------------------|------------------------|------|

| 0    | IO_L01N_0/VRP_0               | P97                    | DCI  |

| 0    | IO_L01P_0/VRN_0               | P96                    | DCI  |

| 0    | IO_L31N_0                     | P92                    | I/O  |

| 0    | IO_L31P_0/VREF_0              | P91                    | VREF |

| 0    | IO_L32N_0/GCLK7               | P90                    | GCLK |

| 0    | IO_L32P_0/GCLK6               | P89                    | GCLK |

| 0    | VCCO_0                        | P94                    | VCCO |

| 1    | 10                            | P81                    | I/O  |

| 1    | IO_L01N_1/VRP_1               | P80                    | DCI  |

| 1    | IO_L01P_1/VRN_1               | P79                    | DCI  |

| 1    | IO_L31N_1/VREF_1              | P86                    | VREF |

| 1    | IO_L31P_1                     | P85                    | I/O  |

| 1    | IO_L32N_1/GCLK5               | P88                    | GCLK |

| 1    | IO_L32P_1/GCLK4               | P87                    | GCLK |

| 1    | VCCO_1                        | P83                    | VCCO |

| 2    | IO_L01N_2/VRP_2               | P75                    | DCI  |

| 2    | IO_L01P_2/VRN_2               | P74                    | DCI  |

| 2    | IO_L21N_2                     | P72                    | I/O  |

| 2    | IO_L21P_2                     | P71                    | I/O  |

| 2    | IO_L24N_2                     | P68                    | I/O  |

| 2    | IO_L24P_2                     | P67                    | I/O  |

www.xilinx.com

# TQ144: 144-lead Thin Quad Flat Package

The XC3S50, the XC3S200, and the XC3S400 are available in the 144-lead thin quad flat package, TQ144. All devices share a common footprint for this package as shown in Table 91 and Figure 46.

The TQ144 package only has four separate VCCO inputs, unlike the BGA packages, which have eight separate VCCO inputs. The TQ144 package has a separate VCCO input for the top, bottom, left, and right. However, there are still eight separate I/O banks, as shown in Table 91 and Figure 46. Banks 0 and 1 share the VCCO\_TOP input, Banks 2 and 3 share the VCCO\_RIGHT input, Banks 4 and 5 share the VCCO\_BOTTOM input, and Banks 6 and 7 share the VCCO\_LEFT input.

All the package pins appear in Table 91 and are sorted by bank number, then by pin name. Pairs of pins that form a differential I/O pair appear together in the table. The table also shows the pin number for each pin and the pin type, as defined earlier.

An electronic version of this package pinout table and footprint diagram is available for download from the Xilinx website at <a href="http://www.xilinx.com/support/documentation/data\_sheets/s3\_pin.zip">http://www.xilinx.com/support/documentation/data\_sheets/s3\_pin.zip</a>.

### **Pinout Table**

| Bank | XC3S50, XC3S200,<br>XC3S400 Pin Name | TQ144 Pin<br>Number | Туре |

|------|--------------------------------------|---------------------|------|

| 0    | IO_L01N_0/VRP_0                      | P141                | DCI  |

| 0    | IO_L01P_0/VRN_0                      | P140                | DCI  |

| 0    | IO_L27N_0                            | P137                | I/O  |

| 0    | IO_L27P_0                            | P135                | I/O  |

| 0    | IO_L30N_0                            | P132                | I/O  |

| 0    | IO_L30P_0                            | P131                | I/O  |

| 0    | IO_L31N_0                            | P130                | I/O  |

| 0    | IO_L31P_0/VREF_0                     | P129                | VREF |

| 0    | IO_L32N_0/GCLK7                      | P128                | GCLK |

| 0    | IO_L32P_0/GCLK6                      | P127                | GCLK |

| 1    | Ю                                    | P116                | I/O  |

| 1    | IO_L01N_1/VRP_1                      | P113                | DCI  |

| 1    | IO_L01P_1/VRN_1                      | P112                | DCI  |

| 1    | IO_L28N_1                            | P119                | I/O  |

| 1    | IO_L28P_1                            | P118                | I/O  |

| 1    | IO_L31N_1/VREF_1                     | P123                | VREF |

| 1    | IO_L31P_1                            | P122                | I/O  |

| 1    | IO_L32N_1/GCLK5                      | P125                | GCLK |

| 1    | IO_L32P_1/GCLK4                      | P124                | GCLK |

| 2    | IO_L01N_2/VRP_2                      | P108                | DCI  |

| 2    | IO_L01P_2/VRN_2                      | P107                | DCI  |

| 2    | IO_L20N_2                            | P105                | I/O  |

| 2    | IO_L20P_2                            | P104                | I/O  |

| 2    | IO_L21N_2                            | P103                | I/O  |

| 2    | IO_L21P_2                            | P102                | I/O  |

| 2    | IO_L22N_2                            | P100                | I/O  |

| 2    | IO_L22P_2                            | P99                 | I/O  |

Table 91: TQ144 Package Pinout

www.xilinx.com

### Table 103: FG676 Package Pinout (Cont'd)

| Bank | XC3S1000<br>Pin Name | XC3S1500<br>Pin Name            | XC3S2000<br>Pin Name | XC3S4000<br>Pin Name | XC3S5000<br>Pin Name | FG676 Pin<br>Number | Туре                |

|------|----------------------|---------------------------------|----------------------|----------------------|----------------------|---------------------|---------------------|

| 1    | N.C. (�)             | IO_L18P_1                       | IO_L18P_1            | IO_L18P_1            | IO <sup>(3)</sup>    | C18                 | I/O                 |

| 1    | IO_L19N_1            | IO_L19N_1                       | IO_L19N_1            | IO_L19N_1            | IO_L19N_1            | F17                 | I/O                 |

| 1    | IO_L19P_1            | IO_L19P_1                       | IO_L19P_1            | IO_L19P_1            | IO_L19P_1            | G17                 | I/O                 |

| 1    | IO_L22N_1            | IO_L22N_1                       | IO_L22N_1            | IO_L22N_1            | IO_L22N_1            | D17                 | I/O                 |

| 1    | IO_L22P_1            | IO_L22P_1                       | IO_L22P_1            | IO_L22P_1            | IO_L22P_1            | E17                 | I/O                 |

| 1    | N.C. (�)             | IO_L23N_1                       | IO_L23N_1            | IO_L23N_1            | IO_L23N_1            | A17                 | I/O                 |

| 1    | N.C. (�)             | IO_L23P_1                       | IO_L23P_1            | IO_L23P_1            | IO_L23P_1            | B17                 | I/O                 |

| 1    | IO_L24N_1            | IO_L24N_1                       | IO_L24N_1            | IO_L24N_1            | IO_L24N_1            | G16                 | I/O                 |

| 1    | IO_L24P_1            | IO_L24P_1                       | IO_L24P_1            | IO_L24P_1            | IO_L24P_1            | H16                 | I/O                 |

| 1    | IO_L25N_1            | IO_L25N_1                       | IO_L25N_1            | IO_L25N_1            | IO_L25N_1            | E16                 | I/O                 |

| 1    | IO_L25P_1            | IO_L25P_1                       | IO_L25P_1            | IO_L25P_1            | IO_L25P_1            | F16                 | I/O                 |

| 1    | N.C. (�)             | IO_L26N_1                       | IO_L26N_1            | IO_L26N_1            | IO_L26N_1            | A16                 | I/O                 |

| 1    | N.C. (�)             | IO_L26P_1                       | IO_L26P_1            | IO_L26P_1            | IO_L26P_1            | B16                 | I/O                 |

| 1    | IO_L27N_1            | IO_L27N_1                       | IO_L27N_1            | IO_L27N_1            | IO_L27N_1            | G15                 | I/O                 |

| 1    | IO_L27P_1            | IO_L27P_1                       | IO_L27P_1            | IO_L27P_1            | IO_L27P_1            | H15                 | I/O                 |

| 1    | IO_L28N_1            | IO_L28N_1                       | IO_L28N_1            | IO_L28N_1            | IO_L28N_1            | E15                 | I/O                 |

| 1    | IO_L28P_1            | IO_L28P_1                       | IO_L28P_1            | IO_L28P_1            | IO_L28P_1            | F15                 | I/O                 |

| 1    | IO_L29N_1            | IO_L29N_1                       | IO_L29N_1            | IO_L29N_1            | IO_L29N_1            | A15                 | I/O                 |

| 1    | IO_L29P_1            | IO_L29P_1                       | IO_L29P_1            | IO_L29P_1            | IO_L29P_1            | B15                 | I/O                 |

| 1    | IO_L30N_1            | IO_L30N_1                       | IO_L30N_1            | IO_L30N_1            | IO_L30N_1            | G14                 | I/O                 |

| 1    | IO_L30P_1            | IO_L30P_1                       | IO_L30P_1            | IO_L30P_1            | IO_L30P_1            | H14                 | I/O                 |

| 1    | IO_L31N_1/VREF_1     | IO_L31N_1/VREF_1                | IO_L31N_1/VREF_1     | IO_L31N_1/VREF_1     | IO_L31N_1/VREF_1     | D14                 | VREF                |

| 1    | IO_L31P_1            | IO_L31P_1                       | IO_L31P_1            | IO_L31P_1            | IO_L31P_1            | E14                 | I/O                 |

| 1    | IO_L32N_1/GCLK5      | IO_L32N_1/GCLK5                 | IO_L32N_1/GCLK5      | IO_L32N_1/GCLK5      | IO_L32N_1/GCLK5      | B14                 | GCLK                |

| 1    | IO_L32P_1/GCLK4      | IO_L32P_1/GCLK4                 | IO_L32P_1/GCLK4      | IO_L32P_1/GCLK4      | IO_L32P_1/GCLK4      | C14                 | GCLK                |

| 1    | VCCO_1               | VCCO_1                          | VCCO_1               | VCCO_1               | VCCO_1               | C16                 | VCCO                |

| 1    | VCCO_1               | VCCO_1                          | VCCO_1               | VCCO_1               | VCCO_1               | C20                 | VCCO                |

| 1    | VCCO_1               | VCCO_1                          | VCCO_1               | VCCO_1               | VCCO_1               | H17                 | VCCO                |

| 1    | VCCO_1               | VCCO_1                          | VCCO_1               | VCCO_1               | VCCO_1               | H18                 | VCCO                |

| 1    | VCCO_1               | VCCO_1                          | VCCO_1               | VCCO_1               | VCCO_1               | J14                 | VCCO                |

| 1    | VCCO_1               | VCCO_1                          | VCCO_1               | VCCO_1               | VCCO_1               | J15                 | VCCO                |

| 1    | VCCO_1               | VCCO_1                          | VCCO_1               | VCCO_1               | VCCO_1               | J16                 | VCCO                |

| 1    | VCCO_1               | VCCO_1                          | VCCO_1               | VCCO_1               | VCCO_1               | K14                 | VCCO                |

| 2    | N.C. (�)             | N.C. (■)                        | Ю                    | Ю                    | IO                   | F22                 | I/O                 |

| 2    | IO_L01N_2/VRP_2      | IO_L01N_2/VRP_2                 | IO_L01N_2/VRP_2      | IO_L01N_2/VRP_2      | IO_L01N_2/VRP_2      | C25                 | DCI                 |

| 2    | IO_L01P_2/VRN_2      | IO_L01P_2/VRN_2                 | IO_L01P_2/VRN_2      | IO_L01P_2/VRN_2      | IO_L01P_2/VRN_2      | C26                 | DCI                 |

| 2    | IO_L02N_2            | IO_L02N_2                       | IO_L02N_2            | IO_L02N_2            | IO_L02N_2            | E23                 | I/O                 |

| 2    | IO_L02P_2            | IO_L02P_2                       | IO_L02P_2            | IO_L02P_2            | IO_L02P_2            | E24                 | I/O                 |

| 2    | IO_L03N_2/VREF_2     | IO_L03N_2/VREF_2 <sup>(1)</sup> | IO_L03N_2/VREF_2     | IO_L03N_2/VREF_2     | IO_L03N_2/VREF_2     | D25                 | VREF <sup>(1)</sup> |

| 2    | IO_L03P_2            | IO_L03P_2                       | IO_L03P_2            | IO_L03P_2            | IO_L03P_2            | D26                 | I/O                 |

| 2    | N.C. (�)             | IO_L05N_2                       | IO_L05N_2            | IO_L05N_2            | IO_L05N_2            | E25                 | I/O                 |

| 2    | N.C. (�)             | IO_L05P_2                       | IO_L05P_2            | IO_L05P_2            | IO_L05P_2            | E26                 | I/O                 |

### Table 103: FG676 Package Pinout (Cont'd)

| Bank | XC3S1000<br>Pin Name | XC3S1500<br>Pin Name | XC3S2000<br>Pin Name | XC3S4000<br>Pin Name | XC3S5000<br>Pin Name | FG676 Pin<br>Number | Туре |

|------|----------------------|----------------------|----------------------|----------------------|----------------------|---------------------|------|

| 3    | IO_L19N_3            | IO_L19N_3            | IO_L19N_3            | IO_L19N_3            | IO_L19N_3            | W26                 | I/O  |

| 3    | IO_L19P_3            | IO_L19P_3            | IO_L19P_3            | IO_L19P_3            | IO_L19P_3            | W25                 | I/O  |

| 3    | IO_L20N_3            | IO_L20N_3            | IO_L20N_3            | IO_L20N_3            | IO_L20N_3            | U20                 | I/O  |

| 3    | IO_L20P_3            | IO_L20P_3            | IO_L20P_3            | IO_L20P_3            | IO_L20P_3            | V20                 | I/O  |

| 3    | IO_L21N_3            | IO_L21N_3            | IO_L21N_3            | IO_L21N_3            | IO_L21N_3            | V23                 | I/O  |

| 3    | IO_L21P_3            | IO_L21P_3            | IO_L21P_3            | IO_L21P_3            | IO_L21P_3            | V22                 | I/O  |

| 3    | IO_L22N_3            | IO_L22N_3            | IO_L22N_3            | IO_L22N_3            | IO_L22N_3            | V25                 | I/O  |

| 3    | IO_L22P_3            | IO_L22P_3            | IO_L22P_3            | IO_L22P_3            | IO_L22P_3            | V24                 | I/O  |

| 3    | IO_L23N_3            | IO_L23N_3            | IO_L23N_3            | IO_L23N_3            | IO_L23N_3            | U22                 | I/O  |

| 3    | IO_L23P_3/VREF_3     | IO_L23P_3/VREF_3     | IO_L23P_3/VREF_3     | IO_L23P_3/VREF_3     | IO_L23P_3/VREF_3     | U21                 | VREF |

| 3    | IO_L24N_3            | IO_L24N_3            | IO_L24N_3            | IO_L24N_3            | IO_L24N_3            | U24                 | I/O  |

| 3    | IO_L24P_3            | IO_L24P_3            | IO_L24P_3            | IO_L24P_3            | IO_L24P_3            | U23                 | I/O  |