### AMD Xilinx - XC3S1000-5FT256C Datasheet

Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                              |

|--------------------------------|--------------------------------------------------------------|

| Product Status                 | Active                                                       |

| Number of LABs/CLBs            | 1920                                                         |

| Number of Logic Elements/Cells | 17280                                                        |

| Total RAM Bits                 | 442368                                                       |

| Number of I/O                  | 173                                                          |

| Number of Gates                | 1000000                                                      |

| Voltage - Supply               | 1.14V ~ 1.26V                                                |

| Mounting Type                  | Surface Mount                                                |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                              |

| Package / Case                 | 256-LBGA                                                     |

| Supplier Device Package        | 256-FTBGA (17x17)                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/xilinx/xc3s1000-5ft256c |

|                                |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Table 3 shows the number of user I/Os as well as the number of differential I/O pairs available for each device/package combination.

|                   | Available User I/Os and Differential (Diff) I/O Pairs by Package Type |      |                     |                     |            |      |            |      |            |      |            |      |            |      |            |      |            |      |                      |                              |

|-------------------|-----------------------------------------------------------------------|------|---------------------|---------------------|------------|------|------------|------|------------|------|------------|------|------------|------|------------|------|------------|------|----------------------|------------------------------|

| Package           | VQ1<br>VQG                                                            |      | CP13<br>CPG         |                     | TQ1<br>TQG |      | PQ2<br>PQG |      | FT2<br>FTG |      | FG3<br>FGG |      | FG4<br>FGG |      | FG6<br>FGG |      | FG9<br>FGG |      |                      | 156 <mark>(1)</mark><br>1156 |

| Footprint<br>(mm) | 16 x                                                                  | 16   | 8 x                 | 8                   | 22 x       | 22   | 30.6 x     | 30.6 | 17 x       | 17   | 19 x       | 19   | 23 x       | 23   | 27 x       | 27   | 31 x       | 31   | 35 3                 | x 35                         |

| Device            | User                                                                  | Diff | User                | Diff                | User       | Diff | User       | Diff | User       | Diff | User       | Diff | User       | Diff | User       | Diff | User       | Diff | User                 | Diff                         |

| XC3S50            | 63                                                                    | 29   | 89 <mark>(1)</mark> | 44 <mark>(1)</mark> | 97         | 46   | 124        | 56   | -          | -    | -          | -    | -          | -    | -          | -    | -          | -    | -                    | -                            |

| XC3S200           | 63                                                                    | 29   | -                   | -                   | 97         | 46   | 141        | 62   | 173        | 76   | -          | _    | -          | _    | -          | -    | -          | I    | -                    | -                            |

| XC3S400           | -                                                                     | _    | -                   | -                   | 97         | 46   | 141        | 62   | 173        | 76   | 221        | 100  | 264        | 116  | -          | -    | -          | -    | -                    | -                            |

| XC3S1000          | -                                                                     | -    | -                   | -                   | -          | -    | -          | -    | 173        | 76   | 221        | 100  | 333        | 149  | 391        | 175  | -          | 1    | Ι                    | -                            |

| XC3S1500          | -                                                                     | -    | -                   | -                   | -          | -    | -          | -    | -          | -    | 221        | 100  | 333        | 149  | 487        | 221  | -          | -    | -                    | -                            |

| XC3S2000          | -                                                                     | -    | -                   | -                   | -          | -    | -          | -    | -          | -    | -          | -    | 333        | 149  | 489        | 221  | 565        | 270  | -                    | -                            |

| XC3S4000          | -                                                                     | -    | 1                   | -                   | -          | -    | -          | -    | -          | -    | -          | -    | -          | -    | 489        | 221  | 633        | 300  | 712 <mark>(1)</mark> | 312 <mark>(1)</mark>         |

| XC3S5000          | -                                                                     | -    | -                   | -                   | -          | -    | -          | -    | -          | -    | -          | -    | -          | -    | 489        | 221  | 633        | 300  | 784 <sup>(1)</sup>   | 344 <sup>(1)</sup>           |

#### Table 3: Spartan-3 Device I/O Chart

#### Notes:

1. The CP132, CPG132, FG1156, and FGG1156 packages are discontinued. See http://www.xilinx.com/support/documentation/spartan-3\_customer\_notices.htm.

2. All device options listed in a given package column are pin-compatible.

3. User = Single-ended user I/O pins. Diff = Differential I/O pairs.

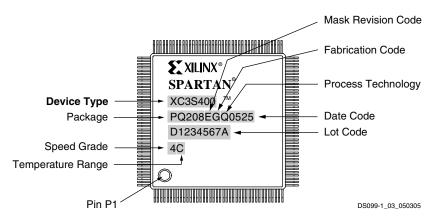

## Package Marking

Figure 2 shows the top marking for Spartan-3 FPGAs in the quad-flat packages. Figure 3 shows the top marking for Spartan-3 FPGAs in BGA packages except the 132-ball chip-scale package (CP132 and CPG132). The markings for the BGA packages are nearly identical to those for the quad-flat packages, except that the marking is rotated with respect to the ball A1 indicator. Figure 4 shows the top marking for Spartan-3 FPGAs in the CP132 and CPG132 packages.

The "5c" and "41" part combinations may be dual marked as "5c/41". Devices with the dual mark can be used as either -5C or -4I devices. Devices with a single mark are only guaranteed for the marked speed grade and temperature range. Some specifications vary according to mask revision. Mask revision E devices are errata-free. All shipments since 2006 have been mask revision E.

Figure 2: Spartan-3 FPGA QFP Package Marking Example for Part Number XC3S400-4PQ208C

In contrast, the 144-pin Thin Quad Flat Pack (TQ144) package and the 132-pin Chip-Scale Package (CP132) tie  $V_{CCO}$  together internally for the pair of banks on each side of the device. For example, the  $V_{CCO}$  Bank 0 and the  $V_{CCO}$  Bank 1 lines are tied together. The interconnected bank-pairs are 0/1, 2/3, 4/5, and 6/7. As a result, Spartan-3 devices in the CP132 and TQ144 packages support four independent  $V_{CCO}$  supplies.

*Note:* The CP132 package is discontinued. See <a href="http://www.xilinx.com/support/documentation/spartan-3\_customer\_notices.htm">http://www.xilinx.com/support/documentation/spartan-3\_customer\_notices.htm</a>.

## Spartan-3 FPGA Compatibility

Within the Spartan-3 family, all devices are pin-compatible by package. When the need for future logic resources outgrows the capacity of the Spartan-3 device in current use, a larger device in the same package can serve as a direct replacement. Larger devices may add extra  $V_{REF}$  and  $V_{CCO}$  lines to support a greater number of I/Os. In the larger device, more pins can convert from user I/Os to  $V_{REF}$  lines. Also, additional  $V_{CCO}$  lines are bonded out to pins that were "not connected" in the smaller device. Thus, it is important to plan for future upgrades at the time of the board's initial design by laying out connections to the extra pins.

The Spartan-3 family is not pin-compatible with any previous Xilinx FPGA family or with other platforms among the Spartan-3 Generation FPGAs.

## **Rules Concerning Banks**

When assigning I/Os to banks, it is important to follow the following  $V_{CCO}$  rules:

- Leave no V<sub>CCO</sub> pins unconnected on the FPGA.

- Set all V<sub>CCO</sub> lines associated with the (interconnected) bank to the same voltage level.

- The V<sub>CCO</sub> levels used by all standards assigned to the I/Os of the (interconnected) bank(s) must agree. The Xilinx development software checks for this. Tables 8, 9, and 10 describe how different standards use the V<sub>CCO</sub> supply.

- Only one of the following standards is allowed on outputs per bank: LVDS, LDT, LVDS\_EXT, or RSDS. This restriction is

for the eight banks in each device, even if the V<sub>CCO</sub> levels are shared across banks, as in the CP132 and TQ144

packages.

- If none of the standards assigned to the I/Os of the (interconnected) bank(s) uses V<sub>CCO</sub>, tie all associated V<sub>CCO</sub> lines to 2.5V.

- In general, apply 2.5V to V<sub>CCO</sub> Bank 4 from power-on to the end of configuration. Apply the same voltage to V<sub>CCO</sub> Bank 5 during parallel configuration or a Readback operation. For information on how to program the FPGA using 3.3V signals and power, see the 3.3V-Tolerant Configuration Interface section.

If any of the standards assigned to the Inputs of the bank use V<sub>REF</sub> then observe the following additional rules:

- Connect all V<sub>REF</sub> pins within the bank to the same voltage level.

- The V<sub>REF</sub> levels used by all standards assigned to the Inputs of the bank must agree. The Xilinx development software checks for this. Tables 8 and 10 describe how different standards use the V<sub>REF</sub> supply.

If none of the standards assigned to the Inputs of a bank use V<sub>REF</sub> for biasing input switching thresholds, all associated V<sub>REF</sub> pins function as User I/Os.

## Exceptions to Banks Supporting I/O Standards

Bank 5 of any Spartan-3 device in a VQ100, CP132, or TQ144 package does not support DCI signal standards. In this case, bank 5 has neither VRN nor VRP pins.

Furthermore, banks 4 and 5 of any Spartan-3 device in a VQ100 package do not support signal standards using  $V_{REF}$  (see Table 8). In this case, the two banks do not have any  $V_{REF}$  pins.

## DFS Clock Output Connections

There are two basic cases that determine how to connect the DFS clock outputs: on-chip and off-chip, which are illustrated in sections [a] and [c], respectively, of Figure 21. This is similar to what has already been described for the DLL component. See DLL Clock Output and Feedback Connections, page 34.

In the on-chip case, it is possible to connect either of the DFS's two output clock signals through general routing resources to the FPGA's internal registers. Either a Global Clock Buffer (BUFG) or a BUFGMUX affords access to the global clock network. The optional feedback loop is formed in this way, routing CLK0 to a global clock net, which in turn drives the CLKFB input.

In the off-chip case, the DFS's two output clock signals, plus CLK0 for an optional feedback loop, can exit the FPGA using output buffers (OBUF) to drive a clock network plus registers on the board. The feedback loop is formed by feeding the CLK0 signal back into the FPGA using an IBUFG, which directly accesses the global clock network, or an IBUF. Then, the global clock net is connected directly to the CLKFB input.

# Phase Shifter (PS)

The DCM provides two approaches to controlling the phase of a DCM clock output signal relative to the CLKIN signal: First, there are nine clock outputs that employ the DLL to achieve a desired phase relationship: CLK0, CLK90, CLK180, CLK270, CLK2X, CLK2X180, CLKDV CLKFX, and CLKFX180. These outputs afford "coarse" phase control.

The second approach uses the PS component described in this section to provide a still finer degree of control. The PS component is only available when the DLL is operating in its low-frequency mode. The PS component phase shifts the DCM output clocks by introducing a "fine phase shift" ( $T_{PS}$ ) between the CLKFB and CLKIN signals inside the DLL component. The user can control this fine phase shift down to a resolution of 1/256 of a CLKIN cycle or one tap delay (DCM\_TAP), whichever is greater. When in use, the PS component shifts the phase of all nine DCM clock output signals together. If the PS component is used together with a DCM clock output such as the CLK90, CLK180, CLK270, CLK2X180 and CLKFX180, then the fine phase shift of the former gets added to the coarse phase shift of the latter.

## **PS Component Enabling and Mode Selection**

The CLKOUT\_PHASE\_SHIFT attribute enables the PS component for use in addition to selecting between two operating modes. As described in Table 20, this attribute has three possible values: NONE, FIXED and VARIABLE. When CLKOUT\_PHASE\_SHIFT is set to NONE, the PS component is disabled and its inputs, PSEN, PSCLK, and PSINCDEC, must be tied to GND. The set of waveforms in section [a] of Figure 22 shows the disabled case, where the DLL maintains a zero-phase alignment of signals CLKFB and CLKIN upon which the PS component has no effect. The PS component is enabled by setting the attribute to either the FIXED or VARIABLE values, which select the Fixed Phase mode and the Variable Phase mode, respectively. These two modes are described in the sections that follow

## **Determining the Fine Phase Shift**

The user controls the phase shift of CLKFB relative to CLKIN by setting and/or adjusting the value of the PHASE\_SHIFT attribute. This value must be an integer ranging from –255 to +255. The PS component uses this value to calculate the desired fine phase shift ( $T_{PS}$ ) as a fraction of the CLKIN period ( $T_{CLKIN}$ ). Given values for PHASE-SHIFT and  $T_{CLKIN}$ , it is possible to calculate  $T_{PS}$  as follows:

$$T_{PS} = T_{CLKIN}(PHASE_SHIFT/256)$$

Equation 4

Both the Fixed Phase and Variable Phase operating modes employ this calculation. If the PHASE\_SHIFT value is zero, then CLKFB and CLKIN will be in phase, the same as when the PS component is disabled. When the PHASE\_SHIFT value is positive, the CLKFB signal will be shifted later in time with respect to CLKIN. If the attribute value is negative, the CLKFB signal will be shifted earlier in time with respect to CLKIN.

## The Fixed Phase Mode

This mode fixes the desired fine phase shift to a fraction of the  $T_{CLKIN}$ , as determined by Equation 4 and its user-selected PHASE\_SHIFT value P. The set of waveforms insection [b] of Figure 22 illustrates the relationship between CLKFB and CLKIN in the Fixed Phase mode. In the Fixed Phase mode, the PSEN, PSCLK and PSINCDEC inputs are not used and must be tied to GND. Fixed phase shift requires ISE software version 10.1.03 or later.

| Symbol                          | Description                                                                      | Test Cond                                    | litions                     | Min    | Тур                                                   | Max   | Units |

|---------------------------------|----------------------------------------------------------------------------------|----------------------------------------------|-----------------------------|--------|-------------------------------------------------------|-------|-------|

| I <sub>L</sub> (2)(4)           | Leakage current at User I/O,                                                     | Driver is Hi-Z, V <sub>IN</sub> =            | $V_{CCO} \ge 3.0V$          | —      | -                                                     | ±25   | μA    |

|                                 | Dual-Purpose, and Dedicated pins                                                 | 0V or V <sub>CCO</sub> max,<br>sample-tested | V <sub>CCO</sub> < 3.0V     | -      | -                                                     | ±10   | μA    |

| I <sub>RPU</sub> <sup>(3)</sup> | Current through pull-up resistor at User I/O,                                    | V <sub>IN</sub> = 0V, V <sub>CC</sub>        | <sub>CO</sub> = 3.3V        | -0.84  | -                                                     | -2.35 | mA    |

|                                 | Dual-Purpose, and Dedicated pins                                                 | V <sub>IN</sub> = 0V, V <sub>CC</sub>        | <sub>CO</sub> = 3.0V        | -0.69  | -                                                     | -1.99 | mA    |

|                                 |                                                                                  | $V_{IN} = 0V, V_{CC}$                        | <sub>CO</sub> = 2.5V        | -0.47  | -                                                     | -1.41 | mA    |

|                                 |                                                                                  | $V_{IN} = 0V, V_{CC}$                        | <sub>CO</sub> = 1.8V        | -0.21  | -                                                     | -0.69 | mA    |

|                                 |                                                                                  | $V_{IN} = 0V, V_{CC}$                        | <sub>CO</sub> = 1.5V        | -0.13  | -                                                     | -0.43 | mA    |

|                                 |                                                                                  | V <sub>IN</sub> = 0V, V <sub>CC</sub>        | <sub>:O</sub> = 1.2V        | -0.06  | -                                                     | -0.22 | mA    |

| R <sub>PU</sub> <sup>(3)</sup>  | Equivalent resistance of pull-up resistor at                                     | $V_{CCO} = 3.0V$                             | to 3.465V                   | 1.27   | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ | 4.11  | kΩ    |

|                                 | User I/O, Dual-Purpose, and Dedicated pins, derived from I <sub>BPU</sub>        | V <sub>CCO</sub> = 2.3V                      | ' to 2.7V                   | 1.15   |                                                       | 3.25  | kΩ    |

|                                 |                                                                                  | V <sub>CCO</sub> = 1.7V                      | ′ to 1.9V                   | 2.45 - | 9.10                                                  | kΩ    |       |

|                                 |                                                                                  | V <sub>CCO</sub> = 1.4V                      | <sub>O</sub> = 1.4V to 1.6V |        | -                                                     | 12.10 | kΩ    |

|                                 |                                                                                  | V <sub>CCO</sub> = 1.14                      | to 1.26V                    | 5.15   | -                                                     | 21.00 | kΩ    |

| I <sub>RPD</sub> <sup>(3)</sup> | Current through pull-down resistor at User I/O, Dual-Purpose, and Dedicated pins | $V_{IN} = V_0$                               | 000                         | 0.37   | -                                                     | 1.67  | mA    |

| R <sub>PD</sub> <sup>(3)</sup>  | Equivalent resistance of pull-down resistor                                      | $V_{IN} = V_{CCO} = 3.0$                     | V to 3.465V                 | 1.75   | -                                                     | 9.35  | kΩ    |

|                                 | at User I/O, Dual-Purpose, and Dedicated pins, driven from I <sub>BPD</sub>      | $V_{IN} = V_{CCO} = 2$                       | .3V to 2.7V                 | 1.35   | -                                                     | 7.30  | kΩ    |

|                                 |                                                                                  | $V_{IN} = V_{CCO} = 1$                       | .7V to 1.9V                 | 1.00   | -                                                     | 5.15  | kΩ    |

|                                 |                                                                                  | $V_{IN} = V_{CCO} = 1$                       | .4V to 1.6V                 | 0.85   | -                                                     | 4.35  | kΩ    |

|                                 |                                                                                  | $V_{IN} = V_{CCO} = 1.$                      | 14 to 1.26V                 | 0.68   | -                                                     | 3.465 | kΩ    |

| R <sub>DCI</sub>                | Value of external reference resistor to supp                                     | ort DCI I/O standards                        |                             | 20     | -                                                     | 100   | Ω     |

| I <sub>REF</sub>                | V <sub>REF</sub> current per pin                                                 | $V_{CCO} \ge 3$                              | 3.0V                        | —      | -                                                     | ±25   | μA    |

|                                 |                                                                                  | V <sub>CCO</sub> < 3                         | 3.0V                        | —      | -                                                     | ±10   | μA    |

| C <sub>IN</sub>                 | Input capacitance                                                                |                                              |                             | 3      | -                                                     | 10    | pF    |

#### Table 33: General DC Characteristics of User I/O, Dual-Purpose, and Dedicated Pins

Notes:

1. The numbers in this table are based on the conditions set forth in Table 32.

2. The I<sub>L</sub> specification applies to every I/O pin throughout power-on as long as the voltage on that pin stays between the absolute V<sub>IN</sub> minimum and maximum values (Table 28). For hot-swap applications, at the time of card connection, be sure to keep all I/O voltages within this range before applying V<sub>CCO</sub> power. Consider applying V<sub>CCO</sub> power before connecting the signal lines, to avoid turning on the ESD protection diodes, shown in Module 2: Figure 7, page 11. When the FPGA is completely unpowered, the I/O pins are high impedance, but there is a path through the upper and lower ESD protection diodes.

3. This parameter is based on characterization. The pull-up resistance  $R_{PU} = V_{CCO} / I_{RPU}$ . The pull-down resistance  $R_{PD} = V_{IN} / I_{RPD}$ . Spartan-3 family values for both resistances are stronger than they have been for previous FPGA families.

For single-ended signals that are placed on a differential-capable I/O, V<sub>IN</sub> of –0.2V to –0.3V is supported but can cause increased leakage between the two pins. See the *Parasitic Leakage* section in <u>UG331</u>, *Spartan-3 Generation FPGA User Guide*.

## I/O Timing

#### Table 40: Pin-to-Pin Clock-to-Output Times for the IOB Output Path

|                       |                                                                                                                 |                                                       |          | Speed Grade        |                    |       |

|-----------------------|-----------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|----------|--------------------|--------------------|-------|

| Symbol                | Description                                                                                                     | Conditions                                            | Device   | -5                 | -4                 | Units |

|                       |                                                                                                                 |                                                       |          | Max <sup>(2)</sup> | Max <sup>(2)</sup> |       |

| Clock-to-Outpu        | t Times                                                                                                         |                                                       |          |                    |                    |       |

| T <sub>ICKOFDCM</sub> | When reading from the Output<br>Flip-Flop (OFF), the time from the<br>active transition on the Global Clock pin | LVCMOS25 <sup>(3)</sup> , 12 mA                       | XC3S50   | 2.04               | 2.35               | ns    |

|                       |                                                                                                                 | output drive, Fast slew rate, with DCM <sup>(4)</sup> | XC3S200  | 1.45               | 1.75               | ns    |

|                       | to data appearing at the Output pin.<br>The DCM is in use.                                                      |                                                       | XC3S400  | 1.45               | 1.75               | ns    |

|                       |                                                                                                                 |                                                       | XC3S1000 | 2.07               | 2.39               | ns    |

|                       |                                                                                                                 |                                                       | XC3S1500 | 2.05               | 2.36               | ns    |

|                       |                                                                                                                 |                                                       | XC3S2000 | 2.03               | 2.34               | ns    |

|                       |                                                                                                                 |                                                       | XC3S4000 | 1.94               | 2.24               | ns    |

|                       |                                                                                                                 |                                                       | XC3S5000 | 2.00               | 2.30               | ns    |

| TICKOF                | When reading from OFF, the time from                                                                            | LVCMOS25 <sup>(3)</sup> , 12 mA                       | XC3S50   | 3.70               | 4.24               | ns    |

|                       | the active transition on the Global Clock<br>pin to data appearing at the Output pin.                           | output drive, Fast slew rate, without DCM             | XC3S200  | 3.89               | 4.46               | ns    |

|                       | The DCM is not in use.                                                                                          |                                                       | XC3S400  | 3.91               | 4.48               | ns    |

|                       |                                                                                                                 |                                                       | XC3S1000 | 4.00               | 4.59               | ns    |

|                       |                                                                                                                 |                                                       | XC3S1500 | 4.07               | 4.66               | ns    |

|                       |                                                                                                                 |                                                       | XC3S2000 | 4.19               | 4.80               | ns    |

|                       |                                                                                                                 |                                                       | XC3S4000 | 4.44               | 5.09               | ns    |

|                       |                                                                                                                 |                                                       | XC3S5000 | 4.38               | 5.02               | ns    |

#### Notes:

1. The numbers in this table are tested using the methodology presented in Table 48 and are based on the operating conditions set forth in Table 32 and Table 35.

2. For minimums, use the values reported by the Xilinx timing analyzer.

3. This clock-to-output time requires adjustment whenever a signal standard other than LVCMOS25 is assigned to the Global Clock Input or a standard other than LVCMOS25 with 12 mA drive and Fast slew rate is assigned to the data Output. If the former is true, *add* the appropriate Input adjustment from Table 44. If the latter is true, *add* the appropriate Output adjustment from Table 47.

4. DCM output jitter is included in all measurements.

### Table 54: Synchronous 18 x 18 Multiplier Timing

|                      |                                                                                                                                 |           |      |      | Units |      |    |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------|-----------|------|------|-------|------|----|

| Symbol               | Description                                                                                                                     | P Outputs | -5   |      |       |      | -4 |

|                      |                                                                                                                                 |           | Min  | Max  | Min   | Max  |    |

| Clock-to-Outpu       | ut Times                                                                                                                        |           |      |      |       |      |    |

| T <sub>MULTCK</sub>  | When reading from the                                                                                                           | P[0]      | -    | 1.00 | -     | 1.15 | ns |

|                      | Multiplier, the time from the active transition at the C clock                                                                  | P[15]     | -    | 1.15 | -     | 1.32 | ns |

|                      | input to data appearing at the P                                                                                                | P[17]     | -    | 1.30 | -     | 1.50 | ns |

|                      | outputs                                                                                                                         | P[19]     | -    | 1.45 | -     | 1.67 | ns |

|                      |                                                                                                                                 | P[23]     | -    | 1.76 | -     | 2.02 | ns |

|                      |                                                                                                                                 | P[31]     | -    | 2.37 | -     | 2.72 | ns |

|                      |                                                                                                                                 | P[35]     | -    | 2.67 | -     | 3.07 | ns |

| Setup Times          |                                                                                                                                 |           |      |      |       |      |    |

| T <sub>MULIDCK</sub> | Time from the setup of data at<br>the A and B inputs to the active<br>transition at the C input of the<br>Multiplier            | -         | 1.84 | -    | 2.11  | -    | ns |

| Hold Times           |                                                                                                                                 |           |      |      |       |      |    |

| T <sub>MULCKID</sub> | Time from the active transition<br>at the Multiplier's C input to the<br>point where data is last held at<br>the A and B inputs | -         | 0    | -    | 0     | -    | ns |

#### Notes:

1. The numbers in this table are based on the operating conditions set forth in Table 32.

#### Table 55: Asynchronous 18 x 18 Multiplier Timing

|                 |                                                                               |           | Speed |      |       |

|-----------------|-------------------------------------------------------------------------------|-----------|-------|------|-------|

| Symbol          | Description                                                                   | P Outputs | -5    | -4   | Units |

|                 |                                                                               |           | Max   | Max  |       |

| Propagation Tim | es                                                                            |           |       |      |       |

|                 | The time it takes for data to travel from the A and B inputs to the P outputs | P[0]      | 1.55  | 1.78 | ns    |

|                 |                                                                               | P[15]     | 3.15  | 3.62 | ns    |

|                 |                                                                               | P[17]     | 3.36  | 3.86 | ns    |

|                 |                                                                               | P[19]     | 3.49  | 4.01 | ns    |

|                 |                                                                               | P[23]     | 3.73  | 4.29 | ns    |

|                 |                                                                               | P[31]     | 4.23  | 4.86 | ns    |

|                 |                                                                               | P[35]     | 4.47  | 5.14 | ns    |

#### Notes:

1. The numbers in this table are based on the operating conditions set forth in Table 32.

# Notice of Disclaimer

THE XILINX HARDWARE FPGA AND CPLD DEVICES REFERRED TO HEREIN ("PRODUCTS") ARE SUBJECT TO THE TERMS AND CONDITIONS OF THE XILINX LIMITED WARRANTY WHICH CAN BE VIEWED AT <a href="http://www.xilinx.com/warranty.htm">http://www.xilinx.com/warranty.htm</a>. THIS LIMITED WARRANTY DOES NOT EXTEND TO ANY USE OF PRODUCTS IN AN APPLICATION OR ENVIRONMENT THAT IS NOT WITHIN THE SPECIFICATIONS STATED IN THE XILINX DATA SHEET. ALL SPECIFICATIONS ARE SUBJECT TO CHANGE WITHOUT NOTICE. PRODUCTS ARE NOT DESIGNED OR INTENDED TO BE FAIL-SAFE OR FOR USE IN ANY APPLICATION REQUIRING FAIL-SAFE PERFORMANCE, SUCH AS LIFE-SUPPORT OR SAFETY DEVICES OR SYSTEMS, OR ANY OTHER APPLICATION THAT INVOKES THE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). USE OF PRODUCTS IN CRITICAL APPLICATIONS IS AT THE SOLE RISK OF CUSTOMER, SUBJECT TO APPLICABLE LAWS AND REGULATIONS.

#### **CRITICAL APPLICATIONS DISCLAIMER**

XILINX PRODUCTS (INCLUDING HARDWARE, SOFTWARE AND/OR IP CORES) ARE NOT DESIGNED OR INTENDED TO BE FAIL-SAFE, OR FOR USE IN ANY APPLICATION REQUIRING FAIL-SAFE PERFORMANCE, SUCH AS IN LIFE-SUPPORT OR SAFETY DEVICES OR SYSTEMS, CLASS III MEDICAL DEVICES, NUCLEAR FACILITIES, APPLICATIONS RELATED TO THE DEPLOYMENT OF AIRBAGS, OR ANY OTHER APPLICATIONS THAT COULD LEAD TO DEATH, PERSONAL INJURY OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE (INDIVIDUALLY AND COLLECTIVELY, "CRITICAL APPLICATIONS"). FURTHERMORE, XILINX PRODUCTS ARE NOT DESIGNED OR INTENDED FOR USE IN ANY APPLICATIONS THAT AFFECT CONTROL OF A VEHICLE OR AIRCRAFT, UNLESS THERE IS A FAIL-SAFE OR REDUNDANCY FEATURE (WHICH DOES NOT INCLUDE USE OF SOFTWARE IN THE XILINX DEVICE TO IMPLEMENT THE REDUNDANCY) AND A WARNING SIGNAL UPON FAILURE TO THE OPERATOR. CUSTOMER AGREES, PRIOR TO USING OR DISTRIBUTING ANY SYSTEMS THAT INCORPORATE XILINX PRODUCTS, TO THOROUGHLY TEST THE SAME FOR SAFETY PURPOSES. TO THE MAXIMUM EXTENT PERMITTED BY APPLICABLE LAW, CUSTOMER ASSUMES THE SOLE RISK AND LIABILITY OF ANY USE OF XILINX PRODUCTS IN CRITICAL APPLICATIONS.

#### AUTOMOTIVE APPLICATIONS DISCLAIMER

XILINX PRODUCTS ARE NOT DESIGNED OR INTENDED TO BE FAIL-SAFE, OR FOR USE IN ANY APPLICATION REQUIRING FAIL-SAFE PERFORMANCE, SUCH AS APPLICATIONS RELATED TO: (I) THE DEPLOYMENT OF AIRBAGS, (II) CONTROL OF A VEHICLE, UNLESS THERE IS A FAIL-SAFE OR REDUNDANCY FEATURE (WHICH DOES NOT INCLUDE USE OF SOFTWARE IN THE XILINX DEVICE TO IMPLEMENT THE REDUNDANCY) AND A WARNING SIGNAL UPON FAILURE TO THE OPERATOR, OR (III) USES THAT COULD LEAD TO DEATH OR PERSONAL INJURY. CUSTOMER ASSUMES THE SOLE RISK AND LIABILITY OF ANY USE OF XILINX PRODUCTS IN SUCH APPLICATIONS.

### **Mechanical Drawings**

Detailed mechanical drawings for each package type are available from the Xilinx website at the specified location in Table 83.

Material Declaration Data Sheets (MDDS) are also available on the Xilinx website for each package.

Table 83: Xilinx Package Mechanical Drawings

| Package                           | Web Link (URL)                                                       |

|-----------------------------------|----------------------------------------------------------------------|

| VQ100 and VQG100                  | http://www.xilinx.com/support/documentation/package_specs/vq100.pdf  |

| CP132 and CPG132 <sup>(1)</sup>   | http://www.xilinx.com/support/documentation/package_specs/cp132.pdf  |

| TQ144 and TQG144                  | http://www.xilinx.com/support/documentation/package_specs/tq144.pdf  |

| PQ208 and PQG208                  | http://www.xilinx.com/support/documentation/package_specs/pq208.pdf  |

| FT256 and FTG256                  | http://www.xilinx.com/support/documentation/package_specs/ft256.pdf  |

| FG320 and FGG320                  | http://www.xilinx.com/support/documentation/package_specs/fg320.pdf  |

| FG456 and FGG456                  | http://www.xilinx.com/support/documentation/package_specs/fg456.pdf  |

| FG676 and FGG676                  | http://www.xilinx.com/support/documentation/package_specs/fg676.pdf  |

| FG900 and FGG900                  | http://www.xilinx.com/support/documentation/package_specs/fg900.pdf  |

| FG1156 and FGG1156 <sup>(1)</sup> | http://www.xilinx.com/support/documentation/package_specs/fg1156.pdf |

#### Notes:

1. The CP132, CPG132, FG1156, and FGG1156 packages are discontinued. See http://www.xilinx.com/support/documentation/spartan-3\_customer\_notices.htm.

### Power, Ground, and I/O by Package

Each package has three separate voltage supply inputs—VCCINT, VCCAUX, and VCCO—and a common ground return, GND. The numbers of pins dedicated to these functions varies by package, as shown in Table 84.

| Package               | VCCINT | VCCAUX | VCCO | GND |

|-----------------------|--------|--------|------|-----|

| VQ100                 | 4      | 4      | 8    | 10  |

| CP132 <sup>(1)</sup>  | 4      | 4      | 12   | 12  |

| TQ144                 | 4      | 4      | 12   | 16  |

| PQ208                 | 4      | 8      | 12   | 28  |

| FT256                 | 8      | 8      | 24   | 32  |

| FG320                 | 12     | 8      | 28   | 40  |

| FG456                 | 12     | 8      | 40   | 52  |

| FG676                 | 20     | 16     | 64   | 76  |

| FG900                 | 32     | 24     | 80   | 120 |

| FG1156 <sup>(1)</sup> | 40     | 32     | 104  | 184 |

#### Notes:

1. The CP132, CPG132, FG1156, and FGG1156 packages are discontinued. See http://www.xilinx.com/support/documentation/spartan-3\_customer\_notices.htm.

A majority of package pins are user-defined I/O pins. However, the numbers and characteristics of these I/O depends on the device type and the package in which it is available, as shown in Table 85. The table shows the maximum number of single-ended I/O pins available, assuming that all I/O-, DUAL-, DCI-, VREF-, and GCLK-type pins are used as general-purpose I/O. Likewise, the table shows the maximum number of differential pin-pairs available on the package. Finally, the table shows how the total maximum user I/Os are distributed by pin type, including the number of unconnected—i.e., N.C.—pins on the device.

### Table 87: VQ100 Package Pinout (Cont'd)

| Bank   | XC3S50<br>XC3S200<br>Pin Name | VQ100<br>Pin<br>Number | Туре |

|--------|-------------------------------|------------------------|------|

| VCCAUX | TDO                           | P76                    | JTAG |

| VCCAUX | TMS                           | P78                    | JTAG |

# User I/Os by Bank

Table 88 indicates how the available user-I/O pins are distributed between the eight I/O banks on the VQ100 package.

| Package Edge | I/O Bank | Maximum I/O | All Possible I/O Pins by Type |      |       |      |      |  |

|--------------|----------|-------------|-------------------------------|------|-------|------|------|--|

| Package Luge |          | Maximum 1/0 | I/O                           | DUAL | DCI   | VREF | GCLK |  |

| Тор          | 0        | 6           | 1                             | 0    | 2     | 1    | 2    |  |

| юр           | 1        | 7           | 2                             | 0    | L DCI | 1    | 2    |  |

| Right        | 2        | 8           | 5                             | 0    | 2     | 1    | 0    |  |

| night        | 3        | 8           | 5                             | 0    | 2     | 1    | 0    |  |

| Bottom       | 4        | 10          | 0                             | 6    | 2     | 0    | 2    |  |

| Bollom       | 5        | 8           | 0                             | 6    | 0     | 0    | 2    |  |

| Left         | 6        | 8           | 4                             | 0    | 2     | 2    | 0    |  |

| Leit         | 7        | 8           | 5                             | 0    | 2     | 1    | 0    |  |

### Table 88: User I/Os Per Bank in VQ100 Package

### Table 93: PQ208 Package Pinout (Cont'd)

| Bank | XC3S50<br>Pin Name | XC3S200, XC3S400<br>Pin Names | PQ208 Pin<br>Number | Туре |

|------|--------------------|-------------------------------|---------------------|------|

| 1    | IO_L10N_1/VREF_1   | IO_L10N_1/VREF_1              | P166                | VREF |

| 1    | IO_L10P_1          | IO_L10P_1                     | P165                | I/O  |

| 1    | IO_L27N_1          | IO_L27N_1                     | P169                | I/O  |

| 1    | IO_L27P_1          | IO_L27P_1                     | P168                | I/O  |

| 1    | IO_L28N_1          | IO_L28N_1                     | P172                | I/O  |

| 1    | IO_L28P_1          | IO_L28P_1                     | P171                | I/O  |

| 1    | IO_L31N_1/VREF_1   | IO_L31N_1/VREF_1              | P178                | VREF |

| 1    | IO_L31P_1          | IO_L31P_1                     | P176                | I/O  |

| 1    | IO_L32N_1/GCLK5    | IO_L32N_1/GCLK5               | P181                | GCLK |

| 1    | IO_L32P_1/GCLK4    | IO_L32P_1/GCLK4               | P180                | GCLK |

| 1    | VCCO_1             | VCCO_1                        | P164                | VCCO |

| 1    | VCCO_1             | VCCO_1                        | P177                | VCCO |

| 2    | N.C. (�)           | IO/VREF_2                     | P154                | VREF |

| 2    | IO_L01N_2/VRP_2    | IO_L01N_2/VRP_2               | P156                | DCI  |

| 2    | IO_L01P_2/VRN_2    | IO_L01P_2/VRN_2               | P155                | DCI  |

| 2    | IO_L19N_2          | IO_L19N_2                     | P152                | I/O  |

| 2    | IO_L19P_2          | IO_L19P_2                     | P150                | I/O  |

| 2    | IO_L20N_2          | IO_L20N_2                     | P149                | I/O  |

| 2    | IO_L20P_2          | IO_L20P_2                     | P148                | I/O  |

| 2    | IO_L21N_2          | IO_L21N_2                     | P147                | I/O  |

| 2    | IO_L21P_2          | IO_L21P_2                     | P146                | I/O  |

| 2    | IO_L22N_2          | IO_L22N_2                     | P144                | I/O  |

| 2    | IO_L22P_2          | IO_L22P_2                     | P143                | I/O  |

| 2    | IO_L23N_2/VREF_2   | IO_L23N_2/VREF_2              | P141                | VREF |

| 2    | IO_L23P_2          | IO_L23P_2                     | P140                | I/O  |

| 2    | IO_L24N_2          | IO_L24N_2                     | P139                | I/O  |

| 2    | IO_L24P_2          | IO_L24P_2                     | P138                | I/O  |

| 2    | N.C. (�)           | IO_L39N_2                     | P137                | I/O  |

| 2    | N.C. (�)           | IO_L39P_2                     | P135                | I/O  |

| 2    | IO_L40N_2          | IO_L40N_2                     | P133                | I/O  |

| 2    | IO_L40P_2/VREF_2   | IO_L40P_2/VREF_2              | P132                | VREF |

| 2    | VCCO_2             | VCCO_2                        | P136                | VCCO |

| 2    | VCCO_2             | VCCO_2                        | P153                | VCCO |

| 3    | IO_L01N_3/VRP_3    | IO_L01N_3/VRP_3               | P107                | DCI  |

| 3    | IO_L01P_3/VRN_3    | IO_L01P_3/VRN_3               | P106                | DCI  |

| 3    | N.C. (�)           | IO_L17N_3                     | P109                | I/O  |

| 3    | N.C. (�)           | IO_L17P_3/VREF_3              | P108                | VREF |

| 3    | IO_L19N_3          | IO_L19N_3                     | P113                | I/O  |

| 3    | IO_L19P_3          | IO_L19P_3                     | P111                | I/O  |

| 3    | IO_L20N_3          | IO_L20N_3                     | P115                | I/O  |

# FT256: 256-lead Fine-pitch Thin Ball Grid Array

The 256-lead fine-pitch thin ball grid array package, FT256, supports three different Spartan-3 devices, including the XC3S200, the XC3S400, and the XC3S1000. The footprints for all three devices are identical, as shown in Table 96 and Figure 49.

All the package pins appear in Table 96 and are sorted by bank number, then by pin name. Pairs of pins that form a differential I/O pair appear together in the table. The table also shows the pin number for each pin and the pin type, as defined earlier.

An electronic version of this package pinout table and footprint diagram is available for download from the Xilinx website at <a href="http://www.xilinx.com/support/documentation/data\_sheets/s3\_pin.zip">http://www.xilinx.com/support/documentation/data\_sheets/s3\_pin.zip</a>.

## **Pinout Table**

#### Table 96: FT256 Package Pinout

| Bank | XC3S200, XC3S400, XC3S1000<br>Pin Name | FT256 Pin<br>Number | Туре |

|------|----------------------------------------|---------------------|------|

| 0    | ю                                      | A5                  | I/O  |

| 0    | IO                                     | A7                  | I/O  |

| 0    | IO/VREF_0                              | A3                  | VREF |

| 0    | IO/VREF_0                              | D5                  | VREF |

| 0    | IO_L01N_0/VRP_0                        | B4                  | DCI  |

| 0    | IO_L01P_0/VRN_0                        | A4                  | DCI  |

| 0    | IO_L25N_0                              | C5                  | I/O  |

| 0    | IO_L25P_0                              | B5                  | I/O  |

| 0    | IO_L27N_0                              | E6                  | I/O  |

| 0    | IO_L27P_0                              | D6                  | I/O  |

| 0    | IO_L28N_0                              | C6                  | I/O  |

| 0    | IO_L28P_0                              | B6                  | I/O  |

| 0    | IO_L29N_0                              | E7                  | I/O  |

| 0    | IO_L29P_0                              | D7                  | I/O  |

| 0    | IO_L30N_0                              | C7                  | I/O  |

| 0    | IO_L30P_0                              | B7                  | I/O  |

| 0    | IO_L31N_0                              | D8                  | I/O  |

| 0    | IO_L31P_0/VREF_0                       | C8                  | VREF |

| 0    | IO_L32N_0/GCLK7                        | B8                  | GCLK |

| 0    | IO_L32P_0/GCLK6                        | A8                  | GCLK |

| 0    | VCCO_0                                 | E8                  | VCCO |

| 0    | VCCO_0                                 | F7                  | VCCO |

| 0    | VCCO_0                                 | F8                  | VCCO |

| 1    | 10                                     | A9                  | I/O  |

| 1    | 10                                     | A12                 | I/O  |

| 1    | Ю                                      | C10                 | I/O  |

| 1    | IO/VREF_1                              | D12                 | VREF |

| 1    | IO_L01N_1/VRP_1                        | A14                 | DCI  |

| 1    | IO_L01P_1/VRN_1                        | B14                 | DCI  |

www.xilinx.com

# FT256 Footprint

|         |    |                         | 2             |                         | 4                      |                         | nk 0<br>6               | 7                   | 0                      | 9                              | 10                      |                            | nk 1                    | 10                      | 14                     | 15                      | 16                      |        |

|---------|----|-------------------------|---------------|-------------------------|------------------------|-------------------------|-------------------------|---------------------|------------------------|--------------------------------|-------------------------|----------------------------|-------------------------|-------------------------|------------------------|-------------------------|-------------------------|--------|

|         | A  | 1<br>GND                | TDI           | 3<br>IO<br>VREF_0       | 4<br>I/O<br>L01P_0     | 5<br>I/O                | VCCAUX                  | I/O                 | 8<br>I/O<br>L32P_0     | I/O                            | 10<br>I/O<br>L31N_1     | 11<br>VCCAUX               | <b>12</b><br>I/O        | 13<br>I/O<br>L10N_1     | 14<br>I/O<br>L01N_1    | 15<br>TDO               | 16<br>GND               |        |

|         | B  | I/O<br>L01P_7           | GND           | PROG_B                  | VRN_0<br>I/O<br>L01N_0 | I/O<br>L25P 0           | I/O<br>L28P_0           | I/O<br>L30P_0       | GCLK6<br>I/O<br>L32N_0 | GND                            | VREF_1<br>I/O<br>L31P 1 | I/O<br>L29N 1              | I/O<br>L27N_1           | VREF_1<br>I/O<br>L10P 1 | VRP_1<br>I/O<br>L01P_1 | GND                     | l/O<br>L01N_2           |        |

|         | С  | VRN_7<br>I/O<br>L01N_7  | I/O<br>L16N_7 | I/O<br>L16P_7           | VRP_0<br>HSWAP_        | I/O<br>L25N_0           | I/O                     | I/O<br>L30N_0       | I/O<br>L31P_0          | I/O<br>L32N_1                  | I/O                     | I/O<br>L29P 1              | I/O<br>L27P_1           | TMS                     | VRN_1                  | I/O<br>L16N_2           | VRP_2<br>I/O<br>L01P_2  |        |

|         | D  | VRP_7                   | I/O           | VREF_7                  | VCCINT                 | 10                      | I/O                     | I/O                 | I/O                    | GCLK5<br>I/O<br>L32P 1         | I/O                     | I/O                        | IO<br>VREF_1            | VCCINT                  | I/O                    | I/O                     | VRN_2<br>I/O<br>L17P_2  |        |

| Bank 7  | E  | L17N_7<br>I/O           | L17P_7<br>I/O | L19P_7<br>I/O<br>L19N_7 | I/O                    | VCCINT                  | L27P_0                  | L29P_0<br>I/O       |                        |                                | L30N_1<br>I/O           | L28N_1                     | VCCINT                  | I/O                     | L16P_2<br>I/O          | L17N_2                  | VREF_2                  | nk 2   |

| Bai     |    | L20N_7                  | L20P_7        | VREF_7                  | L21P_7                 | 1/0                     | L27N_0                  | L29N_0              |                        |                                | L30P_1                  | L28P_1                     | 1/0                     | L19N_2                  | L19P_2                 | L20N_2                  | L20P_2                  | Bank   |

|         | F  | VCCAUX                  | L22N_7        | L22P_7                  | L21N_7                 | L23P_7                  | GND                     | VCCO_0              | VCCO_0                 |                                |                         | GND                        | L21N_2                  | L21P_2                  | L22N_2                 | L22P_2                  | VCCAUX                  |        |

|         | G  | L40P_7                  | I/O           | L24N_7                  | L24P_7                 | L23N_7                  | VCCO_7                  | GND                 | GND                    | GND                            | GND                     | VCCO_2                     | L23N_2<br>VREF_2        | L23P_2                  | L24N_2                 | L24P_2                  | I/O<br>I/O              |        |

|         | н  | L40N_7<br>VREF_7        | GND           | I/O<br>L39N_7           | I/O<br>L39P_7          | VCCO_7                  | VCCO_7                  | GND                 | GND                    | GND                            | GND                     | VCCO_2                     | VCCO_2                  | I/O<br>L39N_2           | I/O<br>L39P_2          | I/O<br>L40N_2           | L40P_2<br>VREF_2        | _      |

|         | J  | I/O<br>L40P_6<br>VREF_6 | I/O<br>L40N_6 | I/O<br>L39P_6           | I/O<br>L39N_6          | VCCO_6                  | VCCO_6                  | GND                 | GND                    | GND                            | GND                     | VCCO_3                     | VCCO_3                  | I/O<br>L39P_3           | I/O<br>L39N_3          | GND                     | I/O<br>L40N_3<br>VREF_3 |        |

|         | κ  | I/O                     | I/O<br>L24P_6 | I/O<br>L24N_6<br>VREF_6 | I/O<br>L23P_6          | I/O<br>L23N_6           | VCCO_6                  | GND                 | GND                    | GND                            | GND                     | VCCO_3                     | I/O<br>L23N_3           | I/O<br>L24P_3           | I/O<br>L24N_3          | I/O                     | I/O<br>L40P_3           |        |

|         | L  | VCCAUX                  | I/O<br>L22P_6 | I/O<br>L22N_6           | I/O<br>L21P_6          | I/O<br>L21N_6           | GND                     | VCCO_5              | VCCO_5                 | VCCO_4                         | VCCO_4                  | GND                        | I/O<br>L23P_3<br>VREF_3 | I/O<br>L21N_3           | I/O<br>L22P_3          | I/O<br>L22N_3           | VCCAUX                  |        |

| Bank 6  | М  | I/O<br>L20P_6           | I/O<br>L20N_6 | I/O<br>L19P_6           | I/O<br>L19N_6          | VCCINT                  | I/O<br>L28P_5<br>D7     | I/O<br>L30P_5       | VCCO_5                 | VCCO_4                         | I/O<br>L29N_4           | I/O<br>L27N_4<br>DIN<br>D0 | VCCINT                  | I/O<br>L21P_3           | I/O<br>L19N_3          | I/O<br>L20P_3           | I/O<br>L20N_3           | Bank 3 |

|         | N  | I/O<br>L17P_6<br>VREF 6 | I/O<br>L17N_6 | I/O<br>L16P_6           | VCCINT                 | I/O                     | I/O<br>L28N_5<br>D6     | I/O<br>L30N_5       | I/O<br>L32P_5<br>GCLK2 | I/O<br>L31N_4<br>INIT B        | I/O<br>L29P_4           | I/O<br>L27P_4<br>D1        | IO<br>VREF_4            | VCCINT                  | I/O<br>L19P_3          | I/O<br>L17P_3<br>VREF 3 | I/O<br>L17N_3           | _      |

|         | Ρ  | I/O<br>L01P_6<br>VRN_6  | I/O<br>L16N_6 | МО                      | M2                     | l/O<br>L27P_5           | I/O<br>L29P_5<br>VREF 5 | I/O                 | I/O<br>L32N_5<br>GCLK3 | DOUT                           | I/O<br>L30N_4<br>D2     | I/O<br>L28N_4              | I/O<br>L25N_4           | IO<br>VREF_4            | I/O<br>L16P_3          | I/O<br>L16N_3           | I/O<br>L01N_3<br>VRP 3  |        |

|         | R  | I/O                     | GND           | I/O<br>L01P_5<br>CS_B   | I/O<br>L10P_5<br>VRN_5 | I/O<br>L27N_5<br>VREF_5 | I/O<br>L29N_5           | I/O<br>L31P_5<br>D5 | GND                    | BUSY<br>I/O<br>L32N_4<br>GCLK1 | I/O<br>L30P_4<br>D3     | I/O<br>L28P_4              | I/O<br>L25P_4           | I/O<br>L01N_4<br>VRP_4  | DONE                   | GND                     | I/O<br>L01P_3<br>VRN_3  |        |

|         | т  | GND                     | M1            | I/O<br>L01N_5<br>RDWR_B | I/O<br>L10N_5          | I/O                     | VCCAUX                  | I/O                 | IO<br>VREF_5           | I/O<br>L32P_4<br>GCLK0         | IO<br>VREF_4            | VCCAUX                     | I/O                     | I/O<br>L01P_4<br>VRN_4  | I/O                    | CCLK                    | GND                     |        |

|         |    |                         |               |                         |                        |                         | nk 5                    |                     | Deelee                 |                                |                         |                            | nk 4                    |                         |                        | DS099                   | -4_10_030503            |        |

| <u></u> | п. | <b>-</b>                |               |                         |                        | -                       | re 49: I                |                     |                        | -                              | en possib               |                            |                         | <b>F</b> : User         | I/O or inr             | out voltac              | le referer              | nce    |

| 113     |    | O: Unres                | -             |                         |                        | ļ                       | us                      | er I/O              | -                      |                                |                         |                            | for b                   | ank                     |                        |                         |                         |        |

| 16      | b  | ank                     |               |                         |                        |                         |                         |                     |                        | -                              | ock buffer              |                            |                         | <b>:O:</b> Outp         | U                      | ,                       |                         |        |

| 7       |    | ONFIG:                  |               | -                       |                        | l                       |                         |                     | licated JT             | IAG port                       | pins                    |                            | • (+1.                  | 2V)<br>CAUX: Au         |                        | -                       |                         |        |

| 0       |    | Ι. <b>C.:</b> Νο ι      | unconneo      | cted pins               | in this p              | ackage                  | 32 GN                   | ND: Grou            | Ind                    |                                |                         |                            | 8 (+2.                  |                         | annar y V              | snaye su                | אאי                     |        |

www.xilinx.com

#### Table 98: FG320 Package Pinout (Cont'd)

| Bank   | XC3S400, XC3S1000, XC3S1500<br>Pin Name | FG320<br>Pin Number | Туре   |

|--------|-----------------------------------------|---------------------|--------|

| N/A    | VCCINT                                  | N6                  | VCCINT |

| N/A    | VCCINT                                  | N7                  | VCCINT |

| VCCAUX | CCLK                                    | T15                 | CONFIG |

| VCCAUX | DONE                                    | R15                 | CONFIG |

| VCCAUX | HSWAP_EN                                | E6                  | CONFIG |

| VCCAUX | МО                                      | P5                  | CONFIG |

| VCCAUX | M1                                      | U3                  | CONFIG |

| VCCAUX | M2                                      | R4                  | CONFIG |

| VCCAUX | PROG_B                                  | E5                  | CONFIG |

| VCCAUX | тск                                     | E14                 | JTAG   |

| VCCAUX | TDI                                     | D4                  | JTAG   |

| VCCAUX | TDO                                     | D15                 | JTAG   |

| VCCAUX | TMS                                     | B16                 | JTAG   |

### User I/Os by Bank

Table 99 indicates how the available user-I/O pins are distributed between the eight I/O banks on the FG320 package.

| Package Edge | I/O Bank | Maximum | Maximum    | All Possible I/O Pins by Type |      |     |      |      |

|--------------|----------|---------|------------|-------------------------------|------|-----|------|------|

| Fackage Euge |          | I/O     | LVDS Pairs | I/O                           | DUAL | DCI | VREF | GCLK |

| Тор          | 0        | 26      | 11         | 19                            | 0    | 2   | 3    | 2    |

| юр           | 1        | 26      | 11         | 19                            | 0    | 2   | 3    | 2    |

| Right        | 2        | 29      | 14         | 23                            | 0    | 2   | 4    | 0    |

| night        | 3        | 29      | 14         | 23                            | 0    | 2   | 4    | 0    |

| Bottom       | 4        | 27      | 11         | 13                            | 6    | 2   | 4    | 2    |

| Dottom       | 5        | 26      | 11         | 13                            | 6    | 2   | 3    | 2    |

| Left         | 6        | 29      | 14         | 23                            | 0    | 2   | 4    | 0    |

| Leit         | 7        | 29      | 14         | 23                            | 0    | 2   | 4    | 0    |

Table 99: User I/Os Per Bank in FG320 Package

# FG676: 676-lead Fine-pitch Ball Grid Array

The 676-lead fine-pitch ball grid array package, FG676, supports five different Spartan-3 devices, including the XC3S1000, XC3S1500, XC3S2000, XC3S4000, and XC3S5000. All five have nearly identical footprints but are slightly different, primarily due to unconnected pins on the XC3S1000 and XC3S1500. For example, because the XC3S1000 has fewer I/O pins, this device has 98 unconnected pins on the FG676 package, labeled as "N.C." In Table 103 and Figure 53, these unconnected pins are indicated with a black diamond symbol (♦). The XC3S1500, however, has only two unconnected pins, also labeled "N.C." in the pinout table but indicated with a black square symbol (■).

All the package pins appear in Table 103 and are sorted by bank number, then by pin name. Pairs of pins that form a differential I/O pair appear together in the table. The table also shows the pin number for each pin and the pin type, as defined earlier.

If there is a difference between the XC3S1000, XC3S1500, XC3S2000, XC3S4000, and XC3S5000 pinouts, then that difference is highlighted in Table 103. If the table entry is shaded grey, then there is an unconnected pin on either the XC3S1000 or XC3S1500 that maps to a user-I/O pin on the XC3S2000, XC3S4000, and XC3S5000. If the table entry is shaded tan, then the unconnected pin on either the XC3S1000 or XC3S1500 maps to a VREF-type pin on the XC3S2000, XC3S4000, and XC3S5000. If the other VREF pins in the bank all connect to a voltage reference to support a special I/O standard, then also connect the N.C. pin on the XC3S1000 or XC3S1500 to the same VREF voltage. This provides maximum flexibility as you could potentially migrate a design from the XC3S1000 through to the XC3S5000 FPGA without changing the printed circuit board.

An electronic version of this package pinout table and footprint diagram is available for download from the Xilinx website at <a href="http://www.xilinx.com/support/documentation/data\_sheets/s3\_pin.zip">http://www.xilinx.com/support/documentation/data\_sheets/s3\_pin.zip</a>.

## **Pinout Table**

| Bank | XC3S1000<br>Pin Name | XC3S1500<br>Pin Name | XC3S2000<br>Pin Name | XC3S4000<br>Pin Name | XC3S5000<br>Pin Name     | FG676 Pin<br>Number | Туре |

|------|----------------------|----------------------|----------------------|----------------------|--------------------------|---------------------|------|

| 0    | Ю                    | Ю                    | Ю                    | Ю                    | IO_L04N_0 <sup>(3)</sup> | A3                  | I/O  |

| 0    | Ю                    | Ю                    | Ю                    | Ю                    | Ю                        | A5                  | I/O  |

| 0    | IO                   | IO                   | Ю                    | Ю                    | Ю                        | A6                  | I/O  |

| 0    | IO                   | Ю                    | Ю                    | Ю                    | IO_L04P_0 <sup>(3)</sup> | C4                  | I/O  |

| 0    | N.C. (�)             | IO                   | IO                   | IO                   | IO_L13N_0 <sup>(3)</sup> | C8                  | I/O  |

| 0    | Ю                    | Ю                    | Ю                    | Ю                    | Ю                        | C12                 | I/O  |

| 0    | IO                   | Ю                    | Ю                    | IO                   | IO                       | E13                 | I/O  |

| 0    | IO                   | Ю                    | Ю                    | IO                   | IO                       | H11                 | I/O  |

| 0    | Ю                    | Ю                    | Ю                    | Ю                    | Ю                        | H12                 | I/O  |

| 0    | IO/VREF_0            | IO/VREF_0            | IO/VREF_0            | IO/VREF_0            | IO/VREF_0                | B3                  | VREF |

| 0    | IO/VREF_0            | IO/VREF_0            | IO/VREF_0            | IO/VREF_0            | IO/VREF_0                | F7                  | VREF |

| 0    | IO/VREF_0            | IO/VREF_0            | IO/VREF_0            | IO/VREF_0            | IO/VREF_0                | G10                 | VREF |

| 0    | IO_L01N_0/VRP_0      | IO_L01N_0/VRP_0      | IO_L01N_0/VRP_0      | IO_L01N_0/VRP_0      | IO_L01N_0/VRP_0          | E5                  | DCI  |

| 0    | IO_L01P_0/VRN_0      | IO_L01P_0/VRN_0      | IO_L01P_0/VRN_0      | IO_L01P_0/VRN_0      | IO_L01P_0/VRN_0          | D5                  | DCI  |

| 0    | IO_L05N_0            | IO_L05N_0            | IO_L05N_0            | IO_L05N_0            | IO_L05N_0                | B4                  | I/O  |

| 0    | IO_L05P_0/VREF_0     | IO_L05P_0/VREF_0     | IO_L05P_0/VREF_0     | IO_L05P_0/VREF_0     | IO_L05P_0/VREF_0         | A4                  | VREF |

| 0    | IO_L06N_0            | IO_L06N_0            | IO_L06N_0            | IO_L06N_0            | IO_L06N_0                | C5                  | I/O  |

| 0    | IO_L06P_0            | IO_L06P_0            | IO_L06P_0            | IO_L06P_0            | IO_L06P_0                | B5                  | I/O  |

| 0    | IO_L07N_0            | IO_L07N_0            | IO_L07N_0            | IO_L07N_0            | IO_L07N_0                | E6                  | I/O  |

| 0    | IO_L07P_0            | IO_L07P_0            | IO_L07P_0            | IO_L07P_0            | IO_L07P_0                | D6                  | I/O  |

| 0    | IO_L08N_0            | IO_L08N_0            | IO_L08N_0            | IO_L08N_0            | IO_L08N_0                | C6                  | I/O  |

| 0    | IO_L08P_0            | IO_L08P_0            | IO_L08P_0            | IO_L08P_0            | IO_L08P_0                | B6                  | I/O  |

#### Table 103: FG676 Package Pinout

### Table 103: FG676 Package Pinout (Cont'd)

| Bank | XC3S1000<br>Pin Name | XC3S1500<br>Pin Name | XC3S2000<br>Pin Name | XC3S4000<br>Pin Name | XC3S5000<br>Pin Name            | FG676 Pin<br>Number | Туре |

|------|----------------------|----------------------|----------------------|----------------------|---------------------------------|---------------------|------|

| 0    | VCCO_0               | VCCO_0               | VCCO_0               | VCCO_0               | VCCO_0                          | H9                  | VCCO |

| 0    | VCCO_0               | VCCO_0               | VCCO_0               | VCCO_0               | VCCO_0                          | H10                 | VCCO |

| 0    | VCCO_0               | VCCO_0               | VCCO_0               | VCCO_0               | VCCO_0                          | J11                 | VCCO |

| 0    | VCCO_0               | VCCO_0               | VCCO_0               | VCCO_0               | VCCO_0                          | J12                 | VCCO |

| 0    | VCCO_0               | VCCO_0               | VCCO_0               | VCCO_0               | VCCO_0                          | J13                 | VCCO |

| 0    | VCCO_0               | VCCO_0               | VCCO_0               | VCCO_0               | VCCO_0                          | K13                 | VCCO |

| 1    | Ю                    | Ю                    | IO                   | IO                   | Ю                               | A14                 | I/O  |

| 1    | Ю                    | Ю                    | IO                   | IO                   | Ю                               | A22                 | I/O  |

| 1    | Ю                    | Ю                    | IO                   | IO                   | Ю                               | A23                 | I/O  |

| 1    | Ю                    | Ю                    | IO                   | IO                   | Ю                               | D16                 | I/O  |

| 1    | IO                   | IO                   | IO                   | IO                   | IO_L17P_1 <sup>(3)</sup>        | E18                 | I/O  |

| 1    | IO                   | IO                   | IO                   | IO                   | 10                              | F14                 | I/O  |

| 1    | IO                   | IO                   | IO                   | IO                   | 10                              | F20                 | I/O  |

| 1    | IO                   | IO                   | IO                   | IO                   | IO                              | G19                 | I/O  |

| 1    | IO/VREF_1            | IO/VREF_1            | IO/VREF_1            | IO/VREF_1            | IO/VREF_1                       | C15                 | VREF |

| 1    | IO/VREF_1            | IO/VREF_1            | IO/VREF_1            | IO/VREF_1            | IO/VREF_1                       | C17                 | VREF |

| 1    | N.C. (�)             | IO/VREF_1            | IO/VREF_1            | IO/VREF_1            | IO_L17N_1/VREF_1 <sup>(3)</sup> | D18                 | VREF |

| 1    | IO_L01N_1/VRP_1      | IO_L01N_1/VRP_1      | IO_L01N_1/VRP_1      | IO_L01N_1/VRP_1      | IO_L01N_1/VRP_1                 | D22                 | DCI  |

| 1    | IO_L01P_1/VRN_1      | IO_L01P_1/VRN_1      | IO_L01P_1/VRN_1      | IO_L01P_1/VRN_1      | IO_L01P_1/VRN_1                 | E22                 | DCI  |

| 1    | IO_L04N_1            | IO_L04N_1            | IO_L04N_1            | IO_L04N_1            | IO_L04N_1                       | B23                 | I/O  |

| 1    | IO_L04P_1            | IO_L04P_1            | IO_L04P_1            | IO_L04P_1            | IO_L04P_1                       | C23                 | I/O  |

| 1    | IO_L05N_1            | IO_L05N_1            | IO_L05N_1            | IO_L05N_1            | IO_L05N_1                       | E21                 | I/O  |

| 1    | IO_L05P_1            | IO_L05P_1            | IO_L05P_1            | IO_L05P_1            | IO_L05P_1                       | F21                 | I/O  |

| 1    | IO_L06N_1/VREF_1     | IO_L06N_1/VREF_1     | IO_L06N_1/VREF_1     | IO_L06N_1/VREF_1     | IO_L06N_1/VREF_1                | B22                 | VREF |

| 1    | IO_L06P_1            | IO_L06P_1            | IO_L06P_1            | IO_L06P_1            | IO_L06P_1                       | C22                 | I/O  |

| 1    | IO_L07N_1            | IO_L07N_1            | IO_L07N_1            | IO_L07N_1            | IO_L07N_1                       | C21                 | I/O  |

| 1    | IO_L07P_1            | IO_L07P_1            | IO_L07P_1            | IO_L07P_1            | IO_L07P_1                       | D21                 | I/O  |

| 1    | IO_L08N_1            | IO_L08N_1            | IO_L08N_1            | IO_L08N_1            | IO_L08N_1                       | A21                 | I/O  |

| 1    | IO_L08P_1            | IO_L08P_1            | IO_L08P_1            | IO_L08P_1            | IO_L08P_1                       | B21                 | I/O  |

| 1    | IO_L09N_1            | IO_L09N_1            | IO_L09N_1            | IO_L09N_1            | IO_L09N_1                       | D20                 | I/O  |

| 1    | IO_L09P_1            | IO_L09P_1            | IO_L09P_1            | IO_L09P_1            | IO_L09P_1                       | E20                 | I/O  |

| 1    | IO_L10N_1/VREF_1     | IO_L10N_1/VREF_1     | IO_L10N_1/VREF_1     | IO_L10N_1/VREF_1     | IO_L10N_1/VREF_1                | A20                 | VREF |

| 1    | IO_L10P_1            | IO_L10P_1            | IO_L10P_1            | IO_L10P_1            | IO_L10P_1                       | B20                 | I/O  |

| 1    | N.C. (�)             | IO_L11N_1            | IO_L11N_1            | IO_L11N_1            | IO_L11N_1                       | E19                 | I/O  |

| 1    | N.C. (�)             | IO_L11P_1            | IO_L11P_1            | IO_L11P_1            | IO_L11P_1                       | F19                 | I/O  |

| 1    | N.C. (�)             | IO_L12N_1            | IO_L12N_1            | IO_L12N_1            | IO_L12N_1                       | C19                 | I/O  |

| 1    | N.C. (�)             | IO_L12P_1            | IO_L12P_1            | IO_L12P_1            | IO_L12P_1                       | D19                 | I/O  |

| 1    | IO_L15N_1            | IO_L15N_1            | IO_L15N_1            | IO_L15N_1            | IO_L15N_1                       | A19                 | I/O  |