Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                               |

|--------------------------------|---------------------------------------------------------------|

| Product Status                 | Active                                                        |

| Number of LABs/CLBs            | 3328                                                          |

| Number of Logic Elements/Cells | 29952                                                         |

| Total RAM Bits                 | 589824                                                        |

| Number of I/O                  | 221                                                           |

| Number of Gates                | 1500000                                                       |

| Voltage - Supply               | 1.14V ~ 1.26V                                                 |

| Mounting Type                  | Surface Mount                                                 |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                               |

| Package / Case                 | 320-BGA                                                       |

| Supplier Device Package        | 320-FBGA (19x19)                                              |

| Purchase URL                   | https://www.e-xfl.com/product-detail/xilinx/xc3s1500-4fgg320c |

|                                |                                                               |

Email: info@E-XFL.COM

- - --

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### Table 4: Example Ordering Information

| Device   | Speed Grade |                                 | Package Type/Number of Pins |                                                  |   | emperature Range (T <sub>j</sub> ) |

|----------|-------------|---------------------------------|-----------------------------|--------------------------------------------------|---|------------------------------------|

| XC3S50   | -4          | Standard Performance            | VQ(G)100                    | 100-pin Very Thin Quad Flat Pack (VQFP)          | С | Commercial (0°C to 85°C)           |

| XC3S200  | -5          | High Performance <sup>(1)</sup> | CP(G)132 <sup>(2)</sup>     | 132-pin Chip-Scale Package (CSP)                 | Ι | Industrial (-40°C to 100°C)        |

| XC3S400  |             |                                 | TQ(G)144                    | 144-pin Thin Quad Flat Pack (TQFP)               |   | ·                                  |

| XC3S1000 |             |                                 | PQ(G)208                    | 208-pin Plastic Quad Flat Pack (PQFP)            |   |                                    |

| XC3S1500 |             |                                 | FT(G)256                    | 256-ball Fine-Pitch Thin Ball Grid Array (FTBGA) |   |                                    |

| XC3S2000 |             |                                 | FG(G)320                    | 320-ball Fine-Pitch Ball Grid Array (FBGA)       |   |                                    |

| XC3S4000 |             |                                 | FG(G)456                    | 456-ball Fine-Pitch Ball Grid Array (FBGA)       |   |                                    |

| XC3S5000 |             |                                 | FG(G)676                    | 676-ball Fine-Pitch Ball Grid Array (FBGA)       |   |                                    |

|          |             |                                 | FG(G)900                    | 900-ball Fine-Pitch Ball Grid Array (FBGA)       |   |                                    |

|          |             |                                 | FG(G)1156 <sup>(2)</sup>    | 1156-ball Fine-Pitch Ball Grid Array (FBGA)      |   |                                    |

#### Notes:

1. The -5 speed grade is exclusively available in the Commercial temperature range.

2. The CP132, CPG132, FG1156, and FGG1156 packages are discontinued. See http://www.xilinx.com/support/documentation/spartan-3\_customer\_notices.htm.

# **Revision History**

| Date     | Version | Description                                                                                                                                                                                                                                                                                                                                                                   |

|----------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 04/11/03 | 1.0     | Initial Xilinx release.                                                                                                                                                                                                                                                                                                                                                       |

| 04/24/03 | 1.1     | Updated block RAM, DCM, and multiplier counts for the XC3S50.                                                                                                                                                                                                                                                                                                                 |

| 12/24/03 | 1.2     | Added the FG320 package.                                                                                                                                                                                                                                                                                                                                                      |

| 07/13/04 | 1.3     | Added information on Pb-free packaging options.                                                                                                                                                                                                                                                                                                                               |

| 01/17/05 | 1.4     | Referenced Spartan-3 XA Automotive FPGA families in Table 1. Added XC3S50CP132, XC3S2000FG456, XC3S4000FG676 options to Table 3. Updated Package Marking to show mask revision code, fabrication facility code, and process technology code.                                                                                                                                  |

| 08/19/05 | 1.5     | Added package markings for BGA packages (Figure 3) and CP132/CPG132 packages (Figure 4).<br>Added differential (complementary single-ended) HSTL and SSTL I/O standards.                                                                                                                                                                                                      |

| 04/03/06 | 2.0     | Increased number of supported single-ended and differential I/O standards.                                                                                                                                                                                                                                                                                                    |

| 04/26/06 | 2.1     | Updated document links.                                                                                                                                                                                                                                                                                                                                                       |

| 05/25/07 | 2.2     | Updated Package Marking to allow for dual-marking.                                                                                                                                                                                                                                                                                                                            |

| 11/30/07 | 2.3     | Added XC3S5000 FG(G)676 to Table 3. Noted that FG(G)1156 package is being discontinued and updated max I/O count.                                                                                                                                                                                                                                                             |

| 06/25/08 | 2.4     | Updated max I/O counts based on FG1156 discontinuation. Clarified dual mark in Package Marking.<br>Updated formatting and links.                                                                                                                                                                                                                                              |

| 12/04/09 | 2.5     | CP132 and CPG132 packages are being discontinued. Added link to Spartan-3 FPGA customer notices. Updated Table 3 with package footprint dimensions.                                                                                                                                                                                                                           |

| 10/29/12 | 3.0     | Added Notice of Disclaimer section. Per <u>XCN07022</u> , updated the discontinued FG1156 and FGG1156 package discussion throughout document. Per <u>XCN08011</u> , updated the discontinued CP132 and CPG132 package discussion throughout document. Although the package is discontinued, updated the marking on Figure 4. This product is not recommended for new designs. |

# Spartan-3 FPGA Family: Functional Description

DS099 (v3.0) October 29, 2012

#### **Product Specification**

# **Spartan-3 FPGA Design Documentation**

The functionality of the Spartan®-3 FPGA family is described in the following documents. The topics covered in each guide are listed.

- UG331: Spartan-3 Generation FPGA User Guide

- Clocking Resources

- Digital Clock Managers (DCMs)

- Block RAM

- Configurable Logic Blocks (CLBs)

- Distributed RAM

- SRL16 Shift Registers

- Carry and Arithmetic Logic

- I/O Resources

- Embedded Multiplier Blocks

- Programmable Interconnect

- ISE® Software Design Tools

- IP Cores

- Embedded Processing and Control Solutions

- Pin Types and Package Overview

- Package Drawings

- Powering FPGAs

- UG332: Spartan-3 Generation Configuration User Guide

- Configuration Overview

- Configuration Pins and Behavior

- Bitstream Sizes

- Detailed Descriptions by Mode

- Master Serial Mode using Xilinx Platform Flash PROM

- Slave Parallel (SelectMAP) using a Processor

- Slave Serial using a Processor

- JTAG Mode

- ISE iMPACT Programming Examples

Create a Xilinx user account and sign up to receive automatic e-mail notification whenever this data sheet or the associated user guides are updated.

Sign Up for Alerts on Xilinx.com

<a href="https://secure.xilinx.com/webreg/register.do">https://secure.xilinx.com/webreg/register.do</a>

<a href="https://secure.xilinx.com/webreg/register.do">group=myprofile&languageID=1</a>

For specific hardware examples, see the Spartan-3 FPGA Starter Kit board web page, which has links to various design examples and the user guide.

- Spartan-3 FPGA Starter Kit Board page

<u>http://www.xilinx.com/s3starter</u>

- <u>UG130</u>: Spartan-3 FPGA Starter Kit User Guide

<sup>©</sup> Copyright 2003–2012 Xilinx, Inc. XILINX, the Xilinx logo, Virtex, Spartan, ISE, Artix, Kintex, Zynq, Vivado, and other designated brands included herein are trademarks of Xilinx in the United States and other countries. PCI and PCI-X are trademarks of PCI-SIG and used under license. All other trademarks are the property of their respective owners.

### Supply Voltages for the IOBs

Three different supplies power the IOBs:

- The V<sub>CCO</sub> supplies, one for each of the FPGA's I/O banks, power the output drivers, except when using the GTL and GTLP signal standards. The voltage on the V<sub>CCO</sub> pins determines the voltage swing of the output signal.

- V<sub>CCINT</sub> is the main power supply for the FPGA's internal logic.

- The V<sub>CCAUX</sub> is an auxiliary source of power, primarily to optimize the performance of various FPGA functions such as I/O switching.

## The I/Os During Power-On, Configuration, and User Mode

With no power applied to the FPGA, all I/Os are in a high-impedance state. The  $V_{CCINT}$  (1.2V),  $V_{CCAUX}$  (2.5V), and  $V_{CCO}$  supplies may be applied in any order. Before power-on can finish,  $V_{CCINT}$ ,  $V_{CCO}$  Bank 4, and  $V_{CCAUX}$  must have reached their respective minimum recommended operating levels (see Table 29, page 59). At this time, all I/O drivers also will be in a high-impedance state.  $V_{CCO}$  Bank 4,  $V_{CCINT}$ , and  $V_{CCAUX}$  serve as inputs to the internal Power-On Reset circuit (POR).

A Low level applied to the HSWAP\_EN input enables pull-up resistors on User I/Os from power-on throughout configuration. A High level on HSWAP\_EN disables the pull-up resistors, allowing the I/Os to float. If the HSWAP\_EN pin is floating, then an internal pull-up resistor pulls HSWAP\_EN High. As soon as power is applied, the FPGA begins initializing its configuration memory. At the same time, the FPGA internally asserts the Global Set-Reset (GSR), which asynchronously resets all IOB storage elements to a Low state.

Upon the completion of initialization, INIT\_B goes High, sampling the M0, M1, and M2 inputs to determine the configuration mode. At this point, the configuration data is loaded into the FPGA. The I/O drivers remain in a high-impedance state (with or without pull-up resistors, as determined by the HSWAP\_EN input) throughout configuration.

The Global Three State (GTS) net is released during Start-Up, marking the end of configuration and the beginning of design operation in the User mode. At this point, those I/Os to which signals have been assigned go active while all unused I/Os remain in a high-impedance state. The release of the GSR net, also part of Start-up, leaves the IOB registers in a Low state by default, unless the loaded design reverses the polarity of their respective RS inputs.

In User mode, all internal pull-up resistors on the I/Os are disabled and HSWAP\_EN becomes a "don't care" input. If it is desirable to have pull-up or pull-down resistors on I/Os carrying signals, the appropriate symbol—e.g., PULLUP, PULLDOWN—must be placed at the appropriate pads in the design. The Bitstream Generator (Bitgen) option UnusedPin available in the Xilinx development software determines whether unused I/Os collectively have pull-up resistors, pull-down resistors, or no resistors in User mode.

# **CLB** Overview

For more details on the CLBs, refer to the chapter entitled "Using Configurable Logic Blocks" in UG331.

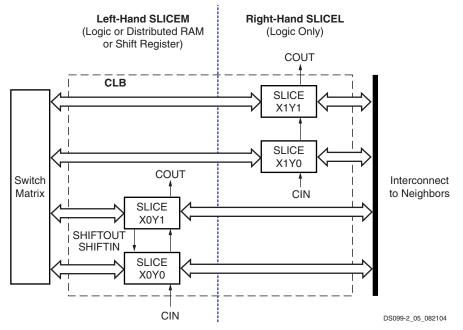

The Configurable Logic Blocks (CLBs) constitute the main logic resource for implementing synchronous as well as combinatorial circuits. Each CLB comprises four interconnected slices, as shown in Figure 11. These slices are grouped in pairs. Each pair is organized as a column with an independent carry chain.

The nomenclature that the FPGA Editor—part of the Xilinx development software—uses to designate slices is as follows: The letter 'X' followed by a number identifies columns of slices. The 'X' number counts up in sequence from the left side of the die to the right. The letter 'Y' followed by a number identifies the position of each slice in a pair as well as indicating the CLB row. The 'Y' number counts slices starting from the bottom of the die according to the sequence: 0, 1, 0, 1 (the first CLB row); 2, 3, 2, 3 (the second CLB row); etc. Figure 11 shows the CLB located in the lower left-hand corner of the die. Slices X0Y0 and X0Y1 make up the column-pair on the left where as slices X1Y0 and X1Y1 make up the column-pair on the right. For each CLB, the term "left-hand" (or SLICEM) indicates the pair of slices labeled with an even 'X' number, such as X0, and the term "right-hand" (or SLICEL) designates the pair of slices with an odd 'X' number, e.g., X1.

Figure 11: Arrangement of Slices within the CLB

### **Elements Within a Slice**

All four slices have the following elements in common: two logic function generators, two storage elements, wide-function multiplexers, carry logic, and arithmetic gates, as shown in Figure 12, page 24. Both the left-hand and right-hand slice pairs use these elements to provide logic, arithmetic, and ROM functions. Besides these, the left-hand pair supports two additional functions: storing data using Distributed RAM and shifting data with 16-bit registers. Figure 12 is a diagram of the left-hand slice; therefore, it represents a superset of the elements and connections to be found in all slices. See Function Generator, page 25 for more information.

The RAM-based function generator—also known as a Look-Up Table or LUT—is the main resource for implementing logic functions. Furthermore, the LUTs in each left-hand slice pair can be configured as Distributed RAM or a 16-bit shift register. For information on the former, refer to the chapter entitled "Using Look-Up Tables as Distributed RAM" in <u>UG331</u>; for information on the latter, refer to the chapter entitled "Using Look-Up Tables as Shift Registers" in <u>UG331</u>. The function generators located in the upper and lower portions of the slice are referred to as the "G" and "F", respectively.

The storage element, which is programmable as either a D-type flip-flop or a level-sensitive latch, provides a means for synchronizing data to a clock signal, among other uses. The storage elements in the upper and lower portions of the slice are called FFY and FFX, respectively.

Wide-function multiplexers effectively combine LUTs in order to permit more complex logic operations. Each slice has two of these multiplexers with F5MUX in the lower portion of the slice and FiMUX in the upper portion. Depending on the slice, FiMUX takes on the name F6MUX, F7MUX, or F8MUX. For more details on the multiplexers, refer to the chapter entitled "Using Dedicated Multiplexers" in <u>UG331</u>.

The carry chain, together with various dedicated arithmetic logic gates, support fast and efficient implementations of math operations. The carry chain enters the slice as CIN and exits as COUT. Five multiplexers control the chain: CYINIT, CYOF, and CYMUXF in the lower portion as well as CYOG and CYMUXG in the upper portion. The dedicated arithmetic logic includes the exclusive-OR gates XORG and XORF (upper and lower portions of the slice, respectively) as well as the AND gates GAND and FAND (upper and lower portions, respectively). For more details on the carry logic, refer to the chapter entitled "Using Carry and Arithmetic Logic" in <u>UG331</u>.

# Main Logic Paths

Central to the operation of each slice are two nearly identical data paths, distinguished using the terms *top* and *bottom*. The description that follows uses names associated with the bottom path. (The top path names appear in parentheses.) The basic path originates at an interconnect-switch matrix outside the CLB. Four lines, F1 through F4 (or G1 through G4 on the

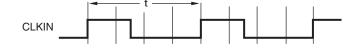

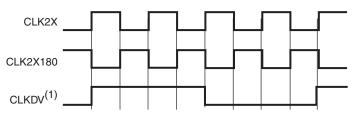

Phase: 0° 90° 180° 270° 0° 90° 180° 270° 0°

Input Signal (40% Duty Cycle)

**Output Signal - Duty Cycle is Always Corrected**

**Output Signal - Attribute Corrects Duty Cycle**

Figure 22: Characteristics of the DLL Clock Outputs

# **Digital Frequency Synthesizer (DFS)**

The DFS component generates clock signals the frequency of which is a product of the clock frequency at the CLKIN input and a ratio of two user-determined integers. Because of the wide range of possible output frequencies such a ratio permits, the DFS feature provides still further flexibility than the DLL's basic synthesis options as described in the preceding section. The DFS component's two dedicated outputs, CLKFX and CLKFX180, are defined in Table 19.

The signal at the CLKFX180 output is essentially an inversion of the CLKFX signal. These two outputs always exhibit a 50% duty cycle. This is true even when the CLKIN signal does not. These DFS clock outputs are driven at the same time as the DLL's seven clock outputs.

The numerator of the ratio is the integer value assigned to the attribute CLKFX\_MULTIPLY and the denominator is the integer value assigned to the attribute CLKFX\_DIVIDE. These attributes are described in Table 18.

### The Standard Configuration Interface

Configuration signals belong to one of two different categories: Dedicated or Dual-Purpose. Which category determines which of the FPGA's power rails supplies the signal's driver and, thus, helps describe the electrical characteristics at the pin.

The Dedicated configuration pins include PROG\_B, HSWAP\_EN, TDI, TMS, TCK, TDO, CCLK, DONE, and M0-M2. These pins are powered by the V<sub>CCAUX</sub> supply.

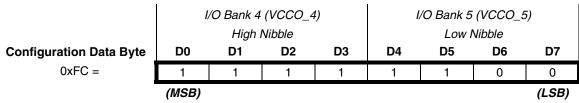

The Dual-Purpose configuration pins comprise INIT\_B, DOUT, BUSY, RDWR\_B, CS\_B, and DIN/D0-D7. Each of these pins, according to its bank placement, uses the  $V_{CCO}$  lines for either Bank 4 (VCCO\_4 on most packages, VCCO\_BOTTOM on TQ144 and CP132 packages) or Bank 5 (VCCO\_5). All the signals used in the serial configuration modes rely on VCCO\_4 power. Signals used in the parallel configuration modes and Readback require from VCCO\_5 as well as from VCCO\_4.

Both the Dedicated signals described above and the Dual-Purpose signals constitute the configuration interface. The Dedicated pins, powered by the 2.5V  $V_{CCAUX}$  supply, always use the LVCMOS25 I/O standard. The Dual-Purpose signals, however, are powered by the VCCO\_4 supply and also by the VCCO\_5 supply in the Parallel configuration modes. The simplest configuration interface uses 2.5V for VCCO\_4 and VCCO\_5, if required. However, VCCO\_4 and, if needed, VCCO\_5 can be voltages other than 2.5V but then the configuration interface will have two voltage levels: 2.5V for V<sub>CCAUX</sub> and a separate  $V_{CCO}$  supply. The Dual-Purpose signals default to the LVCMOS input and output levels for the associated  $V_{CCO}$  voltage supply.

### **3.3V-Tolerant Configuration Interface**

A 3.3V-tolerant configuration interface simply requires adding a few external resistors as described in detail in <u>XAPP453</u>: *The 3.3V Configuration of Spartan-3 FPGAs.*

The 3.3V-tolerance is implemented as follows (a similar approach can be used for other supply voltage levels):

Apply 3.3V to VCCO\_4 and, in some configuration modes, to VCCO\_5 to power the Dual-Purpose configuration pins. This scales the output voltages and input thresholds associated with these pins so that they become 3.3V-compatible.

Apply 2.5V to  $V_{CCAUX}$  to power the Dedicated configuration pins. For 3.3V-tolerance, the Dedicated inputs require series resistors to limit the incoming current to 10 mA or less. The Dedicated outputs have reduced noise margin when the FPGA drives a High logic level into another device's 3.3V receiver. Choose a power regulator or supply that can tolerate reverse current on the V<sub>CCAUX</sub> lines.

### **Configuration Modes**

Spartan-3 FPGAs support the following five configuration modes:

- Slave Serial mode

- Master Serial mode

- Slave Parallel (SelectMAP) mode

- Master Parallel (SelectMAP) mode

- Boundary-Scan (JTAG) mode (IEEE 1532/IEEE 1149.1)

#### Slave Serial Mode

In Slave Serial mode, the FPGA receives configuration data in bit-serial form from a serial PROM or other serial source of configuration data. The FPGA on the far right of Figure 26 is set for the Slave Serial mode. The CCLK pin on the FPGA is an input in this mode. The serial bitstream must be set up at the DIN input pin a short time before each rising edge of the externally generated CCLK.

Multiple FPGAs can be daisy-chained for configuration from a single source. After a particular FPGA has been configured, the data for the next device is routed internally to the DOUT pin. The data on the DOUT pin changes on the falling edge of CCLK.

# **Revision History**

| Date     | Version No. | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 04/11/03 | 1.0         | Initial Xilinx release                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 05/19/03 | 1.1         | Added Block RAM column, DCMs, and multipliers to XC3S50 descriptions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 07/11/03 | 1.2         | Explained the configuration port <i>Persist</i> option in Slave Parallel Mode (SelectMAP) section. Updated Figure 8 and Double-Data-Rate Transmission section to indicate that DDR clocking for the XC3S50 is the same as that for all other Spartan-3 devices. Updated description of I/O voltage tolerance in ESD Protection section. In Table 10, changed input termination type for DCI version of the LVCMOS standard to <i>None.</i> Added additional flexibility for making DLL connections in Figure 21 and accompanying text. In the Configuration section, inserted an explanation of how to choose power supplies for the configuration interface, including guidelines for achieving 3.3V-tolerance. |

| 08/24/04 | 1.3         | Showed inversion of 3-state signal (Figure 7). Clarified description of pull-up and pull-down resistors (Table 6 and page 13). Added information on operating block RAM with multipliers to page 26. Corrected output buffer name in Figure 21. Corrected description of how DOUT is synchronized to CCLK (page 47).                                                                                                                                                                                                                                                                                                                                                                                             |

| 08/19/05 | 1.4         | Corrected description of WRITE_FIRST and READ_FIRST in Table 13. Added note regarding address setup and hold time requirements whenever a block RAM port is enabled (Table 13). Added information in the maximum length of a Configuration daisy-chain. Added reference to <u>XAPP453</u> in 3.3V-Tolerant Configuration Interface section. Added information on the STATUS[2] DCM output (Table 23). Added information on CCLK behavior and termination recommendations to Configuration. Added Additional Configuration Details section. Added Powering Spartan-3 FPGAs section. Removed GSR from Figure 31 because its timing is not programmable.                                                            |

| 04/03/06 | 2.0         | Updated Figure 7. Updated Figure 14. Updated Table 10. Updated Figure 22. Corrected Platform Flash supply voltage name and value in Figure 26 and Figure 28. Added No Internal Charge Pumps or Free-Running Oscillators. Corrected a few minor typographical errors.                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 04/26/06 | 2.1         | Added more information on the pull-up resistors that are active during configuration to Configuration.<br>Added information to Boundary-Scan (JTAG) Mode about potential interactions when configuring via JTAG if the mode select pins are set for other than JTAG.                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 05/25/07 | 2.2         | Added Spartan-3 FPGA Design Documentation. Noted SSTL2_I_DCI 25-Ohm driver in Table 10 and Table 11. Added note that pull-down is active during boundary scan tests.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 11/30/07 | 2.3         | Updated links to documentation on xilinx.com.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 06/25/08 | 2.4         | Added HSLVDCI to Table 10. Updated formatting and links.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 12/04/09 | 2.5         | Updated HSLVDCI description in Digitally Controlled Impedance (DCI). Updated the low-voltage differential signaling $V_{CCO}$ values in Table 10. Noted that the CP132 package is being discontinued in The Organization of IOBs into Banks. Updated rule 4 in Rules Concerning Banks. Added software version requirement in The Fixed Phase Mode.                                                                                                                                                                                                                                                                                                                                                               |

| 10/29/12 | 3.0         | Added Notice of Disclaimer. Per XCN07022, updated the discontinued FG1156 and FGG1156 package discussion throughout document. Per XCN08011, updated the discontinued CP132 and CPG132 package discussion throughout document. This product is not recommended for new designs.                                                                                                                                                                                                                                                                                                                                                                                                                                   |

#### Table 45: Timing for the IOB Output Path

|                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                              |                                                                    | Speed Grade        |                    |       |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|--------------------------------------------------------------------|--------------------|--------------------|-------|

| Symbol              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Conditions                                                   | Device                                                             | -5                 | -4                 | Units |

|                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                              |                                                                    | Max <sup>(3)</sup> | Max <sup>(3)</sup> |       |

| Clock-to-Outp       | ut Times                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ·                                                            |                                                                    |                    |                    | -     |

| T <sub>IOCKP</sub>  | When reading from the Output<br>Flip-Flop (OFF), the time from the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | LVCMOS25 <sup>(2)</sup> , 12 mA output drive, Fast slew rate | XC3S200<br>XC3S400                                                 | 1.28               | 1.47               | ns    |

|                     | active transition at the OTCLK input to data appearing at the Output pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                              | XC3S50<br>XC3S1000<br>XC3S1500<br>XC3S2000<br>XC3S4000<br>XC3S5000 | 1.95               | 2.24               | ns    |

| Propagation T       | imes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                              |                                                                    |                    |                    |       |

| T <sub>IOOP</sub>   | The time it takes for data to travel from the IOB's O input to the Output pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | LVCMOS25 <sup>(2)</sup> , 12 mA output drive, Fast slew rate | XC3S200<br>XC3S400                                                 | 1.28               | 1.46               | ns    |

|                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                              | XC3S50<br>XC3S1000<br>XC3S1500<br>XC3S2000<br>XC3S4000<br>XC3S5000 | 1.94               | 2.23               | ns    |

| T <sub>IOOLP</sub>  | The time it takes for data to travel from<br>the O input through the OFF latch to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                              | XC3S200<br>XC3S400                                                 | 1.28               | 1.47               | ns    |

|                     | the Output pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                              | XC3S50<br>XC3S1000<br>XC3S1500<br>XC3S2000<br>XC3S4000<br>XC3S5000 | 1.95               | 2.24               | ns    |

| Set/Reset Time      | es a la construcción de la const |                                                              |                                                                    |                    |                    | 4     |

| T <sub>IOSRP</sub>  | Time from asserting the OFF's SR input to setting/resetting data at the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | LVCMOS25 <sup>(2)</sup> , 12 mA output drive, Fast slew rate | XC3S200<br>XC3S400                                                 | 2.10               | 2.41               | ns    |

|                     | Output pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                              | XC3S50<br>XC3S1000<br>XC3S1500<br>XC3S2000<br>XC3S4000<br>XC3S5000 | 2.77               | 3.18               | ns    |

| T <sub>IOGSRQ</sub> | Time from asserting the Global Set<br>Reset (GSR) net to setting/resetting<br>data at the Output pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                              | All                                                                | 8.07               | 9.28               | ns    |

#### Notes:

1. The numbers in this table are tested using the methodology presented in Table 48 and are based on the operating conditions set forth in Table 32 and Table 35.

2. This time requires adjustment whenever a signal standard other than LVCMOS25 with 12 mA drive and Fast slew rate is assigned to the data Output. When this is true, *add* the appropriate Output adjustment from Table 47.

3. For minimums, use the values reported by the Xilinx timing analyzer.

### Timing Measurement Methodology

When measuring timing parameters at the programmable I/Os, different signal standards call for different test conditions. Table 48 presents the conditions to use for each standard.

The method for measuring Input timing is as follows: A signal that swings between a Low logic level of  $V_L$  and a High logic level of  $V_H$  is applied to the Input under test. Some standards also require the application of a bias voltage to the  $V_{REF}$  pins of a given bank to properly set the input-switching threshold. The measurement point of the Input signal ( $V_M$ ) is commonly located halfway between  $V_L$  and  $V_H$ .

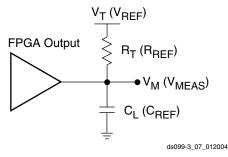

The Output test setup is shown in Figure 35. A termination voltage  $V_T$  is applied to the termination resistor  $R_T$ , the other end of which is connected to the Output. For each standard,  $R_T$  and  $V_T$  generally take on the standard values recommended for minimizing signal reflections. If the standard does not ordinarily use terminations (e.g., LVCMOS, LVTTL), then  $R_T$  is set to 1M $\Omega$  to indicate an open connection, and  $V_T$  is set to zero. The same measurement point ( $V_M$ ) that was used at the Input is also used at the Output.

Notes:

1. The names shown in parentheses are used in the IBIS file.

Figure 35: Output Test Setup

| Signal Standard |                      | Inputs                 |                        |                           | Outputs                   |                    |  |

|-----------------|----------------------|------------------------|------------------------|---------------------------|---------------------------|--------------------|--|

| (IOSTANDARD)    | V <sub>REF</sub> (V) | V <sub>L</sub> (V)     | V <sub>H</sub> (V)     | <b>R</b> <sub>T</sub> (Ω) | <b>V</b> <sub>T</sub> (V) | V <sub>M</sub> (V) |  |

| Single-Ended    |                      |                        |                        |                           |                           |                    |  |

| GTL             | 0.8                  | V <sub>REF</sub> – 0.2 | V <sub>REF</sub> + 0.2 | 25                        | 1.2                       | V <sub>REF</sub>   |  |

| GTL_DCI         |                      |                        |                        | 50                        | 1.2                       |                    |  |

| GTLP            | 1.0                  | V <sub>REF</sub> – 0.2 | V <sub>REF</sub> + 0.2 | 25                        | 1.5                       | V <sub>REF</sub>   |  |

| GTLP_DCI        |                      |                        |                        | 50                        | 1.5                       |                    |  |

| HSLVDCI_15      | 0.9                  | V <sub>REF</sub> – 0.5 | V <sub>REF</sub> + 0.5 | 1M                        | 0                         | 0.75               |  |

| HSLVDCI_18      |                      |                        |                        |                           |                           | 0.90               |  |

| HSLVDCI_25      |                      |                        |                        |                           |                           | 1.25               |  |

| HSLVDCI_33      |                      |                        |                        |                           |                           | 1.65               |  |

| HSTL_I          | 0.75                 | V <sub>REF</sub> – 0.5 | V <sub>REF</sub> + 0.5 | 50                        | 0.75                      | V <sub>REF</sub>   |  |

| HSTL_I_DCI      |                      |                        |                        |                           |                           |                    |  |

| HSTL_III        | 0.90                 | V <sub>REF</sub> – 0.5 | V <sub>REF</sub> + 0.5 | 50                        | 1.5                       | V <sub>REF</sub>   |  |

| HSTL_III_DCI    |                      |                        |                        |                           |                           |                    |  |

| HSTL_I_18       | 0.90                 | V <sub>REF</sub> – 0.5 | V <sub>REF</sub> + 0.5 | 50                        | 0.9                       | V <sub>REF</sub>   |  |

| HSTL_I_DCI_18   |                      |                        |                        |                           |                           |                    |  |

| HSTL_II_18      | 0.90                 | V <sub>REF</sub> – 0.5 | V <sub>REF</sub> + 0.5 | 50                        | 0.9                       | V <sub>REF</sub>   |  |

| HSTL_II_DCI_18  |                      |                        |                        |                           |                           |                    |  |

### Table 48: Test Methods for Timing Measurement at I/Os (Cont'd)

|                | Standard |                      | Inputs                   |                          | Out                       | puts               | Inputs and<br>Outputs |  |

|----------------|----------|----------------------|--------------------------|--------------------------|---------------------------|--------------------|-----------------------|--|

| (IOSTANDARD)   |          | V <sub>REF</sub> (V) | V <sub>L</sub> (V)       | V <sub>H</sub> (V)       | <b>R</b> <sub>T</sub> (Ω) | V <sub>T</sub> (V) | V <sub>M</sub> (V)    |  |

| HSTL_III_18    |          | 1.1                  | V <sub>REF</sub> – 0.5   | V <sub>REF</sub> + 0.5   | 50                        | 1.8                | V <sub>REF</sub>      |  |

| HSTL_III_DC    | CI_18    |                      |                          |                          |                           |                    |                       |  |

| LVCMOS12       |          | -                    | 0                        | 1.2                      | 1M                        | 0                  | 0.6                   |  |

| VCMOS15        |          | -                    | 0                        | 1.5                      | 1M                        | 0                  | 0.75                  |  |

| VDCI_15        |          |                      |                          |                          |                           |                    |                       |  |

| VDCI_DV2_      | 15       |                      |                          |                          |                           |                    |                       |  |

| HSLVDCI_15     | 5        |                      |                          |                          |                           |                    |                       |  |

| VCMOS18        |          | -                    | 0                        | 1.8                      | 1M                        | 0                  | 0.9                   |  |

| VDCI_18        |          |                      |                          |                          |                           |                    |                       |  |

| VDCI_DV2_      | 18       |                      |                          |                          |                           |                    |                       |  |

| ISLVDCI_18     | }        | -                    |                          |                          |                           |                    |                       |  |

| VCMOS25        |          | -                    | 0                        | 2.5                      | 1M                        | 0                  | 1.25                  |  |

| VDCI_25        |          |                      |                          |                          |                           |                    |                       |  |

| LVDCI_DV2_25   |          |                      |                          |                          |                           |                    |                       |  |

| HSLVDCI_25     | 5        |                      |                          |                          |                           |                    |                       |  |

| VCMOS33        |          | -                    | 0                        | 3.3                      | 1M                        | 0                  | 1.65                  |  |

| VDCI_33        |          |                      |                          |                          |                           |                    |                       |  |

| VDCI_DV2_      | 33       |                      |                          |                          |                           |                    |                       |  |

| HSLVDCI_33     |          |                      |                          |                          |                           |                    |                       |  |