# E·XFL

#### AMD Xilinx - XC3S200-4TQ144C Datasheet

Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details |

|---------|

|---------|

| Details                        |                                                             |

|--------------------------------|-------------------------------------------------------------|

| Product Status                 | Active                                                      |

| Number of LABs/CLBs            | 480                                                         |

| Number of Logic Elements/Cells | 4320                                                        |

| Total RAM Bits                 | 221184                                                      |

| Number of I/O                  | 97                                                          |

| Number of Gates                | 200000                                                      |

| Voltage - Supply               | 1.14V ~ 1.26V                                               |

| Mounting Type                  | Surface Mount                                               |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                             |

| Package / Case                 | 144-LQFP                                                    |

| Supplier Device Package        | 144-TQFP (20x20)                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/xilinx/xc3s200-4tq144c |

|                                |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### Coarse Phase Shift Outputs of the DLL Component

In addition to CLK0 for zero-phase alignment to the CLKIN signal, the DLL also provides the CLK90, CLK180 and CLK270 outputs for 90°, 180° and 270° phase-shifted signals, respectively. These signals are described in Table 16, page 33. Their relative timing in the Low Frequency Mode is shown in Figure 22, page 37. The CLK90, CLK180 and CLK270 outputs are not available when operating in the High Frequency mode. (See the description of the DLL\_FREQUENCY\_MODE attribute in Table 17, page 33.) For control in finer increments than 90°, see Phase Shifter (PS), page 39.

### **Basic Frequency Synthesis Outputs of the DLL Component**

The DLL component provides basic options for frequency multiplication and division in addition to the more flexible synthesis capability of the DFS component, described in a later section. These operations result in output clock signals with frequencies that are either a fraction (for division) or a multiple (for multiplication) of the incoming clock frequency. The CLK2X output produces an in-phase signal that is twice the frequency of CLKIN. The CLK2X180 output also doubles the frequency, but is 180° out-of-phase with respect to CLKIN. The CLKDIV output generates a clock frequency that is a predetermined fraction of the CLKIN frequency. The CLKDV\_DIVIDE attribute determines the factor used to divide the CLKIN frequency. The attribute can be set to various values as described in Table 17. The basic frequency synthesis outputs are described in Table 16. Their relative timing in the Low Frequency Mode is shown in Figure 22.

The CLK2X and CLK2X180 outputs are not available when operating in the High Frequency mode. See the description of the DLL\_FREQUENCY\_MODE attribute in Table 18.

### **Duty Cycle Correction of DLL Clock Outputs**

The CLK2X<sup>(1)</sup>, CLK2X180, and CLKDV<sup>(2)</sup> output signals ordinarily exhibit a 50% duty cycle—even if the incoming CLKIN signal has a different duty cycle. A 50% duty cycle means that the High and Low times of each clock cycle are equal. The DUTY\_CYCLE\_CORRECTION attribute determines whether or not duty cycle correction is applied to the CLK0, CLK90, CLK180 and CLK270 outputs. If DUTY\_CYCLE\_CORRECTION is set to TRUE, then the duty cycle of these four outputs is corrected to 50%. If DUTY\_CYCLE\_CORRECTION is set to FALSE, then these outputs exhibit the same duty cycle as the CLKIN signal. Figure 22 compares the characteristics of the DLL's output signals to those of the CLKIN signal.

<sup>1.</sup> The CLK2X output generates a 25% duty cycle clock at the same frequency as the CLKIN signal until the DLL has achieved lock.

<sup>2.</sup> The duty cycle of the CLKDV outputs may differ somewhat from 50% (i.e., the signal will be High for less than 50% of the period) when the CLKDV\_DIVIDE attribute is set to a non-integer value *and* the DLL is operating in the High Frequency mode.

The output frequency (f<sub>CLKEX</sub>) can be expressed as a function of the incoming clock frequency (f<sub>CLKIN</sub>) as follows:

Regarding the two attributes, it is possible to assign any combination of integer values, provided that two conditions are met:

- The two values fall within their corresponding ranges, as specified in Table 18.

- The f<sub>CLKFX</sub> frequency calculated from the above expression accords with the DCM's operating frequency specifications.

For example, if  $CLKFX_MULTIPLY = 5$  and  $CLKFX_DIVIDE = 3$ , then the frequency of the output clock signal would be 5/3 that of the input clock signal.

#### **DFS Frequency Modes**

The DFS supports two operating modes, High Frequency and Low Frequency, with each specified over a different clock frequency range. The DFS\_FREQUENCY\_MODE attribute chooses between the two modes. When the attribute is set to LOW, the Low Frequency mode permits the two DFS outputs to operate over a low-to-moderate frequency range. When the attribute is set to HIGH, the High Frequency mode allows both these outputs to operate at the highest possible frequencies.

#### DFS With or Without the DLL

The DFS component can be used with or without the DLL component:

Without the DLL, the DFS component multiplies or divides the CLKIN signal frequency according to the respective CLKFX\_MULTIPLY and CLKFX\_DIVIDE values, generating a clock with the new target frequency on the CLKFX and CLKFX180 outputs. Though classified as belonging to the DLL component, the CLKIN input is shared with the DFS component. This case does not employ feedback loop; therefore, it cannot correct for clock distribution delay.

With the DLL, the DFS operates as described in the preceding case, only with the additional benefit of eliminating the clock distribution delay. In this case, a feedback loop from the CLK0 output to the CLKFB input must be present.

The DLL and DFS components work together to achieve this phase correction as follows: Given values for the CLKFX\_MULTIPLY and CLKFX\_DIVIDE attributes, the DLL selects the delay element for which the output clock edge coincides with the input clock edge whenever mathematically possible. For example, when CLKFX\_MULTIPLY = 5 and CLKFX\_DIVIDE = 3, the input and output clock edges will coincide every three input periods, which is equivalent in time to five output periods.

Smaller CLKFX\_MULTIPLY and CLKFX\_DIVIDE values achieve faster lock times. With no factors common to the two attributes, alignment will occur once with every number of cycles equal to the CLKFX\_DIVIDE value. Therefore, it is recommended that the user reduce these values by factoring wherever possible. For example, given CLKFX\_MULTIPLY = 9 and CLKFX\_DIVIDE = 6, removing a factor of three yields CLKFX\_MULTIPLY = 3 and CLKFX\_DIVIDE = 2. While both value-pairs will result in the multiplication of clock frequency by 3/2, the latter value-pair will enable the DLL to lock more quickly.

#### Table 18: DFS Attributes

| Attribute Description |                                                        | Values               |

|-----------------------|--------------------------------------------------------|----------------------|

| DFS_FREQUENCY_MODE    | Chooses between High Frequency and Low Frequency modes | Low, High            |

| CLKFX_MULTIPLY        | Frequency multiplier constant                          | Integer from 2 to 32 |

| CLKFX_DIVIDE          | Frequency divisor constant                             | Integer from 1 to 32 |

#### Table 19: DFS Signals

| Signal   | Direction | Description                                                                                                                                       |  |  |  |

|----------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| CLKFX    | Output    | Multiplies the CLKIN frequency by the attribute-value ratio (CLKFX_MULTIPLY/CLKFX_DIVIDE) to generate a clock signal with a new target frequency. |  |  |  |

| CLKFX180 | Output    | Generates a clock signal with same frequency as CLKFX, only shifted 180° out-of-phase.                                                            |  |  |  |

# **XILINX**.

# Interconnect

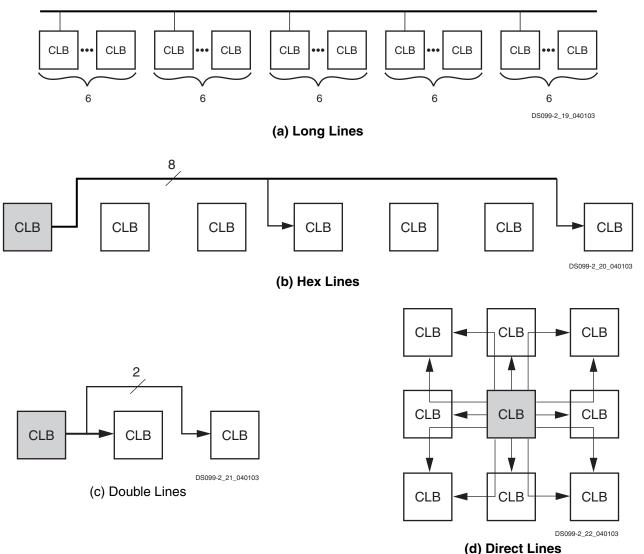

Interconnect (or routing) passes signals among the various functional elements of Spartan-3 devices. There are four kinds of interconnect: Long lines, Hex lines, Double lines, and Direct lines.

Long lines connect to one out of every six CLBs (see section [a] of Figure 25). Because of their low capacitance, these lines are well-suited for carrying high-frequency signals with minimal loading effects (e.g. skew). If all eight Global Clock Inputs are already committed and there remain additional clock signals to be assigned, Long lines serve as a good alternative.

Hex lines connect one out of every three CLBs (see section [b] of Figure 25). These lines fall between Long lines and Double lines in terms of capability: Hex lines approach the high-frequency characteristics of Long lines at the same time, offering greater connectivity.

Double lines connect to every other CLB (see section [c] of Figure 25). Compared to the types of lines already discussed, Double lines provide a higher degree of flexibility when making connections.

Direct lines afford any CLB direct access to neighboring CLBs (see section [d] of Figure 25). These lines are most often used to conduct a signal from a "source" CLB to a Double, Hex, or Long line and then from the longer interconnect back to a Direct line accessing a "destination" CLB.

For more details, refer to the "Using Interconnect" chapter in UG331.

(d) Direct L

Figure 25: Types of Interconnect

(e.g. all configuration pins taken together) when operating in the User mode. This is accomplished by setting the *Persist* option to *Yes*.

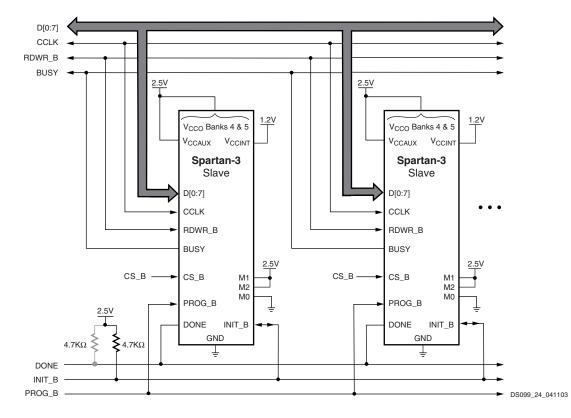

Multiple FPGAs can be configured using the Slave Parallel mode and can be made to start-up simultaneously. Figure 27 shows the device connections. To configure multiple devices in this way, wire the individual CCLK, Data, RDWR\_B, and BUSY pins of all the devices in parallel. The individual devices are loaded separately by deasserting the CS\_B pin of each device in turn and writing the appropriate data.

#### Notes:

- 1. There are two ways to use the DONE line. First, one may set the BitGen option DriveDone to "Yes" only for the last FPGA to be configured in the chain shown above (or for the single FPGA as may be the case). This enables the DONE pin to drive High; thus, no pull-up resistor is necessary. DriveDone is set to "No" for the remaining FPGAs in the chain. Second, DriveDone can be set to "No" for all FPGAs. Then all DONE lines are open-drain and require the pull-up resistor shown in grey. In most cases, a value between 3.3KΩ to 4.7KΩ is sufficient. However, when using DONE synchronously with a long chain of FPGAs, cumulative capacitance may necessitate lower resistor values (e.g. down to 330Ω) in order to ensure a rise time within one clock cycle.

- 2. If the FPGAs use different configuration data files, configure them in sequence by first asserting the CS\_B of one FPGA then asserting the CS\_B of the other FPGA.

- 3. For information on how to program the FPGA using 3.3V signals and power, see 3.3V-Tolerant Configuration Interface.

#### Figure 27: Connection Diagram for Slave Parallel Configuration

# Additional Configuration Details

Additional details about the Spartan-3 FPGA configuration architecture and command set are available in <u>UG332</u>: *Spartan-3 Generation Configuration User Guide* and in application note <u>XAPP452</u>: *Spartan-3 Advanced Configuration Architecture*.

# **Powering Spartan-3 FPGAs**

# Voltage Regulators

Various power supply manufacturers offer complete power solutions for Xilinx FPGAs, including some with integrated multi-rail regulators specifically designed for Spartan-3 FPGAs. The Xilinx Power Corner web page provides links to vendor solution guides as well as Xilinx power estimation and analysis tools.

# Power Distribution System (PDS) Design and Bypass/Decoupling Capacitors

Good power distribution system (PDS) design is important for all FPGA designs, especially for high-performance applications. Proper design results in better overall performance, lower clock and DCM jitter, and a generally more robust system. Before designing the printed circuit board (PCB) for the FPGA design, review application note <u>XAPP623</u>: *Power Distribution System (PDS) Design: Using Bypass/Decoupling Capacitors*.

# **Power-On Behavior**

Spartan-3 FPGAs have a built-in Power-On Reset (POR) circuit that monitors the three power rails required to successfully configure the FPGA. At power-up, the POR circuit holds the FPGA in a reset state until the  $V_{CCINT}$ ,  $V_{CCAUX}$ , and  $V_{CCO}$  Bank 4 supplies reach their respective input threshold levels (see Table 29, page 59). After all three supplies reach their respective threshold, the POR reset is released and the FPGA begins its configuration process.

Because the three supply inputs must be valid to release the POR reset and can be supplied in any order, there are no specific voltage sequencing requirements. However, applying the FPGA's  $V_{CCAUX}$  supply before the  $V_{CCINT}$  supply uses the least I<sub>CCINT</sub> current.

Once all three supplies are valid, the minimum current required to power-on the FPGA is equal to the worst-case quiescent current, as specified in Table 34, page 62. Spartan-3 FPGAs do not require Power-On Surge (POS) current to successfully configure.

# Surplus I<sub>CCINT</sub> if V<sub>CCINT</sub> Applied before V<sub>CCAUX</sub>

If the  $V_{CCINT}$  supply is applied before the  $V_{CCAUX}$  supply, the FPGA may draw a surplus  $I_{CCINT}$  current in addition to the  $I_{CCINT}$  quiescent current levels specified in Table 34. The momentary additional  $I_{CCINT}$  surplus current might be a few hundred milliamperes under nominal conditions, significantly less than the instantaneous current consumed by the bypass capacitors at power-on. However, the surplus current immediately disappears when the  $V_{CCAUX}$  supply is applied, and, in response, the FPGA's  $I_{CCINT}$  quiescent current demand drops to the levels specified in Table 34. The FPGA does not use nor does it require the surplus current to successfully power-on and configure. If applying  $V_{CCINT}$  before  $V_{CCAUX}$ , ensure that the regulator does not have a foldback feature that could inadvertently shut down in the presence of the surplus current.

# Maximum Allowed $V_{\text{CCINT}}$ Ramp Rate on Early Devices, if $V_{\text{VCCINT}} \text{Supply is Last in Sequence}$

All devices with a mask revision code 'E' or later do not have a V<sub>CCINT</sub> ramp rate requirement. See Mask and Fab Revisions, page 58.

Early Spartan-3 FPGAs were produced at a 200 mm wafer production facility and are identified by a fabrication/process code of "FQ" on the device top marking, as shown in Package Marking, page 5. These "FQ" devices have a maximum  $V_{CCINT}$  ramp rate requirement if and only if  $V_{CCINT}$  is the last supply to ramp, after the  $V_{CCAUX}$  and  $V_{CCO}$  Bank 4 supplies. This maximum ramp rate appears as  $T_{CCINT}$  in Table 30, page 60.

# Minimum Allowed V<sub>CCO</sub> Ramp Rate on Early Devices

Devices shipped since 2006 essentially have no  $V_{CCO}$  ramp rate limits, shown in Table 30, page 60. Similarly, all devices with a mask revision code 'E' or later do not have a  $V_{CCO}$  ramp rate limit. See Mask and Fab Revisions, page 58.

#### Table 30: Power Voltage Ramp Time Requirements

| Symbol             | Description                                                                        | Device | Package | Min                     | Max                     | Units |

|--------------------|------------------------------------------------------------------------------------|--------|---------|-------------------------|-------------------------|-------|

| T <sub>CCO</sub>   | V <sub>CCO</sub> ramp time for all eight banks                                     | All    | All     | No limit <sup>(4)</sup> | _                       | N/A   |

| T <sub>CCINT</sub> | $V_{CCINT}$ ramp time, only if $V_{CCINT}$ is last in three-rail power-on sequence | All    | All     | No limit                | No limit <sup>(5)</sup> | N/A   |

#### Notes:

1. If a limit exists, this specification is based on characterization.

2. The ramp time is measured from 10% to 90% of the full nominal voltage swing for all I/O standards.

- 3. For information on power-on current needs, see Power-On Behavior, page 54

- 4. For mask revisions earlier than revision E (see Mask and Fab Revisions, page 58), T<sub>CCO</sub> min is limited to 2.0 ms for the XC3S200 and XC3S400 devices in QFP packages, and limited to 0.6 ms for the XC3S200, XC3S400, XC3S1500, and XC3S4000 devices in the FT and FG packages.

- 5. For earlier device versions with the FQ fabrication/process code (see Mask and Fab Revisions, page 58), T<sub>CCINT</sub> max is limited to 500 µs.

#### Table 31: Power Voltage Levels Necessary for Preserving RAM Contents

| Symbol             | Description                                          | Min | Units |

|--------------------|------------------------------------------------------|-----|-------|

| V <sub>DRINT</sub> | V <sub>CCINT</sub> level required to retain RAM data | 1.0 | V     |

| V <sub>DRAUX</sub> | V <sub>CCAUX</sub> level required to retain RAM data | 2.0 | V     |

#### Notes:

- 1. RAM contents include data stored in CMOS configuration latches.

- 2. The level of the  $V_{CCO}$  supply has no effect on data retention.

- 3. If a brown-out condition occurs where V<sub>CCAUX</sub> or V<sub>CCINT</sub> drops below the retention voltage, then V<sub>CCAUX</sub> or V<sub>CCINT</sub> must drop below the minimum power-on reset voltage indicated in Table 29 in order to clear out the device configuration content.

#### Table 32: General Recommended Operating Conditions

| Symbol                          | Description                                         |                                               | Min   | Nom                                   | Max                                                                                                                                   | Units |

|---------------------------------|-----------------------------------------------------|-----------------------------------------------|-------|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|-------|

| Т <sub>Ј</sub>                  | Junction temperature                                | Commercial                                    | 0     | 25                                    | Max   85   100   1.260   3.465   2.625   10   3.75   3.75   V <sub>CCO</sub> +0.3 <sup>(4)</sup> V <sub>CCO</sub> +0.3 <sup>(4)</sup> | °C    |

|                                 |                                                     | Industrial                                    | -40   | 25                                    | 100                                                                                                                                   | °C    |

| V <sub>CCINT</sub>              | Internal supply voltage                             |                                               | 1.140 | 1.200                                 | 1.260                                                                                                                                 | V     |

| V <sub>CCO</sub> <sup>(1)</sup> | Output driver supply voltage                        |                                               | 1.140 | -                                     | 3.465                                                                                                                                 | V     |

| V <sub>CCAUX</sub>              | Auxiliary supply voltage                            |                                               |       | 2.500                                 | 2.625                                                                                                                                 | V     |

| $\Delta V_{CCAUX}^{(2)}$        | Voltage variance on VCCAUX when using a DCM         |                                               |       | -                                     | 10                                                                                                                                    | mV/ms |

| V <sub>IN</sub> <sup>(3)</sup>  | Voltage applied to all User I/O pins and            | V <sub>CCO</sub> = 3.3V, IO                   | -0.3  | -                                     | 3.75                                                                                                                                  | V     |

|                                 | Dual-Purpose pins relative to GND <sup>(4)(6)</sup> | $V_{\rm CCO} = 3.3$ V, IO_Lxxy <sup>(7)</sup> | -0.3  | -                                     | 3.75                                                                                                                                  | V     |

|                                 |                                                     | $V_{CCO} \le 2.5 V$ , IO                      | -0.3  | -                                     | V <sub>CCO</sub> + 0.3 <sup>(4)</sup>                                                                                                 | V     |

|                                 |                                                     | -0.3                                          | -     | V <sub>CCO</sub> + 0.3 <sup>(4)</sup> | V                                                                                                                                     |       |

|                                 | Voltage applied to all Dedicated pins relativ       | e to GND <sup>(5)</sup>                       | -0.3  | -                                     | V <sub>CCAUX</sub> +0.3 <sup>(5)</sup>                                                                                                | V     |

#### Notes:

- 1. The V<sub>CCO</sub> range given here spans the lowest and highest operating voltages of all supported I/O standards. The recommended V<sub>CCO</sub> range specific to each of the single-ended I/O standards is given in Table 35, and that specific to the differential standards is given in Table 37.

- 2. Only during DCM operation is it recommended that the rate of change of V<sub>CCAUX</sub> not exceed 10 mV/ms.

- 3. Input voltages outside the recommended range are permissible provided that the I<sub>IK</sub> input diode clamp diode rating is met. Refer to Table 28.

- 4. Each of the User I/O and Dual-Purpose pins is associated with one of the V<sub>CCO</sub> rails. Meeting the V<sub>IN</sub> limit ensures that the internal diode junctions that exist between these pins and their associated V<sub>CCO</sub> and GND rails do not turn on. The absolute maximum rating is provided in Table 28.

- All Dedicated pins (PROG\_B, DONE, TCK, TDI, TDO, and TMS) draw power from the V<sub>CCAUX</sub> rail (2.5V). Meeting the V<sub>IN</sub> max limit ensures that the internal diode junctions that exist between each of these pins and the V<sub>CCAUX</sub> and GND rails do not turn on.

- 6. See XAPP459, Eliminating I/O Coupling Effects when Interfacing Large-Swing Single-Ended Signals to User I/O Pins on Spartan-3 Generation FPGAs.

- For single-ended signals that are placed on a differential-capable I/O, V<sub>IN</sub> of –0.2V to –0.3V is supported but can cause increased leakage between the two pins. See the *Parasitic Leakage* section in UG331, *Spartan-3 Generation FPGA User Guide*.

XC3S4000

XC3S5000

-0.61

-0.62

-0.56

-0.57

ns

ns

|                          |                                                                                                          |                                             |          | Speed Grade |       |       |

|--------------------------|----------------------------------------------------------------------------------------------------------|---------------------------------------------|----------|-------------|-------|-------|

| Symbol                   | Description                                                                                              | Conditions                                  | Device   | -5          | -4    | Units |

|                          |                                                                                                          |                                             |          | Min         | Min   |       |

| tup Times                |                                                                                                          |                                             |          |             |       |       |

| T <sub>PSDCM</sub>       | When writing to the Input                                                                                | LVCMOS25 <sup>(2)</sup> ,                   | XC3S50   | 2.37        | 2.71  | ns    |

|                          | Flip-Flop (IFF), the time from the setup of data at the Input pin to                                     | IOBDELAY = NONE,<br>with DCM <sup>(4)</sup> | XC3S200  | 2.13        | 2.35  | ns    |

|                          | the active transition at a Global                                                                        | ,                                           | XC3S400  | 2.15        | 2.36  | ns    |

|                          | Clock pin. The DCM is in use. No Input Delay is programmed.                                              |                                             | XC3S1000 | 2.58        | 2.95  | ns    |

|                          | input Dolay to programmou.                                                                               |                                             | XC3S1500 | 2.55        | 2.91  | ns    |

|                          |                                                                                                          |                                             | XC3S2000 | 2.59        | 2.96  | ns    |

|                          |                                                                                                          |                                             | XC3S4000 | 2.76        | 3.15  | ns    |

|                          |                                                                                                          |                                             | XC3S5000 | 2.69        | 3.08  | ns    |

| the setup of data at the | When writing to IFF, the time from                                                                       | IOBDELAY = IFD,<br>without DCM              | XC3S50   | 3.00        | 3.46  | ns    |

|                          | the setup of data at the Input pin<br>to an active transition at the<br>Global Clock pin. The DCM is not |                                             | XC3S200  | 2.63        | 3.02  | ns    |

|                          |                                                                                                          |                                             | XC3S400  | 2.50        | 2.87  | ns    |

|                          | in use. The Input Delay is<br>programmed.                                                                |                                             | XC3S1000 | 3.50        | 4.03  | ns    |

|                          | programmou                                                                                               |                                             | XC3S1500 | 3.78        | 4.35  | ns    |

|                          |                                                                                                          |                                             | XC3S2000 | 4.98        | 5.73  | ns    |

|                          | XC3S4000                                                                                                 | XC3S4000                                    | 5.25     | 6.05        | ns    |       |

|                          |                                                                                                          |                                             | XC3S5000 | 5.37        | 6.18  | ns    |

| ld Times                 |                                                                                                          |                                             |          |             |       |       |

| T <sub>PHDCM</sub>       | When writing to IFF, the time from                                                                       | LVCMOS25 <sup>(3)</sup> ,                   | XC3S50   | -0.45       | -0.40 | ns    |

|                          | the active transition at the Global<br>Clock pin to the point when data                                  | IOBDELAY = NONE,<br>with DCM <sup>(4)</sup> | XC3S200  | -0.12       | -0.05 | ns    |

|                          | must be held at the Input pin. The                                                                       |                                             | XC3S400  | -0.12       | -0.05 | ns    |

|                          | DCM is in use. No Input Delay is programmed.                                                             |                                             | XC3S1000 | -0.43       | -0.38 | ns    |

|                          | F. 9. anni 6 an                                                                                          |                                             | XC3S1500 | -0.45       | -0.40 | ns    |

|                          |                                                                                                          |                                             | XC3S2000 | -0.47       | -0.42 | ns    |

#### Table 41: System-Synchronous Pin-to-Pin Setup and Hold Times for the IOB Input Path

#### Table 46: Timing for the IOB Three-State Path

|                                    |                                                                                                                                                       |                                                    |                                                                    | Speed Grade        |                    |       |

|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|--------------------------------------------------------------------|--------------------|--------------------|-------|

| Symbol                             | Description                                                                                                                                           | Conditions                                         | Device                                                             | -5                 | -4                 | Units |

|                                    |                                                                                                                                                       |                                                    |                                                                    | Max <sup>(3)</sup> | Max <sup>(3)</sup> |       |

| Synchronous (                      | Output Enable/Disable Times                                                                                                                           |                                                    |                                                                    |                    |                    |       |

| Т <sub>ІОСКНZ</sub>                | Time from the active transition at the<br>OTCLK input of the Three-state Flip-Flop<br>(TFF) to when the Output pin enters the<br>high-impedance state | LVCMOS25, 12 mA<br>output drive, Fast slew<br>rate | All                                                                | 0.74               | 0.85               | ns    |

| T <sub>IOCKON</sub> <sup>(2)</sup> | Time from the active transition at TFF's<br>OTCLK input to when the Output pin drives<br>valid data                                                   |                                                    | All                                                                | 0.72               | 0.82               | ns    |

| Asynchronous                       | Output Enable/Disable Times                                                                                                                           |                                                    |                                                                    |                    |                    |       |

|                                    | Time from asserting the Global Three State (GTS) net to when the Output pin enters the bigh impedance state                                           | LVCMOS25, 12 mA output drive, Fast slew            | XC3S200<br>XC3S400                                                 | 7.71               | 8.87               | ns    |

|                                    | high-impedance state                                                                                                                                  | rate                                               | XC3S50<br>XC3S1000<br>XC3S1500<br>XC3S2000<br>XC3S4000<br>XC3S5000 | 8.38               | 9.63               | ns    |

| Set/Reset Time                     | es                                                                                                                                                    |                                                    |                                                                    | •                  |                    |       |

| T <sub>IOSRHZ</sub>                | Time from asserting TFF's SR input to when<br>the Output pin enters a high-impedance<br>state                                                         | LVCMOS25, 12 mA<br>output drive, Fast slew<br>rate | All                                                                | 1.55               | 1.78               | ns    |

| T <sub>IOSRON</sub> <sup>(2)</sup> | Time from asserting TFF's SR input at TFF to when the Output pin drives valid data                                                                    |                                                    | XC3S200<br>XC3S400                                                 | 2.24               | 2.57               | ns    |

|                                    |                                                                                                                                                       |                                                    | XC3S50<br>XC3S1000<br>XC3S1500<br>XC3S2000<br>XC3S4000<br>XC3S5000 | 2.91               | 3.34               | ns    |

#### Notes:

1. The numbers in this table are tested using the methodology presented in Table 48 and are based on the operating conditions set forth in Table 32 and Table 35.

2. This time requires adjustment whenever a signal standard other than LVCMOS25 with 12 mA drive and Fast slew rate is assigned to the data Output. When this is true, *add* the appropriate Output adjustment from Table 47.

3. For minimums, use the values reported by the Xilinx timing analyzer.

#### Table 47: Output Timing Adjustments for IOB

|                                                 | Add the Adju |       |    |

|-------------------------------------------------|--------------|-------|----|

| ITL<br>ITL_DCI<br>ITLP<br>ITLP_DCI<br>SLVDCI_15 | Speed        | Units |    |

|                                                 | -5           | -4    |    |

| Single-Ended Standards                          |              |       |    |

| GTL                                             | 0            | 0.02  | ns |

| GTL_DCI                                         | 0.13         | 0.15  | ns |

| GTLP                                            | 0.03         | 0.04  | ns |

| GTLP_DCI                                        | 0.23         | 0.27  | ns |

| HSLVDCI_15                                      | 1.51         | 1.74  | ns |

| HSLVDCI_18                                      | 0.81         | 0.94  | ns |

#

# PRODUCT NOT RECOMMENDED FOR NEW DESIGNS

Spartan-3 FPGA Family: DC and Switching Characteristics

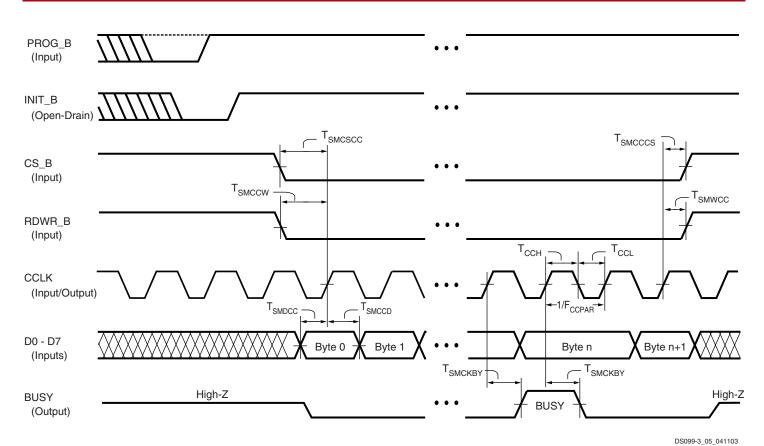

Figure 38: Waveforms for Master and Slave Parallel Configuration

| Table 67 | 7: Timing fo | or the Master a | and Slave Parallel | <b>Configuration Modes</b> |

|----------|--------------|-----------------|--------------------|----------------------------|

|----------|--------------|-----------------|--------------------|----------------------------|

| Ourseland I                       | Description                                                                                                        | Slave/ | All Speed Grades |      | Unite |

|-----------------------------------|--------------------------------------------------------------------------------------------------------------------|--------|------------------|------|-------|

| Symbol                            | Description                                                                                                        | Master | Min              | Max  | Units |

| Clock-to-Out                      | put Times                                                                                                          |        |                  |      |       |

| T <sub>SMCKBY</sub>               | The time from the rising transition on the CCLK pin to a signal transition at the BUSY pin                         | Slave  | -                | 12.0 | ns    |

| Setup Times                       |                                                                                                                    |        |                  |      |       |

| T <sub>SMDCC</sub>                | The time from the setup of data at the D0-D7 pins to the rising transition at the CCLK pin                         | Both   | 10.0             | -    | ns    |

| T <sub>SMCSCC</sub>               | The time from the setup of a logic level at the CS_B pin to the rising transition at the CCLK pin                  |        | 10.0             | -    | ns    |

| T <sub>SMCCW</sub> <sup>(3)</sup> | The time from the setup of a logic level at the RDWR_B pin to the rising transition at the CCLK pin                |        | 10.0             | -    | ns    |

| Hold Times                        |                                                                                                                    |        | 4                | L    |       |

| T <sub>SMCCD</sub>                | The time from the rising transition at the CCLK pin to the point when data is last held at the D0-D7 pins          |        | 0                | -    | ns    |

| T <sub>SMCCCS</sub>               | The time from the rising transition at the CCLK pin to the point when a logic level is last held at the CS_B pin   |        | 0                | -    | ns    |

| T <sub>SMWCC</sub> <sup>(3)</sup> | The time from the rising transition at the CCLK pin to the point when a logic level is last held at the RDWR_B pin |        | 0                | -    | ns    |

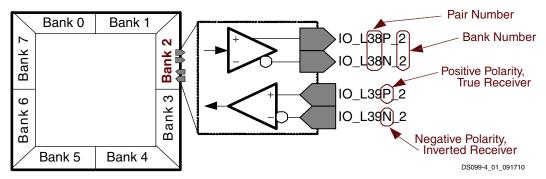

### **Differential Pair Labeling**

A pin supports differential standards if the pin is labeled in the format "Lxxy\_#". The pin name suffix has the following significance. Figure 40 provides a specific example showing a differential input to and a differential output from Bank 2.

- 'L' indicates differential capability.

- "xx" is a two-digit integer, unique for each bank, that identifies a differential pin-pair.

- 'y' is replaced by 'P' for the true signal or 'N' for the inverted. These two pins form one differential pin-pair.

- '#' is an integer, 0 through 7, indicating the associated I/O bank.

If unused, these pins are in a high impedance state. The Bitstream generator option UnusedPin enables a pull-up or pull-down resistor on all unused I/O pins.

#### Behavior from Power-On through End of Configuration

During the configuration process, all pins that are not actively involved in the configuration process are in a high-impedance state. The CONFIG- and JTAG-type pins have an internal pull-up resistor to VCCAUX during configuration. For all other I/O pins, the HSWAP\_EN input determines whether or not pull-up resistors are activated during configuration. HSWAP\_EN = 0 enables the pull-up resistors. HSWAP\_EN = 1 disables the pull-up resistors allowing the pins to float, which is the desired state for hot-swap applications.

Figure 40: Differential Pair Labelling

### **DUAL Type: Dual-Purpose Configuration and I/O Pins**

These pins serve dual purposes. The user-I/O pins are temporarily borrowed during the configuration process to load configuration data into the FPGA. After configuration, these pins are then usually available as a user I/O in the application. If a pin is not applicable to the specific configuration mode—controlled by the mode select pins M2, M1, and M0—then the pin behaves as an I/O-type pin.

There are 12 dual-purpose configuration pins on every package, six of which are part of I/O Bank 4, the other six part of I/O Bank 5. Only a few of the pins in Bank 4 are used in the Serial configuration modes.

See Pin Behavior During Configuration, page 122.

#### **Serial Configuration Modes**

This section describes the dual-purpose pins used during either Master or Slave Serial mode. See Table 75 for Mode Select pin settings required for Serial modes. All such pins are in Bank 4 and powered by VCCO\_4.

In both the Master and Slave Serial modes, DIN is the serial configuration data input. The D1-D7 inputs are unused in serial mode and behave like general-purpose I/O pins.

In all the cases, the configuration data is synchronized to the rising edge of the CCLK clock signal.

The DIN, DOUT, and INIT\_B pins can be retained in the application to support reconfiguration by setting the Persist bitstream generation option. However, the serial modes do not support device readback.

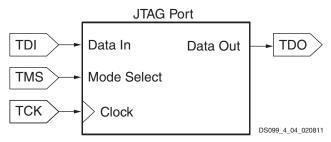

Figure 43: JTAG Port

#### **IDCODE Register**

Spartan-3 FPGAs contain a 32-bit identification register called the IDCODE register, as defined in the IEEE 1149.1 JTAG standard. The fixed value electrically identifies the manufacture (Xilinx) and the type of device being addressed over a JTAG chain. This register allows the JTAG host to identify the device being tested or programmed via JTAG. See Table 78.

#### **Using JTAG Port After Configuration**

The JTAG port is always active and available before, during, and after FPGA configuration. Add the BSCAN\_SPARTAN3 primitive to the design to create user-defined JTAG instructions and JTAG chains to communicate with internal logic.

Furthermore, the contents of the User ID register within the JTAG port can be specified as a Bitstream Generation option. By default, the 32-bit User ID register contains 0xFFFFFFF.

| Part Number | IDCODE Register |

|-------------|-----------------|

| XC3S50      | 0x0140C093      |

| XC3S200     | 0x01414093      |

| XC3S400     | 0x0141C093      |

| XC3S1000    | 0x01428093      |

| XC3S1500    | 0x01434093      |

| XC3S2000    | 0x01440093      |

| XC3S4000    | 0x01448093      |

| XC3S5000    | 0x01450093      |

Table 78: Spartan-3 JTAG IDCODE Register Values (hexadecimal)

### Precautions When Using the JTAG Port in 3.3V Environments

The JTAG port is powered by the +2.5V VCCAUX power supply. When connecting to a 3.3V interface, the JTAG input pins must be current-limited using a series resistor. Similarly, the TDO pin is a CMOS output powered from +2.5V. The TDO output can directly drive a 3.3V input but with reduced noise immunity. See 3.3V-Tolerant Configuration Interface, page 47. See also XAPP453: The 3.3V Configuration of Spartan-3 FPGAs for additional details.

The following interface precautions are recommended when connecting the JTAG port to a 3.3V interface.

- Avoid actively driving the JTAG input signals High with 3.3V signal levels. If required in the application, use series current-limiting resistors to keep the current below 10 mA per pin.

- If possible, drive the FPGA JTAG inputs with drivers that can be placed in high-impedance (Hi-Z) after using the JTAG port. Alternatively, drive the FPGA JTAG inputs with open-drain outputs, which only drive Low. In both cases, pull-up resistors are required. The FPGA JTAG pins have pull-up resistors to VCCAUX before configuration and optional pull-up resistors after configuration, controlled by Bitstream Options, page 125.

# **EXILINX**

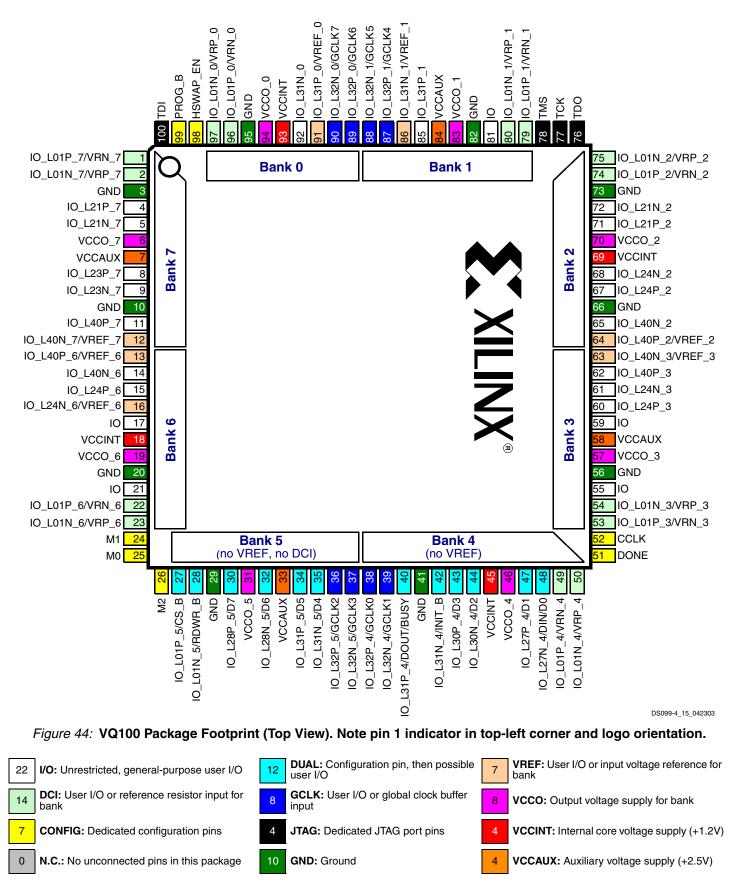

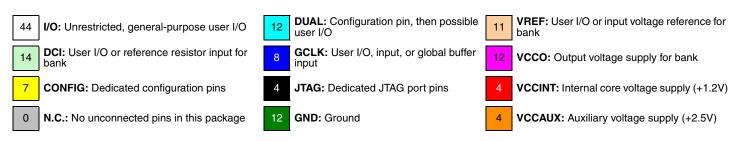

# VQ100 Footprint

# **CP132 Footprint**

|                                 |                                     |   |                                |                                | VCCO_TOP for Top Edge Outputs  |                                |                            |                               |                                |                                      |                                |                                   |                               |                                |                                |                                |        |                                   |

|---------------------------------|-------------------------------------|---|--------------------------------|--------------------------------|--------------------------------|--------------------------------|----------------------------|-------------------------------|--------------------------------|--------------------------------------|--------------------------------|-----------------------------------|-------------------------------|--------------------------------|--------------------------------|--------------------------------|--------|-----------------------------------|

|                                 |                                     |   |                                |                                |                                |                                | Bank 0                     |                               |                                |                                      |                                | Bar                               |                               |                                |                                |                                |        |                                   |

|                                 |                                     |   | 1                              | 2                              | 3<br>1/0                       | 4                              | 5                          | 6                             | 7<br>I/O                       | 8<br>I/O                             | 9<br>1/0                       | 10                                | 11                            | 12                             | 13<br>1/0                      | 14                             | ľ      |                                   |

|                                 |                                     | Α | TDI                            | PROG_B                         | L01N_0<br>VRP_0                | VCCO_<br>TOP                   | VCCAUX                     | <b>I/O</b><br>L30P_0          | L32N_0<br>GCLK7                | L32N_1<br>GCLK5                      | L32P_1<br>GCLK4                | <b>I/O</b><br>L31P_1              | <b>I/O</b><br>L28N_1          | <b>I/O</b><br>L27P_1           | L01N_1<br>VRP_1                | TMS                            |        |                                   |

|                                 |                                     | в | <b>I/O</b><br>L01P_7<br>VRN_7  | <b>I/O</b><br>L01N_7<br>VRP_7  | HSWAP_<br>EN                   | GND                            | <b>I/O</b><br>L27P_0       | <b>I/O</b><br>L30N_0          | <b>I/O</b><br>L31P_0<br>VREF_0 | VCCO_<br>TOP                         | GND                            | VCCINT                            | <b>I/O</b><br>L28P_1          | VCCO_<br>TOP                   | <b>I/O</b><br>L01P_1<br>VRN_1  | тск                            |        |                                   |

|                                 |                                     | С | <b>i/O</b><br>L21N_7           | GND                            | VCCO_<br>LEFT                  | <b>I/O</b><br>L01P_0<br>VRN_0  | <b>I/O</b><br>L27N_0       | VCCINT                        | <b>I/O</b><br>L31N_0           | <b>I/O</b><br>L32P_0<br>GCLK6        | <b>I/O</b><br>L31N_1<br>VREF_1 | VCCAUX                            | <b>I/O</b><br>L27N_1          | GND                            | TDO                            | <b>I/O</b><br>L01P_2<br>VRN_2  |        |                                   |

|                                 | Bank 7                              | D | <b>i/O</b><br>L22N_7           | <b>I/O</b><br>L22P_7           | <b>I/O</b><br>L21P_7           |                                |                            |                               |                                |                                      |                                |                                   |                               | <b>I/O</b><br>L01N_2<br>VRP_2  | VCCO_<br>RIGHT                 | GND                            |        |                                   |

| ts                              | Bai                                 | Е | <b>i/O</b><br>L24P_7           | <b>I/O</b><br>L23N_7           | <b>I/O</b><br>L23P_7           |                                |                            |                               |                                |                                      |                                |                                   |                               | <b>I/O</b><br>L20N_2           | <b>I/O</b><br>L20P_2           | <b>I/O</b><br>L21N_2           | Bank 2 |                                   |

| VCCO_LEFT for Left Edge Outputs |                                     | F | GND                            | <b>I/O</b><br>L40P_7           | <b>I/O</b><br>L24N_7           |                                |                            |                               |                                |                                      |                                |                                   |                               | <b>I/O</b><br>L21P_2           | <b>I/O</b><br>L23N_2<br>VREF_2 | <b>I/O</b><br>L23P_2           |        | s                                 |

| Left Edg                        |                                     | G | <b>I/O</b><br>L40N_7<br>VREF_7 | VCCO_<br>LEFT                  | <b>I/O</b><br>L40P_6<br>VREF_6 |                                |                            |                               |                                |                                      |                                |                                   |                               | <b>I/O</b><br>L24N_2           | <b>I/O</b><br>L24P_2           | <b>I/O</b><br>L40N_2           |        | Output                            |

| EFT for                         |                                     | н | <b>I/O</b><br>L40N_6           | <b>I/O</b><br>L24P_6           | <b>I/O</b><br>L24N_6<br>VREF_6 |                                |                            |                               |                                |                                      |                                |                                   |                               | <b>I/O</b><br>L40P_2<br>VREF_2 | VCCO_<br>RIGHT                 | <b>I/O</b><br>L40N_3<br>VREF_3 |        | ght Edge                          |

| VCCO_L                          |                                     | J | <b>I/O</b><br>L23P_6           | <b>I/O</b><br>L23N_6           | <b>I/O</b><br>L22P_6           |                                |                            |                               |                                |                                      |                                |                                   |                               | <b>I/O</b><br>L24N_3           | <b>I/O</b><br>L40P_3           | GND                            |        | VCCO_RIGHT for Right Edge Outputs |

|                                 | Bank 6                              | κ | <b>I/O</b><br>L22N_6           | <b>I/O</b><br>L20P_6           | <b>I/O</b><br>L20N_6           |                                |                            |                               |                                |                                      |                                |                                   |                               | <b>I/O</b><br>L23P_3<br>VREF_3 | <b>I/O</b><br>L23N_3           | <b>I/O</b><br>L24P_3           | Bank 3 | O_RIGH                            |

|                                 |                                     | L | GND                            | VCCO_<br>LEFT                  | <b>I/O</b><br>L01N_6<br>VRP_6  |                                |                            |                               |                                |                                      |                                |                                   |                               | <b>I/O</b><br>L20N_3           | <b>I/O</b><br>L22P_3           | <b>I/O</b><br>L22N_3           | Ba     | VCC                               |

|                                 |                                     | м | <b>I/O</b><br>L01P_6<br>VRN_6  | М1                             | GND                            | <b>I/O</b><br>L27N_5<br>VREF_5 | VCCAUX                     | <b>I/O</b><br>L31N_5<br>D4    | <b>I/O</b><br>L32P_4<br>GCLK0  | <b>I/O</b><br>L31N_4<br>INIT_B       | VCCINT                         | <b>I/O</b><br>L27N_4<br>DIN<br>D0 | <b>I/O</b><br>L01P_4<br>VRN_4 | VCCO_<br>RIGHT                 | GND                            | <b>I/O</b><br>L20P_3           |        |                                   |

|                                 |                                     | Ν | МО                             | <b>I/O</b><br>L01P_5<br>CS_B   | VCCO_<br>BOTTOM                | <b>I/O</b><br>L28P_5<br>D7     | VCCINT                     | GND                           | VCCO_<br>BOTTOM                | <b>I/O</b><br>L31P_4<br>DOUT<br>BUSY | <b>I/O</b><br>L30N_4<br>D2     | <b>I/O</b><br>L27P_4<br>D1        | GND                           | <b>I/O</b><br>VREF_4           | <b>I/O</b><br>L01N_3<br>VRP_3  | <b>I/O</b><br>L01P_3<br>VRN_3  |        |                                   |

|                                 |                                     | Ρ | M2                             | <b>I/O</b><br>L01N_5<br>RDWR_B | <b>I/O</b><br>L27P_5           | <b>I/O</b><br>L28N_5<br>D6     | <b>I/O</b><br>L31P_5<br>D5 | <b>I/O</b><br>L32P_5<br>GCLK2 | I/O<br>L32N_5<br>GCLK3         | I/O<br>L32N_4<br>GCLK1               | <b>I/O</b><br>L30P_4<br>D3     | VCCAUX                            | VCCO_<br>BOTTOM               | <b>I/O</b><br>L01N_4<br>VRP_4  | DONE                           | CCLK                           |        |                                   |

|                                 |                                     |   |                                |                                |                                | Bar                            | ık 5                       |                               |                                |                                      |                                | Bar                               | nk 4                          |                                |                                |                                |        |                                   |

|                                 | VCCO_BOTTOM for Bottom Edge Outputs |   |                                |                                |                                |                                |                            |                               |                                |                                      | ĺ                              |                                   |                               |                                |                                |                                |        |                                   |

DS099-4\_17\_011005

#### Figure 45: CP132 Package Footprint (Top View). Note pin 1 indicator in top-left corner and logo orientation.

### Table 93: PQ208 Package Pinout (Cont'd)

| Bank | XC3S50<br>Pin Name | XC3S200, XC3S400<br>Pin Names | PQ208 Pin<br>Number | Туре |

|------|--------------------|-------------------------------|---------------------|------|

| 7    | IO_L21N_7          | IO_L21N_7                     | P13                 | I/O  |

| 7    | IO_L21P_7          | IO_L21P_7                     | P12                 | I/O  |

| 7    | IO_L22N_7          | IO_L22N_7                     | P16                 | I/O  |

| 7    | IO_L22P_7          | IO_L22P_7                     | P15                 | I/O  |

| 7    | IO_L23N_7          | IO_L23N_7                     | P19                 | I/O  |

| 7    | IO_L23P_7          | IO_L23P_7                     | P18                 | I/O  |

| 7    | IO_L24N_7          | IO_L24N_7                     | P21                 | I/O  |

| 7    | IO_L24P_7          | IO_L24P_7                     | P20                 | I/O  |

| 7    | N.C. (�)           | IO_L39N_7                     | P24                 | I/O  |

| 7    | N.C. (�)           | IO_L39P_7                     | P22                 | I/O  |

| 7    | IO_L40N_7/VREF_7   | IO_L40N_7/VREF_7              | P27                 | VREF |

| 7    | IO_L40P_7          | IO_L40P_7                     | P26                 | I/O  |

| 7    | VCCO_7             | VCCO_7                        | P6                  | VCCO |

| 7    | VCCO_7             | VCCO_7                        | P23                 | VCCO |

| N/A  | GND                | GND                           | P1                  | GND  |

| N/A  | GND                | GND                           | P186                | GND  |

| N/A  | GND                | GND                           | P195                | GND  |

| N/A  | GND                | GND                           | P202                | GND  |

| N/A  | GND                | GND                           | P163                | GND  |

| N/A  | GND                | GND                           | P170                | GND  |

| N/A  | GND                | GND                           | P179                | GND  |

| N/A  | GND                | GND                           | P134                | GND  |

| N/A  | GND                | GND                           | P145                | GND  |

| N/A  | GND                | GND                           | P151                | GND  |

| N/A  | GND                | GND                           | P157                | GND  |

| N/A  | GND                | GND                           | P112                | GND  |

| N/A  | GND                | GND                           | P118                | GND  |

| N/A  | GND                | GND                           | P129                | GND  |

| N/A  | GND                | GND                           | P82                 | GND  |

| N/A  | GND                | GND                           | P91                 | GND  |

| N/A  | GND                | GND                           | P99                 | GND  |

| N/A  | GND                | GND                           | P105                | GND  |

| N/A  | GND                | GND                           | P53                 | GND  |

| N/A  | GND                | GND                           | P59                 | GND  |

| N/A  | GND                | GND                           | P66                 | GND  |

| N/A  | GND                | GND                           | P75                 | GND  |

| N/A  | GND                | GND                           | P30                 | GND  |

| N/A  | GND                | GND                           | P41                 | GND  |

| N/A  | GND                | GND                           | P47                 | GND  |

| N/A  | GND                | GND                           | P8                  | GND  |

# User I/Os by Bank

Table 97 indicates how the available user-I/O pins are distributed between the eight I/O banks on the FT256 package.

#### Table 97: User I/Os Per Bank in FT256 Package

| Package Edge | I/O Bank | Maximum I/O | All Possible I/O Pins by Type |      |     |      |      |  |  |  |

|--------------|----------|-------------|-------------------------------|------|-----|------|------|--|--|--|

| Таскаде соде |          |             | I/O                           | DUAL | DCI | VREF | GCLK |  |  |  |

| Тор          | 0        | 20          | 13                            | 0    | 2   | 3    | 2    |  |  |  |

| юр           | 1        | 20          | 13                            | 0    | 2   | 3    | 2    |  |  |  |

| Right        | 2        | 23          | 18                            | 0    | 2   | 3    | 0    |  |  |  |

| night        | 3        | 23          | 18                            | 0    | 2   | 3    | 0    |  |  |  |

| Bottom       | 4        | 21          | 8                             | 6    | 2   | 3    | 2    |  |  |  |

| Dottom       | 5        | 20          | 7                             | 6    | 2   | 3    | 2    |  |  |  |

| Left         | 6        | 23          | 18                            | 0    | 2   | 3    | 0    |  |  |  |

| Leit         | 7        | 23          | 18                            | 0    | 2   | 3    | 0    |  |  |  |

# FT256 Footprint

|         |    |                         | 2             |                         | 4                      |                         | nk 0<br>6               | 7                   | 0                      | 9                              | 10                      |                            | nk 1                    | 10                      | 14                     | 15                      | 16                      |        |

|---------|----|-------------------------|---------------|-------------------------|------------------------|-------------------------|-------------------------|---------------------|------------------------|--------------------------------|-------------------------|----------------------------|-------------------------|-------------------------|------------------------|-------------------------|-------------------------|--------|

|         | A  | 1<br>GND                | TDI           | 3<br>IO<br>VREF_0       | 4<br>I/O<br>L01P_0     | 5<br>I/O                | VCCAUX                  | I/O                 | 8<br>I/O<br>L32P_0     | I/O                            | 10<br>I/O<br>L31N_1     | 11<br>VCCAUX               | <b>12</b><br>I/O        | 13<br>I/O<br>L10N_1     | 14<br>I/O<br>L01N_1    | 15<br>TDO               | 16<br>GND               |        |

|         | B  | I/O<br>L01P_7           | GND           | PROG_B                  | VRN_0<br>I/O<br>L01N_0 | I/O<br>L25P 0           | I/O<br>L28P_0           | I/O<br>L30P_0       | GCLK6<br>I/O<br>L32N_0 | GND                            | VREF_1<br>I/O<br>L31P 1 | I/O<br>L29N 1              | I/O<br>L27N_1           | VREF_1<br>I/O<br>L10P 1 | VRP_1<br>I/O<br>L01P_1 | GND                     | l/O<br>L01N_2           |        |

|         | С  | VRN_7<br>I/O<br>L01N_7  | I/O<br>L16N_7 | I/O<br>L16P_7           | VRP_0<br>HSWAP_        | I/O<br>L25N_0           | I/O                     | I/O<br>L30N_0       | I/O<br>L31P_0          | I/O<br>L32N_1                  | I/O                     | I/O<br>L29P 1              | I/O<br>L27P_1           | TMS                     | VRN_1                  | I/O<br>L16N_2           | VRP_2<br>I/O<br>L01P_2  |        |

|         | D  | VRP_7                   | I/O           | VREF_7                  | VCCINT                 | 10                      | I/O                     | I/O                 | I/O                    | GCLK5<br>I/O<br>L32P 1         | I/O                     | I/O                        | IO<br>VREF_1            | VCCINT                  | I/O                    | I/O                     | VRN_2<br>I/O<br>L17P_2  |        |

| Bank 7  | E  | L17N_7<br>I/O           | L17P_7<br>I/O | L19P_7<br>I/O<br>L19N_7 | I/O                    | VCCINT                  | L27P_0                  | L29P_0<br>I/O       |                        |                                | L30N_1<br>I/O           | L28N_1                     | VCCINT                  | I/O                     | L16P_2<br>I/O          | L17N_2                  | VREF_2                  | nk 2   |

| Bai     |    | L20N_7                  | L20P_7        | VREF_7                  | L21P_7                 | 1/0                     | L27N_0                  | L29N_0              |                        |                                | L30P_1                  | L28P_1                     | 1/0                     | L19N_2                  | L19P_2                 | L20N_2                  | L20P_2                  | Bank   |

|         | F  | VCCAUX                  | L22N_7        | L22P_7                  | L21N_7                 | L23P_7                  | GND                     | VCCO_0              | VCCO_0                 |                                |                         | GND                        | L21N_2                  | L21P_2                  | L22N_2                 | L22P_2                  | VCCAUX                  |        |

|         | G  | L40P_7                  | I/O           | L24N_7                  | L24P_7                 | L23N_7                  | VCCO_7                  | GND                 | GND                    | GND                            | GND                     | VCCO_2                     | L23N_2<br>VREF_2        | L23P_2                  | L24N_2                 | L24P_2                  | I/O<br>I/O              |        |

|         | н  | L40N_7<br>VREF_7        | GND           | I/O<br>L39N_7           | I/O<br>L39P_7          | VCCO_7                  | VCCO_7                  | GND                 | GND                    | GND                            | GND                     | VCCO_2                     | VCCO_2                  | I/O<br>L39N_2           | I/O<br>L39P_2          | I/O<br>L40N_2           | L40P_2<br>VREF_2        | _      |

|         | J  | I/O<br>L40P_6<br>VREF_6 | I/O<br>L40N_6 | I/O<br>L39P_6           | I/O<br>L39N_6          | VCCO_6                  | VCCO_6                  | GND                 | GND                    | GND                            | GND                     | VCCO_3                     | VCCO_3                  | I/O<br>L39P_3           | I/O<br>L39N_3          | GND                     | I/O<br>L40N_3<br>VREF_3 |        |

|         | κ  | I/O                     | I/O<br>L24P_6 | I/O<br>L24N_6<br>VREF_6 | I/O<br>L23P_6          | I/O<br>L23N_6           | VCCO_6                  | GND                 | GND                    | GND                            | GND                     | VCCO_3                     | I/O<br>L23N_3           | I/O<br>L24P_3           | I/O<br>L24N_3          | I/O                     | I/O<br>L40P_3           |        |

|         | L  | VCCAUX                  | I/O<br>L22P_6 | I/O<br>L22N_6           | I/O<br>L21P_6          | I/O<br>L21N_6           | GND                     | VCCO_5              | VCCO_5                 | VCCO_4                         | VCCO_4                  | GND                        | I/O<br>L23P_3<br>VREF_3 | I/O<br>L21N_3           | I/O<br>L22P_3          | I/O<br>L22N_3           | VCCAUX                  |        |

| Bank 6  | М  | I/O<br>L20P_6           | I/O<br>L20N_6 | I/O<br>L19P_6           | I/O<br>L19N_6          | VCCINT                  | I/O<br>L28P_5<br>D7     | I/O<br>L30P_5       | VCCO_5                 | VCCO_4                         | I/O<br>L29N_4           | I/O<br>L27N_4<br>DIN<br>D0 | VCCINT                  | I/O<br>L21P_3           | I/O<br>L19N_3          | I/O<br>L20P_3           | I/O<br>L20N_3           | Bank 3 |

|         | N  | I/O<br>L17P_6<br>VREF 6 | I/O<br>L17N_6 | I/O<br>L16P_6           | VCCINT                 | I/O                     | I/O<br>L28N_5<br>D6     | I/O<br>L30N_5       | I/O<br>L32P_5<br>GCLK2 | I/O<br>L31N_4<br>INIT B        | I/O<br>L29P_4           | I/O<br>L27P_4<br>D1        | IO<br>VREF_4            | VCCINT                  | I/O<br>L19P_3          | I/O<br>L17P_3<br>VREF 3 | I/O<br>L17N_3           | _      |

|         | Ρ  | I/O<br>L01P_6<br>VRN_6  | I/O<br>L16N_6 | МО                      | M2                     | l/O<br>L27P_5           | I/O<br>L29P_5<br>VREF 5 | I/O                 | I/O<br>L32N_5<br>GCLK3 | DOUT                           | I/O<br>L30N_4<br>D2     | I/O<br>L28N_4              | I/O<br>L25N_4           | IO<br>VREF_4            | I/O<br>L16P_3          | I/O<br>L16N_3           | I/O<br>L01N_3<br>VRP 3  |        |

|         | R  | I/O                     | GND           | I/O<br>L01P_5<br>CS_B   | I/O<br>L10P_5<br>VRN_5 | I/O<br>L27N_5<br>VREF_5 | I/O<br>L29N_5           | I/O<br>L31P_5<br>D5 | GND                    | BUSY<br>I/O<br>L32N_4<br>GCLK1 | I/O<br>L30P_4<br>D3     | I/O<br>L28P_4              | I/O<br>L25P_4           | I/O<br>L01N_4<br>VRP_4  | DONE                   | GND                     | I/O<br>L01P_3<br>VRN_3  |        |

|         | т  | GND                     | M1            | I/O<br>L01N_5<br>RDWR_B | I/O<br>L10N_5          | I/O                     | VCCAUX                  | I/O                 | IO<br>VREF_5           | I/O<br>L32P_4<br>GCLK0         | IO<br>VREF_4            | VCCAUX                     | I/O                     | I/O<br>L01P_4<br>VRN_4  | I/O                    | CCLK                    | GND                     |        |

|         |    |                         |               |                         |                        |                         | nk 5                    |                     | Deelee                 |                                |                         |                            | nk 4                    |                         |                        | DS099                   | -4_10_030503            |        |

| <u></u> | п. | <b>-</b>                |               |                         |                        | -                       | re 49: I                |                     |                        | -                              | en possib               |                            |                         | <b>F</b> : User         | I/O or inr             | out voltac              | le referer              | nce    |

| 113     |    | O: Unres                | -             |                         |                        | ļ                       | us                      | er I/O              | -                      |                                |                         |                            | for b                   | ank                     |                        |                         |                         |        |

| 16      | b  | ank                     |               |                         |                        |                         |                         |                     |                        | -                              | ock buffer              |                            |                         | <b>:O:</b> Outp         | U                      | ,                       |                         |        |

| 7       |    | ONFIG:                  |               | -                       |                        | l                       |                         |                     | licated JT             | IAG port                       | pins                    |                            | • (+1.                  | 2V)<br>CAUX: Au         |                        | -                       |                         |        |

| 0       |    | Ι. <b>C.:</b> Νο ι      | unconneo      | cted pins               | in this p              | ackage                  | 32 GN                   | ND: Grou            | Ind                    |                                |                         |                            | 8 (+2.                  |                         | annar y V              | snaye su                | אאי                     |        |

#### Table 98: FG320 Package Pinout (Cont'd)

| Bank   | XC3S400, XC3S1000, XC3S1500<br>Pin Name | FG320<br>Pin Number | Туре   |

|--------|-----------------------------------------|---------------------|--------|

| N/A    | VCCINT                                  | N6                  | VCCINT |

| N/A    | VCCINT                                  | N7                  | VCCINT |

| VCCAUX | CCLK                                    | T15                 | CONFIG |

| VCCAUX | DONE                                    | R15                 | CONFIG |

| VCCAUX | HSWAP_EN                                | E6                  | CONFIG |

| VCCAUX | МО                                      | P5                  | CONFIG |

| VCCAUX | M1                                      | U3                  | CONFIG |

| VCCAUX | M2                                      | R4                  | CONFIG |

| VCCAUX | PROG_B                                  | E5                  | CONFIG |

| VCCAUX | тск                                     | E14                 | JTAG   |

| VCCAUX | TDI                                     | D4                  | JTAG   |

| VCCAUX | TDO                                     | D15                 | JTAG   |

| VCCAUX | TMS                                     | B16                 | JTAG   |

### User I/Os by Bank

Table 99 indicates how the available user-I/O pins are distributed between the eight I/O banks on the FG320 package.

| Package Edge | I/O Bank | Maximum | Maximum    |     |      |     |      |      |  |  |

|--------------|----------|---------|------------|-----|------|-----|------|------|--|--|

| Fackage Euge |          | I/O     | LVDS Pairs | I/O | DUAL | DCI | VREF | GCLK |  |  |

| Тор          | 0        | 26      | 11         | 19  | 0    | 2   | 3    | 2    |  |  |

| юр           | 1        | 26      | 11         | 19  | 0    | 2   | 3    | 2    |  |  |

| Right        | 2        | 29      | 14         | 23  | 0    | 2   | 4    | 0    |  |  |

| night        | 3        | 29      | 14         | 23  | 0    | 2   | 4    | 0    |  |  |

| Bottom       | 4        | 27      | 11         | 13  | 6    | 2   | 4    | 2    |  |  |

| Dottom       | 5        | 26      | 11         | 13  | 6    | 2   | 3    | 2    |  |  |

| Loft         | 6        | 29      | 14         | 23  | 0    | 2   | 4    | 0    |  |  |

| Left         | 7        | 29      | 14         | 23  | 0    | 2   | 4    | 0    |  |  |

Table 99: User I/Os Per Bank in FG320 Package

### Table 107: FG900 Package Pinout (Cont'd)

| Bank | XC3S2000<br>Pin Name | XC3S4000, XC3S5000<br>Pin Name | FG900 Pin<br>Number | Туре |

|------|----------------------|--------------------------------|---------------------|------|

| 2    | VCCO_2               | VCCO_2                         | J28                 | VCCO |

| 2    | VCCO_2               | VCCO_2                         | N28                 | VCCO |