Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Obsolete                                                     |

|--------------------------------|--------------------------------------------------------------|

| Number of LABs/CLBs            | 480                                                          |

| Number of Logic Elements/Cells | 4320                                                         |

| Total RAM Bits                 | 221184                                                       |

| Number of I/O                  | 141                                                          |

| Number of Gates                | 200000                                                       |

| Voltage - Supply               | 1.14V ~ 1.26V                                                |

| Mounting Type                  | Surface Mount                                                |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                              |

| Package / Case                 | 208-BFQFP                                                    |

| Supplier Device Package        | 208-PQFP (28x28)                                             |

| Purchase URL                   | https://www.e-xfl.com/product-detail/xilinx/xc3s200-5pqg208c |

|                                |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Table 3 shows the number of user I/Os as well as the number of differential I/O pairs available for each device/package combination.

|                   |            |      |                     | Av                  | vailable   | Usei | r I/Os a   | nd Di | fferent    | ial (Di | iff) I/O   | Pairs | by Pac     | kage | Туре       |      |            |      |                      |                              |

|-------------------|------------|------|---------------------|---------------------|------------|------|------------|-------|------------|---------|------------|-------|------------|------|------------|------|------------|------|----------------------|------------------------------|

| Package           | VQ1<br>VQG |      | CP13<br>CPG         |                     | TQ1<br>TQG |      | PQ2<br>PQG |       | FT2<br>FTG |         | FG3<br>FGG |       | FG4<br>FGG |      | FG6<br>FGG |      | FG9<br>FGG |      |                      | 156 <mark>(1)</mark><br>1156 |

| Footprint<br>(mm) | 16 x       | 16   | 8 x                 | 8                   | 22 x       | 22   | 30.6 x     | 30.6  | 17 x       | 17      | 19 x       | 19    | 23 x       | 23   | 27 x       | 27   | 31 x       | 31   | 35 3                 | x 35                         |

| Device            | User       | Diff | User                | Diff                | User       | Diff | User       | Diff  | User       | Diff    | User       | Diff  | User       | Diff | User       | Diff | User       | Diff | User                 | Diff                         |

| XC3S50            | 63         | 29   | 89 <mark>(1)</mark> | 44 <mark>(1)</mark> | 97         | 46   | 124        | 56    | -          | -       | -          | -     | -          | -    | -          | -    | -          | -    | -                    | -                            |

| XC3S200           | 63         | 29   | -                   | -                   | 97         | 46   | 141        | 62    | 173        | 76      | -          | _     | -          | _    | -          | -    | -          | I    | -                    | -                            |

| XC3S400           | -          | _    | -                   | -                   | 97         | 46   | 141        | 62    | 173        | 76      | 221        | 100   | 264        | 116  | -          | -    | -          | -    | -                    | -                            |

| XC3S1000          | -          | -    | -                   | -                   | -          | -    | -          | -     | 173        | 76      | 221        | 100   | 333        | 149  | 391        | 175  | -          | 1    | Ι                    | -                            |

| XC3S1500          | -          | -    | -                   | -                   | -          | -    | -          | -     | -          | -       | 221        | 100   | 333        | 149  | 487        | 221  | -          | -    | -                    | -                            |

| XC3S2000          | -          | -    | -                   | -                   | -          | -    | -          | -     | -          | -       | -          | -     | 333        | 149  | 489        | 221  | 565        | 270  | -                    | -                            |

| XC3S4000          | -          | -    | 1                   | -                   | -          | -    | -          | -     | -          | -       | -          | -     | -          | -    | 489        | 221  | 633        | 300  | 712 <mark>(1)</mark> | 312 <mark>(1)</mark>         |

| XC3S5000          | -          | -    | -                   | -                   | -          | -    | -          | -     | -          | -       | -          | -     | -          | -    | 489        | 221  | 633        | 300  | 784 <sup>(1)</sup>   | 344 <sup>(1)</sup>           |

### Table 3: Spartan-3 Device I/O Chart

#### Notes:

1. The CP132, CPG132, FG1156, and FGG1156 packages are discontinued. See http://www.xilinx.com/support/documentation/spartan-3\_customer\_notices.htm.

2. All device options listed in a given package column are pin-compatible.

3. User = Single-ended user I/O pins. Diff = Differential I/O pairs.

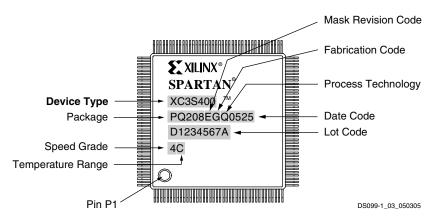

# Package Marking

Figure 2 shows the top marking for Spartan-3 FPGAs in the quad-flat packages. Figure 3 shows the top marking for Spartan-3 FPGAs in BGA packages except the 132-ball chip-scale package (CP132 and CPG132). The markings for the BGA packages are nearly identical to those for the quad-flat packages, except that the marking is rotated with respect to the ball A1 indicator. Figure 4 shows the top marking for Spartan-3 FPGAs in the CP132 and CPG132 packages.

The "5c" and "41" part combinations may be dual marked as "5c/41". Devices with the dual mark can be used as either -5C or -4I devices. Devices with a single mark are only guaranteed for the marked speed grade and temperature range. Some specifications vary according to mask revision. Mask revision E devices are errata-free. All shipments since 2006 have been mask revision E.

Figure 2: Spartan-3 FPGA QFP Package Marking Example for Part Number XC3S400-4PQ208C

# **EXILINX**.

# IOBs

For additional information, refer to the chapter entitled "Using I/O Resources" in UG331: Spartan-3 Generation FPGA User Guide.

# **IOB** Overview

The Input/Output Block (IOB) provides a programmable, bidirectional interface between an I/O pin and the FPGA's internal logic.

A simplified diagram of the IOB's internal structure appears in Figure 7. There are three main signal paths within the IOB: the output path, input path, and 3-state path. Each path has its own pair of storage elements that can act as either registers or latches. For more information, see the Storage Element Functions section. The three main signal paths are as follows:

- The input path carries data from the pad, which is bonded to a package pin, through an optional programmable delay element directly to the I line. There are alternate routes through a pair of storage elements to the IQ1 and IQ2 lines. The IOB outputs I, IQ1, and IQ2 all lead to the FPGA's internal logic. The delay element can be set to ensure a hold time of zero.

- The output path, starting with the O1 and O2 lines, carries data from the FPGA's internal logic through a multiplexer and then a three-state driver to the IOB pad. In addition to this direct path, the multiplexer provides the option to insert a pair of storage elements.

- The 3-state path determines when the output driver is high impedance. The T1 and T2 lines carry data from the FPGA's internal logic through a multiplexer to the output driver. In addition to this direct path, the multiplexer provides the option to insert a pair of storage elements. When the T1 or T2 lines are asserted High, the output driver is high-impedance (floating, hi-Z). The output driver is active-Low enabled.

- All signal paths entering the IOB, including those associated with the storage elements, have an inverter option. Any inverter placed on these paths is automatically absorbed into the IOB.

# **Storage Element Functions**

There are three pairs of storage elements in each IOB, one pair for each of the three paths. It is possible to configure each of these storage elements as an edge-triggered D-type flip-flop (FD) or a level-sensitive latch (LD).

The storage-element-pair on either the Output path or the Three-State path can be used together with a special multiplexer to produce Double-Data-Rate (DDR) transmission. This is accomplished by taking data synchronized to the clock signal's rising edge and converting them to bits synchronized on both the rising and the falling edge. The combination of two registers and a multiplexer is referred to as a Double-Data-Rate D-type flip-flop (FDDR). See Double-Data-Rate Transmission, page 12 for more information.

The signal paths associated with the storage element are described in Table 5.

Table 5: Storage Element Signal Description

| Storage<br>Element<br>Signal | Description        | Function                                                                                                                                                                         |

|------------------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D                            | Data input         | Data at this input is stored on the active edge of CK enabled by CE. For latch operation when the input is enabled, data passes directly to the output Q.                        |

| Q                            | Data output        | The data on this output reflects the state of the storage element. For operation as a latch in transparent mode, Q will mirror the data at D.                                    |

| СК                           | Clock input        | A signal's active edge on this input with CE asserted, loads data into the storage element.                                                                                      |

| CE                           | Clock Enable input | When asserted, this input enables CK. If not connected, CE defaults to the asserted state.                                                                                       |

| SR                           | Set/Reset          | Forces storage element into the state specified by the SRHIGH/SRLOW attributes. The SYNC/ASYNC attribute setting determines if the SR input is synchronized to the clock or not. |

| REV                          | Reverse            | Used together with SR. Forces storage element into the state opposite from what SR does.                                                                                         |

www.xilinx.com

### Table 13: Block RAM Port Signals (Cont'd)

| Signal<br>Description    | Port A<br>Signal Name | Port B<br>Signal Name | Direction | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------------------------|-----------------------|-----------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Data Output Bus          | DOA                   | DOB                   | Output    | Basic data access occurs whenever WE is inactive. The DO outputs mirror the data stored in the addressed memory location.                                                                                                                                                                                                                                                                                                                                |

|                          |                       |                       |           | Data access with WE asserted is also possible if one of the following two attributes is chosen: WRITE_FIRST and READ_FIRST. WRITE_FIRST simultaneously presents the new input data on the DO output port and writes the data to the address RAM location. READ_FIRST presents the previously stored RAM data on the DO output port while writing new data to RAM.                                                                                        |

|                          |                       |                       |           | A third attribute, NO_CHANGE, latches the DO outputs upon the assertion of WE.                                                                                                                                                                                                                                                                                                                                                                           |

|                          |                       |                       |           | It is possible to configure a port's total data path width (w) to be 1, 2, 4, 9, 18, or 36 bits. This selection applies to both the DI and DO paths. See the DI signal description.                                                                                                                                                                                                                                                                      |

| Parity Data<br>Output(s) | DOPA                  | DOPB                  | Output    | Parity inputs represent additional bits included in the data input path to support error detection. The number of parity bits "p" included in the DI (same as for the DO bus) depends on a port's total data path width (w). See Table 14.                                                                                                                                                                                                               |

| Write Enable             | WEA                   | WEB                   | Input     | When asserted together with EN, this input enables the writing of data<br>to the RAM. In this case, the data access attributes WRITE_FIRST,<br>READ_FIRST or NO_CHANGE determines if and how data is updated<br>on the DO outputs. See the DO signal description.<br>When WE is inactive with EN asserted, read operations are still<br>possible. In this case, a transparent latch passes data from the<br>addressed memory location to the DO outputs. |

| Clock Enable             | ENA                   | ENB                   | Input     | When asserted, this input enables the CLK signal to synchronize Block<br>RAM functions as follows: the writing of data to the DI inputs (when WE<br>is also asserted), the updating of data at the DO outputs as well as the<br>setting/resetting of the DO output latches.<br>When de-asserted, the above functions are disabled.                                                                                                                       |

| Set/Reset                | SSRA                  | SSRB                  | Input     | When asserted, this pin forces the DO output latch to the value that the SRVAL attribute is set to. A Set/Reset operation on one port has no effect on the other ports functioning, nor does it disturb the memory's data contents. It is synchronized to the CLK signal.                                                                                                                                                                                |

| Clock                    | CLKA                  | CLKB                  | Input     | This input accepts the clock signal to which read and write operations<br>are synchronized. All associated port inputs are required to meet setup<br>times with respect to the clock signal's active edge. The data output bus<br>responds after a clock-to-out delay referenced to the clock signal's<br>active edge.                                                                                                                                   |

## **Port Aspect Ratios**

On a given port, it is possible to select a number of different possible widths (w - p) for the DI/DO buses as shown in Table 14. These two buses always have the same width. This data bus width selection is independent for each port. If the data bus width of Port A differs from that of Port B, the Block RAM automatically performs a bus-matching function. When data are written to a port with a narrow bus, then read from a port with a wide bus, the latter port will effectively combine "narrow" words to form "wide" words. Similarly, when data are written into a port with a wide bus, then read from a port with a narrow bus, the latter port will divide "wide" words to form "narrow" words. When the data bus width is eight bits or greater, extra parity bits become available. The width of the total data path (*w*) is the sum of the DI/DO bus width and any parity bits (*p*).

The width selection made for the DI/DO bus determines the number of address lines according to the relationship expressed below:

$$r = 14 - [\log(w - p)/\log(2)]$$

In turn, the number of address lines delimits the total number (n) of addressable locations or depth according to the following equation:

$$n = 2^r$$

Equation 2

Equation 1

# DFS Clock Output Connections

There are two basic cases that determine how to connect the DFS clock outputs: on-chip and off-chip, which are illustrated in sections [a] and [c], respectively, of Figure 21. This is similar to what has already been described for the DLL component. See DLL Clock Output and Feedback Connections, page 34.

In the on-chip case, it is possible to connect either of the DFS's two output clock signals through general routing resources to the FPGA's internal registers. Either a Global Clock Buffer (BUFG) or a BUFGMUX affords access to the global clock network. The optional feedback loop is formed in this way, routing CLK0 to a global clock net, which in turn drives the CLKFB input.

In the off-chip case, the DFS's two output clock signals, plus CLK0 for an optional feedback loop, can exit the FPGA using output buffers (OBUF) to drive a clock network plus registers on the board. The feedback loop is formed by feeding the CLK0 signal back into the FPGA using an IBUFG, which directly accesses the global clock network, or an IBUF. Then, the global clock net is connected directly to the CLKFB input.

# Phase Shifter (PS)

The DCM provides two approaches to controlling the phase of a DCM clock output signal relative to the CLKIN signal: First, there are nine clock outputs that employ the DLL to achieve a desired phase relationship: CLK0, CLK90, CLK180, CLK270, CLK2X, CLK2X180, CLKDV CLKFX, and CLKFX180. These outputs afford "coarse" phase control.

The second approach uses the PS component described in this section to provide a still finer degree of control. The PS component is only available when the DLL is operating in its low-frequency mode. The PS component phase shifts the DCM output clocks by introducing a "fine phase shift" ( $T_{PS}$ ) between the CLKFB and CLKIN signals inside the DLL component. The user can control this fine phase shift down to a resolution of 1/256 of a CLKIN cycle or one tap delay (DCM\_TAP), whichever is greater. When in use, the PS component shifts the phase of all nine DCM clock output signals together. If the PS component is used together with a DCM clock output such as the CLK90, CLK180, CLK270, CLK2X180 and CLKFX180, then the fine phase shift of the former gets added to the coarse phase shift of the latter.

# **PS Component Enabling and Mode Selection**

The CLKOUT\_PHASE\_SHIFT attribute enables the PS component for use in addition to selecting between two operating modes. As described in Table 20, this attribute has three possible values: NONE, FIXED and VARIABLE. When CLKOUT\_PHASE\_SHIFT is set to NONE, the PS component is disabled and its inputs, PSEN, PSCLK, and PSINCDEC, must be tied to GND. The set of waveforms in section [a] of Figure 22 shows the disabled case, where the DLL maintains a zero-phase alignment of signals CLKFB and CLKIN upon which the PS component has no effect. The PS component is enabled by setting the attribute to either the FIXED or VARIABLE values, which select the Fixed Phase mode and the Variable Phase mode, respectively. These two modes are described in the sections that follow

# **Determining the Fine Phase Shift**

The user controls the phase shift of CLKFB relative to CLKIN by setting and/or adjusting the value of the PHASE\_SHIFT attribute. This value must be an integer ranging from –255 to +255. The PS component uses this value to calculate the desired fine phase shift ( $T_{PS}$ ) as a fraction of the CLKIN period ( $T_{CLKIN}$ ). Given values for PHASE-SHIFT and  $T_{CLKIN}$ , it is possible to calculate  $T_{PS}$  as follows:

$$T_{PS} = T_{CLKIN}(PHASE_SHIFT/256)$$

Equation 4

Both the Fixed Phase and Variable Phase operating modes employ this calculation. If the PHASE\_SHIFT value is zero, then CLKFB and CLKIN will be in phase, the same as when the PS component is disabled. When the PHASE\_SHIFT value is positive, the CLKFB signal will be shifted later in time with respect to CLKIN. If the attribute value is negative, the CLKFB signal will be shifted earlier in time with respect to CLKIN.

# The Fixed Phase Mode

This mode fixes the desired fine phase shift to a fraction of the  $T_{CLKIN}$ , as determined by Equation 4 and its user-selected PHASE\_SHIFT value P. The set of waveforms insection [b] of Figure 22 illustrates the relationship between CLKFB and CLKIN in the Fixed Phase mode. In the Fixed Phase mode, the PSEN, PSCLK and PSINCDEC inputs are not used and must be tied to GND. Fixed phase shift requires ISE software version 10.1.03 or later.

(e.g. all configuration pins taken together) when operating in the User mode. This is accomplished by setting the *Persist* option to *Yes*.

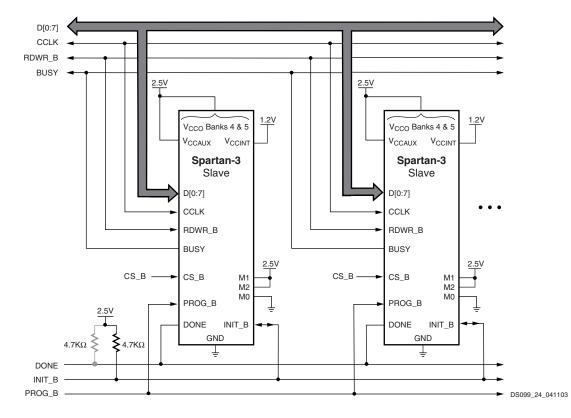

Multiple FPGAs can be configured using the Slave Parallel mode and can be made to start-up simultaneously. Figure 27 shows the device connections. To configure multiple devices in this way, wire the individual CCLK, Data, RDWR\_B, and BUSY pins of all the devices in parallel. The individual devices are loaded separately by deasserting the CS\_B pin of each device in turn and writing the appropriate data.

#### Notes:

- 1. There are two ways to use the DONE line. First, one may set the BitGen option DriveDone to "Yes" only for the last FPGA to be configured in the chain shown above (or for the single FPGA as may be the case). This enables the DONE pin to drive High; thus, no pull-up resistor is necessary. DriveDone is set to "No" for the remaining FPGAs in the chain. Second, DriveDone can be set to "No" for all FPGAs. Then all DONE lines are open-drain and require the pull-up resistor shown in grey. In most cases, a value between 3.3KΩ to 4.7KΩ is sufficient. However, when using DONE synchronously with a long chain of FPGAs, cumulative capacitance may necessitate lower resistor values (e.g. down to 330Ω) in order to ensure a rise time within one clock cycle.

- 2. If the FPGAs use different configuration data files, configure them in sequence by first asserting the CS\_B of one FPGA then asserting the CS\_B of the other FPGA.

- 3. For information on how to program the FPGA using 3.3V signals and power, see 3.3V-Tolerant Configuration Interface.

### Figure 27: Connection Diagram for Slave Parallel Configuration

#### Notes:

1. There are two ways to use the DONE line. First, one may set the BitGen option DriveDone to "Yes" only for the last FPGA to be configured in the chain shown above (or for the single FPGA as may be the case). This enables the DONE pin to drive High; thus, no pull-up resistor is necessary. DriveDone is set to "No" for the remaining FPGAs in the chain. Second, DriveDone can be set to "No" for all FPGAs. Then all DONE lines are open-drain and require the pull-up resistor shown in grey. In most cases, a value between  $3.3K\Omega$  to  $4.7K\Omega$  is sufficient. However, when using DONE synchronously with a long chain of FPGAs, cumulative capacitance may necessitate lower resistor values (e.g. down to  $330\Omega$ ) in order to ensure a rise time within one clock cycle.

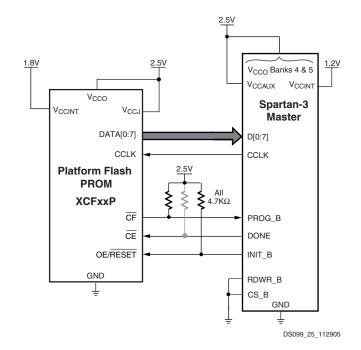

### Figure 28: Connection Diagram for Master Parallel Configuration

### **Master Parallel Mode**

In this mode, the FPGA configures from byte-wide data, and the FPGA supplies the CCLK configuration clock. In Master configuration modes, CCLK behaves as a bidirectional I/O pin. Timing is similar to the Slave Parallel mode except that CCLK is supplied by the FPGA. The device connections are shown in Figure 28.

### Boundary-Scan (JTAG) Mode

In Boundary-Scan mode, dedicated pins are used for configuring the FPGA. The configuration is done entirely through the IEEE 1149.1 Test Access Port (TAP). FPGA configuration using the Boundary-Scan mode is compatible with the IEEE Std 1149.1-1993 standard and IEEE Std 1532 for In-System Configurable (ISC) devices.

Configuration through the boundary-scan port is always available, regardless of the selected configuration mode. In some cases, however, the mode pin setting may affect proper programming of the device due to various interactions. For example, if the mode pins are set to Master Serial or Master Parallel mode, and the associated PROM is already programmed with a valid configuration image, then there is potential for configuration interference between the JTAG and PROM data. Selecting the Boundary-Scan mode disables the other modes and is the most reliable mode when programming via JTAG.

### **Configuration Sequence**

The configuration of Spartan-3 devices is a three-stage process that occurs after Power-On Reset or the assertion of PROG\_B. POR occurs after the  $V_{CCINT}$ ,  $V_{CCAUX}$ , and  $V_{CCO}$  Bank 4 supplies have reached their respective maximum input threshold levels (see Table 29, page 59). After POR, the three-stage process begins.

First, the configuration memory is cleared. Next, configuration data is loaded into the memory, and finally, the logic is activated by a start-up process. A flow diagram for the configuration sequence of the Serial and Parallel modes is shown in Figure 29. The flow diagram for the Boundary-Scan configuration sequence appears in Figure 30.

# **E** XILINX.

Initial Spartan-3 FPGA mask revisions have a limit on how fast the V<sub>CCO</sub> supply can ramp. The minimum allowed V<sub>CCO</sub> ramp rate appears as  $T_{CCO}$  in Table 30, page 60. The minimum rate is affected by the package inductance. Consequently, the ball grid array and chip-scale packages (CP132, FT256, FG456, FG676, and FG900) allow a faster ramp rate than the quad-flat packages (VQ100, TQ144, and PQ208).

# **Configuration Data Retention, Brown-Out**

The FPGA's configuration data is stored in robust CMOS configuration latches. The data in these latches is retained even when the voltages drop to the minimum levels necessary to preserve RAM contents. This is specified in Table 31, page 60.

If, after configuration, the  $V_{CCAUX}$  or  $V_{CCINT}$  supply drops below its data retention voltage, clear the current device configuration using one of the following methods:

- Force the V<sub>CCAUX</sub> or V<sub>CCINT</sub> supply voltage below the minimum Power On Reset (POR) voltage threshold Table 29, page 59).

- Assert PROG\_B Low.

The POR circuit does not monitor the VCCO\_4 supply after configuration. Consequently, dropping the VCCO\_4 voltage does not reset the device by triggering a Power-On Reset (POR) event.

# No Internal Charge Pumps or Free-Running Oscillators

Some system applications are sensitive to sources of analog noise. Spartan-3 FPGA circuitry is fully static and does not employ internal charge pumps.

The CCLK configuration clock is active during the FPGA configuration process. After configuration completes, the CCLK oscillator is automatically disabled unless the Bitstream Generator (BitGen) option *Persist=Yes*. See Module 4: Table 80, page 125.

Spartan-3 FPGAs optionally support a featured called Digitally Controlled Impedance (DCI). When used in an application, the DCI logic uses an internal oscillator. The DCI logic is only enabled if the FPGA application specifies an I/O standard that requires DCI (LVDCI\_33, LVDCI\_25, etc.). If DCI is not used, the associated internal oscillator is also disabled.

In summary, unless an application uses the *Persist=Yes* option or specifies a DCI I/O standard, an FPGA with no external switching remains fully static.

# Table 36: DC Characteristics of User I/Os Using Single-Ended Standards

| Signal Star                     | ndard                  | Test Co                 | nditions                | -                          | Characteristics            |  |  |

|---------------------------------|------------------------|-------------------------|-------------------------|----------------------------|----------------------------|--|--|

| (IOSTANDARD) a<br>Drive Attribu | ind Current<br>te (mA) | l <sub>OL</sub><br>(mA) | I <sub>ОН</sub><br>(mA) | V <sub>OL</sub><br>Max (V) | V <sub>OH</sub><br>Min (V) |  |  |

| GTL                             |                        | 32                      | -                       | 0.4                        | -                          |  |  |

| GTL_DCI                         |                        | Note 3                  | Note 3                  |                            |                            |  |  |

| GTLP                            |                        | 36                      | -                       | 0.6                        | -                          |  |  |

| GTLP_DCI                        |                        | Note 3                  | Note 3                  |                            |                            |  |  |

| HSLVDCI_15                      |                        | Note 3                  | Note 3                  | 0.4                        | V <sub>CCO</sub> – 0.4     |  |  |

| HSLVDCI_18                      |                        |                         |                         |                            |                            |  |  |

| HSLVDCI_25                      |                        |                         |                         |                            |                            |  |  |

| HSLVDCI_33                      |                        |                         |                         |                            |                            |  |  |

| HSTL_I                          |                        | 8                       | -8                      | 0.4                        | V <sub>CCO</sub> – 0.4     |  |  |

| HSTL_I_DCI                      |                        | Note 3                  | Note 3                  |                            |                            |  |  |

| HSTL_III                        |                        | 24                      | -8                      | 0.4                        | V <sub>CCO</sub> - 0.4     |  |  |

| HSTL_III_DCI                    |                        | Note 3                  | Note 3                  | 1                          |                            |  |  |

| HSTL_I_18                       |                        | 8                       | -8                      | 0.4                        | V <sub>CCO</sub> - 0.4     |  |  |

| HSTL_I_DCI_18                   |                        | Note 3                  | Note 3                  |                            |                            |  |  |

| HSTL_II_18                      |                        | 16                      | -16                     | 0.4                        | V <sub>CCO</sub> - 0.4     |  |  |

| HSTL_II_DCI_18                  |                        | Note 3                  | Note 3                  | -                          |                            |  |  |

| HSTL_III_18                     |                        | 24                      | 0.4                     | V <sub>CCO</sub> – 0.4     |                            |  |  |

| HSTL_III_DCI_18                 |                        | Note 3                  | Note 3                  | -                          |                            |  |  |

| LVCMOS12(4)                     | 2                      | 2                       | -2                      | 0.4                        | V <sub>CCO</sub> - 0.4     |  |  |

|                                 | 4                      | 4                       | -4                      | -                          |                            |  |  |

|                                 | 6                      | 6                       | -6                      | -                          |                            |  |  |

| LVCMOS15 <sup>(4)</sup>         | 2                      | 2                       | -2                      | 0.4                        | V <sub>CCO</sub> - 0.4     |  |  |

|                                 | 4                      | 4                       | -4                      | -                          | 000                        |  |  |

|                                 | 6                      | 6                       | -6                      | -                          |                            |  |  |

|                                 | 8                      | 8                       | -8                      | -                          |                            |  |  |

|                                 | 12                     | 12                      | -12                     | -                          |                            |  |  |

| LVDCI_15,<br>LVDCI_DV2_15       |                        | Note 3                  | Note 3                  | -                          |                            |  |  |

| LVCMOS18 <sup>(4)</sup>         | 2                      | 2                       | -2                      | 0.4                        | V <sub>CCO</sub> – 0.4     |  |  |

|                                 | 4                      | 4                       | -4                      | -                          |                            |  |  |

|                                 | 6                      | 6                       | -6                      | -                          |                            |  |  |

|                                 | 8                      | 8                       | -8                      | -                          |                            |  |  |

|                                 | 12                     | 12                      | -12                     | -                          |                            |  |  |

|                                 | 16                     | 16                      | -16                     | -                          |                            |  |  |

| LVDCI_18,<br>LVDCI_DV2_18       |                        | Note 3                  | Note 3                  |                            |                            |  |  |

| LVCMOS25 <sup>(4,5)</sup>       | 2                      | 2                       | -2                      | 0.4                        | V <sub>CCO</sub> – 0.4     |  |  |

|                                 | 4                      | 4                       | -4                      | 1                          |                            |  |  |

|                                 | 6                      | 6                       | -6                      | 1                          |                            |  |  |

|                                 | 8                      | 8                       | -8                      | -                          |                            |  |  |

|                                 | 12                     | 12                      | -12                     | -                          |                            |  |  |

|                                 | 16                     | 16                      | -16                     | =                          |                            |  |  |

|                                 | 24                     | 24                      | -24                     | -                          |                            |  |  |

| LVDCI_25,<br>LVDCI_DV2_25       |                        | Note 3                  | Note 3                  | -                          |                            |  |  |

### Table 42: Setup and Hold Times for the IOB Input Path (Cont'd)

|                      |                                                                                                       |                           |          | Speed |       |       |

|----------------------|-------------------------------------------------------------------------------------------------------|---------------------------|----------|-------|-------|-------|

| Symbol               | Description                                                                                           | Conditions                | Device   | -5    | -4    | Unite |

|                      |                                                                                                       |                           |          | Min   | Min   | 1     |

| Hold Times           |                                                                                                       |                           |          |       |       | 4     |

| T <sub>IOICKP</sub>  | Time from the active transition at the IFF's                                                          | LVCMOS25 <sup>(3)</sup> , | XC3S50   | -0.55 | -0.55 | ns    |

|                      | ICLK input to the point where data must be<br>held at the Input pin. No Input Delay is<br>programmed. | IOBDELAY = NONE           | XC3S200  | -0.29 | -0.29 | ns    |

|                      |                                                                                                       |                           | XC3S400  | -0.29 | -0.29 | ns    |

|                      |                                                                                                       |                           | XC3S1000 | -0.55 | -0.55 | ns    |

|                      |                                                                                                       |                           | XC3S1500 | -0.55 | -0.55 | ns    |

|                      |                                                                                                       |                           | XC3S2000 | -0.55 | -0.55 | ns    |

|                      |                                                                                                       |                           | XC3S4000 | -0.61 | -0.61 | ns    |

|                      |                                                                                                       |                           | XC3S5000 | -0.68 | -0.68 | ns    |

| T <sub>IOICKPD</sub> | Time from the active transition at the IFF's                                                          | LVCMOS25 <sup>(3)</sup> , | XC3S50   | -2.74 | -2.74 | ns    |

|                      | ICLK input to the point where data must be<br>held at the Input pin. The Input Delay is               | IOBDELAY = IFD            | XC3S200  | -3.00 | -3.00 | ns    |

|                      | programmed.                                                                                           |                           | XC3S400  | -2.90 | -2.90 | ns    |

|                      |                                                                                                       |                           | XC3S1000 | -3.24 | -3.24 | ns    |

|                      |                                                                                                       |                           | XC3S1500 | -3.55 | -3.55 | ns    |

|                      |                                                                                                       |                           | XC3S2000 | -4.57 | -4.57 | ns    |

|                      |                                                                                                       |                           | XC3S4000 | -4.96 | -4.96 | ns    |

|                      |                                                                                                       |                           | XC3S5000 | -5.09 | -5.09 | ns    |

| Set/Reset Puls       | e Width                                                                                               |                           |          |       |       |       |

| T <sub>RPW_IOB</sub> | Minimum pulse width to SR control input on IOB                                                        |                           | All      | 0.66  | 0.76  | ns    |

Notes:

1. The numbers in this table are tested using the methodology presented in Table 48 and are based on the operating conditions set forth in Table 32 and Table 35.

2. This setup time requires adjustment whenever a signal standard other than LVCMOS25 is assigned to the data Input. If this is true, add the appropriate Input adjustment from Table 44.

3. These hold times require adjustment whenever a signal standard other than LVCMOS25 is assigned to the data Input. If this is true, subtract the appropriate Input adjustment from Table 44. When the hold time is negative, it is possible to change the data before the clock's active edge.

## Table 44: Input Timing Adjustments for IOB (Cont'd)

|                                                                                   | Add the Adju | stment Below |       |

|-----------------------------------------------------------------------------------|--------------|--------------|-------|

| Convert Input Time from LVCMOS25 to the<br>Following Signal Standard (IOSTANDARD) | Speed        | I Grade      | Units |

|                                                                                   | -5           | -4           |       |

| LVCMOS15                                                                          | 0.42         | 0.49         | ns    |

| LVDCI_15                                                                          | 0.38         | 0.43         | ns    |

| LVDCI_DV2_15                                                                      | 0.38         | 0.44         | ns    |

| LVCMOS18                                                                          | 0.24         | 0.28         | ns    |

| LVDCI_18                                                                          | 0.29         | 0.33         | ns    |

| LVDCI_DV2_18                                                                      | 0.28         | 0.33         | ns    |

| LVCMOS25                                                                          | 0            | 0            | ns    |

| LVDCI_25                                                                          | 0.05         | 0.05         | ns    |

| LVDCI_DV2_25                                                                      | 0.04         | 0.04         | ns    |

| LVCMOS33, LVDCI_33, LVDCI_DV2_33                                                  | -0.05        | -0.02        | ns    |

| LVTTL                                                                             | 0.18         | 0.21         | ns    |

| PCI33_3                                                                           | 0.20         | 0.22         | ns    |

| SSTL18_I, SSTL18_I_DCI                                                            | 0.39         | 0.45         | ns    |

| SSTL18_II                                                                         | 0.39         | 0.45         | ns    |

| SSTL2_I, SSTL2_I_DCI                                                              | 0.40         | 0.46         | ns    |

| SSTL2_II, SSTL2_II_DCI                                                            | 0.36         | 0.41         | ns    |

| Differential Standards                                                            |              | 1 1          |       |

| LDT_25 (ULVDS_25)                                                                 | 0.76         | 0.88         | ns    |

| LVDS_25, LVDS_25_DCI                                                              | 0.65         | 0.75         | ns    |

| BLVDS_25                                                                          | 0.34         | 0.39         | ns    |

| LVDSEXT_25, LVDSEXT_25_DCI                                                        | 0.80         | 0.92         | ns    |

| LVPECL_25                                                                         | 0.18         | 0.21         | ns    |

| RSDS_25                                                                           | 0.43         | 0.50         | ns    |

| DIFF_HSTL_II_18, DIFF_HSTL_II_18_DCI                                              | 0.34         | 0.39         | ns    |

| DIFF_SSTL2_II, DIFF_SSTL2_II_DCI                                                  | 0.65         | 0.75         | ns    |

#### Notes:

1. The numbers in this table are tested using the methodology presented in Table 48 and are based on the operating conditions set forth in Table 32, Table 35, and Table 37.

2. These adjustments are used to convert input path times originally specified for the LVCMOS25 standard to times that correspond to other signal standards.

# Timing Measurement Methodology

When measuring timing parameters at the programmable I/Os, different signal standards call for different test conditions. Table 48 presents the conditions to use for each standard.

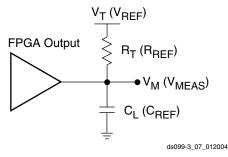

The method for measuring Input timing is as follows: A signal that swings between a Low logic level of  $V_L$  and a High logic level of  $V_H$  is applied to the Input under test. Some standards also require the application of a bias voltage to the  $V_{REF}$  pins of a given bank to properly set the input-switching threshold. The measurement point of the Input signal ( $V_M$ ) is commonly located halfway between  $V_L$  and  $V_H$ .

The Output test setup is shown in Figure 35. A termination voltage  $V_T$  is applied to the termination resistor  $R_T$ , the other end of which is connected to the Output. For each standard,  $R_T$  and  $V_T$  generally take on the standard values recommended for minimizing signal reflections. If the standard does not ordinarily use terminations (e.g., LVCMOS, LVTTL), then  $R_T$  is set to 1M $\Omega$  to indicate an open connection, and  $V_T$  is set to zero. The same measurement point ( $V_M$ ) that was used at the Input is also used at the Output.

Notes:

1. The names shown in parentheses are used in the IBIS file.

Figure 35: Output Test Setup

| Signal Standard |                      | Inputs                 |                        | Out                       | Inputs and<br>Outputs     |                           |  |

|-----------------|----------------------|------------------------|------------------------|---------------------------|---------------------------|---------------------------|--|

| (IOSTANDARD)    | V <sub>REF</sub> (V) | V <sub>L</sub> (V)     | V <sub>H</sub> (V)     | <b>R</b> <sub>T</sub> (Ω) | <b>V</b> <sub>T</sub> (V) | <b>V</b> <sub>M</sub> (V) |  |

| Single-Ended    |                      |                        |                        |                           |                           |                           |  |

| GTL             | 0.8                  | V <sub>REF</sub> – 0.2 | V <sub>REF</sub> + 0.2 | 25                        | 1.2                       | V <sub>REF</sub>          |  |

| GTL_DCI         |                      |                        |                        | 50                        | 1.2                       |                           |  |

| GTLP            | 1.0                  | V <sub>REF</sub> – 0.2 | V <sub>REF</sub> + 0.2 | 25                        | 1.5                       | V <sub>REF</sub>          |  |

| GTLP_DCI        |                      |                        |                        | 50                        | 1.5                       |                           |  |

| HSLVDCI_15      | 0.9                  | V <sub>REF</sub> – 0.5 | V <sub>REF</sub> + 0.5 | 1M                        | 0                         | 0.75                      |  |

| HSLVDCI_18      |                      |                        |                        |                           |                           | 0.90                      |  |

| HSLVDCI_25      |                      |                        |                        |                           |                           | 1.25                      |  |

| HSLVDCI_33      |                      |                        |                        |                           |                           | 1.65                      |  |

| HSTL_I          | 0.75                 | V <sub>REF</sub> – 0.5 | V <sub>REF</sub> + 0.5 | 50                        | 0.75                      | V <sub>REF</sub>          |  |

| HSTL_I_DCI      |                      |                        |                        |                           |                           |                           |  |

| HSTL_III        | 0.90                 | V <sub>REF</sub> – 0.5 | V <sub>REF</sub> + 0.5 | 50                        | 1.5                       | V <sub>REF</sub>          |  |

| HSTL_III_DCI    |                      |                        |                        |                           |                           |                           |  |

| HSTL_I_18       | 0.90                 | V <sub>REF</sub> – 0.5 | V <sub>REF</sub> + 0.5 | 50                        | 0.9                       | V <sub>REF</sub>          |  |

| HSTL_I_DCI_18   |                      |                        |                        |                           |                           |                           |  |

| HSTL_II_18      | 0.90                 | V <sub>REF</sub> – 0.5 | V <sub>REF</sub> + 0.5 | 50                        | 0.9                       | V <sub>REF</sub>          |  |

| HSTL_II_DCI_18  |                      |                        |                        |                           |                           |                           |  |

### Table 59: Switching Characteristics for the DLL (Cont'd)

|             |                                                           |                                                               |        | Speed Grade |      |      |      |       |

|-------------|-----------------------------------------------------------|---------------------------------------------------------------|--------|-------------|------|------|------|-------|

| Symbol      | Description                                               | Frequency Mode /<br>FCLKIN Range                              | Device | -5          |      | -4   |      | Units |

|             |                                                           | i o Litit i nango                                             |        | Min         | Max  | Min  | Max  |       |

| Lock Time   |                                                           |                                                               |        |             |      |      |      |       |

| LOCK_DLL    | When using the DLL alone:                                 | 18 MHz $\leq$ F <sub>CLKIN</sub> $\leq$ 30 MHz                | All    | -           | 2.88 | -    | 2.88 | ms    |

|             | The time from deassertion at the DCM's Reset input to the | $30 \text{ MHz} < \text{F}_{\text{CLKIN}} \le 40 \text{ MHz}$ |        | -           | 2.16 | -    | 2.16 | ms    |

|             | rising transition at its LOCKED output. When the          | 40 MHz < $F_{CLKIN} \le 50$ MHz                               |        | -           | 1.20 | -    | 1.20 | ms    |

|             | DCM is locked, the CLKIN and                              | 50 MHz < $F_{CLKIN} \le$ 60 MHz                               |        | -           | 0.60 | -    | 0.60 | ms    |

|             | CLKFB signals are in phase                                | F <sub>CLKIN</sub> > 60 MHz                                   |        | -           | 0.48 | -    | 0.48 | ms    |

| Delay Lines |                                                           |                                                               |        |             |      |      |      |       |

| DCM_TAP     | Delay tap resolution                                      | All                                                           | All    | 30.0        | 60.0 | 30.0 | 60.0 | ps    |

#### Notes:

- 1. The numbers in this table are based on the operating conditions set forth in Table 32 and Table 58.

- 2. DLL specifications apply when any of the DLL outputs (CLK0, CLK90, CLK180, CLK270, CLK2X, CLK2X180, or CLKDV) are in use.

- Only mask revision 'E' and later devices (see Mask and Fab Revisions, page 58) and all revisions of the XC3S50 and the XC3S1000 support DLL feedback using the CLK2X output. For all other Spartan-3 devices, use feedback from the CLK0 output (instead of the CLK2X output) and set the CLK\_FEEDBACK attribute to 1X.

- 4. Indicates the maximum amount of output jitter that the DCM adds to the jitter on the CLKIN input.

- 5. This specification only applies if the attribute DUTY\_CYCLE\_CORRECTION = TRUE.

### **Digital Frequency Synthesizer (DFS)**

### Table 60: Recommended Operating Conditions for the DFS

|                      | Symbol                            | Description                        | Frequency<br>Mode | -   | 5    | -4  |      | Units |

|----------------------|-----------------------------------|------------------------------------|-------------------|-----|------|-----|------|-------|

|                      |                                   |                                    |                   | Min | Max  | Min | Max  |       |

| Input Freq           | uency Ranges <sup>(2)</sup>       |                                    |                   |     |      |     |      |       |

| F <sub>CLKIN</sub>   | CLKIN_FREQ_FX                     | Frequency for the CLKIN input      | All               | 1   | 280  | 1   | 280  | MHz   |

| Input Cloc           | k Jitter Tolerance <sup>(3)</sup> |                                    |                   |     |      |     |      |       |

| CLKIN_CY             | C_JITT_FX_LF                      | Cycle-to-cycle jitter at the CLKIN | Low               | _   | ±300 | _   | ±300 | ps    |

| CLKIN_CYC_JITT_FX_HF |                                   | input                              | High              | -   | ±150 | _   | ±150 | ps    |

| CLKIN_PER_JITT_FX    |                                   | Period jitter at the CLKIN input   | All               | _   | ±1   | -   | ±1   | ns    |

#### Notes:

1. DFS specifications apply when either of the DFS outputs (CLKFX or CLKFX180) are used.

2. If both DFS and DLL outputs are used on the same DCM, follow the more restrictive CLKIN\_FREQ\_DLL specifications in Table 58.

3. CLKIN input jitter beyond these limits may cause the DCM to lose lock.

| Pin Name | Direction                     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DIN      | Input                         | Serial Data Input:<br>During the Master or Slave Serial configuration modes, DIN is the serial configuration data input, and<br>all data is synchronized to the rising CCLK edge. After configuration, this pin is available as a user I/O.<br>This signal is located in Bank 4 and its output voltage determined by VCCO_4.<br>The BitGen option <i>Persist</i> permits this pin to retain its configuration function in the User mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| DOUT     | Output                        | Serial Data Output:<br>In a multi-FPGA design where all the FPGAs use serial mode, connect the DOUT output of one<br>FPGA—in either Master or Slave Serial mode—to the DIN input of the next FPGA—in Slave Serial<br>mode—so that configuration data passes from one to the next, in daisy-chain fashion. This "daisy<br>chain" permits sequential configuration of multiple FPGAs.<br>This signal is located in Bank 4 and its output voltage determined by VCCO_4.<br>The BitGen option <i>Persist</i> permits this pin to retain its configuration function in the User mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| INIT_B   | Bidirectional<br>(open-drain) | Initializing Configuration Memory/Configuration Error:<br>Just after power is applied, the FPGA produces a Low-to-High transition on this pin indicating that<br>initialization ( <i>i.e.</i> , clearing) of the configuration memory has finished. Before entering the User mode,<br>this pin functions as an open-drain output, which requires a pull-up resistor in order to produce a High<br>logic level. In a multi-FPGA design, tie (wire AND) the INIT_B pins from all FPGAs together so that the<br>common node transitions High only after all of the FPGAs have been successfully initialized.<br>Externally holding this pin Low beyond the initialization phase delays the start of configuration. This<br>action stalls the FPGA at the configuration step just before the mode select pins are sampled.<br>During configuration, the FPGA indicates the occurrence of a data (i.e., CRC) error by asserting<br>INIT_B Low.<br>This signal is located in Bank 4 and its output voltage determined by VCCO_4.<br>The BitGen option <i>Persist</i> permits this pin to retain its configuration function in the User mode. |

### Table 71: Dual-Purpose Pins Used in Master or Slave Serial Mode

## Parallel Configuration Modes (SelectMAP)

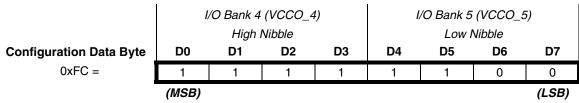

This section describes the dual-purpose configuration pins used during the Master and Slave Parallel configuration modes, sometimes also called the SelectMAP modes. In both Master and Slave Parallel configuration modes, D0-D7 form the byte-wide configuration data input. See Table 75 for Mode Select pin settings required for Parallel modes.

As shown in Figure 41, D0 is the most-significant bit while D7 is the least-significant bit. Bits D0-D3 form the high nibble of the byte and bits D4-D7 form the low nibble.

In the Parallel configuration modes, both the VCCO\_4 and VCCO\_5 voltage supplies are required and must both equal the voltage of the attached configuration device, typically either 2.5V or 3.3V.

Assert Low both the chip-select pin, CS\_B, and the read/write control pin, RDWR\_B, to write the configuration data byte presented on the D0-D7 pins to the FPGA on a rising-edge of the configuration clock, CCLK. The order of CS\_B and RDWR\_B does not matter, although RDWR\_B must be asserted throughout the configuration process. If RDWR\_B is de-asserted during configuration, the FPGA aborts the configuration operation.

After configuration, these pins are available as general-purpose user I/O. However, the SelectMAP configuration interface is optionally available for debugging and dynamic reconfiguration. To use these SelectMAP pins after configuration, set the Persist bitstream generation option.

The Readback debugging option, for example, requires the Persist bitstream generation option. During Readback mode, assert CS\_B Low, along with RDWR\_B High, to read a configuration data byte from the FPGA to the D0-D7 bus on a rising CCLK edge. During Readback mode, D0-D7 are output pins.

In all the cases, the configuration data and control signals are synchronized to the rising edge of the CCLK clock signal.

## HSWAP\_EN: Disable Pull-up Resistors During Configuration

As shown in Table 76, a Low on this asynchronous pin enables pull-up resistors on all user I/Os not actively involved in the configuration process, although only until device configuration completes. A High disables the pull-up resistors during configuration, which is the desired state for some applications.

The dedicated configuration CONFIG pins (CCLK, DONE, PROG\_B, HSWAP\_EN, M2, M1, M0), the JTAG pins (TDI, TMS, TCK, TDO) and the INIT\_B always have active pull-up resistors during configuration, regardless of the value on HSWAP\_EN.

After configuration, HSWAP\_EN becomes a "don't care" input and any pull-up resistors previously enabled by HSWAP\_EN are disabled. If a user I/O in the application requires a pull-up resistor after configuration, place a PULLUP primitive on the associated I/O pin or, for some pins, set the associated bitstream generator option.

### Table 76: HSWAP\_EN Encoding

| HSWAP_EN       | Function                                                                                                                                                       |  |  |  |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| During Config  | During Configuration                                                                                                                                           |  |  |  |

| 0              | Enable pull-up resistors on all pins not actively involved in the configuration process. Pull-ups are only active until configuration completes. See Table 79. |  |  |  |

| 1              | No pull-up resistors during configuration.                                                                                                                     |  |  |  |

| After Configur | ation, User Mode                                                                                                                                               |  |  |  |

| Х              | This pin has no function except during device configuration.                                                                                                   |  |  |  |

#### Notes:

1. X =don't care, either 0 or 1.

The Bitstream generator option HswapenPin determines whether a pull-up resistor to VCCAUX, a pull-down resistor, or no resistor is present on HSWAP\_EN after configuration.

## **JTAG: Dedicated JTAG Port Pins**

### Table 77: JTAG Pin Descriptions

| Pin Name | Direction | Description                                                                                                                                                                                                                                                                              | Bitstream Generation Option                                                                                                |

|----------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| ТСК      | Input     | <b>Test Clock:</b> The TCK clock signal synchronizes all boundary scan operations on its rising edge.                                                                                                                                                                                    | The BitGen option <b>TckPin</b> determines whether a pull-up resistor, pull-down resistor or no resistor is present.       |

| TDI      | Input     | <b>Test Data Input:</b> TDI is the serial data input for all JTAG instruction and data registers. This input is sampled on the rising edge of TCK.                                                                                                                                       | The BitGen option <b>TdiPin</b> determines<br>whether a pull-up resistor, pull-down<br>resistor or no resistor is present. |

| TMS      | Input     | <b>Test Mode Select:</b> The TMS input controls the sequence of states through which the JTAG TAP state machine passes. This input is sampled on the rising edge of TCK.                                                                                                                 | The BitGen option <b>TmsPin</b> determines whether a pull-up resistor, pull-down resistor or no resistor is present.       |

| TDO      | Output    | <b>Test Data Output:</b> The TDO pin is the data output for all JTAG instruction and data registers. This output is sampled on the rising edge of TCK. The TDO output is an active totem-pole driver and is not like the open-collector TDO output on Virtex <sup>®</sup> -II Pro FPGAs. | The BitGen option <b>TdoPin</b> determines<br>whether a pull-up resistor, pull-down<br>resistor or no resistor is present. |

These pins are dedicated connections to the four-wire IEEE 1532/IEEE 1149.1 JTAG port, shown in Figure 43 and described in Table 77. The JTAG port is used for boundary-scan testing, device configuration, application debugging, and possibly an additional serial port for the application. These pins are dedicated and are not available as user-I/O pins. Every package has four dedicated JTAG pins and these pins are powered by the +2.5V VCCAUX supply.

For additional information on JTAG configuration, see Boundary-Scan (JTAG) Mode, page 50.

### Table 86: Spartan-3 FPGA Package Thermal Characteristics (Cont'd)

| Package                  |          | Junction-to-           | Junction-to-B           | Junction-to-A        | Ambient ( <sub>8J4</sub> | ) at Differen | t Air Flows |         |

|--------------------------|----------|------------------------|-------------------------|----------------------|--------------------------|---------------|-------------|---------|

|                          | Device   | Case ( $\theta_{JC}$ ) | oard (θ <sub>JB</sub> ) | Still Air<br>(0 LFM) | 250 LFM                  | 500 LFM       | 750 LFM     | Units   |

| FG(G)1156 <sup>(1)</sup> | XC3S4000 | 1.9                    | -                       | 14.7                 | 11.4                     | 10.1          | 9.0         | °C/Watt |

| FG(G)1150(9)             | XC3S5000 | 1.9                    | 8.9                     | 14.5                 | 11.3                     | 10.0          | 8.9         | °C/Watt |

#### Notes:

1. The CP132, CPG132, FG1156, and FGG1156 packages are discontinued. See http://www.xilinx.com/support/documentation/spartan-3\_customer\_notices.htm.

# VQ100: 100-lead Very-Thin Quad Flat Package

The XC3S50 and the XC3S200 devices are available in the 100-lead very-thin quad flat package, VQ100. Both devices share a common footprint for this package as shown in Table 87 and Figure 44.

All the package pins appear in Table 87 and are sorted by bank number, then by pin name. Pairs of pins that form a differential I/O pair appear together in the table. The table also shows the pin number for each pin and the pin type, as defined earlier.

An electronic version of this package pinout table and footprint diagram is available for download from the Xilinx website at <a href="http://www.xilinx.com/support/documentation/data\_sheets/s3\_pin.zip">http://www.xilinx.com/support/documentation/data\_sheets/s3\_pin.zip</a>.

## **Pinout Table**

### Table 87: VQ100 Package Pinout

| Bank | XC3S50<br>XC3S200<br>Pin Name | VQ100<br>Pin<br>Number | Туре |

|------|-------------------------------|------------------------|------|

| 0    | IO_L01N_0/VRP_0               | P97                    | DCI  |

| 0    | IO_L01P_0/VRN_0               | P96                    | DCI  |

| 0    | IO_L31N_0                     | P92                    | I/O  |

| 0    | IO_L31P_0/VREF_0              | P91                    | VREF |

| 0    | IO_L32N_0/GCLK7               | P90                    | GCLK |

| 0    | IO_L32P_0/GCLK6               | P89                    | GCLK |

| 0    | VCCO_0                        | P94                    | VCCO |

| 1    | 10                            | P81                    | I/O  |

| 1    | IO_L01N_1/VRP_1               | P80                    | DCI  |

| 1    | IO_L01P_1/VRN_1               | P79                    | DCI  |

| 1    | IO_L31N_1/VREF_1              | P86                    | VREF |

| 1    | IO_L31P_1                     | P85                    | I/O  |

| 1    | IO_L32N_1/GCLK5               | P88                    | GCLK |

| 1    | IO_L32P_1/GCLK4               | P87                    | GCLK |

| 1    | VCCO_1                        | P83                    | VCCO |

| 2    | IO_L01N_2/VRP_2               | P75                    | DCI  |

| 2    | IO_L01P_2/VRN_2               | P74                    | DCI  |

| 2    | IO_L21N_2                     | P72                    | I/O  |

| 2    | IO_L21P_2                     | P71                    | I/O  |

| 2    | IO_L24N_2                     | P68                    | I/O  |

| 2    | 2 IO_L24P_2                   |                        | I/O  |

www.xilinx.com

# Table 91: TQ144 Package Pinout (Cont'd)

| Bank | XC3S50, XC3S200,<br>XC3S400 Pin Name | TQ144 Pin<br>Number | Туре |

|------|--------------------------------------|---------------------|------|

| 5    | IO_L32P_5/GCLK2                      | P52                 | GCLK |

| 6    | IO_L01N_6/VRP_6                      | P36                 | DCI  |

| 6    | IO_L01P_6/VRN_6                      | P35                 | DCI  |

| 6    | IO_L20N_6                            | P33                 | I/O  |

| 6    | IO_L20P_6                            | P32                 | I/O  |

| 6    | IO_L21N_6                            | P31                 | I/O  |

| 6    | IO_L21P_6                            | P30                 | I/O  |

| 6    | IO_L22N_6                            | P28                 | I/O  |

| 6    | IO_L22P_6                            | P27                 | I/O  |

| 6    | IO_L23N_6                            | P26                 | I/O  |

| 6    | IO_L23P_6                            | P25                 | I/O  |

| 6    | IO_L24N_6/VREF_6                     | P24                 | VREF |

| 6    | IO_L24P_6                            | P23                 | I/O  |

| 6    | IO_L40N_6                            | P21                 | I/O  |

| 6    | IO_L40P_6/VREF_6                     | P20                 | VREF |

| 7    | IO/VREF_7                            | P4                  | VREF |

| 7    | IO_L01N_7/VRP_7                      | P2                  | DCI  |

| 7    | IO_L01P_7/VRN_7                      | P1                  | DCI  |

| 7    | IO_L20N_7                            | P6                  | I/O  |

| 7    | IO_L20P_7                            | P5                  | I/O  |

| 7    | IO_L21N_7                            | P8                  | I/O  |

| 7    | IO_L21P_7                            | P7                  | I/O  |

| 7    | IO_L22N_7                            | P11                 | I/O  |

| 7    | IO_L22P_7                            | P10                 | I/O  |

| 7    | IO_L23N_7                            | P13                 | I/O  |

| 7    | IO_L23P_7                            | P12                 | I/O  |

| 7    | IO_L24N_7                            | P15                 | I/O  |

| 7    | IO_L24P_7                            | P14                 | I/O  |

| 7    | IO_L40N_7/VREF_7                     | P18                 | VREF |

| 7    | IO_L40P_7                            | P17                 | I/O  |

| 0,1  | VCCO_TOP                             | P126                | VCCO |

| 0,1  | VCCO_TOP                             | P138                | VCCO |

| 0,1  | VCCO_TOP                             | P115                | VCCO |

| 2,3  | VCCO_RIGHT                           | P106                | VCCO |

| 2,3  | VCCO_RIGHT                           | P75                 | VCCO |

| 2,3  | VCCO_RIGHT                           | P91                 | VCCO |

| 4,5  | VCCO_BOTTOM                          | P54                 | VCCO |