Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                               |

|--------------------------------|---------------------------------------------------------------|

| Product Status                 | Active                                                        |

| Number of LABs/CLBs            | 5120                                                          |

| Number of Logic Elements/Cells | 46080                                                         |

| Total RAM Bits                 | 737280                                                        |

| Number of I/O                  | 489                                                           |

| Number of Gates                | 2000000                                                       |

| Voltage - Supply               | 1.14V ~ 1.26V                                                 |

| Mounting Type                  | Surface Mount                                                 |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                            |

| Package / Case                 | 676-BGA                                                       |

| Supplier Device Package        | 676-FBGA (27x27)                                              |

| Purchase URL                   | https://www.e-xfl.com/product-detail/xilinx/xc3s2000-4fgg676i |

|                                |                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### Table 8: Single-Ended I/O Standards

| Signal Standard | V <sub>cco</sub> | (Volts)    | V <sub>REF</sub> for Inputs                           | Board Termination<br>Voltage (V <sub>TT</sub> ) in Volts |  |

|-----------------|------------------|------------|-------------------------------------------------------|----------------------------------------------------------|--|

| (IOSTANDARD)    | For Outputs      | For Inputs | V <sub>REF</sub> for Inputs<br>(Volts) <sup>(1)</sup> |                                                          |  |

| GTL             | Note 2           | Note 2     | 0.8                                                   | 1.2                                                      |  |

| GTLP            | Note 2           | Note 2     | 1                                                     | 1.5                                                      |  |

| HSTL_I          | 1.5              | -          | 0.75                                                  | 0.75                                                     |  |

| HSTL_III        | 1.5              | _          | 0.9                                                   | 1.5                                                      |  |

| HSTL_I_18       | 1.8              | -          | 0.9                                                   | 0.9                                                      |  |

| HSTL_II_18      | 1.8              | -          | 0.9                                                   | 0.9                                                      |  |

| HSTL_III_18     | 1.8              | -          | 1.1                                                   | 1.8                                                      |  |

| LVCMOS12        | 1.2              | 1.2        | -                                                     | -                                                        |  |

| LVCMOS15        | 1.5              | 1.5        | -                                                     | -                                                        |  |

| LVCMOS18        | 1.8              | 1.8        | -                                                     | -                                                        |  |

| LVCMOS25        | 2.5              | 2.5        | -                                                     | -                                                        |  |

| LVCMOS33        | 3.3              | 3.3        | -                                                     | -                                                        |  |

| LVTTL           | 3.3              | 3.3        | -                                                     | -                                                        |  |

| PCI33_3         | 3.0              | 3.0        | -                                                     | -                                                        |  |

| SSTL18_I        | 1.8              | -          | 0.9                                                   | 0.9                                                      |  |

| SSTL18_II       | 1.8              | -          | 0.9                                                   | 0.9                                                      |  |

| SSTL2_I         | 2.5              | -          | 1.25                                                  | 1.25                                                     |  |

| SSTL2_II        | 2.5              | -          | 1.25                                                  | 1.25                                                     |  |

#### Notes:

1. Banks 4 and 5 of any Spartan-3 device in a VQ100 package do not support signal standards using V<sub>REF</sub>

2. The V<sub>CCO</sub> level used for the GTL and GTLP standards must be no lower than the termination voltage (V<sub>TT</sub>), nor can it be lower than the voltage at the I/O pad.

3. See Table 10 for a listing of the single-ended DCI standards.

Differential standards employ a pair of signals, one the opposite polarity of the other. The noise canceling (e.g., Common-Mode Rejection) properties of these standards permit exceptionally high data transfer rates. This section introduces the differential signaling capabilities of Spartan-3 devices.

Each device-package combination designates specific I/O pairs that are specially optimized to support differential standards. A unique "L-number", part of the pin name, identifies the line-pairs associated with each bank (see Figure 40, page 112). For each pair, the letters 'P' and 'N' designate the true and inverted lines, respectively. For example, the pin names IO\_L43P\_7 and IO\_L43N\_7 indicate the true and inverted lines comprising the line pair L43 on Bank 7. The V<sub>CCO</sub> lines provide current to the outputs. The V<sub>CCAUX</sub> lines supply power to the differential inputs, making them independent of the V<sub>CCO</sub> voltage for an I/O bank. The V<sub>REF</sub> lines are not used. Select the V<sub>CCO</sub> level to suit the desired differential standard according to Table 9.

# Supply Voltages for the IOBs

Three different supplies power the IOBs:

- The V<sub>CCO</sub> supplies, one for each of the FPGA's I/O banks, power the output drivers, except when using the GTL and GTLP signal standards. The voltage on the V<sub>CCO</sub> pins determines the voltage swing of the output signal.

- V<sub>CCINT</sub> is the main power supply for the FPGA's internal logic.

- The V<sub>CCAUX</sub> is an auxiliary source of power, primarily to optimize the performance of various FPGA functions such as I/O switching.

# The I/Os During Power-On, Configuration, and User Mode

With no power applied to the FPGA, all I/Os are in a high-impedance state. The  $V_{CCINT}$  (1.2V),  $V_{CCAUX}$  (2.5V), and  $V_{CCO}$  supplies may be applied in any order. Before power-on can finish,  $V_{CCINT}$ ,  $V_{CCO}$  Bank 4, and  $V_{CCAUX}$  must have reached their respective minimum recommended operating levels (see Table 29, page 59). At this time, all I/O drivers also will be in a high-impedance state.  $V_{CCO}$  Bank 4,  $V_{CCINT}$ , and  $V_{CCAUX}$  serve as inputs to the internal Power-On Reset circuit (POR).

A Low level applied to the HSWAP\_EN input enables pull-up resistors on User I/Os from power-on throughout configuration. A High level on HSWAP\_EN disables the pull-up resistors, allowing the I/Os to float. If the HSWAP\_EN pin is floating, then an internal pull-up resistor pulls HSWAP\_EN High. As soon as power is applied, the FPGA begins initializing its configuration memory. At the same time, the FPGA internally asserts the Global Set-Reset (GSR), which asynchronously resets all IOB storage elements to a Low state.

Upon the completion of initialization, INIT\_B goes High, sampling the M0, M1, and M2 inputs to determine the configuration mode. At this point, the configuration data is loaded into the FPGA. The I/O drivers remain in a high-impedance state (with or without pull-up resistors, as determined by the HSWAP\_EN input) throughout configuration.

The Global Three State (GTS) net is released during Start-Up, marking the end of configuration and the beginning of design operation in the User mode. At this point, those I/Os to which signals have been assigned go active while all unused I/Os remain in a high-impedance state. The release of the GSR net, also part of Start-up, leaves the IOB registers in a Low state by default, unless the loaded design reverses the polarity of their respective RS inputs.

In User mode, all internal pull-up resistors on the I/Os are disabled and HSWAP\_EN becomes a "don't care" input. If it is desirable to have pull-up or pull-down resistors on I/Os carrying signals, the appropriate symbol—e.g., PULLUP, PULLDOWN—must be placed at the appropriate pads in the design. The Bitstream Generator (Bitgen) option UnusedPin available in the Xilinx development software determines whether unused I/Os collectively have pull-up resistors, pull-down resistors, or no resistors in User mode.

# **CLB** Overview

For more details on the CLBs, refer to the chapter entitled "Using Configurable Logic Blocks" in UG331.

The Configurable Logic Blocks (CLBs) constitute the main logic resource for implementing synchronous as well as combinatorial circuits. Each CLB comprises four interconnected slices, as shown in Figure 11. These slices are grouped in pairs. Each pair is organized as a column with an independent carry chain.

The nomenclature that the FPGA Editor—part of the Xilinx development software—uses to designate slices is as follows: The letter 'X' followed by a number identifies columns of slices. The 'X' number counts up in sequence from the left side of the die to the right. The letter 'Y' followed by a number identifies the position of each slice in a pair as well as indicating the CLB row. The 'Y' number counts slices starting from the bottom of the die according to the sequence: 0, 1, 0, 1 (the first CLB row); 2, 3, 2, 3 (the second CLB row); etc. Figure 11 shows the CLB located in the lower left-hand corner of the die. Slices X0Y0 and X0Y1 make up the column-pair on the left where as slices X1Y0 and X1Y1 make up the column-pair on the right. For each CLB, the term "left-hand" (or SLICEM) indicates the pair of slices labeled with an even 'X' number, such as X0, and the term "right-hand" (or SLICEL) designates the pair of slices with an odd 'X' number, e.g., X1.

# **Function Generator**

Each of the two LUTs (F and G) in a slice have four logic inputs (A1-A4) and a single output (D). This permits any four-variable Boolean logic operation to be programmed into them. Furthermore, wide function multiplexers can be used to effectively combine LUTs within the same CLB or across different CLBs, making logic functions with still more input variables possible.

The LUTs in both the right-hand and left-hand slice-pairs not only support the logic functions described above, but also can function as ROM that is initialized with data at the time of configuration.

The LUTs in the left-hand slice-pair (even-numbered columns such as X0 in Figure 11) of each CLB support two additional functions that the right-hand slice-pair (odd-numbered columns such as X1) do not.

First, it is possible to program the "left-hand LUTs" as distributed RAM. This type of memory affords moderate amounts of data buffering anywhere along a data path. One left-hand LUT stores 16 bits. Multiple left-hand LUTs can be combined in various ways to store larger amounts of data. A dual port option combines two LUTs so that memory access is possible from two independent data lines. A Distributed ROM option permits pre-loading the memory with data during FPGA configuration.

Second, it is possible to program each left-hand LUT as a 16-bit shift register. Used in this way, each LUT can delay serial data anywhere from one to 16 clock cycles. The four left-hand LUTs of a single CLB can be combined to produce delays up to 64 clock cycles. The SHIFTIN and SHIFTOUT lines cascade LUTs to form larger shift registers. It is also possible to combine shift registers across more than one CLB. The resulting programmable delays can be used to balance the timing of data pipelines.

# **Block RAM Overview**

All Spartan-3 devices support block RAM, which is organized as configurable, synchronous 18Kbit blocks. Block RAM stores relatively large amounts of data more efficiently than the distributed RAM feature described earlier. (The latter is better suited for buffering small amounts of data anywhere along signal paths.) This section describes basic Block RAM functions. For more information, refer to the chapter entitled "Using Block RAM" in <u>UG331</u>.

The aspect ratio—i.e., width vs. depth—of each block RAM is configurable. Furthermore, multiple blocks can be cascaded to create still wider and/or deeper memories.

A choice among primitives determines whether the block RAM functions as dual- or single-port memory. A name of the form RAMB16\_S[w<sub>A</sub>]\_S[w<sub>B</sub>] calls out the dual-port primitive, where the integers w<sub>A</sub> and w<sub>B</sub> specify the total data path width at ports w<sub>A</sub> and w<sub>B</sub>, respectively. Thus, a RAMB16\_S9\_S18 is a dual-port RAM with a 9-bit-wide Port A and an 18-bit-wide Port B. A name of the form RAMB16\_S[w] identifies the single-port primitive, where the integer w specifies the total data path width of the lone port. A RAMB16\_S18 is a single-port RAM with an 18-bit-wide port. Other memory functions—e.g., FIFOs, data path width conversion, ROM, etc.—are readily available using the CORE Generator<sup>TM</sup> software, part of the Xilinx development software.

### Table 13: Block RAM Port Signals (Cont'd)

| Signal<br>Description    | Port A<br>Signal Name | Port B<br>Signal Name | Direction | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------------------------|-----------------------|-----------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Data Output Bus          | DOA                   | DOB                   | Output    | Basic data access occurs whenever WE is inactive. The DO outputs mirror the data stored in the addressed memory location.                                                                                                                                                                                                                                                                                                                                |

|                          |                       |                       |           | Data access with WE asserted is also possible if one of the following two attributes is chosen: WRITE_FIRST and READ_FIRST. WRITE_FIRST simultaneously presents the new input data on the DO output port and writes the data to the address RAM location. READ_FIRST presents the previously stored RAM data on the DO output port while writing new data to RAM.                                                                                        |

|                          |                       |                       |           | A third attribute, NO_CHANGE, latches the DO outputs upon the assertion of WE.                                                                                                                                                                                                                                                                                                                                                                           |

|                          |                       |                       |           | It is possible to configure a port's total data path width (w) to be 1, 2, 4, 9, 18, or 36 bits. This selection applies to both the DI and DO paths. See the DI signal description.                                                                                                                                                                                                                                                                      |

| Parity Data<br>Output(s) | DOPA                  | DOPB                  | Output    | Parity inputs represent additional bits included in the data input path to support error detection. The number of parity bits "p" included in the DI (same as for the DO bus) depends on a port's total data path width (w). See Table 14.                                                                                                                                                                                                               |

| Write Enable             | WEA                   | WEB                   | Input     | When asserted together with EN, this input enables the writing of data<br>to the RAM. In this case, the data access attributes WRITE_FIRST,<br>READ_FIRST or NO_CHANGE determines if and how data is updated<br>on the DO outputs. See the DO signal description.<br>When WE is inactive with EN asserted, read operations are still<br>possible. In this case, a transparent latch passes data from the<br>addressed memory location to the DO outputs. |

| Clock Enable             | ENA                   | ENB                   | Input     | When asserted, this input enables the CLK signal to synchronize Block<br>RAM functions as follows: the writing of data to the DI inputs (when WE<br>is also asserted), the updating of data at the DO outputs as well as the<br>setting/resetting of the DO output latches.<br>When de-asserted, the above functions are disabled.                                                                                                                       |

| Set/Reset                | SSRA                  | SSRB                  | Input     | When asserted, this pin forces the DO output latch to the value that the SRVAL attribute is set to. A Set/Reset operation on one port has no effect on the other ports functioning, nor does it disturb the memory's data contents. It is synchronized to the CLK signal.                                                                                                                                                                                |

| Clock                    | CLKA                  | CLKB                  | Input     | This input accepts the clock signal to which read and write operations<br>are synchronized. All associated port inputs are required to meet setup<br>times with respect to the clock signal's active edge. The data output bus<br>responds after a clock-to-out delay referenced to the clock signal's<br>active edge.                                                                                                                                   |

## **Port Aspect Ratios**

On a given port, it is possible to select a number of different possible widths (w - p) for the DI/DO buses as shown in Table 14. These two buses always have the same width. This data bus width selection is independent for each port. If the data bus width of Port A differs from that of Port B, the Block RAM automatically performs a bus-matching function. When data are written to a port with a narrow bus, then read from a port with a wide bus, the latter port will effectively combine "narrow" words to form "wide" words. Similarly, when data are written into a port with a wide bus, then read from a port with a narrow bus, the latter port will divide "wide" words to form "narrow" words. When the data bus width is eight bits or greater, extra parity bits become available. The width of the total data path (*w*) is the sum of the DI/DO bus width and any parity bits (*p*).

The width selection made for the DI/DO bus determines the number of address lines according to the relationship expressed below:

$$r = 14 - [\log(w - p)/\log(2)]$$

In turn, the number of address lines delimits the total number (n) of addressable locations or depth according to the following equation:

$$n = 2^r$$

Equation 2

Equation 1

The DLL component has two clock inputs, CLKIN and CLKFB, as well as seven clock outputs, CLK0, CLK90, CLK180, CLK270, CLK2X, CLK2X180, and CLKDV as described in Table 16. The clock outputs drive simultaneously; however, the High Frequency mode only supports a subset of the outputs available in the Low Frequency mode. See DLL Frequency Modes, page 35. Signals that initialize and report the state of the DLL are discussed in The Status Logic Component, page 41.

### Table 16: DLL Signals

| Signal Direction |        |                                                                                                                            | Mode Support     |                   |  |

|------------------|--------|----------------------------------------------------------------------------------------------------------------------------|------------------|-------------------|--|

|                  |        | Description                                                                                                                | Low<br>Frequency | High<br>Frequency |  |

| CLKIN            | Input  | Accepts original clock signal.                                                                                             | Yes              | Yes               |  |

| CLKFB            | Input  | Accepts either CLK0 or CLK2X as feed back signal. (Set CLK_FEEDBACK attribute accordingly).                                |                  | Yes               |  |

| CLK0             | Output | Generates clock signal with same frequency and phase as CLKIN.                                                             | Yes              | Yes               |  |

| CLK90            | Output | Generates clock signal with same frequency as CLKIN, only phase-shifted 90°.                                               | Yes              | No                |  |

| CLK180           | Output | Generates clock signal with same frequency as CLKIN, only phase-shifted 180°.                                              | Yes              | Yes               |  |

| CLK270           | Output | Generates clock signal with same frequency as CLKIN, only phase-shifted 270°.                                              | Yes              | No                |  |

| CLK2X            | Output | Generates clock signal with same phase as CLKIN, only twice the frequency.                                                 | Yes              | No                |  |

| CLK2X180         | Output | Generates clock signal with twice the frequency of CLKIN, phase-shifted 180° with respect to CLKIN.                        | Yes              | No                |  |

| CLKDV            | Output | Divides the CLKIN frequency by CLKDV_DIVIDE value to generate lower frequency clock signal that is phase-aligned to CLKIN. | Yes              | Yes               |  |

The clock signal supplied to the CLKIN input serves as a reference waveform, with which the DLL seeks to align the feedback signal at the CLKFB input. When eliminating clock skew, the common approach to using the DLL is as follows: The CLK0 signal is passed through the clock distribution network to all the registers it synchronizes. These registers are either internal or external to the FPGA. After passing through the clock distribution network, the clock signal returns to the DLL via a feedback line called CLKFB. The control block inside the DLL measures the phase error between CLKFB and CLKIN. This phase error is a measure of the clock skew that the clock distribution network introduces. The control block activates the appropriate number of delay elements to cancel out the clock skew. Once the DLL has brought the CLK0 signal in phase with the CLKIN signal, it asserts the LOCKED output, indicating a "lock" on to the CLKIN signal.

### **DLL Attributes and Related Functions**

A number of different functional options can be set for the DLL component through the use of the attributes described in Table 17. Each attribute is described in detail in the sections that follow:

| Attribute             | Description                                                                                      | Values                                                                                                  |

|-----------------------|--------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|

| CLK_FEEDBACK          | Chooses either the CLK0 or CLK2X output to drive the CLKFB input                                 | NONE, 1X, 2X                                                                                            |

| DLL_FREQUENCY_MODE    | Chooses between High Frequency and Low Frequency modes                                           | LOW, HIGH                                                                                               |

| CLKIN_DIVIDE_BY_2     | Halves the frequency of the CLKIN signal just as it enters the DCM                               | TRUE, FALSE                                                                                             |

| CLKDV_DIVIDE          | Selects constant used to divide the CLKIN input frequency to generate the CLKDV output frequency | 1.5, 2, 2.5, 3, 3.5, 4, 4.5,<br>5, 5.5, 6.0, 6.5, 7.0, 7.5,<br>8, 9, 10, 11, 12, 13, 14,<br>15, and 16. |

| DUTY_CYCLE_CORRECTION | Enables 50% duty cycle correction for the CLK0, CLK90, CLK180, and CLK270 outputs                | TRUE, FALSE                                                                                             |

### Table 17: DLL Attributes

### Table 22: Status Logic Signals

| Signal      | Direction | Description                                                                                                                                                       |  |  |  |  |

|-------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| RST         | Input     | A High resets the entire DCM to its initial power-on state. Initializes the DLL taps for a delay of zero. Sets the LOCKED output Low. This input is asynchronous. |  |  |  |  |

| STATUS[7:0] | Output    | The bit values on the STATUS bus provide information regarding the state of DLL and PS operation                                                                  |  |  |  |  |

| LOCKED      | Output    | Indicates that the CLKIN and CLKFB signals are in phase by going High. The two signals are out-of-phase when Low.                                                 |  |  |  |  |

### Table 23: DCM STATUS Bus

| Bit | Name                                         | Description                                                                                                                                                                                                                                                        |

|-----|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | Phase Shift Overflow                         | A value of 1 indicates a phase shift overflow when one of two conditions occurs:<br>Incrementing (or decrementing) TPS beyond 255/256 of a CLKIN cycle.<br>The DLL is producing its maximum possible phase shift (i.e., all delay taps are active). <sup>(1)</sup> |

| 1   | CLKIN Input Stopped<br>Toggling              | A value of 1 indicates that the CLKIN input signal is not toggling. A value of 0 indicates toggling. This bit functions only when the CLKFB input is connected. <sup>(2)</sup>                                                                                     |

| 2   | CLKFX/CLKFX180<br>Output Stopped<br>Toggling | A value of 1 indicates that the CLKFX or CLKFX180 output signals are not toggling. A value of 0 indicates toggling. This bit functions only when using the Digital Frequency Synthesizer (DFS).                                                                    |

| 3:7 | Reserved                                     | -                                                                                                                                                                                                                                                                  |

#### Notes:

- 1. The DLL phase shift with all delay taps active is specified as the parameter FINE\_SHIFT\_RANGE.

- 2. If only the DFS clock outputs are used, but none of the DLL clock outputs, this bit will not go High when the CLKIN signal stops.

### Table 24: Status Attributes

| Attribute    | Attribute Description                                                               |             |

|--------------|-------------------------------------------------------------------------------------|-------------|

| STARTUP_WAIT | Delays transition from configuration to user mode until lock condition is achieved. | TRUE, FALSE |

### Stabilizing DCM Clocks Before User Mode

It is possible to delay the completion of device configuration until after the DLL has achieved a lock condition using the STARTUP\_WAIT attribute described in Table 24. This option ensures that the FPGA does not enter user mode—i.e., begin functional operation—until all system clocks generated by the DCM are stable. In order to achieve the delay, it is necessary to set the attribute to TRUE as well as set the BitGen option LCK\_cycle to one of the six cycles making up the Startup phase of configuration. The selected cycle defines the point at which configuration will halt until the LOCKED output goes High.

# **Global Clock Network**

Spartan-3 devices have eight Global Clock inputs called GCLK0 - GCLK7. These inputs provide access to a low-capacitance, low-skew network that is well-suited to carrying high-frequency signals. The Spartan-3 FPGAs clock network is shown in Figure 23. GCLK0 through GCLK3 are located in the center of the bottom edge. GCLK4 through GCLK7 are located in the center of the top edge.

Eight Global Clock Multiplexers (also called BUFGMUX elements) are provided that accept signals from Global Clock inputs and route them to the internal clock network as well as DCMs. Four BUFGMUX elements are located in the center of the bottom edge, just above the GCLK0 - GCLK3 inputs. The remaining four BUFGMUX elements are located in the center of the top edge, just below the GCLK4 - GCLK7 inputs.

Pairs of BUFGMUX elements share global inputs, as shown in Figure 24. For example, the GCLK4 and GCLK5 inputs both potentially connect to BUFGMUX4 and BUFGMUX5 located in the upper right center. A differential clock input uses a pair of GCLK inputs to connect to a single BUFGMUX element.

Each BUFGMUX element, shown in Figure 24, is a 2-to-1 multiplexer that can receive signals from any of the four following sources:

- One of the four Global Clock inputs on the same side of the die-top or bottom-as the BUFGMUX element in use.

- Any of four nearby horizontal Double lines.

- Any of four outputs from the DCM in the right-hand quadrant that is on the same side of the die as the BUFGMUX element in use.

- Any of four outputs from the DCM in the left-hand quadrant that is on the same side of the die as the BUFGMUX element in use.

The multiplexer select line, S, chooses which of the two inputs, I0 or I1, drives the BUFGMUX's output signal, O, as described in Table 25. The switching from one clock to the other is glitchless, and done in such a way that the output High and Low times are never shorter than the shortest High or Low time of either input clock.

Table 25: BUFGMUX Select Mechanism

| S Input | O Output |

|---------|----------|

| 0       | 10 Input |

| 1       | I1 Input |

The two clock inputs can be asynchronous with regard to each other, and the S input can change at any time, except for a short setup time prior to the rising edge of the presently selected clock (I0 or I1). Violating this setup time requirement can result in an undefined runt pulse output.

The BUFG clock buffer primitive drives a single clock signal onto the clock network and is essentially the same element as a BUFGMUX, just without the clock select mechanism. Similarly, the BUFGCE primitive creates an enabled clock buffer using the BUFGMUX select mechanism.

Each BUFGMUX buffers incoming clock signals to two possible destinations:

- The vertical spine belonging to the same side of the die—top or bottom—as the BUFGMUX element in use. The two spines—top and bottom—each comprise four vertical clock lines, each running from one of the BUFGMUX elements on the same side towards the center of the die. At the center of the die, clock signals reach the eight-line horizontal spine, which spans the width of the die. In turn, the horizontal spine branches out into a subsidiary clock interconnect that accesses the CLBs.

- The clock input of either DCM on the same side of the die-top or bottom-as the BUFGMUX element in use.

Use either a BUFGMUX element or a BUFG (Global Clock Buffer) element to place a Global input in the design. For the purpose of minimizing the dynamic power dissipation of the clock network, the Xilinx development software automatically disables all clock line segments that a design does not use.

A global clock line ideally drives clock inputs on the various clocked elements within the FPGA, such as CLB or IOB flip-flops or block RAMs. A global clock line also optionally drives combinatorial inputs. However, doing so provides additional loading on the clock line that might also affect clock jitter. Ideally, drive combinatorial inputs using the signal that also drives the input to the BUFGMUX or BUFG element.

For more details, refer to the chapter entitled "Using Global Clock Resources" in UG331.

| Symbol                          | Description                                                                      | Test Cond                                    | litions                 | Min   | Тур   | Max   | Units |

|---------------------------------|----------------------------------------------------------------------------------|----------------------------------------------|-------------------------|-------|-------|-------|-------|

| I <sub>L</sub> (2)(4)           | Leakage current at User I/O,                                                     | Driver is Hi-Z, V <sub>IN</sub> =            | $V_{CCO} \ge 3.0V$      | —     | -     | ±25   | μA    |

|                                 | Dual-Purpose, and Dedicated pins                                                 | 0V or V <sub>CCO</sub> max,<br>sample-tested | V <sub>CCO</sub> < 3.0V | -     | -     | ±10   | μA    |

| I <sub>RPU</sub> <sup>(3)</sup> | Current through pull-up resistor at User I/O,                                    | V <sub>IN</sub> = 0V, V <sub>CC</sub>        | <sub>CO</sub> = 3.3V    | -0.84 | -     | -2.35 | mA    |

|                                 | Dual-Purpose, and Dedicated pins                                                 | V <sub>IN</sub> = 0V, V <sub>CC</sub>        | <sub>CO</sub> = 3.0V    | -0.69 | -     | -1.99 | mA    |

|                                 |                                                                                  | $V_{IN} = 0V, V_{CC}$                        | <sub>CO</sub> = 2.5V    | -0.47 | -     | -1.41 | mA    |

|                                 |                                                                                  | $V_{IN} = 0V, V_{CC}$                        | <sub>CO</sub> = 1.8V    | -0.21 | -     | -0.69 | mA    |

|                                 |                                                                                  | $V_{IN} = 0V, V_{CC}$                        | <sub>CO</sub> = 1.5V    | -0.13 | -     | -0.43 | mA    |

|                                 |                                                                                  | V <sub>IN</sub> = 0V, V <sub>CC</sub>        | <sub>:O</sub> = 1.2V    | -0.06 | -     | -0.22 | mA    |

| Use                             | Equivalent resistance of pull-up resistor at                                     | V <sub>CCO</sub> = 3.0V to 3.465V            |                         | 1.27  | -     | 4.11  | kΩ    |

|                                 | User I/O, Dual-Purpose, and Dedicated pins, derived from I <sub>RPU</sub>        | V <sub>CCO</sub> = 2.3V                      | 1.15                    | -     | 3.25  | kΩ    |       |

|                                 |                                                                                  | V <sub>CCO</sub> = 1.7V                      | 2.45                    | -     | 9.10  | kΩ    |       |

|                                 |                                                                                  | V <sub>CCO</sub> = 1.4V                      | 3.25                    | -     | 12.10 | kΩ    |       |

|                                 |                                                                                  | V <sub>CCO</sub> = 1.14                      | 5.15                    | -     | 21.00 | kΩ    |       |

| I <sub>RPD</sub> <sup>(3)</sup> | Current through pull-down resistor at User I/O, Dual-Purpose, and Dedicated pins | $V_{IN} = V_{CCO}$                           |                         | 0.37  | -     | 1.67  | mA    |

| R <sub>PD</sub> <sup>(3)</sup>  | Equivalent resistance of pull-down resistor                                      | $V_{IN} = V_{CCO} = 3.0$                     | 1.75                    | -     | 9.35  | kΩ    |       |

|                                 | at User I/O, Dual-Purpose, and Dedicated pins, driven from I <sub>BPD</sub>      | $V_{IN} = V_{CCO} = 2$                       | 1.35                    | -     | 7.30  | kΩ    |       |

|                                 |                                                                                  | $V_{IN} = V_{CCO} = 1.7V$ to 1.9V            |                         | 1.00  | -     | 5.15  | kΩ    |

|                                 |                                                                                  | $V_{IN} = V_{CCO} = 1$                       | 0.85                    | -     | 4.35  | kΩ    |       |

|                                 |                                                                                  | $V_{IN} = V_{CCO} = 1.$                      | 0.68                    | -     | 3.465 | kΩ    |       |

| R <sub>DCI</sub>                | Value of external reference resistor to supp                                     | ort DCI I/O standards                        |                         | 20    | -     | 100   | Ω     |

| I <sub>REF</sub>                | V <sub>REF</sub> current per pin                                                 | $V_{CCO} \ge 3$                              | —                       | -     | ±25   | μA    |       |

|                                 |                                                                                  | V <sub>CCO</sub> < 3                         | —                       | -     | ±10   | μA    |       |

| C <sub>IN</sub>                 | Input capacitance                                                                |                                              |                         | 3     | -     | 10    | pF    |

### Table 33: General DC Characteristics of User I/O, Dual-Purpose, and Dedicated Pins

Notes:

1. The numbers in this table are based on the conditions set forth in Table 32.

2. The I<sub>L</sub> specification applies to every I/O pin throughout power-on as long as the voltage on that pin stays between the absolute V<sub>IN</sub> minimum and maximum values (Table 28). For hot-swap applications, at the time of card connection, be sure to keep all I/O voltages within this range before applying V<sub>CCO</sub> power. Consider applying V<sub>CCO</sub> power before connecting the signal lines, to avoid turning on the ESD protection diodes, shown in Module 2: Figure 7, page 11. When the FPGA is completely unpowered, the I/O pins are high impedance, but there is a path through the upper and lower ESD protection diodes.

3. This parameter is based on characterization. The pull-up resistance  $R_{PU} = V_{CCO} / I_{RPU}$ . The pull-down resistance  $R_{PD} = V_{IN} / I_{RPD}$ . Spartan-3 family values for both resistances are stronger than they have been for previous FPGA families.

For single-ended signals that are placed on a differential-capable I/O, V<sub>IN</sub> of –0.2V to –0.3V is supported but can cause increased leakage between the two pins. See the *Parasitic Leakage* section in <u>UG331</u>, *Spartan-3 Generation FPGA User Guide*.

## Table 36: DC Characteristics of User I/Os Using Single-Ended Standards (Cont'd)

| Signal Sta                                       | andard | Test Co                 | nditions                | Logic Level C              | haracteristics             |  |

|--------------------------------------------------|--------|-------------------------|-------------------------|----------------------------|----------------------------|--|

| (IOSTANDARD) and Current<br>Drive Attribute (mA) |        | l <sub>OL</sub><br>(mA) | I <sub>ОН</sub><br>(mA) | V <sub>OL</sub><br>Max (V) | V <sub>OH</sub><br>Min (V) |  |

| LVCMOS33 <sup>(4)</sup>                          | 2      | 2                       | -2                      | 0.4                        | V <sub>CCO</sub> – 0.4     |  |

|                                                  | 4      | 4                       | -4                      | _                          |                            |  |

|                                                  | 6      | 6                       | 6                       | _                          |                            |  |

|                                                  | 8      | 8                       | -8                      |                            |                            |  |

|                                                  | 12     | 12                      | -12                     |                            |                            |  |

|                                                  | 16     | 16                      | -16                     | _                          |                            |  |

|                                                  | 24     | 24                      | -24                     | _                          |                            |  |

| LVDCI_33,<br>LVDCI_DV2_33                        |        | Note 3                  | Note 3                  | _                          |                            |  |

| LVTTL <sup>(4)</sup>                             | 2      | 2                       | -2                      | 0.4                        | 2.4                        |  |

|                                                  | 4      | 4                       | -4                      |                            |                            |  |

|                                                  | 6      | 6                       | 6                       |                            |                            |  |

|                                                  | 8      | 8                       | 8                       |                            |                            |  |

|                                                  | 12     | 12                      | -12                     |                            |                            |  |

|                                                  | 16     | 16                      | -16                     |                            |                            |  |

|                                                  | 24     | 24                      | -24                     |                            |                            |  |

| PCI33_3                                          |        | Note 6                  | Note 6                  | 0.10V <sub>CCO</sub>       | 0.90V <sub>CCO</sub>       |  |

| SSTL18_I                                         |        | 6.7                     | -6.7                    | V <sub>TT</sub> – 0.475    | V <sub>TT</sub> + 0.475    |  |

| SSTL18_I_DCI                                     |        | Note 3                  | Note 3                  |                            |                            |  |

| SSTL18_II<br>SSTL2_I<br>SSTL2_I_DCI              |        | 13.4                    | -13.4                   | V <sub>TT</sub> – 0.475    | V <sub>TT</sub> + 0.475    |  |

|                                                  |        | 8.1                     | -8.1                    | V <sub>TT</sub> – 0.61     | V <sub>TT</sub> + 0.61     |  |

|                                                  |        | Note 3                  | Note 3                  |                            |                            |  |

| SSTL2_II <sup>(7)</sup>                          |        | 16.2                    | -16.2                   | V <sub>TT</sub> – 0.81     | V <sub>TT</sub> + 0.81     |  |

| SSTL2_II_DCI <sup>(7)</sup>                      |        | Note 3                  | Note 3                  |                            |                            |  |

#### Notes:

2.

The numbers in this table are based on the conditions set forth in Table 32 and Table 35. 1.

The numbers in this table are based on the conditions set for Descriptions of the symbols used in this table are as follows:  $I_{OL}$  – the output current condition under which VOL is tested  $V_{OL}$  – the output current condition under which VOH is tested  $V_{OL}$  – the output voltage that indicates a Low logic level  $V_{H}$  – the input voltage that indicates a High logic level  $V_{H}$  – the input voltage that indicates a High logic level  $V_{H}$  – the input voltage that indicates a High logic level  $V_{H}$  – the supply voltage for output drivers as well as LVCM

$V_{CCO}$  – the supply voltage for output drivers as well as LVCMOS, LVTTL, and PCI inputs  $V_{REF}$  – the reference voltage for setting the input switching threshold  $V_{TT}$  – the voltage applied to a resistor termination

Tested according to the standard's relevant specifications. When using the DCI version of a standard on a given I/O bank, that bank will consume more power than if the non-DCI version had been used instead. The additional power is drawn for the purpose of impedance-matching at the I/O pins. A portion of this power is dissipated in the two RREF resistors. 3.

For the LVCMOS and LVTTL standards: the same V<sub>OL</sub> and V<sub>OH</sub> limits apply for both the Fast and Slow slew attributes. 4.

All dedicated output pins (CCLK, DONE, and TDO) and dual-purpose totem-pole output pins (D0-D7 and BUSY/DOUT) exhibit the characteristics of 5. LVCMOS25 with 12 mA drive and slow slew rate. For information concerning the use of 3.3V signals, see 3.3V-Tolerant Configuration Interface, page 47.

Tested according to the relevant PCI specifications. For more information, see XAPP457. 6.

7. The minimum usable V<sub>TT</sub> voltage is 1.25V.

# Spartan-3 FPGA Family: DC and Switching Characteristics

# Table 50: Recommended Number of Simultaneously Switching Outputs per V<sub>CCO</sub>/GND Pair

| Signal Standard<br>(IOSTANDARD) |      |    | Package |       |       |       |                                              |  |

|---------------------------------|------|----|---------|-------|-------|-------|----------------------------------------------|--|

|                                 |      |    | VQ100   | TQ144 | PQ208 | CP132 | FT256, FG320, FG456,<br>FG676, FG900, FG1156 |  |

| Single-Ended Stand              | ards |    |         | ·     |       |       |                                              |  |

| GTL                             |      |    | 0       | 0     | 0     | 1     | 14                                           |  |

| GTL_DCI                         |      |    | 0       | 0     | 0     | 1     | 14                                           |  |

| GTLP                            |      |    | 0       | 0     | 0     | 1     | 19                                           |  |

| GTLP_DCI                        |      |    | 0       | 0     | 0     | 1     | 19                                           |  |

| HSLVDCI_15                      |      |    | 6       | 6     | 6     | 6     | 14                                           |  |

| HSLVDCI_18                      |      |    | 7       | 7     | 7     | 7     | 10                                           |  |

| HSLVDCI_25                      |      |    | 7       | 7     | 7     | 7     | 11                                           |  |

| HSLVDCI_33                      |      |    | 10      | 10    | 10    | 10    | 10                                           |  |

| HSTL_I                          |      |    | 11      | 11    | 11    | 11    | 17                                           |  |

| HSTL_I_DCI                      |      |    | 11      | 11    | 11    | 11    | 17                                           |  |

| HSTL_III                        |      |    | 7       | 7     | 7     | 7     | 7                                            |  |

| HSTL_III_DCI                    |      |    | 7       | 7     | 7     | 7     | 7                                            |  |

| HSTL_I_18                       |      |    | 13      | 13    | 13    | 13    | 17                                           |  |

| HSTL_I_DCI_18                   |      |    | 13      | 13    | 13    | 13    | 17                                           |  |

| HSTL_II_18                      |      |    | 9       | 9     | 9     | 9     | 9                                            |  |

| HSTL_II_DCI_18                  |      |    | 9       | 9     | 9     | 9     | 9                                            |  |

| HSTL_III_18                     |      |    | 8       | 8     | 8     | 8     | 8                                            |  |

| HSTL_III_DCI_18                 |      |    | 8       | 8     | 8     | 8     | 8                                            |  |

| LVCMOS12                        | Slow | 2  | 17      | 17    | 17    | 17    | 55                                           |  |

|                                 |      | 4  | 13      | 13    | 13    | 13    | 32                                           |  |

|                                 |      | 6  | 10      | 10    | 10    | 10    | 18                                           |  |

|                                 | Fast | 2  | 12      | 12    | 12    | 12    | 31                                           |  |

|                                 |      | 4  | 11      | 11    | 11    | 11    | 13                                           |  |

|                                 |      | 6  | 9       | 9     | 9     | 9     | 9                                            |  |

| LVCMOS15                        | Slow | 2  | 16      | 12    | 12    | 19    | 55                                           |  |

|                                 |      | 4  | 8       | 7     | 7     | 9     | 31                                           |  |

|                                 |      | 6  | 7       | 7     | 7     | 9     | 18                                           |  |

| 8                               |      | 8  | 6       | 6     | 6     | 6     | 15                                           |  |

|                                 |      | 12 | 5       | 5     | 5     | 5     | 10                                           |  |

|                                 | Fast | 2  | 10      | 10    | 10    | 13    | 25                                           |  |

|                                 |      | 4  | 6       | 7     | 7     | 7     | 16                                           |  |

|                                 |      | 6  | 7       | 7     | 7     | 7     | 13                                           |  |

|                                 |      | 8  | 6       | 6     | 6     | 6     | 11                                           |  |

|                                 |      | 12 | 6       | 6     | 6     | 6     | 7                                            |  |

# Table 50: Recommended Number of Simultaneously Switching Outputs per V<sub>CCO</sub>/GND Pair (Cont'd)

| Cime                            | al Chandard |       | Package |       |       |                                              |    |  |

|---------------------------------|-------------|-------|---------|-------|-------|----------------------------------------------|----|--|

| Signal Standard<br>(IOSTANDARD) |             | VQ100 | TQ144   | PQ208 | CP132 | FT256, FG320, FG456,<br>FG676, FG900, FG1156 |    |  |

| LVCMOS33                        | Slow        | 2     | 34      | 24    | 24    | 52                                           | 76 |  |

|                                 |             | 4     | 17      | 14    | 14    | 26                                           | 46 |  |

|                                 |             | 6     | 17      | 11    | 11    | 26                                           | 27 |  |

|                                 |             | 8     | 10      | 10    | 10    | 13                                           | 20 |  |

|                                 |             | 12    | 9       | 9     | 9     | 13                                           | 13 |  |

|                                 |             | 16    | 8       | 8     | 8     | 8                                            | 10 |  |

|                                 |             | 24    | 8       | 8     | 8     | 8                                            | 9  |  |

|                                 | Fast        | 2     | 20      | 20    | 20    | 26                                           | 44 |  |

|                                 |             | 4     | 15      | 15    | 15    | 15                                           | 26 |  |

|                                 |             | 6     | 11      | 11    | 11    | 13                                           | 16 |  |

|                                 |             | 8     | 10      | 10    | 10    | 10                                           | 12 |  |

|                                 |             | 12    | 8       | 8     | 8     | 8                                            | 10 |  |

|                                 |             | 16    | 8       | 8     | 8     | 8                                            | 8  |  |

|                                 |             | 24    | 7       | 7     | 7     | 7                                            | 7  |  |

| LVDCI_33                        |             | -+    | 10      | 10    | 10    | 10                                           | 10 |  |

| LVDCI_DV2_33                    |             |       | 10      | 10    | 10    | 10                                           | 10 |  |

| HSLVDCI_33                      |             |       | 10      | 10    | 10    | 10                                           | 10 |  |

| LVTTL                           | Slow        | 2     | 34      | 25    | 25    | 52                                           | 60 |  |

|                                 |             | 4     | 17      | 16    | 16    | 26                                           | 41 |  |

|                                 |             | 6     | 17      | 15    | 15    | 26                                           | 29 |  |

|                                 |             | 8     | 12      | 12    | 12    | 13                                           | 22 |  |

|                                 |             | 12    | 10      | 10    | 10    | 13                                           | 13 |  |

|                                 |             | 16    | 10      | 10    | 10    | 10                                           | 11 |  |

|                                 |             | 24    | 8       | 8     | 8     | 8                                            | 9  |  |

|                                 | Fast        | 2     | 20      | 20    | 20    | 26                                           | 34 |  |

|                                 |             | 4     | 13      | 13    | 13    | 13                                           | 20 |  |

|                                 |             | 6     | 11      | 11    | 11    | 13                                           | 15 |  |

|                                 |             | 8     | 10      | 10    | 10    | 10                                           | 12 |  |

|                                 |             | 12    | 9       | 9     | 9     | 9                                            | 10 |  |

|                                 |             | 16    | 8       | 8     | 8     | 8                                            | 9  |  |

|                                 |             | 24    | 7       | 7     | 7     | 7                                            | 7  |  |

www.xilinx.com

## Table 50: Recommended Number of Simultaneously Switching Outputs per V<sub>CCO</sub>/GND Pair (Cont'd)

| Cinnel Chenderd                            |                 | Package  |       |       |                                              |  |  |

|--------------------------------------------|-----------------|----------|-------|-------|----------------------------------------------|--|--|

| Signal Standard<br>(IOSTANDARD)            | VQ100           | TQ144    | PQ208 | CP132 | FT256, FG320, FG456,<br>FG676, FG900, FG1156 |  |  |

| PCl33_3                                    | 9               | 9        | 9     | 9     | 9                                            |  |  |

| SSTL18_I                                   | 13              | 13       | 13    | 13    | 17                                           |  |  |

| SSTL18_I_DCI                               | 13              | 13       | 13    | 13    | 17                                           |  |  |

| SSTL18_II                                  | 8               | 8        | 8     | 8     | 9                                            |  |  |

| SSTL2_I                                    | 10              | 10       | 10    | 10    | 13                                           |  |  |

| SSTL2_I_DCI                                | 10              | 10       | 10    | 10    | 13                                           |  |  |

| SSTL2_II                                   | 6               | 6        | 6     | 6     | 9                                            |  |  |

| SSTL2_II_DCI                               | 6               | 6        | 6     | 6     | 9                                            |  |  |

| Differential Standards (Number of I/O Pair | rs or Channels) | <u>.</u> |       | !     |                                              |  |  |

| LDT_25 (ULVDS_25)                          | 5               | 5        | 5     | 5     | 5                                            |  |  |

| LVDS_25                                    | 7               | 5        | 5     | 12    | 20                                           |  |  |

| BLVDS_25                                   | 2               | 1        | 1     |       | 4                                            |  |  |

| LVDSEXT_25                                 | 5               | 5        | 5     | 5     | 5                                            |  |  |

| LVPECL_25                                  | 2               | 1        | 1     |       | 4                                            |  |  |

| RSDS_25                                    | 7               | 5        | 5     | 12    | 20                                           |  |  |

| DIFF_HSTL_II_18                            | 4               | 4        | 4     | 4     | 4                                            |  |  |

| DIFF_HSTL_II_18_DCI                        | 4               | 4        | 4     | 4     | 4                                            |  |  |

| DIFF_SSTL2_II                              | 3               | 3        | 3     | 3     | 4                                            |  |  |

| DIFF_SSTL2_II_DCI                          | 3               | 3        | 3     | 3     | 4                                            |  |  |

Notes:

1. The numbers in this table are recommendations that assume the FPGA is soldered on a printed circuit board using sound practices. This table assumes the following parasitic factors: combined PCB trace and land inductance per  $V_{CCO}$  and GND pin of 1.0 nH, receiver capacitive load of 15 pF. Test limits are the  $V_{IL}/V_{IH}$  voltage limits for the respective I/O standard.

2. Regarding the SSO numbers for all DCI standards, the R<sub>REF</sub> resistors connected to the VRN and VRP pins of the FPGA are 50W.

3. If more than one signal standard is assigned to the I/Os of a given bank, refer to XAPP689: Managing Ground Bounce in Large FPGAs for information on how to perform weighted average SSO calculations.

4. Results are based on actual silicon testing using an FPGA soldered on a typical printed-circuit board.

| Pin Name | Direction                     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DIN      | Input                         | Serial Data Input:<br>During the Master or Slave Serial configuration modes, DIN is the serial configuration data input, and<br>all data is synchronized to the rising CCLK edge. After configuration, this pin is available as a user I/O.<br>This signal is located in Bank 4 and its output voltage determined by VCCO_4.<br>The BitGen option <i>Persist</i> permits this pin to retain its configuration function in the User mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| DOUT     | Output                        | Serial Data Output:<br>In a multi-FPGA design where all the FPGAs use serial mode, connect the DOUT output of one<br>FPGA—in either Master or Slave Serial mode—to the DIN input of the next FPGA—in Slave Serial<br>mode—so that configuration data passes from one to the next, in daisy-chain fashion. This "daisy<br>chain" permits sequential configuration of multiple FPGAs.<br>This signal is located in Bank 4 and its output voltage determined by VCCO_4.<br>The BitGen option <i>Persist</i> permits this pin to retain its configuration function in the User mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| INIT_B   | Bidirectional<br>(open-drain) | Initializing Configuration Memory/Configuration Error:<br>Just after power is applied, the FPGA produces a Low-to-High transition on this pin indicating that<br>initialization ( <i>i.e.</i> , clearing) of the configuration memory has finished. Before entering the User mode,<br>this pin functions as an open-drain output, which requires a pull-up resistor in order to produce a High<br>logic level. In a multi-FPGA design, tie (wire AND) the INIT_B pins from all FPGAs together so that the<br>common node transitions High only after all of the FPGAs have been successfully initialized.<br>Externally holding this pin Low beyond the initialization phase delays the start of configuration. This<br>action stalls the FPGA at the configuration step just before the mode select pins are sampled.<br>During configuration, the FPGA indicates the occurrence of a data (i.e., CRC) error by asserting<br>INIT_B Low.<br>This signal is located in Bank 4 and its output voltage determined by VCCO_4.<br>The BitGen option <i>Persist</i> permits this pin to retain its configuration function in the User mode. |

### Table 71: Dual-Purpose Pins Used in Master or Slave Serial Mode

## Parallel Configuration Modes (SelectMAP)

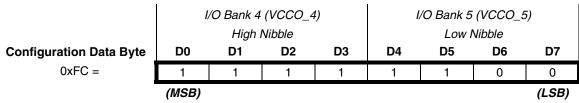

This section describes the dual-purpose configuration pins used during the Master and Slave Parallel configuration modes, sometimes also called the SelectMAP modes. In both Master and Slave Parallel configuration modes, D0-D7 form the byte-wide configuration data input. See Table 75 for Mode Select pin settings required for Parallel modes.

As shown in Figure 41, D0 is the most-significant bit while D7 is the least-significant bit. Bits D0-D3 form the high nibble of the byte and bits D4-D7 form the low nibble.

In the Parallel configuration modes, both the VCCO\_4 and VCCO\_5 voltage supplies are required and must both equal the voltage of the attached configuration device, typically either 2.5V or 3.3V.

Assert Low both the chip-select pin, CS\_B, and the read/write control pin, RDWR\_B, to write the configuration data byte presented on the D0-D7 pins to the FPGA on a rising-edge of the configuration clock, CCLK. The order of CS\_B and RDWR\_B does not matter, although RDWR\_B must be asserted throughout the configuration process. If RDWR\_B is de-asserted during configuration, the FPGA aborts the configuration operation.

After configuration, these pins are available as general-purpose user I/O. However, the SelectMAP configuration interface is optionally available for debugging and dynamic reconfiguration. To use these SelectMAP pins after configuration, set the Persist bitstream generation option.

The Readback debugging option, for example, requires the Persist bitstream generation option. During Readback mode, assert CS\_B Low, along with RDWR\_B High, to read a configuration data byte from the FPGA to the D0-D7 bus on a rising CCLK edge. During Readback mode, D0-D7 are output pins.

In all the cases, the configuration data and control signals are synchronized to the rising edge of the CCLK clock signal.

# User I/Os by Bank

Table 92 indicates how the available user-I/O pins are distributed between the eight I/O banks on the TQ144 package.

## Table 92: User I/Os Per Bank in TQ144 Package

| Dookogo Edgo | I/O Bank | Maximum I/O | All Possible I/O Pins by Type |      |     |      |      |  |

|--------------|----------|-------------|-------------------------------|------|-----|------|------|--|

| Package Edge |          |             | I/O                           | DUAL | DCI | VREF | GCLK |  |

| Тор          | 0        | 10          | 5                             | 0    | 2   | 1    | 2    |  |

| юр           | 1        | 9           | 4                             | 0    | 2   | 1    | 2    |  |

| Right        | 2        | 14          | 10                            | 0    | 2   | 2    | 0    |  |

| right        | 3        | 15          | 11                            | 0    | 2   | 2    | 0    |  |

| Bottom       | 4        | 11          | 0                             | 6    | 2   | 1    | 2    |  |

| Dottom       | 5        | 9           | 0                             | 6    | 0   | 1    | 2    |  |

| Left         | 6        | 14          | 10                            | 0    | 2   | 2    | 0    |  |

| Leit         | 7        | 15          | 11                            | 0    | 2   | 2    | 0    |  |

### Table 100: FG456 Package Pinout (Cont'd)

| Bank | 3S400<br>Pin Name | 3S1000, 3S1500, 3S2000<br>Pin Name | FG456<br>Pin Number | Туре |

|------|-------------------|------------------------------------|---------------------|------|

| 2    | IO_L21P_2         | IO_L21P_2                          | E22                 | I/O  |

| 2    | IO_L22N_2         | IO_L22N_2                          | G17                 | I/O  |

| 2    | IO_L22P_2         | IO_L22P_2                          | G18                 | I/O  |

| 2    | IO_L23N_2/VREF_2  | IO_L23N_2/VREF_2                   | F19                 | VREF |

| 2    | IO_L23P_2         | IO_L23P_2                          | G19                 | I/O  |

| 2    | IO_L24N_2         | IO_L24N_2                          | F20                 | I/O  |

| 2    | IO_L24P_2         | IO_L24P_2                          | F21                 | I/O  |

| 2    | N.C. (�)          | IO_L26N_2                          | G20                 | I/O  |

| 2    | N.C. (�)          | IO_L26P_2                          | H19                 | I/O  |

| 2    | IO_L27N_2         | IO_L27N_2                          | G21                 | I/O  |

| 2    | IO_L27P_2         | IO_L27P_2                          | G22                 | I/O  |

| 2    | N.C. (�)          | IO_L28N_2                          | H18                 | I/O  |

| 2    | N.C. (�)          | IO_L28P_2                          | J17                 | I/O  |

| 2    | N.C. (�)          | IO_L29N_2                          | H21                 | I/O  |

| 2    | N.C. (�)          | IO_L29P_2                          | H22                 | I/O  |

| 2    | N.C. (�)          | IO_L31N_2                          | J18                 | I/O  |

| 2    | N.C. (�)          | IO_L31P_2                          | J19                 | I/O  |

| 2    | N.C. (�)          | IO_L32N_2                          | J21                 | I/O  |

| 2    | N.C. (�)          | IO_L32P_2                          | J22                 | I/O  |

| 2    | N.C. (�)          | IO_L33N_2                          | K17                 | I/O  |

| 2    | N.C. (�)          | IO_L33P_2                          | K18                 | I/O  |

| 2    | IO_L34N_2/VREF_2  | IO_L34N_2/VREF_2                   | K19                 | VREF |

| 2    | IO_L34P_2         | IO_L34P_2                          | K20                 | I/O  |

| 2    | IO_L35N_2         | IO_L35N_2                          | K21                 | I/O  |

| 2    | IO_L35P_2         | IO_L35P_2                          | K22                 | I/O  |

| 2    | IO_L38N_2         | IO_L38N_2                          | L17                 | I/O  |

| 2    | IO_L38P_2         | IO_L38P_2                          | L18                 | I/O  |

| 2    | IO_L39N_2         | IO_L39N_2                          | L19                 | I/O  |

| 2    | IO_L39P_2         | IO_L39P_2                          | L20                 | I/O  |

| 2    | IO_L40N_2         | IO_L40N_2                          | L21                 | I/O  |

| 2    | IO_L40P_2/VREF_2  | IO_L40P_2/VREF_2                   | L22                 | VREF |

| 2    | VCCO_2            | VCCO_2                             | H17                 | VCCO |

| 2    | VCCO_2            | VCCO_2                             | H20                 | VCCO |

| 2    | VCCO_2            | VCCO_2                             | J16                 | VCCO |

| 2    | VCCO_2            | VCCO_2                             | K16                 | VCCO |

| 2    | VCCO_2            | VCCO_2                             | L16                 | VCCO |

| 3    | IO                | IO                                 | Y21                 | I/O  |

| 3    | IO_L01N_3/VRP_3   | IO_L01N_3/VRP_3                    | Y20                 | DCI  |

| 3    | IO_L01P_3/VRN_3   | IO_L01P_3/VRN_3                    | Y19                 | DCI  |

| 3    | IO_L16N_3         | IO_L16N_3                          | W22                 | I/O  |

### Table 100: FG456 Package Pinout (Cont'd)

| Bank | 3S400<br>Pin Name | 3S1000, 3S1500, 3S2000<br>Pin Name | FG456<br>Pin Number | Туре |

|------|-------------------|------------------------------------|---------------------|------|

| 3    | IO_L16P_3         | IO_L16P_3                          | Y22                 | I/O  |

| 3    | IO_L17N_3         | IO_L17N_3                          | V19                 | I/O  |

| 3    | IO_L17P_3/VREF_3  | IO_L17P_3/VREF_3                   | W19                 | VREF |

| 3    | IO_L19N_3         | IO_L19N_3                          | W21                 | I/O  |