# E·XFL

Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                               |

|--------------------------------|---------------------------------------------------------------|

| Product Status                 | Active                                                        |

| Number of LABs/CLBs            | 5120                                                          |

| Number of Logic Elements/Cells | 46080                                                         |

| Total RAM Bits                 | 737280                                                        |

| Number of I/O                  | 565                                                           |

| Number of Gates                | 2000000                                                       |

| Voltage - Supply               | 1.14V ~ 1.26V                                                 |

| Mounting Type                  | Surface Mount                                                 |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                               |

| Package / Case                 | 900-BBGA                                                      |

| Supplier Device Package        | 900-FBGA (31x31)                                              |

| Purchase URL                   | https://www.e-xfl.com/product-detail/xilinx/xc3s2000-4fgg900c |

|                                |                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### Table 8: Single-Ended I/O Standards

| Signal Standard | V <sub>cco</sub> | (Volts)    | V <sub>REF</sub> for Inputs                           | Board Termination Voltage ( $V_{TT}$ ) in Volts |  |

|-----------------|------------------|------------|-------------------------------------------------------|-------------------------------------------------|--|

| (IOSTANDARD)    | For Outputs      | For Inputs | V <sub>REF</sub> for Inputs<br>(Volts) <sup>(1)</sup> |                                                 |  |

| GTL             | Note 2           | Note 2     | 0.8                                                   | 1.2                                             |  |

| GTLP            | Note 2           | Note 2     | 1                                                     | 1.5                                             |  |

| HSTL_I          | 1.5              | -          | 0.75                                                  | 0.75                                            |  |

| HSTL_III        | 1.5              | _          | 0.9                                                   | 1.5                                             |  |

| HSTL_I_18       | 1.8              | -          | 0.9                                                   | 0.9                                             |  |

| HSTL_II_18      | 1.8              | -          | 0.9                                                   | 0.9                                             |  |

| HSTL_III_18     | 1.8              | -          | 1.1                                                   | 1.8                                             |  |

| LVCMOS12        | 1.2              | 1.2        | -                                                     | -                                               |  |

| LVCMOS15        | 1.5              | 1.5        | -                                                     | -                                               |  |

| LVCMOS18        | 1.8              | 1.8        | -                                                     | -                                               |  |

| LVCMOS25        | 2.5              | 2.5        | -                                                     | -                                               |  |

| LVCMOS33        | 3.3              | 3.3        | -                                                     | -                                               |  |

| LVTTL           | 3.3              | 3.3        | -                                                     | -                                               |  |

| PCI33_3         | 3.0              | 3.0        | -                                                     | -                                               |  |

| SSTL18_I        | 1.8              | -          | 0.9                                                   | 0.9                                             |  |

| SSTL18_II       | 1.8              | -          | 0.9                                                   | 0.9                                             |  |

| SSTL2_I         | 2.5              | -          | 1.25                                                  | 1.25                                            |  |

| SSTL2_II        | 2.5              | -          | 1.25                                                  | 1.25                                            |  |

#### Notes:

1. Banks 4 and 5 of any Spartan-3 device in a VQ100 package do not support signal standards using V<sub>REF</sub>

2. The V<sub>CCO</sub> level used for the GTL and GTLP standards must be no lower than the termination voltage (V<sub>TT</sub>), nor can it be lower than the voltage at the I/O pad.

3. See Table 10 for a listing of the single-ended DCI standards.

Differential standards employ a pair of signals, one the opposite polarity of the other. The noise canceling (e.g., Common-Mode Rejection) properties of these standards permit exceptionally high data transfer rates. This section introduces the differential signaling capabilities of Spartan-3 devices.

Each device-package combination designates specific I/O pairs that are specially optimized to support differential standards. A unique "L-number", part of the pin name, identifies the line-pairs associated with each bank (see Figure 40, page 112). For each pair, the letters 'P' and 'N' designate the true and inverted lines, respectively. For example, the pin names IO\_L43P\_7 and IO\_L43N\_7 indicate the true and inverted lines comprising the line pair L43 on Bank 7. The V<sub>CCO</sub> lines provide current to the outputs. The V<sub>CCAUX</sub> lines supply power to the differential inputs, making them independent of the V<sub>CCO</sub> voltage for an I/O bank. The V<sub>REF</sub> lines are not used. Select the V<sub>CCO</sub> level to suit the desired differential standard according to Table 9.

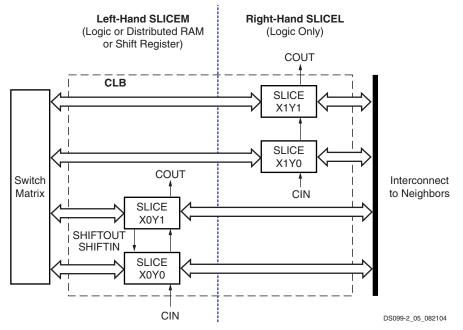

Figure 11: Arrangement of Slices within the CLB

# **Elements Within a Slice**

All four slices have the following elements in common: two logic function generators, two storage elements, wide-function multiplexers, carry logic, and arithmetic gates, as shown in Figure 12, page 24. Both the left-hand and right-hand slice pairs use these elements to provide logic, arithmetic, and ROM functions. Besides these, the left-hand pair supports two additional functions: storing data using Distributed RAM and shifting data with 16-bit registers. Figure 12 is a diagram of the left-hand slice; therefore, it represents a superset of the elements and connections to be found in all slices. See Function Generator, page 25 for more information.

The RAM-based function generator—also known as a Look-Up Table or LUT—is the main resource for implementing logic functions. Furthermore, the LUTs in each left-hand slice pair can be configured as Distributed RAM or a 16-bit shift register. For information on the former, refer to the chapter entitled "Using Look-Up Tables as Distributed RAM" in <u>UG331</u>; for information on the latter, refer to the chapter entitled "Using Look-Up Tables as Shift Registers" in <u>UG331</u>. The function generators located in the upper and lower portions of the slice are referred to as the "G" and "F", respectively.

The storage element, which is programmable as either a D-type flip-flop or a level-sensitive latch, provides a means for synchronizing data to a clock signal, among other uses. The storage elements in the upper and lower portions of the slice are called FFY and FFX, respectively.

Wide-function multiplexers effectively combine LUTs in order to permit more complex logic operations. Each slice has two of these multiplexers with F5MUX in the lower portion of the slice and FiMUX in the upper portion. Depending on the slice, FiMUX takes on the name F6MUX, F7MUX, or F8MUX. For more details on the multiplexers, refer to the chapter entitled "Using Dedicated Multiplexers" in <u>UG331</u>.

The carry chain, together with various dedicated arithmetic logic gates, support fast and efficient implementations of math operations. The carry chain enters the slice as CIN and exits as COUT. Five multiplexers control the chain: CYINIT, CYOF, and CYMUXF in the lower portion as well as CYOG and CYMUXG in the upper portion. The dedicated arithmetic logic includes the exclusive-OR gates XORG and XORF (upper and lower portions of the slice, respectively) as well as the AND gates GAND and FAND (upper and lower portions, respectively). For more details on the carry logic, refer to the chapter entitled "Using Carry and Arithmetic Logic" in <u>UG331</u>.

# Main Logic Paths

Central to the operation of each slice are two nearly identical data paths, distinguished using the terms *top* and *bottom*. The description that follows uses names associated with the bottom path. (The top path names appear in parentheses.) The basic path originates at an interconnect-switch matrix outside the CLB. Four lines, F1 through F4 (or G1 through G4 on the

The output frequency (f<sub>CLKEX</sub>) can be expressed as a function of the incoming clock frequency (f<sub>CLKIN</sub>) as follows:

Regarding the two attributes, it is possible to assign any combination of integer values, provided that two conditions are met:

- The two values fall within their corresponding ranges, as specified in Table 18.

- The f<sub>CLKFX</sub> frequency calculated from the above expression accords with the DCM's operating frequency specifications.

For example, if  $CLKFX_MULTIPLY = 5$  and  $CLKFX_DIVIDE = 3$ , then the frequency of the output clock signal would be 5/3 that of the input clock signal.

### **DFS Frequency Modes**

The DFS supports two operating modes, High Frequency and Low Frequency, with each specified over a different clock frequency range. The DFS\_FREQUENCY\_MODE attribute chooses between the two modes. When the attribute is set to LOW, the Low Frequency mode permits the two DFS outputs to operate over a low-to-moderate frequency range. When the attribute is set to HIGH, the High Frequency mode allows both these outputs to operate at the highest possible frequencies.

### DFS With or Without the DLL

The DFS component can be used with or without the DLL component:

Without the DLL, the DFS component multiplies or divides the CLKIN signal frequency according to the respective CLKFX\_MULTIPLY and CLKFX\_DIVIDE values, generating a clock with the new target frequency on the CLKFX and CLKFX180 outputs. Though classified as belonging to the DLL component, the CLKIN input is shared with the DFS component. This case does not employ feedback loop; therefore, it cannot correct for clock distribution delay.

With the DLL, the DFS operates as described in the preceding case, only with the additional benefit of eliminating the clock distribution delay. In this case, a feedback loop from the CLK0 output to the CLKFB input must be present.

The DLL and DFS components work together to achieve this phase correction as follows: Given values for the CLKFX\_MULTIPLY and CLKFX\_DIVIDE attributes, the DLL selects the delay element for which the output clock edge coincides with the input clock edge whenever mathematically possible. For example, when CLKFX\_MULTIPLY = 5 and CLKFX\_DIVIDE = 3, the input and output clock edges will coincide every three input periods, which is equivalent in time to five output periods.

Smaller CLKFX\_MULTIPLY and CLKFX\_DIVIDE values achieve faster lock times. With no factors common to the two attributes, alignment will occur once with every number of cycles equal to the CLKFX\_DIVIDE value. Therefore, it is recommended that the user reduce these values by factoring wherever possible. For example, given CLKFX\_MULTIPLY = 9 and CLKFX\_DIVIDE = 6, removing a factor of three yields CLKFX\_MULTIPLY = 3 and CLKFX\_DIVIDE = 2. While both value-pairs will result in the multiplication of clock frequency by 3/2, the latter value-pair will enable the DLL to lock more quickly.

#### Table 18: DFS Attributes

| Attribute          | Description                                            | Values               |

|--------------------|--------------------------------------------------------|----------------------|

| DFS_FREQUENCY_MODE | Chooses between High Frequency and Low Frequency modes | Low, High            |

| CLKFX_MULTIPLY     | Frequency multiplier constant                          | Integer from 2 to 32 |

| CLKFX_DIVIDE       | Frequency divisor constant                             | Integer from 1 to 32 |

#### Table 19: DFS Signals

| Signal   | Direction Description                                                                                                                                          |  |  |  |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| CLKFX    | CLKFX Output Multiplies the CLKIN frequency by the attribute-value ratio (CLKFX_MULTIPLY/CLKFX_DIVIDE) to generate a clock signal with a new target frequency. |  |  |  |

| CLKFX180 | CLKFX180 Output Generates a clock signal with same frequency as CLKFX, only shifted 180° out-of-phase.                                                         |  |  |  |

# DFS Clock Output Connections

There are two basic cases that determine how to connect the DFS clock outputs: on-chip and off-chip, which are illustrated in sections [a] and [c], respectively, of Figure 21. This is similar to what has already been described for the DLL component. See DLL Clock Output and Feedback Connections, page 34.

In the on-chip case, it is possible to connect either of the DFS's two output clock signals through general routing resources to the FPGA's internal registers. Either a Global Clock Buffer (BUFG) or a BUFGMUX affords access to the global clock network. The optional feedback loop is formed in this way, routing CLK0 to a global clock net, which in turn drives the CLKFB input.

In the off-chip case, the DFS's two output clock signals, plus CLK0 for an optional feedback loop, can exit the FPGA using output buffers (OBUF) to drive a clock network plus registers on the board. The feedback loop is formed by feeding the CLK0 signal back into the FPGA using an IBUFG, which directly accesses the global clock network, or an IBUF. Then, the global clock net is connected directly to the CLKFB input.

# Phase Shifter (PS)

The DCM provides two approaches to controlling the phase of a DCM clock output signal relative to the CLKIN signal: First, there are nine clock outputs that employ the DLL to achieve a desired phase relationship: CLK0, CLK90, CLK180, CLK270, CLK2X, CLK2X180, CLKDV CLKFX, and CLKFX180. These outputs afford "coarse" phase control.

The second approach uses the PS component described in this section to provide a still finer degree of control. The PS component is only available when the DLL is operating in its low-frequency mode. The PS component phase shifts the DCM output clocks by introducing a "fine phase shift" ( $T_{PS}$ ) between the CLKFB and CLKIN signals inside the DLL component. The user can control this fine phase shift down to a resolution of 1/256 of a CLKIN cycle or one tap delay (DCM\_TAP), whichever is greater. When in use, the PS component shifts the phase of all nine DCM clock output signals together. If the PS component is used together with a DCM clock output such as the CLK90, CLK180, CLK270, CLK2X180 and CLKFX180, then the fine phase shift of the former gets added to the coarse phase shift of the latter.

# **PS Component Enabling and Mode Selection**

The CLKOUT\_PHASE\_SHIFT attribute enables the PS component for use in addition to selecting between two operating modes. As described in Table 20, this attribute has three possible values: NONE, FIXED and VARIABLE. When CLKOUT\_PHASE\_SHIFT is set to NONE, the PS component is disabled and its inputs, PSEN, PSCLK, and PSINCDEC, must be tied to GND. The set of waveforms in section [a] of Figure 22 shows the disabled case, where the DLL maintains a zero-phase alignment of signals CLKFB and CLKIN upon which the PS component has no effect. The PS component is enabled by setting the attribute to either the FIXED or VARIABLE values, which select the Fixed Phase mode and the Variable Phase mode, respectively. These two modes are described in the sections that follow

# **Determining the Fine Phase Shift**

The user controls the phase shift of CLKFB relative to CLKIN by setting and/or adjusting the value of the PHASE\_SHIFT attribute. This value must be an integer ranging from –255 to +255. The PS component uses this value to calculate the desired fine phase shift ( $T_{PS}$ ) as a fraction of the CLKIN period ( $T_{CLKIN}$ ). Given values for PHASE-SHIFT and  $T_{CLKIN}$ , it is possible to calculate  $T_{PS}$  as follows:

$$T_{PS} = T_{CLKIN}(PHASE_SHIFT/256)$$

Equation 4

Both the Fixed Phase and Variable Phase operating modes employ this calculation. If the PHASE\_SHIFT value is zero, then CLKFB and CLKIN will be in phase, the same as when the PS component is disabled. When the PHASE\_SHIFT value is positive, the CLKFB signal will be shifted later in time with respect to CLKIN. If the attribute value is negative, the CLKFB signal will be shifted earlier in time with respect to CLKIN.

# The Fixed Phase Mode

This mode fixes the desired fine phase shift to a fraction of the  $T_{CLKIN}$ , as determined by Equation 4 and its user-selected PHASE\_SHIFT value P. The set of waveforms insection [b] of Figure 22 illustrates the relationship between CLKFB and CLKIN in the Fixed Phase mode. In the Fixed Phase mode, the PSEN, PSCLK and PSINCDEC inputs are not used and must be tied to GND. Fixed phase shift requires ISE software version 10.1.03 or later.

#### Notes:

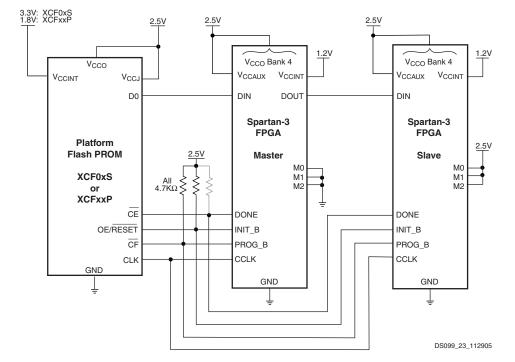

- There are two ways to use the DONE line. First, one may set the BitGen option DriveDone to "Yes" only for the last FPGA to be configured in the chain shown above (or for the single FPGA as may be the case). This enables the DONE pin to drive High; thus, no pull-up resistor is necessary. DriveDone is set to "No" for the remaining FPGAs in the chain. Second, DriveDone can be set to "No" for all FPGAs. Then all DONE lines are open-drain and require the pull-up resistor shown in grey. In most cases, a value between 3.3KΩ to 4.7KΩ is sufficient. However, when using DONE synchronously with a long chain of FPGAs, cumulative capacitance may necessitate lower resistor values (e.g. down to 330Ω) in order to ensure a rise time within one clock cycle.

- 2. For information on how to program the FPGA using 3.3V signals and power, see 3.3V-Tolerant Configuration Interface.

#### Figure 26: Connection Diagram for Master and Slave Serial Configuration

Slave Serial mode is selected by applying <111> to the mode pins (M0, M1, and M2). A pull-up on the mode pins makes slave serial the default mode if the pins are left unconnected.

#### **Master Serial Mode**

In Master Serial mode, the FPGA drives CCLK pin, which behaves as a bidirectional I/O pin. The FPGA in the center of Figure 26 is set for Master Serial mode and connects to the serial configuration PROM and to the CCLK inputs of any slave FPGAs in a configuration daisy-chain. The master FPGA drives the configuration clock on the CCLK pin to the Xilinx Serial PROM, which, in response, provides bit-serial data to the FPGA's DIN input. The FPGA accepts this data on each rising CCLK edge. After the master FPGA finishes configuring, it passes data on its DOUT pin to the next FPGA device in a daisy-chain. The DOUT data appears after the falling CCLK clock edge.

The Master Serial mode interface is identical to Slave Serial except that an internal oscillator generates the configuration clock (CCLK). A wide range of frequencies can be selected for CCLK, which always starts at a default frequency of 6 MHz. Configuration bits then switch CCLK to a higher frequency for the remainder of the configuration.

#### Slave Parallel Mode (SelectMAP)

The Parallel or SelectMAP modes support the fastest configuration. Byte-wide data is written into the FPGA with a BUSY flag controlling the flow of data. An external source provides 8-bit-wide data, CCLK, an active-Low Chip Select (CS\_B) signal and an active-Low Write signal (RDWR\_B). If BUSY is asserted (High) by the FPGA, the data must be held until BUSY goes Low. Data can also be read using the Slave Parallel mode. If RDWR\_B is asserted, configuration data is read out of the FPGA as part of a readback operation.

After configuration, it is possible to use any of the Multipurpose pins (DIN/D0-D7, DOUT/BUSY, INIT\_B, CS\_B, and RDWR\_B) as User I/Os. To do this, simply set the BitGen option *Persist* to *No* and assign the desired signals to multipurpose configuration pins using the Xilinx development software. Alternatively, it is possible to continue using the configuration port

### Table 47: Output Timing Adjustments for IOB (Cont'd)

|                                           | Add the Adju | stment Below |       |       |    |

|-------------------------------------------|--------------|--------------|-------|-------|----|

| Convert Output Time from LVC<br>Following | Speed Grade  |              | Units |       |    |

|                                           | -5           | -4           |       |       |    |

| HSLVDCI_25                                |              |              | 0.27  | 0.31  | ns |

| HSLVDCI_33                                |              |              | 0.28  | 0.32  | ns |

| HSTL_I                                    |              |              | 0.60  | 0.69  | ns |

| HSTL_I_DCI                                |              |              | 0.59  | 0.68  | ns |

| HSTL_III                                  |              |              | 0.19  | 0.22  | ns |

| HSTL_III_DCI                              |              |              | 0.20  | 0.23  | ns |

| HSTL_I_18                                 |              |              | 0.18  | 0.21  | ns |

| HSTL_I_DCI_18                             |              |              | 0.17  | 0.19  | ns |

| HSTL_II_18                                |              |              | -0.02 | -0.01 | ns |

| HSTL_II_DCI_18                            |              |              | 0.75  | 0.86  | ns |

| HSTL_III_18                               |              |              | 0.28  | 0.32  | ns |

| HSTL_III_DCI_18                           |              |              | 0.28  | 0.32  | ns |

| LVCMOS12                                  | Slow         | 2 mA         | 7.60  | 8.73  | ns |

|                                           |              | 4 mA         | 7.42  | 8.53  | ns |

|                                           |              | 6 mA         | 6.67  | 7.67  | ns |

|                                           | Fast         | 2 mA         | 3.16  | 3.63  | ns |

|                                           |              | 4 mA         | 2.70  | 3.10  | ns |

|                                           |              | 6 mA         | 2.41  | 2.77  | ns |

| LVCMOS15                                  | Slow         | 2 mA         | 4.55  | 5.23  | ns |

|                                           |              | 4 mA         | 3.76  | 4.32  | ns |

|                                           |              | 6 mA         | 3.57  | 4.11  | ns |

|                                           |              | 8 mA         | 3.55  | 4.09  | ns |

|                                           |              | 12 mA        | 3.00  | 3.45  | ns |

|                                           | Fast         | 2 mA         | 3.11  | 3.57  | ns |

|                                           |              | 4 mA         | 1.71  | 1.96  | ns |

|                                           |              | 6 mA         | 1.44  | 1.66  | ns |

|                                           |              | 8 mA         | 1.26  | 1.44  | ns |

|                                           |              | 12 mA        | 1.11  | 1.27  | ns |

| LVDCI_15                                  |              |              | 1.51  | 1.74  | ns |

| LVDCI_DV2_15                              |              |              | 1.32  | 1.52  | ns |

### Timing Measurement Methodology

When measuring timing parameters at the programmable I/Os, different signal standards call for different test conditions. Table 48 presents the conditions to use for each standard.

The method for measuring Input timing is as follows: A signal that swings between a Low logic level of  $V_L$  and a High logic level of  $V_H$  is applied to the Input under test. Some standards also require the application of a bias voltage to the  $V_{REF}$  pins of a given bank to properly set the input-switching threshold. The measurement point of the Input signal ( $V_M$ ) is commonly located halfway between  $V_L$  and  $V_H$ .

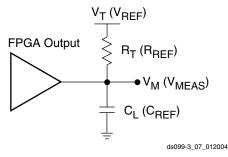

The Output test setup is shown in Figure 35. A termination voltage  $V_T$  is applied to the termination resistor  $R_T$ , the other end of which is connected to the Output. For each standard,  $R_T$  and  $V_T$  generally take on the standard values recommended for minimizing signal reflections. If the standard does not ordinarily use terminations (e.g., LVCMOS, LVTTL), then  $R_T$  is set to 1M $\Omega$  to indicate an open connection, and  $V_T$  is set to zero. The same measurement point ( $V_M$ ) that was used at the Input is also used at the Output.

Notes:

1. The names shown in parentheses are used in the IBIS file.

Figure 35: Output Test Setup

| Signal Standard |                      | Inputs                      |                          | Out                       | Inputs and<br>Outputs     |                    |

|-----------------|----------------------|-----------------------------|--------------------------|---------------------------|---------------------------|--------------------|

| (IOSTANDARD)    | V <sub>REF</sub> (V) | V <sub>L</sub> (V)          | V <sub>H</sub> (V)       | <b>R</b> <sub>T</sub> (Ω) | <b>V</b> <sub>T</sub> (V) | V <sub>M</sub> (V) |

| Single-Ended    |                      |                             |                          |                           |                           |                    |

| GTL             | 0.8                  | V <sub>REF</sub> – 0.2      | V <sub>REF</sub> + 0.2   | 25                        | 1.2                       | V <sub>REF</sub>   |

| GTL_DCI         |                      |                             |                          | 50                        | 1.2                       |                    |

| GTLP            | 1.0                  | V <sub>REF</sub> – 0.2      | V <sub>REF</sub> + 0.2   | 25                        | 1.5                       | V <sub>REF</sub>   |

| GTLP_DCI        |                      |                             |                          | 50                        | 1.5                       |                    |

| HSLVDCI_15      | 0.9                  | V <sub>REF</sub> – 0.5      | V <sub>REF</sub> + 0.5   | 1M                        | 0                         | 0.75               |

| HSLVDCI_18      |                      |                             |                          |                           |                           | 0.90               |

| HSLVDCI_25      |                      |                             |                          |                           |                           | 1.25               |

| HSLVDCI_33      |                      |                             |                          |                           |                           | 1.65               |

| HSTL_I          | 0.75                 | V <sub>REF</sub> – 0.5      | V <sub>REF</sub> + 0.5   | 50                        | 0.75                      | V <sub>REF</sub>   |

| HSTL_I_DCI      |                      |                             |                          |                           |                           |                    |

| HSTL_III        | 0.90                 | V <sub>REF</sub> – 0.5      | 5 V <sub>REF</sub> + 0.5 | 50                        | 1.5                       | V <sub>REF</sub>   |

| HSTL_III_DCI    |                      |                             |                          |                           |                           |                    |

| HSTL_I_18       | 0.90                 | 0.90 V <sub>REF</sub> – 0.5 | V <sub>REF</sub> + 0.5   | 50                        | 0.9                       | V <sub>REF</sub>   |

| HSTL_I_DCI_18   |                      |                             |                          |                           |                           |                    |

| HSTL_II_18      | 0.90                 | 0.90 V <sub>REF</sub> – 0.5 | V <sub>REF</sub> + 0.5   | 50                        | 0.9                       | V <sub>REF</sub>   |

| HSTL_II_DCI_18  |                      |                             |                          |                           |                           |                    |

# Spartan-3 FPGA Family: DC and Switching Characteristics

# Table 50: Recommended Number of Simultaneously Switching Outputs per V<sub>CCO</sub>/GND Pair

| Signal Standard<br>(IOSTANDARD) |      | Package |       |       |       |                                              |    |

|---------------------------------|------|---------|-------|-------|-------|----------------------------------------------|----|

|                                 |      | VQ100   | TQ144 | PQ208 | CP132 | FT256, FG320, FG456,<br>FG676, FG900, FG1156 |    |

| Single-Ended Stand              | ards |         |       | ·     |       |                                              |    |

| GTL                             |      |         | 0     | 0     | 0     | 1                                            | 14 |

| GTL_DCI                         |      |         | 0     | 0     | 0     | 1                                            | 14 |

| GTLP                            |      |         | 0     | 0     | 0     | 1                                            | 19 |

| GTLP_DCI                        |      |         | 0     | 0     | 0     | 1                                            | 19 |

| HSLVDCI_15                      |      |         | 6     | 6     | 6     | 6                                            | 14 |

| HSLVDCI_18                      |      |         | 7     | 7     | 7     | 7                                            | 10 |

| HSLVDCI_25                      |      |         | 7     | 7     | 7     | 7                                            | 11 |

| HSLVDCI_33                      |      |         | 10    | 10    | 10    | 10                                           | 10 |

| HSTL_I                          |      |         | 11    | 11    | 11    | 11                                           | 17 |

| HSTL_I_DCI                      |      |         | 11    | 11    | 11    | 11                                           | 17 |

| HSTL_III                        |      |         | 7     | 7     | 7     | 7                                            | 7  |

| HSTL_III_DCI                    |      |         | 7     | 7     | 7     | 7                                            | 7  |

| HSTL_I_18                       |      |         | 13    | 13    | 13    | 13                                           | 17 |

| HSTL_I_DCI_18                   |      |         | 13    | 13    | 13    | 13                                           | 17 |

| HSTL_II_18                      |      |         | 9     | 9     | 9     | 9                                            | 9  |

| HSTL_II_DCI_18                  |      |         | 9     | 9     | 9     | 9                                            | 9  |

| HSTL_III_18                     |      |         | 8     | 8     | 8     | 8                                            | 8  |

| HSTL_III_DCI_18                 |      | 8       | 8     | 8     | 8     | 8                                            |    |

| LVCMOS12                        | Slow | 2       | 17    | 17    | 17    | 17                                           | 55 |

|                                 |      | 4       | 13    | 13    | 13    | 13                                           | 32 |

|                                 |      | 6       | 10    | 10    | 10    | 10                                           | 18 |

|                                 | Fast | 2       | 12    | 12    | 12    | 12                                           | 31 |

|                                 |      | 4       | 11    | 11    | 11    | 11                                           | 13 |

|                                 |      | 6       | 9     | 9     | 9     | 9                                            | 9  |

| LVCMOS15                        | Slow | 2       | 16    | 12    | 12    | 19                                           | 55 |

|                                 |      | 4       | 8     | 7     | 7     | 9                                            | 31 |

|                                 |      | 6       | 7     | 7     | 7     | 9                                            | 18 |

|                                 |      | 8       | 6     | 6     | 6     | 6                                            | 15 |

|                                 |      | 12      | 5     | 5     | 5     | 5                                            | 10 |

|                                 | Fast | 2       | 10    | 10    | 10    | 13                                           | 25 |

|                                 |      | 4       | 6     | 7     | 7     | 7                                            | 16 |

|                                 |      | 6       | 7     | 7     | 7     | 7                                            | 13 |

|                                 |      | 8       | 6     | 6     | 6     | 6                                            | 11 |

|                                 |      | 12      | 6     | 6     | 6     | 6                                            | 7  |

| Date     | Version | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 05/25/07 | 2.2     | Improved absolute maximum voltage specifications in Table 28, providing additional overshoot allowance.<br>Improved XC3S50 HBM ESD to 2000V in Table 28. Based on extensive 90 nm production data, improved (reduced) the maximum quiescent current limits for the I <sub>CCINTQ</sub> and I <sub>CCOQ</sub> specifications in Table 34.<br>Widened the recommended voltage range for the PCI standard and clarified the hysteresis footnote in Table 35. Noted restriction on combining differential outputs in Table 38. Updated footnote 1 in Table 64.                                                                                                                                                                                                                                                                                               |

| 11/30/07 | 2.3     | Updated 3.3V VCCO max from 3.45V to 3.465V in Table 32 and elsewhere. Reduced $t_{ICCK}$ minimum from 0.50 $\mu$ s to 0.25 $\mu$ s in Table 65. Updated links to technical documentation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 06/25/08 | 2.4     | Clarified dual marking. Added Mask and Fab Revisions. Added references to <u>XAPP459</u> in Table 28 and Table 32. Removed absolute minimum and added footnote referring to timing analyzer for minimum delay values. Added HSLVDCI to Table 48 and Table 50. Updated t <sub>DICK</sub> in Table 51 to match largest possible value in speed file. Updated formatting and links.                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 12/04/09 | 2.5     | Updated notes 2 and 3 in Table 28. Removed silicon process specific information and revised notes in Table 30. Updated note 3 in Table 32. Updated note 3 in Table 34. Updated note 5 in Table 35. Updated $V_{OL}$ max and $V_{OH}$ min for SSTL2_II in Table 36. Updated note 5 in Table 36. Updated JTAG Waveforms in Figure 39. Updated $V_{ICM}$ max for LVPECL_25 in Table 37. Updated RT and VT for LVDS_25_DCI in Table 48. Updated Simultaneously Switching Output Guidelines. Noted that the CP132 package is being discontinued in Table 49. Removed minimum values for $T_{MULTCK}$ clock-to-output times in Table 54. Updated footnote 3 in Table 58. Removed minimum values for T <sub>MULTCK</sub> propagation times in Table 55. Removed silicon process specific information and revised notes in Table 61. Updated Phase Shifter (PS). |

| 10/29/12 | 3.0     | Added Notice of Disclaimer. Per <u>XCN07022</u> , updated the discontinued FG1156 and FGG1156 package discussion throughout document. Per <u>XCN08011</u> , updated the discontinued CP132 and CPG132 package discussion throughout document. Revised description of V <sub>IN</sub> in Table 32 and added note 7. Added note 4 to Table 33. This product is not recommended for new designs.                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

### Table 70: Spartan-3 FPGA Pin Definitions (Cont'd)

| Pin Name                                                                                                                                                    | Direction                                                                                | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GCLK: Global clock bu                                                                                                                                       | iffer inputs                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| IO_Lxxy_#/GCLK0,<br>IO_Lxxy_#/GCLK1,<br>IO_Lxxy_#/GCLK2,<br>IO_Lxxy_#/GCLK3,<br>IO_Lxxy_#/GCLK4,<br>IO_Lxxy_#/GCLK5,<br>IO_Lxxy_#/GCLK6,<br>IO_Lxxy_#/GCLK7 | Input if connected to global clock<br>buffers<br>Otherwise, same as I/O                  | <b>Global Buffer Input:</b><br>Direct input to a low-skew global clock buffer. If not connected to a global clock buffer, this pin is a user I/O.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| VREF: I/O bank input r                                                                                                                                      | eference voltage pins                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| IO_Lxxy_#/VREF_# or<br>IO/VREF_#                                                                                                                            | Voltage supply input when VREF<br>pins are used within a bank.<br>Otherwise, same as I/O | Input Buffer Reference Voltage for Special I/O Standards (per<br>bank):<br>If required to support special I/O standards, all the VREF pins within a bank<br>connect to a input threshold voltage source.<br>If not used as input reference voltage pins, these pins are available as<br>individual user-I/O pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| CONFIG: Dedicated co<br>HSWAP_EN pin)                                                                                                                       | nfiguration pins (pull-up resisto                                                        | r to VCCAUX always active during configuration, regardless of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| CCLK                                                                                                                                                        | Input in Slave configuration<br>modes<br>Output in Master configuration<br>modes         | <b>Configuration Clock:</b><br>The configuration clock signal synchronizes configuration data. This pin<br>has an internal pull-up resistor to VCCAUX during configuration.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| PROG_B                                                                                                                                                      | Input                                                                                    | <b>Program/Configure Device:</b><br>Active Low asynchronous reset to configuration logic. Asserting PROG_B<br>Low for an extended period delays the configuration process. This pin has<br>an internal pull-up resistor to VCCAUX during configuration.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| DONE                                                                                                                                                        | Bidirectional with open-drain or<br>totem-pole Output                                    | Configuration Done, Delay Start-up Sequence:<br>A Low-to-High output transition on this bidirectional pin signals the end of<br>the configuration process.<br>The FPGA produces a Low-to-High transition on this pin to indicate that the<br>configuration process is complete. The DriveDone bitstream generation<br>option defines whether this pin functions as a totem-pole output that<br>actively drives High or as an open-drain output. An open-drain output<br>requires a pull-up resistor to produce a High logic level. The open-drain<br>option permits the DONE lines of multiple FPGAs to be tied together, so<br>that the common node transitions High only after all of the FPGAs have<br>completed configuration. Externally holding the open-drain output Low<br>delays the start-up sequence, which marks the transition to user mode. |

| M0, M1, M2                                                                                                                                                  | Input                                                                                    | <b>Configuration Mode Selection:</b><br>These inputs select the configuration mode. The logic levels applied to the mode pins are sampled on the rising edge of INIT_B. See Table 75. These pins have an internal pull-up resistor to VCCAUX during configuration, making Slave Serial the default configuration mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| HSWAP_EN                                                                                                                                                    | Input                                                                                    | <b>Disable Pull-up Resistors During Configuration:</b><br>A Low on this pin enables pull-up resistors on all pins that are not actively involved in the configuration process. A High value disables all pull-ups, allowing the non-configuration pins to float.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| JTAG: JTAG interface                                                                                                                                        | e pins (pull-up resistor to VCCA                                                         | UX always active during configuration, regardless of HSWAP_EN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| тск                                                                                                                                                         | Input                                                                                    | <b>JTAG Test Clock:</b><br>The TCK clock signal synchronizes all JTAG port operations. This pin has<br>an internal pull-up resistor to VCCAUX during configuration.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

www.xilinx.com

#### Table 70: Spartan-3 FPGA Pin Definitions (Cont'd)

| Pin Name            | Direction               | Description                                                                                                                                                                                                                                    |

|---------------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TDI                 | Input                   | <b>JTAG Test Data Input:</b><br>TDI is the serial data input for all JTAG instruction and data registers. This<br>pin has an internal pull-up resistor to VCCAUX during configuration.                                                         |

| TMS                 | Input                   | <b>JTAG Test Mode Select:</b><br>The serial TMS input controls the operation of the JTAG port. This pin has an internal pull-up resistor to VCCAUX during configuration.                                                                       |

| TDO                 | Output                  | <b>JTAG Test Data Output:</b><br>TDO is the serial data output for all JTAG instruction and data registers.<br>This pin has an internal pull-up resistor to VCCAUX during configuration.                                                       |

| VCCO: I/O bank out  | out voltage supply pins |                                                                                                                                                                                                                                                |

| VCCO_#              | Supply                  | <b>Power Supply for Output Buffer Drivers (per bank):</b><br>These pins power the output drivers within a specific I/O bank.                                                                                                                   |

| VCCAUX: Auxiliary   | voltage supply pins     |                                                                                                                                                                                                                                                |

| VCCAUX              | Supply                  | Power Supply for Auxiliary Circuits:<br>+2.5V power pins for auxiliary circuits, including the Digital Clock<br>Managers (DCMs), the dedicated configuration pins (CONFIG), and the<br>dedicated JTAG pins. All VCCAUX pins must be connected. |

| VCCINT: Internal co | re voltage supply pins  |                                                                                                                                                                                                                                                |

| VCCINT              | Supply                  | <b>Power Supply for Internal Core Logic:</b><br>+1.2V power pins for the internal logic. All pins must be connected.                                                                                                                           |

| GND: Ground supply  | y pins                  |                                                                                                                                                                                                                                                |

| GND                 | Supply                  | <b>Ground:</b><br>Ground pins, which are connected to the power supply's return path. All pins must be connected.                                                                                                                              |

| N.C.: Unconnected   | backage pins            |                                                                                                                                                                                                                                                |

| N.C.                |                         | Unconnected Package Pin:<br>These package pins are unconnected.                                                                                                                                                                                |

#### Notes:

1. All unused inputs and bidirectional pins must be tied either High or Low. For unused enable inputs, apply the level that disables the associated function. One common approach is to activate internal pull-up or pull-down resistors. An alternative approach is to externally connect the pin to either VCCO or GND.

2. All outputs are of the totem-pole type — i.e., they can drive High as well as Low logic levels — except for the cases where "Open Drain" is indicated. The latter can only drive a Low logic level and require a pull-up resistor to produce a High logic level.

# **Detailed, Functional Pin Descriptions**

### I/O Type: Unrestricted, General-purpose I/O Pins

After configuration, I/O-type pins are inputs, outputs, bidirectional I/O, three-state outputs, open-drain outputs, or open-source outputs, as defined in the application

Pins labeled "IO" support all SelectIO<sup>™</sup> interface signal standards except differential standards. A given device at most only has a few of these pins.

A majority of the general-purpose I/O pins are labeled in the format "IO\_Lxxy\_#". These pins support all SelectIO signal standards, including the differential standards such as LVDS, ULVDS, BLVDS, RSDS, or LDT.

For additional information, see IOBs, page 10

# VREF: User I/O or Input Buffer Reference Voltage for Special Interface Standards

These pins are individual user-I/O pins unless collectively they supply an input reference voltage, VREF\_#, for any SSTL, HSTL, GTL, or GTLP I/Os implemented in the associated I/O bank. The '#' character in the pin name represents an integer, 0 through 7, that indicates the associated I/O bank.

The VREF function becomes active for this pin whenever a signal standard requiring a reference voltage is used in the associated bank. If used as a user I/O, then each pin behaves as an independent I/O described in the I/O type section. If used for a reference voltage within a bank, then *all* VREF pins within the bank must be connected to the same reference voltage.

Spartan-3 devices are designed and characterized to support certain I/O standards when VREF is connected to +1.25V, +1.10V, +1.00V, +0.90V, +0.80V, and +0.75V. During configuration, the VREF pins behave exactly like user-I/O pins.

If designing for footprint compatibility across the range of devices in a specific package, and if the VREF\_# pins within a bank connect to an input reference voltage, then also connect any N.C. (not connected) pins on the smaller devices in that package to the input reference voltage. More details are provided later for each package type.

# N.C. Type: Unconnected Package Pins

Pins marked as "N.C." are unconnected for the specific device/package combination. For other devices in this same package, this pin may be used as an I/O or VREF connection. In both the pinout tables and the footprint diagrams, unconnected pins are noted with either a black diamond symbol ( $\blacklozenge$ ) or a black square symbol ( $\blacksquare$ ).

If designing for footprint compatibility across multiple device densities, check the pin types of the other Spartan-3 devices available in the same footprint. If the N.C. pin matches to VREF pins in other devices, and the VREF pins are used in the associated I/O bank, then connect the N.C. to the VREF voltage source.

# VCCO Type: Output Voltage Supply for I/O Bank

Each I/O bank has its own set of voltage supply pins that determines the output voltage for the output buffers in the I/O bank. Furthermore, for some I/O standards such as LVCMOS, LVCMOS25, LVTTL, etc., VCCO sets the input threshold voltage on the associated input buffers.

Spartan-3 devices are designed and characterized to support various I/O standards for VCCO values of +1.2V, +1.5V, +1.8V, +2.5V, and +3.3V.

Most VCCO pins are labeled as VCCO\_# where the '#' symbol represents the associated I/O bank number, an integer ranging from 0 to 7. In the 144-pin TQFP package (TQ144) however, the VCCO pins along an edge of the device are combined into a single VCCO input. For example, the VCCO inputs for Bank 0 and Bank 1 along the top edge of the package are combined and relabeled VCCO\_TOP. The bottom, left, and right edges are similarly combined.

In Serial configuration mode, VCCO\_4 must be at a level compatible with the attached configuration memory or data source. In Parallel configuration mode, both VCCO\_4 and VCCO\_5 must be at the same compatible voltage level.

All VCCO inputs to a bank must be connected together and to the voltage supply. Furthermore, there must be sufficient supply decoupling to guarantee problem-free operation, as described in <u>XAPP623</u>: *Power Distribution System (PDS) Design: Using Bypass/Decoupling Capacitors*.

# VCCINT Type: Voltage Supply for Internal Core Logic

Internal core logic circuits such as the configurable logic blocks (CLBs) and programmable interconnect operate from the VCCINT voltage supply inputs. VCCINT must be +1.2V.

All VCCINT inputs must be connected together and to the +1.2V voltage supply. Furthermore, there must be sufficient supply decoupling to guarantee problem-free operation, as described in <u>XAPP623</u>.

# VCCAUX Type: Voltage Supply for Auxiliary Logic

The VCCAUX pins supply power to various auxiliary circuits, such as to the Digital Clock Managers (DCMs), the JTAG pins, and to the dedicated configuration pins (CONFIG type). VCCAUX must be +2.5V.

### Table 91: TQ144 Package Pinout (Cont'd)

| Bank | XC3S50, XC3S200,<br>XC3S400 Pin Name | TQ144 Pin<br>Number | Туре |

|------|--------------------------------------|---------------------|------|

| 2    | IO_L23N_2/VREF_2                     | P98                 | VREF |

| 2    | IO_L23P_2                            | P97                 | I/O  |

| 2    | IO_L24N_2                            | P96                 | I/O  |

| 2    | IO_L24P_2                            | P95                 | I/O  |

| 2    | IO_L40N_2                            | P93                 | I/O  |

| 2    | IO_L40P_2/VREF_2                     | P92                 | VREF |

| 3    | IO                                   | P76                 | I/O  |

| 3    | IO_L01N_3/VRP_3                      | P74                 | DCI  |

| 3    | IO_L01P_3/VRN_3                      | P73                 | DCI  |

| 3    | IO_L20N_3                            | P78                 | I/O  |

| 3    | IO_L20P_3                            | P77                 | I/O  |

| 3    | IO_L21N_3                            | P80                 | I/O  |

| 3    | IO_L21P_3                            | P79                 | I/O  |

| 3    | IO_L22N_3                            | P83                 | I/O  |

| 3    | IO_L22P_3                            | P82                 | I/O  |

| 3    | IO_L23N_3                            | P85                 | I/O  |

| 3    | IO_L23P_3/VREF_3                     | P84                 | VREF |

| 3    | IO_L24N_3                            | P87                 | I/O  |

| 3    | IO_L24P_3                            | P86                 | I/O  |

| 3    | IO_L40N_3/VREF_3                     | P90                 | VREF |

| 3    | IO_L40P_3                            | P89                 | I/O  |

| 4    | IO/VREF_4                            | P70                 | VREF |

| 4    | IO_L01N_4/VRP_4                      | P69                 | DCI  |

| 4    | IO_L01P_4/VRN_4                      | P68                 | DCI  |

| 4    | IO_L27N_4/DIN/D0                     | P65                 | DUAL |

| 4    | IO_L27P_4/D1                         | P63                 | DUAL |

| 4    | IO_L30N_4/D2                         | P60                 | DUAL |

| 4    | IO_L30P_4/D3                         | P59                 | DUAL |

| 4    | IO_L31N_4/INIT_B                     | P58                 | DUAL |

| 4    | IO_L31P_4/DOUT/BUSY                  | P57                 | DUAL |

| 4    | IO_L32N_4/GCLK1                      | P56                 | GCLK |

| 4    | IO_L32P_4/GCLK0                      | P55                 | GCLK |

| 5    | IO/VREF_5                            | P44                 | VREF |

| 5    | IO_L01N_5/RDWR_B                     | P41                 | DUAL |

| 5    | IO_L01P_5/CS_B                       | P40                 | DUAL |

| 5    | IO_L28N_5/D6                         | P47                 | DUAL |

| 5    | IO_L28P_5/D7                         | P46                 | DUAL |

| 5    | IO_L31N_5/D4                         | P51                 | DUAL |

| 5    | IO_L31P_5/D5                         | P50                 | DUAL |

| 5    | IO_L32N_5/GCLK3                      | P53                 | GCLK |

www.xilinx.com

### Table 98: FG320 Package Pinout (Cont'd)

| Bank | XC3S400, XC3S1000, XC3S1500<br>Pin Name | FG320<br>Pin Number | Туре |

|------|-----------------------------------------|---------------------|------|

| 6    | IO_L01P_6/VRN_6                         | T2                  | DCI  |

| 6    | IO_L16N_6                               | U1                  | I/O  |

| 6    | IO_L16P_6                               | T1                  | I/O  |

| 6    | IO_L17N_6                               | R2                  | I/O  |

| 6    | IO_L17P_6/VREF_6                        | R1                  | VREF |

| 6    | IO_L19N_6                               | R3                  | I/O  |

| 6    | IO_L19P_6                               | P3                  | I/O  |

| 6    | IO_L20N_6                               | P2                  | I/O  |

| 6    | IO_L20P_6                               | P1                  | I/O  |

| 6    | IO_L21N_6                               | N4                  | I/O  |

| 6    | IO_L21P_6                               | P4                  | I/O  |

| 6    | IO_L22N_6                               | N5                  | I/O  |

| 6    | IO_L22P_6                               | M5                  | I/O  |

| 6    | IO_L23N_6                               | M3                  | I/O  |

| 6    | IO_L23P_6                               | M4                  | I/O  |

| 6    | IO_L24N_6/VREF_6                        | N2                  | VREF |

| 6    | IO_L24P_6                               | M1                  | I/O  |

| 6    | IO_L27N_6                               | L6                  | I/O  |

| 6    | IO_L27P_6                               | L5                  | I/O  |

| 6    | IO_L34N_6/VREF_6                        | L3                  | VREF |

| 6    | IO_L34P_6                               | L4                  | I/O  |

| 6    | IO_L35N_6                               | L2                  | I/O  |

| 6    | IO_L35P_6                               | L1                  | I/O  |

| 6    | IO_L39N_6                               | K5                  | I/O  |

| 6    | IO_L39P_6                               | K4                  | I/O  |

| 6    | IO_L40N_6                               | K1                  | I/O  |

| 6    | IO_L40P_6/VREF_6                        | K2                  | VREF |

| 6    | VCCO_6                                  | K7                  | VCCO |

| 6    | VCCO_6                                  | L7                  | VCCO |

| 6    | VCCO_6                                  | N3                  | VCCO |

| 7    | Ю                                       | J6                  | I/O  |

| 7    | IO_L01N_7/VRP_7                         | C3                  | DCI  |

| 7    | IO_L01P_7/VRN_7                         | C2                  | DCI  |

| 7    | IO_L16N_7                               | C1                  | I/O  |

| 7    | IO_L16P_7/VREF_7                        | B1                  | VREF |

| 7    | IO_L17N_7                               | D1                  | I/O  |

| 7    | IO_L17P_7                               | D2                  | I/O  |

| 7    | IO_L19N_7/VREF_7                        | E3                  | VREF |

| 7    | IO_L19P_7                               | D3                  | I/O  |

| 7    | IO_L20N_7                               | E2                  | I/O  |

|                               | 12               | 14                        | Ban                          |                    | 47                 | 10                      | 10                      | 20                      | 24                     | 22                      |        |        |

|-------------------------------|------------------|---------------------------|------------------------------|--------------------|--------------------|-------------------------|-------------------------|-------------------------|------------------------|-------------------------|--------|--------|

| 12                            | <b>13</b><br>I/O | 1/0                       | 15<br>I/O                    | 16<br>1/0          | 17                 | 18<br>I/O               | 19<br>1/0               | 20<br>TMO               | 21<br>Tor              | 22                      |        |        |

| I/O                           | L30N_1           |                           | L25P_1                       | •                  | VCCAUX             |                         | L06N_1<br>VREF_1        | TMS                     | ТСК                    | GND                     | Α      |        |

| I/O<br>L32N_1<br>GCLK5        | I/O<br>L30P_1    | I/O<br>L28P_1             | I/O<br>L25N_1                | I/O<br>L22P_1<br>♦ | I/O<br>L16N_1      | I/O<br>L10P_1           | I/O<br>L06P_1           | I/O<br>L01P_1<br>VRN_1  | GND                    | TDO                     | в      |        |

| I/O<br>L32P_1<br>GCLK4        | I/O<br>L29N_1    | GND                       | VCCO_1                       | I/O<br>L19N_1<br>♦ | I/O<br>L16P_1      | I/O<br>L09N_1           | I/O<br>L01N_1<br>VRP_1  | I/O<br>L01N_2<br>VRP_2  | I/O<br>L01P_2<br>VRN_2 | I/O                     | С      |        |

| I/O<br>L31N_1<br>VREF_1       | I/O<br>L29P_1    | I/O<br>L27N_1             | I/O<br>L24N_1                | I/O<br>L19P_1<br>♦ | I/O<br>L15N_1      | I/O<br>L09P_1           | I/O<br>L16P_2           | I/O<br>L16N_2           | l/O<br>L17N_2          | I/O<br>L17P_2<br>VREF_2 | D      |        |

| I/O<br>L31P_1                 | IO<br>VREF_1     | I/O<br>L27P_1             | I/O<br>L24P_1                | I/O                | I/O<br>L15P_1      | I/O<br>L19N_2           | I/O<br>L20N_2           | I/O<br>L20P_2           | I/O<br>L21N_2          | l/O<br>L21P_2           | Е      |        |

| I/O                           | I/O              | IO<br>VREF_1<br>◆         | VCCO_1                       | I/O                | I/O                | l/O<br>L19P_2           | I/O<br>L23N_2<br>VREF_2 | I/O<br>L24N_2           | I/O<br>L24P_2          | VCCAUX                  | F      |        |

| VCCO_1                        | VCCO_1           | VCCO_1                    | VCCINT                       | VCCINT             | 1/0<br>L22N_2      | l/O<br>L22P_2           | I/O<br>L23P_2           | I/O<br>L26N_2<br>♦      | I/O<br>L27N_2          | l/O<br>L27P_2           | G      | Bank 2 |

| $\mathbf{X}$                  | $\times$         | $\times$                  | $\times$                     | VCCINT             | VCCO_2             | I/O<br>L28N_2<br>♦      | I/O<br>L26P_2<br>♦      | VCCO_2                  | I/O<br>L29N_2<br>♦     | I/O<br>L29P_2<br>♦      | н      |        |

| GND                           | GND              | GND                       | $\times$                     | VCCO_2             | I/O<br>L28P_2<br>♦ | I/O<br>L31N_2<br>◆      | I/O<br>L31P_2<br>♦      | GND                     | I/O<br>L32N_2<br>♦     | I/O<br>L32P_2<br>♦      | J      |        |

| GND                           | GND              | GND                       | $\times$                     | VCCO_2             | I/O<br>L33N_2<br>♦ | I/O<br>L33P_2<br>♦      | I/O<br>L34N_2<br>VREF_2 | I/O<br>L34P_2           | I/O<br>L35N_2          | I/O<br>L35P_2           | к      |        |

| GND                           | GND              | GND                       | $\times$                     | VCCO_2             | I/O<br>L38N_2      | I/O<br>L38P_2           | I/O<br>L39N_2           | I/O<br>L39P_2           | I/O<br>L40N_2          | I/O<br>L40P_2<br>VREF_2 | L      |        |

| GND                           | GND              | GND                       | $\times$                     | VCCO_3             | I/O<br>L38P_3      | I/O<br>L38N_3           | I/O<br>L39P_3           | I/O<br>L39N_3           | I/O<br>L40P_3          | I/O<br>L40N_3<br>VREF_3 | м      |        |