# E·XFL

Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                              |

|--------------------------------|--------------------------------------------------------------|

| Product Status                 | Active                                                       |

| Number of LABs/CLBs            | 5120                                                         |

| Number of Logic Elements/Cells | 46080                                                        |

| Total RAM Bits                 | 737280                                                       |

| Number of I/O                  | 489                                                          |

| Number of Gates                | 200000                                                       |

| Voltage - Supply               | 1.14V ~ 1.26V                                                |

| Mounting Type                  | Surface Mount                                                |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                              |

| Package / Case                 | 676-BGA                                                      |

| Supplier Device Package        | 676-FBGA (27x27)                                             |

| Purchase URL                   | https://www.e-xfl.com/product-detail/xilinx/xc3s2000-5fg676c |

|                                |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

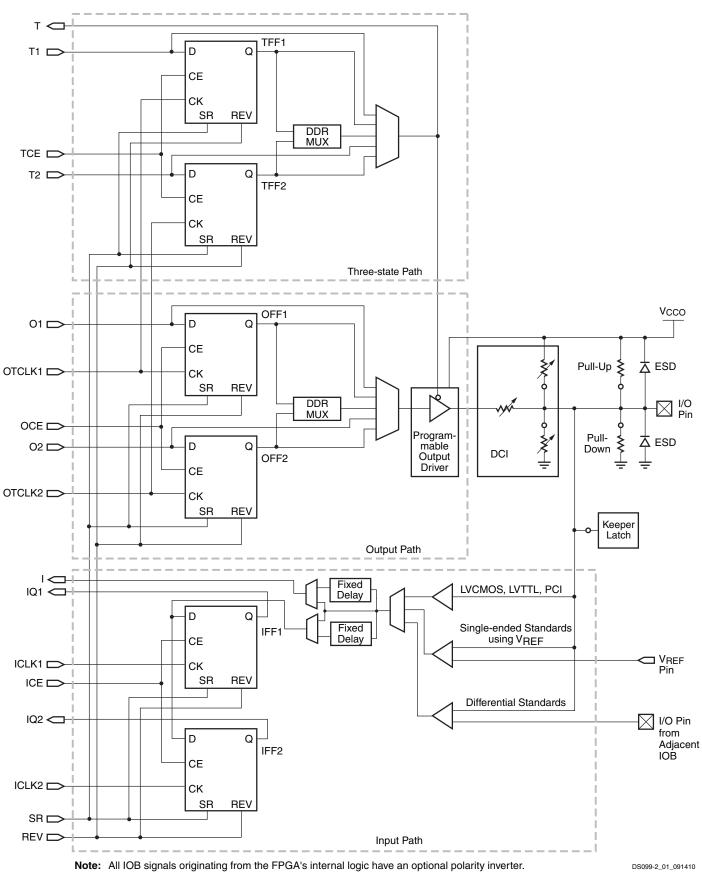

Figure 7: Simplified IOB Diagram

# Supply Voltages for the IOBs

Three different supplies power the IOBs:

- The V<sub>CCO</sub> supplies, one for each of the FPGA's I/O banks, power the output drivers, except when using the GTL and GTLP signal standards. The voltage on the V<sub>CCO</sub> pins determines the voltage swing of the output signal.

- V<sub>CCINT</sub> is the main power supply for the FPGA's internal logic.

- The V<sub>CCAUX</sub> is an auxiliary source of power, primarily to optimize the performance of various FPGA functions such as I/O switching.

# The I/Os During Power-On, Configuration, and User Mode

With no power applied to the FPGA, all I/Os are in a high-impedance state. The  $V_{CCINT}$  (1.2V),  $V_{CCAUX}$  (2.5V), and  $V_{CCO}$  supplies may be applied in any order. Before power-on can finish,  $V_{CCINT}$ ,  $V_{CCO}$  Bank 4, and  $V_{CCAUX}$  must have reached their respective minimum recommended operating levels (see Table 29, page 59). At this time, all I/O drivers also will be in a high-impedance state.  $V_{CCO}$  Bank 4,  $V_{CCINT}$ , and  $V_{CCAUX}$  serve as inputs to the internal Power-On Reset circuit (POR).

A Low level applied to the HSWAP\_EN input enables pull-up resistors on User I/Os from power-on throughout configuration. A High level on HSWAP\_EN disables the pull-up resistors, allowing the I/Os to float. If the HSWAP\_EN pin is floating, then an internal pull-up resistor pulls HSWAP\_EN High. As soon as power is applied, the FPGA begins initializing its configuration memory. At the same time, the FPGA internally asserts the Global Set-Reset (GSR), which asynchronously resets all IOB storage elements to a Low state.

Upon the completion of initialization, INIT\_B goes High, sampling the M0, M1, and M2 inputs to determine the configuration mode. At this point, the configuration data is loaded into the FPGA. The I/O drivers remain in a high-impedance state (with or without pull-up resistors, as determined by the HSWAP\_EN input) throughout configuration.

The Global Three State (GTS) net is released during Start-Up, marking the end of configuration and the beginning of design operation in the User mode. At this point, those I/Os to which signals have been assigned go active while all unused I/Os remain in a high-impedance state. The release of the GSR net, also part of Start-up, leaves the IOB registers in a Low state by default, unless the loaded design reverses the polarity of their respective RS inputs.

In User mode, all internal pull-up resistors on the I/Os are disabled and HSWAP\_EN becomes a "don't care" input. If it is desirable to have pull-up or pull-down resistors on I/Os carrying signals, the appropriate symbol—e.g., PULLUP, PULLDOWN—must be placed at the appropriate pads in the design. The Bitstream Generator (Bitgen) option UnusedPin available in the Xilinx development software determines whether unused I/Os collectively have pull-up resistors, pull-down resistors, or no resistors in User mode.

# **CLB** Overview

For more details on the CLBs, refer to the chapter entitled "Using Configurable Logic Blocks" in UG331.

The Configurable Logic Blocks (CLBs) constitute the main logic resource for implementing synchronous as well as combinatorial circuits. Each CLB comprises four interconnected slices, as shown in Figure 11. These slices are grouped in pairs. Each pair is organized as a column with an independent carry chain.

The nomenclature that the FPGA Editor—part of the Xilinx development software—uses to designate slices is as follows: The letter 'X' followed by a number identifies columns of slices. The 'X' number counts up in sequence from the left side of the die to the right. The letter 'Y' followed by a number identifies the position of each slice in a pair as well as indicating the CLB row. The 'Y' number counts slices starting from the bottom of the die according to the sequence: 0, 1, 0, 1 (the first CLB row); 2, 3, 2, 3 (the second CLB row); etc. Figure 11 shows the CLB located in the lower left-hand corner of the die. Slices X0Y0 and X0Y1 make up the column-pair on the left where as slices X1Y0 and X1Y1 make up the column-pair on the right. For each CLB, the term "left-hand" (or SLICEM) indicates the pair of slices labeled with an even 'X' number, such as X0, and the term "right-hand" (or SLICEL) designates the pair of slices with an odd 'X' number, e.g., X1.

# **Function Generator**

Each of the two LUTs (F and G) in a slice have four logic inputs (A1-A4) and a single output (D). This permits any four-variable Boolean logic operation to be programmed into them. Furthermore, wide function multiplexers can be used to effectively combine LUTs within the same CLB or across different CLBs, making logic functions with still more input variables possible.

The LUTs in both the right-hand and left-hand slice-pairs not only support the logic functions described above, but also can function as ROM that is initialized with data at the time of configuration.

The LUTs in the left-hand slice-pair (even-numbered columns such as X0 in Figure 11) of each CLB support two additional functions that the right-hand slice-pair (odd-numbered columns such as X1) do not.

First, it is possible to program the "left-hand LUTs" as distributed RAM. This type of memory affords moderate amounts of data buffering anywhere along a data path. One left-hand LUT stores 16 bits. Multiple left-hand LUTs can be combined in various ways to store larger amounts of data. A dual port option combines two LUTs so that memory access is possible from two independent data lines. A Distributed ROM option permits pre-loading the memory with data during FPGA configuration.

Second, it is possible to program each left-hand LUT as a 16-bit shift register. Used in this way, each LUT can delay serial data anywhere from one to 16 clock cycles. The four left-hand LUTs of a single CLB can be combined to produce delays up to 64 clock cycles. The SHIFTIN and SHIFTOUT lines cascade LUTs to form larger shift registers. It is also possible to combine shift registers across more than one CLB. The resulting programmable delays can be used to balance the timing of data pipelines.

# **Block RAM Overview**

All Spartan-3 devices support block RAM, which is organized as configurable, synchronous 18Kbit blocks. Block RAM stores relatively large amounts of data more efficiently than the distributed RAM feature described earlier. (The latter is better suited for buffering small amounts of data anywhere along signal paths.) This section describes basic Block RAM functions. For more information, refer to the chapter entitled "Using Block RAM" in <u>UG331</u>.

The aspect ratio—i.e., width vs. depth—of each block RAM is configurable. Furthermore, multiple blocks can be cascaded to create still wider and/or deeper memories.

A choice among primitives determines whether the block RAM functions as dual- or single-port memory. A name of the form RAMB16\_S[w<sub>A</sub>]\_S[w<sub>B</sub>] calls out the dual-port primitive, where the integers w<sub>A</sub> and w<sub>B</sub> specify the total data path width at ports w<sub>A</sub> and w<sub>B</sub>, respectively. Thus, a RAMB16\_S9\_S18 is a dual-port RAM with a 9-bit-wide Port A and an 18-bit-wide Port B. A name of the form RAMB16\_S[w] identifies the single-port primitive, where the integer w specifies the total data path width of the lone port. A RAMB16\_S18 is a single-port RAM with an 18-bit-wide port. Other memory functions—e.g., FIFOs, data path width conversion, ROM, etc.—are readily available using the CORE Generator<sup>TM</sup> software, part of the Xilinx development software.

(e.g. all configuration pins taken together) when operating in the User mode. This is accomplished by setting the *Persist* option to *Yes*.

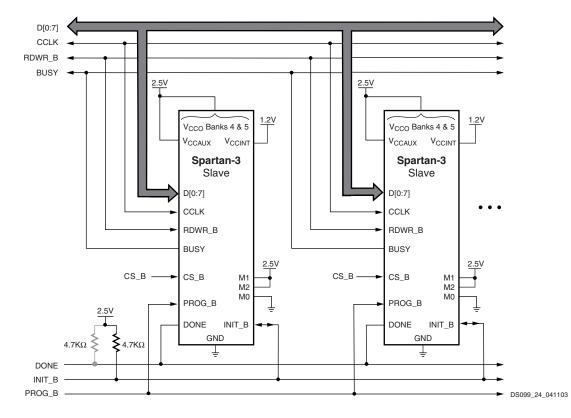

Multiple FPGAs can be configured using the Slave Parallel mode and can be made to start-up simultaneously. Figure 27 shows the device connections. To configure multiple devices in this way, wire the individual CCLK, Data, RDWR\_B, and BUSY pins of all the devices in parallel. The individual devices are loaded separately by deasserting the CS\_B pin of each device in turn and writing the appropriate data.

#### Notes:

- 1. There are two ways to use the DONE line. First, one may set the BitGen option DriveDone to "Yes" only for the last FPGA to be configured in the chain shown above (or for the single FPGA as may be the case). This enables the DONE pin to drive High; thus, no pull-up resistor is necessary. DriveDone is set to "No" for the remaining FPGAs in the chain. Second, DriveDone can be set to "No" for all FPGAs. Then all DONE lines are open-drain and require the pull-up resistor shown in grey. In most cases, a value between 3.3KΩ to 4.7KΩ is sufficient. However, when using DONE synchronously with a long chain of FPGAs, cumulative capacitance may necessitate lower resistor values (e.g. down to 330Ω) in order to ensure a rise time within one clock cycle.

- 2. If the FPGAs use different configuration data files, configure them in sequence by first asserting the CS\_B of one FPGA then asserting the CS\_B of the other FPGA.

- 3. For information on how to program the FPGA using 3.3V signals and power, see 3.3V-Tolerant Configuration Interface.

#### Figure 27: Connection Diagram for Slave Parallel Configuration

# **EXILINX**.

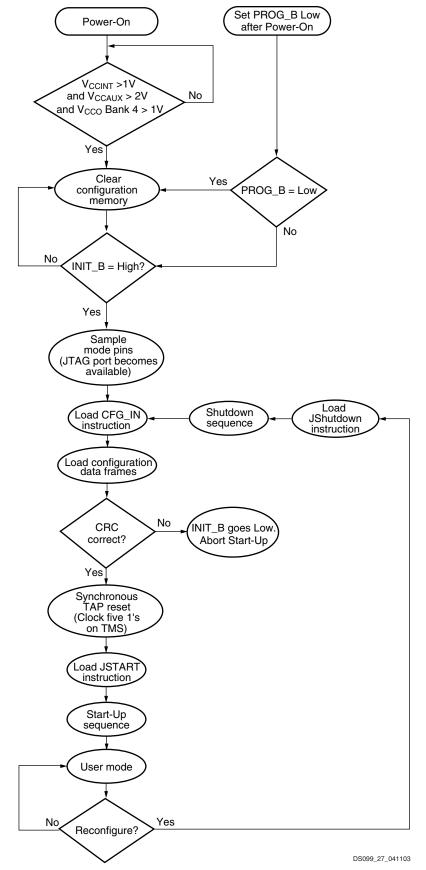

Configuration is automatically initiated after power-on unless it is delayed by the user. INIT\_B is an open-drain line that the FPGA holds Low during the clearing of the configuration memory. Extending the time that the pin is Low causes the configuration sequencer to wait. Thus, configuration is delayed by preventing entry into the phase where data is loaded.

The configuration process can also be initiated by asserting the PROG\_B pin. The end of the memory-clearing phase is signaled by the INIT\_B pin going High. At this point, the configuration data is written to the FPGA. The FPGA pulses the Global Set/Reset (GSR) signal at the end of configuration, resetting all flip-flops. The completion of the entire process is signaled by the DONE pin going High.

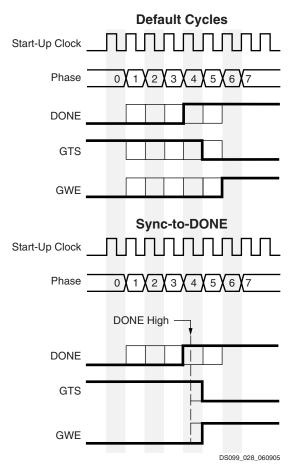

Figure 31: Default Start-Up Sequence

The default start-up sequence, shown in Figure 31, serves as a transition to the User mode. The default start-up sequence is that one CCLK cycle after DONE goes High, the Global Three-State signal (GTS) is released. This permits device outputs to which signals have been assigned to become active. One CCLK cycle later, the Global Write Enable (GWE) signal is released. This permits the internal storage elements to begin changing state in response to the design logic and the user clock.

The relative timing of configuration events can be changed via the BitGen options in the Xilinx development software. In addition, the GTS and GWE events can be made dependent on the DONE pins of multiple devices all going High, forcing the devices to start synchronously. The sequence can also be paused at any stage, until lock has been achieved on any DCM.

### Readback

🗶 XILINX.

Using Slave Parallel mode, configuration data from the FPGA can be read back. Readback is supported only in the Slave Parallel and Boundary-Scan modes.

Along with the configuration data, it is possible to read back the contents of all registers, distributed RAM, and block RAM resources. This capability is used for real-time debugging.

# Notice of Disclaimer

THE XILINX HARDWARE FPGA AND CPLD DEVICES REFERRED TO HEREIN ("PRODUCTS") ARE SUBJECT TO THE TERMS AND CONDITIONS OF THE XILINX LIMITED WARRANTY WHICH CAN BE VIEWED AT <a href="http://www.xilinx.com/warranty.htm">http://www.xilinx.com/warranty.htm</a>. THIS LIMITED WARRANTY DOES NOT EXTEND TO ANY USE OF PRODUCTS IN AN APPLICATION OR ENVIRONMENT THAT IS NOT WITHIN THE SPECIFICATIONS STATED IN THE XILINX DATA SHEET. ALL SPECIFICATIONS ARE SUBJECT TO CHANGE WITHOUT NOTICE. PRODUCTS ARE NOT DESIGNED OR INTENDED TO BE FAIL-SAFE OR FOR USE IN ANY APPLICATION REQUIRING FAIL-SAFE PERFORMANCE, SUCH AS LIFE-SUPPORT OR SAFETY DEVICES OR SYSTEMS, OR ANY OTHER APPLICATION THAT INVOKES THE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). USE OF PRODUCTS IN CRITICAL APPLICATIONS IS AT THE SOLE RISK OF CUSTOMER, SUBJECT TO APPLICABLE LAWS AND REGULATIONS.

#### **CRITICAL APPLICATIONS DISCLAIMER**

XILINX PRODUCTS (INCLUDING HARDWARE, SOFTWARE AND/OR IP CORES) ARE NOT DESIGNED OR INTENDED TO BE FAIL-SAFE, OR FOR USE IN ANY APPLICATION REQUIRING FAIL-SAFE PERFORMANCE, SUCH AS IN LIFE-SUPPORT OR SAFETY DEVICES OR SYSTEMS, CLASS III MEDICAL DEVICES, NUCLEAR FACILITIES, APPLICATIONS RELATED TO THE DEPLOYMENT OF AIRBAGS, OR ANY OTHER APPLICATIONS THAT COULD LEAD TO DEATH, PERSONAL INJURY OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE (INDIVIDUALLY AND COLLECTIVELY, "CRITICAL APPLICATIONS"). FURTHERMORE, XILINX PRODUCTS ARE NOT DESIGNED OR INTENDED FOR USE IN ANY APPLICATIONS THAT AFFECT CONTROL OF A VEHICLE OR AIRCRAFT, UNLESS THERE IS A FAIL-SAFE OR REDUNDANCY FEATURE (WHICH DOES NOT INCLUDE USE OF SOFTWARE IN THE XILINX DEVICE TO IMPLEMENT THE REDUNDANCY) AND A WARNING SIGNAL UPON FAILURE TO THE OPERATOR. CUSTOMER AGREES, PRIOR TO USING OR DISTRIBUTING ANY SYSTEMS THAT INCORPORATE XILINX PRODUCTS, TO THOROUGHLY TEST THE SAME FOR SAFETY PURPOSES. TO THE MAXIMUM EXTENT PERMITTED BY APPLICABLE LAW, CUSTOMER ASSUMES THE SOLE RISK AND LIABILITY OF ANY USE OF XILINX PRODUCTS IN CRITICAL APPLICATIONS.

#### AUTOMOTIVE APPLICATIONS DISCLAIMER

XILINX PRODUCTS ARE NOT DESIGNED OR INTENDED TO BE FAIL-SAFE, OR FOR USE IN ANY APPLICATION REQUIRING FAIL-SAFE PERFORMANCE, SUCH AS APPLICATIONS RELATED TO: (I) THE DEPLOYMENT OF AIRBAGS, (II) CONTROL OF A VEHICLE, UNLESS THERE IS A FAIL-SAFE OR REDUNDANCY FEATURE (WHICH DOES NOT INCLUDE USE OF SOFTWARE IN THE XILINX DEVICE TO IMPLEMENT THE REDUNDANCY) AND A WARNING SIGNAL UPON FAILURE TO THE OPERATOR, OR (III) USES THAT COULD LEAD TO DEATH OR PERSONAL INJURY. CUSTOMER ASSUMES THE SOLE RISK AND LIABILITY OF ANY USE OF XILINX PRODUCTS IN SUCH APPLICATIONS.

#### Table 28: Absolute Maximum Ratings (Cont'd)

| Symbol           | Description                                   | Conditions                                                                        | Min | Max   | Units |

|------------------|-----------------------------------------------|-----------------------------------------------------------------------------------|-----|-------|-------|

| Ι <sub>ΙΚ</sub>  | Input clamp current per I/O pin               | $-0.5 \text{ V} < \text{V}_{\text{IN}} < (\text{V}_{\text{CCO}} + 0.5 \text{ V})$ | -   | ±100  | mA    |

|                  | Electrostatic Discharge Voltage pins relative | Human body model                                                                  | -   | ±2000 | V     |

|                  | to GND                                        | Charged device model                                                              | -   | ±500  | V     |

|                  |                                               | Machine model                                                                     | -   | ±200  | V     |

| ТJ               | Junction temperature                          |                                                                                   | -   | 125   | °C    |

| T <sub>SOL</sub> | Soldering temperature <sup>(4)</sup>          |                                                                                   |     | 220   | °C    |

| T <sub>STG</sub> | Storage temperature                           |                                                                                   |     | 150   | °C    |

#### Notes:

- 1. Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only; functional operation of the device at these or any other conditions beyond those listed under the Recommended Operating Conditions is not implied. Exposure to Absolute Maximum Ratings conditions for extended periods of time adversely affects device reliability.

- All User I/O and Dual-Purpose pins (DIN/D0, D1–D7, CS\_B, RDWR\_B, BUSY/DOUT, and INIT\_B) draw power from the V<sub>CCO</sub> power rail of the associated bank. Keeping VIN within 500 mV of the associated V<sub>CCO</sub> rails or ground rail ensures that the internal diode junctions that exist between each of these pins and the V<sub>CCO</sub> and GND rails do not turn on. Table 32 specifies the V<sub>CCO</sub> range used to determine the max limit. Input voltages outside the –0.5V to V<sub>CCO</sub>+0.5V voltage range are permissible provided that the I<sub>IK</sub> input clamp diode rating is met and no more than 100 pins exceed the range simultaneously. Prolonged exposure to such current may compromise device reliability. A sustained current of 10 mA will not compromise device reliability. See <u>XAPP459</u>, *Eliminating I/O Coupling Effects when Interfacing Large-Swing Single-Ended Signals to User I/O Pins on Spartan-3 Generation FPGAs* for more details. The VIN limits apply to both the DC and AC components of signals. Simple application solutions are available that show how to handle overshoot/undershoot as well as achieve PCI compliance. Refer to the following application notes: XAPP457, *Powering and Configuring Spartan-3 Generation FPGAs in Compliant PCI Applications* and <u>XAPP659</u>, *Virtex®-II Pro / Virtex-II Pro X 3.3V I/O Design Guidelines*.

- All Dedicated pins (M0–M2, CCLK, PROG\_B, DONE, HSWAP\_EN, TCK, TDI, TDO, and TMS) draw power from the V<sub>CCAUX</sub> rail (2.5V). Meeting the V<sub>IN</sub> max limit ensures that the internal diode junctions that exist between each of these pins and the V<sub>CCAUX</sub> rail do not turn on. Table 32 specifies the V<sub>CCAUX</sub> range used to determine the max limit. When V<sub>CCAUX</sub> is at its maximum recommended operating level (2.625V), V<sub>IN</sub> max < 3.125V. As long as the V<sub>IN</sub> max specification is met, oxide stress is not possible. For information concerning the use of 3.3V signals, see the 3.3V-Tolerant Configuration Interface, page 47. See also XAPP459.

- 4. For soldering guidelines, see UG112, Device Packaging and Thermal Characteristics and XAPP427, Implementation and Solder Reflow Guidelines for Pb-Free Packages.

| Symbol              | Description                                      | Min | Max | Units |

|---------------------|--------------------------------------------------|-----|-----|-------|

| V <sub>CCINTT</sub> | Threshold for the V <sub>CCINT</sub> supply      | 0.4 | 1.0 | V     |

| V <sub>CCAUXT</sub> | Threshold for the V <sub>CCAUX</sub> supply      | 0.8 | 2.0 | V     |

| V <sub>CCO4T</sub>  | Threshold for the V <sub>CCO</sub> Bank 4 supply | 0.4 | 1.0 | V     |

#### Table 29: Supply Voltage Thresholds for Power-On Reset

#### Notes:

- V<sub>CCINT</sub>, V<sub>CCAUX</sub>, and V<sub>CCO</sub> supplies may be applied in any order. When applying V<sub>CCINT</sub> power before V<sub>CCAUX</sub> power, the FPGA may draw a *surplus* current in addition to the quiescent current levels specified in Table 34. Applying V<sub>CCAUX</sub> eliminates the surplus current. The FPGA does not use any of the surplus current for the power-on process. For this power sequence, make sure that regulators with foldback features will not shut down inadvertently.

- 2. To ensure successful power-on, V<sub>CCINT</sub>, V<sub>CCO</sub> Bank 4, and V<sub>CCAUX</sub> supplies must rise through their respective threshold-voltage ranges with no dips at any point.

- 3. If a brown-out condition occurs where V<sub>CCAUX</sub> or V<sub>CCINT</sub> drops below the retention voltage indicated in Table 31, then V<sub>CCAUX</sub> or V<sub>CCINT</sub> must drop below the minimum power-on reset voltage in order to clear out the device configuration content.

# Table 36: DC Characteristics of User I/Os Using Single-Ended Standards (Cont'd)

| Signal Standard<br>(IOSTANDARD) and Current<br>Drive Attribute (mA) |    | Test Co                 | nditions                | Logic Level C              | Logic Level Characteristics |  |  |

|---------------------------------------------------------------------|----|-------------------------|-------------------------|----------------------------|-----------------------------|--|--|

|                                                                     |    | l <sub>OL</sub><br>(mA) | I <sub>ОН</sub><br>(mA) | V <sub>OL</sub><br>Max (V) | V <sub>OH</sub><br>Min (V)  |  |  |

| LVCMOS33 <sup>(4)</sup>                                             | 2  | 2                       | -2                      | 0.4                        | V <sub>CCO</sub> – 0.4      |  |  |

|                                                                     | 4  | 4                       | -4                      | _                          |                             |  |  |

|                                                                     | 6  | 6                       | 6                       | _                          |                             |  |  |

|                                                                     | 8  | 8                       | -8                      |                            |                             |  |  |

|                                                                     | 12 | 12                      | -12                     |                            |                             |  |  |

|                                                                     | 16 | 16                      | -16                     | _                          |                             |  |  |

|                                                                     | 24 | 24                      | -24                     | _                          |                             |  |  |

| LVDCI_33,<br>LVDCI_DV2_33                                           |    | Note 3                  | Note 3                  | _                          |                             |  |  |

| LVTTL <sup>(4)</sup>                                                | 2  | 2                       | -2                      | 0.4                        | 2.4                         |  |  |

|                                                                     | 4  | 4                       | -4                      |                            |                             |  |  |

|                                                                     | 6  | 6                       | 6                       |                            |                             |  |  |

|                                                                     | 8  | 8                       | 8                       |                            |                             |  |  |

|                                                                     | 12 | 12                      | -12                     |                            |                             |  |  |

|                                                                     | 16 | 16                      | -16                     |                            |                             |  |  |

|                                                                     | 24 | 24                      | -24                     |                            |                             |  |  |

| PCI33_3                                                             |    | Note 6                  | Note 6                  | 0.10V <sub>CCO</sub>       | 0.90V <sub>CCO</sub>        |  |  |

| SSTL18_I                                                            |    | 6.7                     | -6.7                    | V <sub>TT</sub> – 0.475    | V <sub>TT</sub> + 0.475     |  |  |

| SSTL18_I_DCI                                                        |    | Note 3                  | Note 3                  |                            |                             |  |  |

| SSTL18_II                                                           |    | 13.4                    | -13.4                   | V <sub>TT</sub> – 0.475    | V <sub>TT</sub> + 0.475     |  |  |

| SSTL2_I                                                             |    | 8.1                     | -8.1                    | V <sub>TT</sub> – 0.61     | V <sub>TT</sub> + 0.61      |  |  |

| SSTL2_I_DCI                                                         |    | Note 3                  | Note 3                  |                            |                             |  |  |

| SSTL2_II <sup>(7)</sup>                                             |    | 16.2                    | -16.2                   | V <sub>TT</sub> – 0.81     | V <sub>TT</sub> + 0.81      |  |  |

| SSTL2_II_DCI <sup>(7)</sup>                                         |    | Note 3                  | Note 3                  |                            |                             |  |  |

#### Notes:

2.

The numbers in this table are based on the conditions set forth in Table 32 and Table 35. 1.

The numbers in this table are based on the conditions set for Descriptions of the symbols used in this table are as follows:  $I_{OL}$  – the output current condition under which VOL is tested  $V_{OL}$  – the output current condition under which VOH is tested  $V_{OL}$  – the output voltage that indicates a Low logic level  $V_{H}$  – the input voltage that indicates a High logic level  $V_{H}$  – the input voltage that indicates a High logic level  $V_{H}$  – the input voltage that indicates a High logic level  $V_{H}$  – the supply voltage for output drivers as well as LVCM

$V_{CCO}$  – the supply voltage for output drivers as well as LVCMOS, LVTTL, and PCI inputs  $V_{REF}$  – the reference voltage for setting the input switching threshold  $V_{TT}$  – the voltage applied to a resistor termination

Tested according to the standard's relevant specifications. When using the DCI version of a standard on a given I/O bank, that bank will consume more power than if the non-DCI version had been used instead. The additional power is drawn for the purpose of impedance-matching at the I/O pins. A portion of this power is dissipated in the two RREF resistors. 3.

For the LVCMOS and LVTTL standards: the same V<sub>OL</sub> and V<sub>OH</sub> limits apply for both the Fast and Slow slew attributes. 4.

All dedicated output pins (CCLK, DONE, and TDO) and dual-purpose totem-pole output pins (D0-D7 and BUSY/DOUT) exhibit the characteristics of 5. LVCMOS25 with 12 mA drive and slow slew rate. For information concerning the use of 3.3V signals, see 3.3V-Tolerant Configuration Interface, page 47.

Tested according to the relevant PCI specifications. For more information, see XAPP457. 6.

7. The minimum usable V<sub>TT</sub> voltage is 1.25V.

### Table 41: System-Synchronous Pin-to-Pin Setup and Hold Times for the IOB Input Path (Cont'd)

|                   |                                                                         |                                |          | Speed Grade |       |       |

|-------------------|-------------------------------------------------------------------------|--------------------------------|----------|-------------|-------|-------|

| Symbol            | Description                                                             | Conditions                     | Device   | -5          | -4    | Units |

|                   |                                                                         |                                |          | Min         | Min   |       |

| T <sub>PHFD</sub> | When writing to IFF, the time from                                      | LVCMOS25 <sup>(3)</sup> ,      | XC3S50   | -0.98       | -0.93 | ns    |

|                   | the active transition at the Global<br>Clock pin to the point when data | IOBDELAY = IFD,<br>without DCM | XC3S200  | -0.40       | -0.35 | ns    |

|                   | must be held at the Input pin. The                                      |                                | XC3S400  | -0.27       | -0.22 | ns    |

|                   | DCM is not in use. The Input Delay is programmed.                       |                                | XC3S1000 | -1.19       | -1.14 | ns    |

|                   |                                                                         |                                | XC3S1500 | -1.43       | -1.38 | ns    |

|                   |                                                                         |                                | XC3S2000 | -2.33       | -2.28 | ns    |

|                   |                                                                         |                                | XC3S4000 | -2.47       | -2.42 | ns    |

|                   |                                                                         |                                | XC3S5000 | -2.66       | -2.61 | ns    |

#### Notes:

- 1. The numbers in this table are tested using the methodology presented in Table 48 and are based on the operating conditions set forth in Table 32 and Table 35.

- 2. This setup time requires adjustment whenever a signal standard other than LVCMOS25 is assigned to the Global Clock Input or the data Input. If this is true of the Global Clock Input, *subtract* the appropriate adjustment from Table 44. If this is true of the data Input, *add* the appropriate Input adjustment from the same table.

- 3. This hold time requires adjustment whenever a signal standard other than LVCMOS25 is assigned to the Global Clock Input or the data Input. If this is true of the Global Clock Input, *add* the appropriate Input adjustment from Table 44. If this is true of the data Input, *subtract* the appropriate Input adjustment from the same table. When the hold time is negative, it is possible to change the data before the clock's active edge.

- 4. DCM output jitter is included in all measurements.

#### Table 42: Setup and Hold Times for the IOB Input Path

|                      |                                                                                                                                     |                                             |          | Speed Grade |      |       |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|----------|-------------|------|-------|

| Symbol               | Description                                                                                                                         | Conditions                                  | Device   | -5          | -4   | Units |

|                      |                                                                                                                                     |                                             |          | Min         | Min  |       |

| Setup Times          |                                                                                                                                     | -                                           | U        |             |      |       |

| T <sub>IOPICK</sub>  | Time from the setup of data at the Input pin                                                                                        | LVCMOS25 <sup>(2)</sup> ,                   | XC3S50   | 1.65        | 1.89 | ns    |

|                      | to the active transition at the ICLK input of<br>the Input Flip-Flop (IFF). No Input Delay is                                       | IOBDELAY = NONE                             | XC3S200  | 1.37        | 1.57 | ns    |

|                      | programmed.                                                                                                                         |                                             | XC3S400  | 1.37        | 1.57 | ns    |

|                      |                                                                                                                                     |                                             | XC3S1000 | 1.65        | 1.89 | ns    |

|                      |                                                                                                                                     |                                             | XC3S1500 | 1.65        | 1.89 | ns    |

|                      |                                                                                                                                     |                                             | XC3S2000 | 1.65        | 1.89 | ns    |

|                      |                                                                                                                                     |                                             | XC3S4000 | 1.73        | 1.99 | ns    |

|                      |                                                                                                                                     |                                             | XC3S5000 | 1.82        | 2.09 | ns    |

| T <sub>IOPICKD</sub> | Time from the setup of data at the Input pin<br>to the active transition at the IFF's ICLK<br>input. The Input Delay is programmed. | LVCMOS25 <sup>(2)</sup> ,<br>IOBDELAY = IFD | XC3S50   | 4.39        | 5.04 | ns    |

|                      |                                                                                                                                     |                                             | XC3S200  | 4.76        | 5.47 | ns    |

|                      |                                                                                                                                     |                                             | XC3S400  | 4.63        | 5.32 | ns    |

|                      |                                                                                                                                     |                                             | XC3S1000 | 5.02        | 5.76 | ns    |

|                      |                                                                                                                                     |                                             | XC3S1500 | 5.40        | 6.20 | ns    |

|                      |                                                                                                                                     |                                             | XC3S2000 | 6.68        | 7.68 | ns    |

|                      |                                                                                                                                     |                                             | XC3S4000 | 7.16        | 8.24 | ns    |

|                      |                                                                                                                                     |                                             | XC3S5000 | 7.33        | 8.42 | ns    |

# Table 47: Output Timing Adjustments for IOB (Cont'd)

| Convert Output Time from LVCMOS25 with 12mA Drive and Fast Slew Rate to the<br>Following Signal Standard (IOSTANDARD) |      |       | Add the Adju | stment Below | Units |

|-----------------------------------------------------------------------------------------------------------------------|------|-------|--------------|--------------|-------|

|                                                                                                                       |      |       | Speed        | Grade        |       |

|                                                                                                                       | -5   | -4    |              |              |       |

| HSLVDCI_25                                                                                                            | 0.27 | 0.31  | ns           |              |       |

| HSLVDCI_33                                                                                                            | 0.28 | 0.32  | ns           |              |       |

| HSTL_I                                                                                                                |      |       | 0.60         | 0.69         | ns    |

| HSTL_I_DCI                                                                                                            |      |       | 0.59         | 0.68         | ns    |

| HSTL_III                                                                                                              |      |       | 0.19         | 0.22         | ns    |

| HSTL_III_DCI                                                                                                          |      |       | 0.20         | 0.23         | ns    |

| HSTL_I_18                                                                                                             |      |       | 0.18         | 0.21         | ns    |

| HSTL_I_DCI_18                                                                                                         |      |       | 0.17         | 0.19         | ns    |

| HSTL_II_18                                                                                                            |      |       | -0.02        | -0.01        | ns    |

| HSTL_II_DCI_18                                                                                                        |      |       | 0.75         | 0.86         | ns    |

| HSTL_III_18                                                                                                           |      |       | 0.28         | 0.32         | ns    |

| HSTL_III_DCI_18                                                                                                       |      |       | 0.28         | 0.32         | ns    |

| LVCMOS12                                                                                                              | Slow | 2 mA  | 7.60         | 8.73         | ns    |

|                                                                                                                       |      | 4 mA  | 7.42         | 8.53         | ns    |

|                                                                                                                       |      | 6 mA  | 6.67         | 7.67         | ns    |

|                                                                                                                       | Fast | 2 mA  | 3.16         | 3.63         | ns    |

|                                                                                                                       |      | 4 mA  | 2.70         | 3.10         | ns    |

|                                                                                                                       |      | 6 mA  | 2.41         | 2.77         | ns    |

| LVCMOS15                                                                                                              | Slow | 2 mA  | 4.55         | 5.23         | ns    |

|                                                                                                                       |      | 4 mA  | 3.76         | 4.32         | ns    |

|                                                                                                                       |      | 6 mA  | 3.57         | 4.11         | ns    |

|                                                                                                                       |      | 8 mA  | 3.55         | 4.09         | ns    |

|                                                                                                                       |      | 12 mA | 3.00         | 3.45         | ns    |

|                                                                                                                       | Fast | 2 mA  | 3.11         | 3.57         | ns    |

|                                                                                                                       |      | 4 mA  | 1.71         | 1.96         | ns    |

|                                                                                                                       |      | 6 mA  | 1.44         | 1.66         | ns    |

|                                                                                                                       |      | 8 mA  | 1.26         | 1.44         | ns    |

|                                                                                                                       |      | 12 mA | 1.11         | 1.27         | ns    |

| LVDCI_15                                                                                                              |      |       | 1.51         | 1.74         | ns    |

| LVDCI_DV2_15                                                                                                          |      |       | 1.32         | 1.52         | ns    |

# Table 50: Recommended Number of Simultaneously Switching Outputs per V<sub>CCO</sub>/GND Pair (Cont'd)

| Cime                            | al Chandard |    |       |       | Pac   | kage  |                                              |  |

|---------------------------------|-------------|----|-------|-------|-------|-------|----------------------------------------------|--|

| Signal Standard<br>(IOSTANDARD) |             |    | VQ100 | TQ144 | PQ208 | CP132 | FT256, FG320, FG456,<br>FG676, FG900, FG1156 |  |

| LVCMOS33                        | Slow        | 2  | 34    | 24    | 24    | 52    | 76                                           |  |

|                                 |             | 4  | 17    | 14    | 14    | 26    | 46                                           |  |

|                                 |             | 6  | 17    | 11    | 11    | 26    | 27                                           |  |

|                                 |             | 8  | 10    | 10    | 10    | 13    | 20                                           |  |

|                                 |             | 12 | 9     | 9     | 9     | 13    | 13                                           |  |

|                                 |             | 16 | 8     | 8     | 8     | 8     | 10                                           |  |

|                                 |             | 24 | 8     | 8     | 8     | 8     | 9                                            |  |

|                                 | Fast        | 2  | 20    | 20    | 20    | 26    | 44                                           |  |

|                                 |             | 4  | 15    | 15    | 15    | 15    | 26                                           |  |

|                                 |             | 6  | 11    | 11    | 11    | 13    | 16                                           |  |

|                                 |             | 8  | 10    | 10    | 10    | 10    | 12                                           |  |

|                                 |             | 12 | 8     | 8     | 8     | 8     | 10                                           |  |

|                                 |             | 16 | 8     | 8     | 8     | 8     | 8                                            |  |

|                                 |             | 24 | 7     | 7     | 7     | 7     | 7                                            |  |

| LVDCI_33                        |             | -+ | 10    | 10    | 10    | 10    | 10                                           |  |

| LVDCI_DV2_33                    |             |    | 10    | 10    | 10    | 10    | 10                                           |  |

| HSLVDCI_33                      |             |    | 10    | 10    | 10    | 10    | 10                                           |  |

| LVTTL                           | Slow        | 2  | 34    | 25    | 25    | 52    | 60                                           |  |

|                                 |             | 4  | 17    | 16    | 16    | 26    | 41                                           |  |

|                                 |             | 6  | 17    | 15    | 15    | 26    | 29                                           |  |

|                                 |             | 8  | 12    | 12    | 12    | 13    | 22                                           |  |

|                                 |             | 12 | 10    | 10    | 10    | 13    | 13                                           |  |

|                                 |             | 16 | 10    | 10    | 10    | 10    | 11                                           |  |

|                                 |             | 24 | 8     | 8     | 8     | 8     | 9                                            |  |

|                                 | Fast        | 2  | 20    | 20    | 20    | 26    | 34                                           |  |

|                                 |             | 4  | 13    | 13    | 13    | 13    | 20                                           |  |

|                                 |             | 6  | 11    | 11    | 11    | 13    | 15                                           |  |

|                                 |             | 8  | 10    | 10    | 10    | 10    | 12                                           |  |

|                                 |             | 12 | 9     | 9     | 9     | 9     | 10                                           |  |

|                                 |             | 16 | 8     | 8     | 8     | 8     | 9                                            |  |

|                                 |             | 24 | 7     | 7     | 7     | 7     | 7                                            |  |

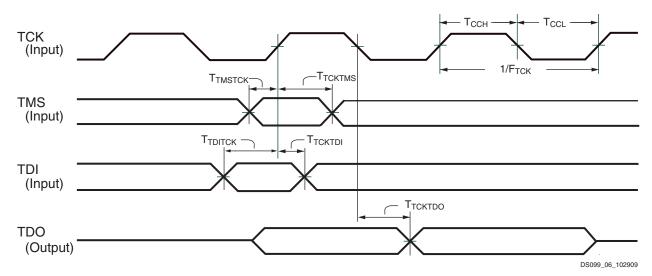

#### Figure 39: JTAG Waveforms

### Table 68: Timing for the JTAG Test Access Port

| O much al           | Deseri                                                                       | Description                           |     |      |       |  |

|---------------------|------------------------------------------------------------------------------|---------------------------------------|-----|------|-------|--|

| Symbol              | Symbol Description                                                           |                                       |     |      | Units |  |

| Clock-to-Output     | t Times                                                                      | · · · · · · · · · · · · · · · · · · · |     |      |       |  |

| T <sub>TCKTDO</sub> | The time from the falling transition on the TDO pin                          | the TCK pin to data appearing at      | 1.0 | 11.0 | ns    |  |

| Setup Times         |                                                                              |                                       |     | 1    | 1     |  |

| T <sub>TDITCK</sub> | The time from the setup of data at the the TCK pin                           | e TDI pin to the rising transition at | 7.0 | -    | ns    |  |

| T <sub>TMSTCK</sub> | The time from the setup of a logic lev transition at the TCK pin             | el at the TMS pin to the rising       | 7.0 | -    | ns    |  |

| Hold Times          |                                                                              |                                       |     |      |       |  |

| Т <sub>ТСКТОІ</sub> | The time from the rising transition at t is last held at the TDI pin         | he TCK pin to the point when data     | 0   | -    | ns    |  |

| T <sub>TCKTMS</sub> | The time from the rising transition at the level is last held at the TMS pin | ne TCK pin to the point when a logic  | 0   | -    | ns    |  |

| Clock Timing        |                                                                              |                                       |     |      |       |  |

| Т <sub>тскн</sub>   | TCK pin High pulse width                                                     |                                       | 5   | ∞    | ns    |  |

| T <sub>TCKL</sub>   | TCK pin Low pulse width                                                      |                                       | 5   | ∞    | ns    |  |

| F <sub>TCK</sub>    | Frequency of the TCK signal                                                  | JTAG Configuration                    | 0   | 33   | MHz   |  |

|                     |                                                                              | Boundary-Scan                         | 0   | 25   | MHz   |  |

#### Notes:

1. The numbers in this table are based on the operating conditions set forth in Table 32.

# **Revision History**

| Date     | Version | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 04/11/03 | 1.0     | Initial Xilinx release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 07/11/03 | 1.1     | Extended Absolute Maximum Rating for junction temperature in Table 28. Added numbers for typical quiescent supply current (Table 34) and DLL timing.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 02/06/04 | 1.2     | Revised V <sub>IN</sub> maximum rating (Table 28). Added power-on requirements (Table 30), leakage current number (Table 33), and differential output voltage levels (Table 38) for Rev. 0. Published new quiescent current numbers (Table 34). Updated pull-up and pull-down resistor strengths (Table 33). Added LVDCI_DV2 and LVPECL standards (Table 37 and Table 38). Changed CCLK setup time (Table 66 and Table 67).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 03/04/04 | 1.3     | Added timing numbers from v1.29 speed files as well as DCM timing (Table 58 through Table 63).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 08/24/04 | 1.4     | Added reference to errata documents on page 49. Clarified Absolute Maximum Ratings and added ESD information (Table 28). Explained $V_{CCO}$ ramp time measurement (Table 30). Clarified I <sub>L</sub> specification (Table 33). Updated quiescent current numbers and added information on power-on and surplus current (Table 34). Adjusted V <sub>REF</sub> range for HSTL_III and HSTL_I_18 and changed V <sub>IH</sub> min for LVCMOS12 (Table 35). Added note limiting V <sub>TT</sub> range for SSTL2_II signal standards (Table 36). Calculated V <sub>OH</sub> and V <sub>OL</sub> levels for differential standards (Table 38). Updated Switching Characteristics with speed file v1.32 (Table 40 through Table 48 and Table 51 through Table 56). Corrected IOB test conditions (Table 41). Updated DCM timing with latest characterization data (Table 58 through Table 62). Improved DCM CLKIN pulse width specification (Table 58). Recommended use of Virtex-II FPGA Jitter calculator (Table 61). Improved DCM PSCLK pulse width specification (Table 62). Changed Phase Shifter lock time parameter (Table 63). Because the BitGen option Centered_x#_y# is not necessary for Variable Phase Shift mode, removed BitGen command table and referring text. Adjusted maximum CCLK frequency for the slave serial and parallel configuration modes (Table 66). Inverted CCLK waveform (Figure 37). Adjusted JTAG setup times (Table 68). |

| 12/17/04 | 1.5     | Updated timing parameters to match v1.35 speed file. Improved $V_{CCO}$ ramp time specification (Table 30).<br>Added a note limiting the rate of change of $V_{CCAUX}$ (Table 32). Added typical quiescent current values for the XC3S2000, XC3S4000, and XC3S5000 (Table 34). Increased $I_{OH}$ and $I_{OL}$ for SSTL2-I and SSTL2-II standards (Table 36). Added SSO guidelines for the VQ, TQ, and PQ packages as well as edited SSO guidelines for the FT and FG packages (Table 50). Added maximum CCLK frequencies for configuration using compressed bitstreams (Table 66 and Table 67). Added specifications for the HSLVDCI standards (Table 35, Table 36, Table 44, Table 47, Table 48, and Table 50).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 08/19/05 | 1.6     | Updated timing parameters to match v1.37 speed file. All Spartan-3 FPGA part types, except XC3S5000, promoted to Production status. Removed V <sub>CCO</sub> ramp rate restriction from all mask revision 'E' and later devices (Table 30). Added equivalent resistance values for internal pull-up and pull-down resistors (Table 33). Added worst-case quiescent current values for XC3S2000, XC3S4000, XC3S5000 (Table 34). Added industrial temperature range specification and improved typical quiescent current values (Table 34). Improved the DLL minimum clock input frequency specification from 24 MHz down to 18 MHz (Table 58). Improved the DFS minimum and maximum clock output frequency specifications (Table 60, Table 61). Added new miscellaneous DCM specifications (Table 64), primarily affecting Industrial temperature range applications. Updated Simultaneously Switching Output Guidelines and Table 50 for QFP packages. Added information on SSTL18_II I/O standard and timing to support DDR2 SDRAM interfaces. Added differential (or complementary single-ended) DIFF_HSTL_II_18 and DIFF_SSTL2_II I/O standards, including DCI terminated versions. Added electro-static discharge (ESD) data for the XC3S2000 and larger FPGAs (Table 28). Added link to Spartan-3 FPGA errata notices and how to receive automatic notifications of data sheet or errata changes.                                                  |

| 04/03/06 | 2.0     | Upgraded Module 3, removing Preliminary status. Moved XC3S5000 to Production status in Table 39.<br>Finalized I/O timing on XC3S5000 for v1.38 speed files. Added minimum timing values for various logic<br>and I/O paths. Corrected labels for $R_{PU}$ and $R_{PD}$ and updated $R_{PD}$ conditions for in Table 33. Added final<br>mask revision 'E' specifications for LVDS_25, RSDS_25, LVDSEXT_25 differential outputs to Table 38.<br>Added BLVDS termination requirements to Figure 34. Improved recommended Simultaneous Switching<br>Outputs (SSOs) limits in Table 50 for quad-flat packaged based on silicon testing using devices soldered<br>on a printed circuit board. Updated Note 2 in Table 63. Updated Note 6 in Table 30. Added INIT_B<br>minimum pulse width specification, $T_{INIT}$ , to Table 65.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 04/26/06 | 2.1     | Updated document links.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

Once the FPGA enters User mode after completing configuration, the DONE pin no longer drives the DONE pin Low. The bitstream generator option DonePin determines whether or not a pull-up resistor is present on the DONE pin to pull the pin to VCCAUX. If the pull-up resistor is eliminated, then the DONE pin must be pulled High using an external pull-up resistor or one of the FPGAs in the design must actively drive the DONE pin High via the DriveDone bitstream generator option.

The bitstream generator option DriveDone causes the FPGA to actively drive the DONE output High after configuration. This option should only be used in single-FPGA designs or on the last FPGA in a multi-FPGA daisy-chain.

By default, the bitstream generator software retains the pull-up resistor and does not actively drive the DONE pin as highlighted in Table 74, which shows the interaction of these bitstream options in single- and multi-FPGA designs.

| DonePin  | DriveDone | Single- or Multi-<br>FPGA Design | Comments                                                                                                                         |

|----------|-----------|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| Pullnone | No        | Single                           | External pull-up resistor, with value between $330\Omega$ to $3.3k\Omega$ , required on DONE.                                    |

| Pullnone | No        | Multi                            | External pull-up resistor, with value between $330\Omega$ to $3.3k\Omega$ , required on common node connecting to all DONE pins. |

| Pullnone | Yes       | Single                           | OK, no external requirements.                                                                                                    |

| Pullnone | Yes       | Multi                            | DriveDone on last device in daisy-chain only. No external requirements.                                                          |

| Pullup   | No        | Single                           | OK, but pull-up on DONE pin has slow rise time. May require 330 $\Omega$ pull-up resistor for high CCLK frequencies.             |

| Pullup   | No        | Multi                            | External pull-up resistor, with value between $330\Omega$ to $3.3k\Omega$ , required on common node connecting to all DONE pins. |

| Pullup   | Yes       | Single                           | OK, no external requirements.                                                                                                    |

| Pullup   | Yes       | Multi                            | DriveDone on last device in daisy-chain only. No external requirements.                                                          |

Table 74: DonePin and DriveDone Bitstream Option Interaction

# M2, M1, M0: Configuration Mode Selection

The M2, M1, and M0 inputs select the FPGA configuration mode, as described in Table 75. The logic levels applied to the mode pins are sampled on the rising edge of INIT\_B.

| Configuration Mode  | M2 | M1 | MO |

|---------------------|----|----|----|

| Master Serial       | 0  | 0  | 0  |

| Slave Serial        | 1  | 1  | 1  |

| Master Parallel     | 0  | 1  | 1  |

| Slave Parallel      | 1  | 1  | 0  |

| JTAG                | 1  | 0  | 1  |

| Reserved            | 0  | 0  | 1  |

| Reserved            | 0  | 1  | 0  |

| Reserved            | 1  | 0  | 0  |

| After Configuration | Х  | Х  | Х  |

Table 75: Spartan-3 FPGA Mode Select Settings

## Notes:

1. X =don't care, either 0 or 1.

Before and during configuration, the mode pins have an internal pull-up resistor to VCCAUX, regardless of the HSWAP\_EN pin. If the mode pins are unconnected, then the FPGA defaults to the Slave Serial configuration mode. After configuration successfully completes, any levels applied to these input are ignored. Furthermore, the bitstream generator options M0Pin, M1Pin, and M2Pin determines whether a pull-up resistor, pull-down resistor, or no resistor is present on its respective mode pin, M0, M1, or M2.

# **EXILINX**

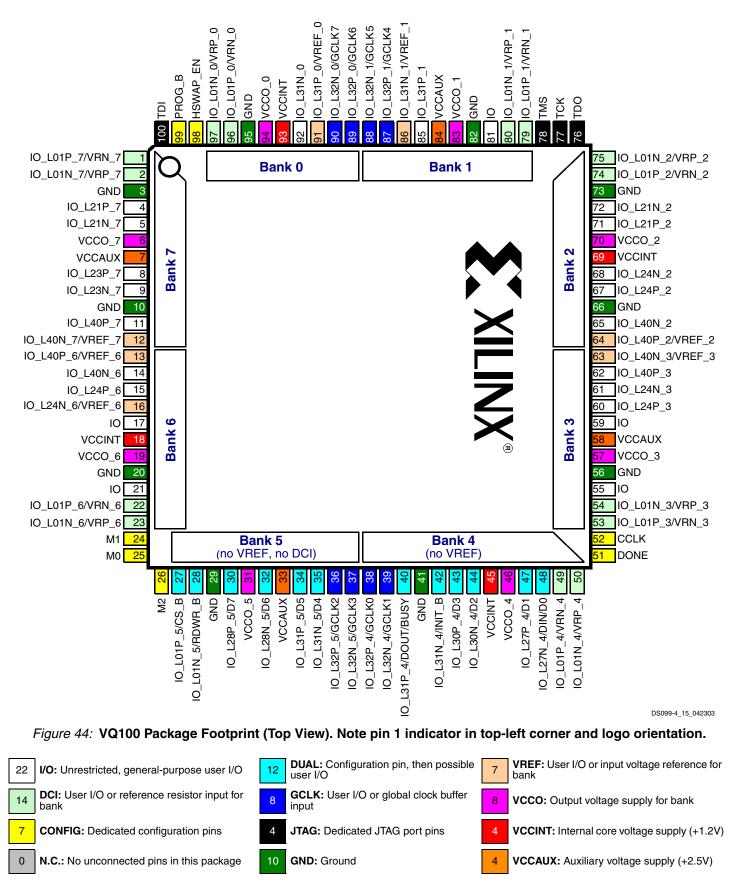

# VQ100 Footprint

# Table 91: TQ144 Package Pinout (Cont'd)

| Bank | XC3S50, XC3S200,<br>XC3S400 Pin Name | TQ144 Pin<br>Number | Туре |

|------|--------------------------------------|---------------------|------|

| 5    | IO_L32P_5/GCLK2                      | P52                 | GCLK |

| 6    | IO_L01N_6/VRP_6                      | P36                 | DCI  |

| 6    | IO_L01P_6/VRN_6                      | P35                 | DCI  |

| 6    | IO_L20N_6                            | P33                 | I/O  |

| 6    | IO_L20P_6                            | P32                 | I/O  |

| 6    | IO_L21N_6                            | P31                 | I/O  |

| 6    | IO_L21P_6                            | P30                 | I/O  |

| 6    | IO_L22N_6                            | P28                 | I/O  |

| 6    | IO_L22P_6                            | P27                 | I/O  |

| 6    | IO_L23N_6                            | P26                 | I/O  |

| 6    | IO_L23P_6                            | P25                 | I/O  |

| 6    | IO_L24N_6/VREF_6                     | P24                 | VREF |

| 6    | IO_L24P_6                            | P23                 | I/O  |

| 6    | IO_L40N_6                            | P21                 | I/O  |

| 6    | IO_L40P_6/VREF_6                     | P20                 | VREF |

| 7    | IO/VREF_7                            | P4                  | VREF |

| 7    | IO_L01N_7/VRP_7                      | P2                  | DCI  |

| 7    | IO_L01P_7/VRN_7                      | P1                  | DCI  |

| 7    | IO_L20N_7                            | P6                  | I/O  |

| 7    | IO_L20P_7                            | P5                  | I/O  |

| 7    | IO_L21N_7                            | P8                  | I/O  |

| 7    | IO_L21P_7                            | P7                  | I/O  |

| 7    | IO_L22N_7                            | P11                 | I/O  |

| 7    | IO_L22P_7                            | P10                 | I/O  |

| 7    | IO_L23N_7                            | P13                 | I/O  |

| 7    | IO_L23P_7                            | P12                 | I/O  |

| 7    | IO_L24N_7                            | P15                 | I/O  |

| 7    | IO_L24P_7                            | P14                 | I/O  |

| 7    | IO_L40N_7/VREF_7                     | P18                 | VREF |

| 7    | IO_L40P_7                            | P17                 | I/O  |

| 0,1  | VCCO_TOP                             | P126                | VCCO |

| 0,1  | VCCO_TOP                             | P138                | VCCO |

| 0,1  | VCCO_TOP                             | P115                | VCCO |

| 2,3  | VCCO_RIGHT                           | P106                | VCCO |

| 2,3  | VCCO_RIGHT                           | P75                 | VCCO |

| 2,3  | VCCO_RIGHT                           | P91                 | VCCO |

| 4,5  | VCCO_BOTTOM                          | P54                 | VCCO |

| 4,5  | VCCO_BOTTOM                          | P43                 | VCCO |

| 4,5  | VCCO_BOTTOM                          | P66                 | VCCO |

| 6,7  | VCCO_LEFT                            | P19                 | VCCO |

### Table 100: FG456 Package Pinout (Cont'd)

| Bank | 3S400<br>Pin Name | 3S1000, 3S1500, 3S2000<br>Pin Name | FG456<br>Pin Number | Туре |

|------|-------------------|------------------------------------|---------------------|------|

| 1    | IO_L15P_1         | IO_L15P_1                          | E17                 | I/O  |

| 1    | IO_L16N_1         | IO_L16N_1                          | B17                 | I/O  |

| 1    | IO_L16P_1         | IO_L16P_1                          | C17                 | I/O  |

| 1    | N.C. (�)          | IO_L19N_1                          | C16                 | I/O  |

| 1    | N.C. (�)          | IO_L19P_1                          | D16                 | I/O  |

| 1    | N.C. (�)          | IO_L22N_1                          | A16                 | I/O  |

| 1    | N.C. (�)          | IO_L22P_1                          | B16                 | I/O  |

| 1    | IO_L24N_1         | IO_L24N_1                          | D15                 | I/O  |

| 1    | IO_L24P_1         | IO_L24P_1                          | E15                 | I/O  |

| 1    | IO_L25N_1         | IO_L25N_1                          | B15                 | I/O  |

| 1    | IO_L25P_1         | IO_L25P_1                          | A15                 | I/O  |

| 1    | IO_L27N_1         | IO_L27N_1                          | D14                 | I/O  |

| 1    | IO_L27P_1         | IO_L27P_1                          | E14                 | I/O  |

| 1    | IO_L28N_1         | IO_L28N_1                          | A14                 | I/O  |

| 1    | IO_L28P_1         | IO_L28P_1                          | B14                 | I/O  |

| 1    | IO_L29N_1         | IO_L29N_1                          | C13                 | I/O  |

| 1    | IO_L29P_1         | IO_L29P_1                          | D13                 | I/O  |

| 1    | IO_L30N_1         | IO_L30N_1                          | A13                 | I/O  |

| 1    | IO_L30P_1         | IO_L30P_1                          | B13                 | I/O  |

| 1    | IO_L31N_1/VREF_1  | IO_L31N_1/VREF_1                   | D12                 | VREF |

| 1    | IO_L31P_1         | IO_L31P_1                          | E12                 | I/O  |

| 1    | IO_L32N_1/GCLK5   | IO_L32N_1/GCLK5                    | B12                 | GCLK |

| 1    | IO_L32P_1/GCLK4   | IO_L32P_1/GCLK4                    | C12                 | GCLK |

| 1    | VCCO_1            | VCCO_1                             | C15                 | VCCO |

| 1    | VCCO_1            | VCCO_1                             | F15                 | VCCO |

| 1    | VCCO_1            | VCCO_1                             | G12                 | VCCO |

| 1    | VCCO_1            | VCCO_1                             | G13                 | VCCO |

| 1    | VCCO_1            | VCCO_1                             | G14                 | VCCO |

| 2    | IO                | IO                                 | C22                 | I/O  |

| 2    | IO_L01N_2/VRP_2   | IO_L01N_2/VRP_2                    | C20                 | DCI  |

| 2    | IO_L01P_2/VRN_2   | IO_L01P_2/VRN_2                    | C21                 | DCI  |

| 2    | IO_L16N_2         | IO_L16N_2                          | D20                 | I/O  |

| 2    | IO_L16P_2         | IO_L16P_2                          | D19                 | I/O  |