# E·XFL

### AMD Xilinx - XC3S400-4PQ208C Datasheet

Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                             |

|--------------------------------|-------------------------------------------------------------|

| Product Status                 | Obsolete                                                    |

| Number of LABs/CLBs            | 896                                                         |

| Number of Logic Elements/Cells | 8064                                                        |

| Total RAM Bits                 | 294912                                                      |

| Number of I/O                  | 141                                                         |

| Number of Gates                | 400000                                                      |

| Voltage - Supply               | 1.14V ~ 1.26V                                               |

| Mounting Type                  | Surface Mount                                               |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                             |

| Package / Case                 | 208-BFQFP                                                   |

| Supplier Device Package        | 208-PQFP (28x28)                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/xilinx/xc3s400-4pq208c |

|                                |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

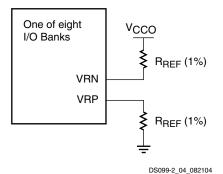

The DCI feature operates independently for each of the device's eight banks. Each bank has an 'N' reference pin (VRN) and a 'P' reference pin, (VRP), to calibrate driver and termination resistance. Only when using a DCI standard on a given bank do these two pins function as VRN and VRP. When not using a DCI standard, the two pins function as user I/Os. As shown in Figure 9, add an external reference resistor to pull the VRN pin up to V<sub>CCO</sub> and another reference resistor to pull the VRP pin down to GND. Also see Figure 42, page 116. Both resistors have the same value—commonly  $50\Omega$ —with one-percent tolerance, which is either the characteristic impedance of the line or twice that, depending on the DCI standard in use. Standards having a symbol name that contains the letters "DV2" use a reference resistor value that is twice the line impedance. DCI adjusts the output driver impedance to match the reference resistors' value or half that, according to the standard. DCI always adjusts the on-chip termination resistors to directly match the reference resistors' value.

Figure 9: Connection of Reference Resistors (R<sub>BFF</sub>)

The rules guiding the use of DCI standards on banks are as follows:

- No more than one DCI I/O standard with a Single Termination is allowed per bank.

- No more than one DCI I/O standard with a Split Termination is allowed per bank.

- Single Termination, Split Termination, Controlled- Impedance Driver, and Controlled-Impedance Driver with Half Impedance can co-exist in the same bank.

See also The Organization of IOBs into Banks, immediately below, and DCI: User I/O or Digitally Controlled Impedance Resistor Reference Input, page 115.

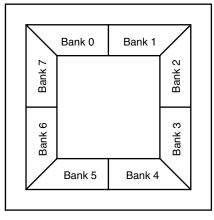

### The Organization of IOBs into Banks

IOBs are allocated among eight banks, so that each side of the device has two banks, as shown in Figure 10. For all packages, each bank has independent  $V_{REF}$  lines. For example,  $V_{REF}$  Bank 3 lines are separate from the  $V_{REF}$  lines going to all other banks.

For the Very Thin Quad Flat Pack (VQ), Plastic Quad Flat Pack (PQ), Fine Pitch Thin Ball Grid Array (FT), and Fine Pitch Ball Grid Array (FG) packages, each bank has dedicated  $V_{CCO}$  lines. For example, the  $V_{CCO}$  Bank 7 lines are separate from the  $V_{CCO}$  lines going to all other banks. Thus, Spartan-3 devices in these packages support eight independent  $V_{CCO}$  supplies.

DS099-2\_03\_082104

Figure 10: Spartan-3 FPGA I/O Banks (Top View)

Phase Shifting: The DCM provides the ability to shift the phase of all its output clock signals with respect to its input clock signal.

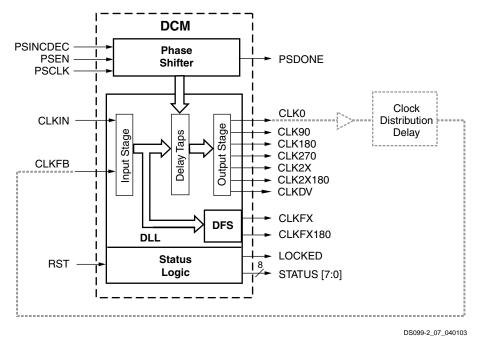

The DCM has four functional components: the Delay-Locked Loop (DLL), the Digital Frequency Synthesizer (DFS), the Phase Shifter (PS), and the Status Logic. Each component has its associated signals, as shown in Figure 19.

Figure 19: DCM Functional Blocks and Associated Signals

# **Delay-Locked Loop (DLL)**

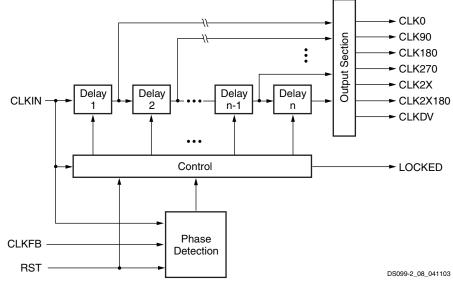

The most basic function of the DLL component is to eliminate clock skew. The main signal path of the DLL consists of an input stage, followed by a series of discrete delay elements or *taps*, which in turn leads to an output stage. This path together with logic for phase detection and control forms a system complete with feedback as shown in Figure 20.

Figure 20: Simplified Functional Diagram of DLL

The output frequency (f<sub>CLKEX</sub>) can be expressed as a function of the incoming clock frequency (f<sub>CLKIN</sub>) as follows:

Regarding the two attributes, it is possible to assign any combination of integer values, provided that two conditions are met:

- The two values fall within their corresponding ranges, as specified in Table 18.

- The f<sub>CLKFX</sub> frequency calculated from the above expression accords with the DCM's operating frequency specifications.

For example, if  $CLKFX_MULTIPLY = 5$  and  $CLKFX_DIVIDE = 3$ , then the frequency of the output clock signal would be 5/3 that of the input clock signal.

#### **DFS Frequency Modes**

The DFS supports two operating modes, High Frequency and Low Frequency, with each specified over a different clock frequency range. The DFS\_FREQUENCY\_MODE attribute chooses between the two modes. When the attribute is set to LOW, the Low Frequency mode permits the two DFS outputs to operate over a low-to-moderate frequency range. When the attribute is set to HIGH, the High Frequency mode allows both these outputs to operate at the highest possible frequencies.

#### DFS With or Without the DLL

The DFS component can be used with or without the DLL component:

Without the DLL, the DFS component multiplies or divides the CLKIN signal frequency according to the respective CLKFX\_MULTIPLY and CLKFX\_DIVIDE values, generating a clock with the new target frequency on the CLKFX and CLKFX180 outputs. Though classified as belonging to the DLL component, the CLKIN input is shared with the DFS component. This case does not employ feedback loop; therefore, it cannot correct for clock distribution delay.

With the DLL, the DFS operates as described in the preceding case, only with the additional benefit of eliminating the clock distribution delay. In this case, a feedback loop from the CLK0 output to the CLKFB input must be present.

The DLL and DFS components work together to achieve this phase correction as follows: Given values for the CLKFX\_MULTIPLY and CLKFX\_DIVIDE attributes, the DLL selects the delay element for which the output clock edge coincides with the input clock edge whenever mathematically possible. For example, when CLKFX\_MULTIPLY = 5 and CLKFX\_DIVIDE = 3, the input and output clock edges will coincide every three input periods, which is equivalent in time to five output periods.

Smaller CLKFX\_MULTIPLY and CLKFX\_DIVIDE values achieve faster lock times. With no factors common to the two attributes, alignment will occur once with every number of cycles equal to the CLKFX\_DIVIDE value. Therefore, it is recommended that the user reduce these values by factoring wherever possible. For example, given CLKFX\_MULTIPLY = 9 and CLKFX\_DIVIDE = 6, removing a factor of three yields CLKFX\_MULTIPLY = 3 and CLKFX\_DIVIDE = 2. While both value-pairs will result in the multiplication of clock frequency by 3/2, the latter value-pair will enable the DLL to lock more quickly.

#### Table 18: DFS Attributes

| Attribute          | Description                                            | Values               |

|--------------------|--------------------------------------------------------|----------------------|

| DFS_FREQUENCY_MODE | Chooses between High Frequency and Low Frequency modes | Low, High            |

| CLKFX_MULTIPLY     | Frequency multiplier constant                          | Integer from 2 to 32 |

| CLKFX_DIVIDE       | Frequency divisor constant                             | Integer from 1 to 32 |

#### Table 19: DFS Signals

| Signal   | Direction | Description                                                                                                                                       |  |  |

|----------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| CLKFX    | Output    | Multiplies the CLKIN frequency by the attribute-value ratio (CLKFX_MULTIPLY/CLKFX_DIVIDE) to generate a clock signal with a new target frequency. |  |  |

| CLKFX180 | Output    | Generates a clock signal with same frequency as CLKFX, only shifted 180° out-of-phase.                                                            |  |  |

# The Standard Configuration Interface

Configuration signals belong to one of two different categories: Dedicated or Dual-Purpose. Which category determines which of the FPGA's power rails supplies the signal's driver and, thus, helps describe the electrical characteristics at the pin.

The Dedicated configuration pins include PROG\_B, HSWAP\_EN, TDI, TMS, TCK, TDO, CCLK, DONE, and M0-M2. These pins are powered by the V<sub>CCAUX</sub> supply.

The Dual-Purpose configuration pins comprise INIT\_B, DOUT, BUSY, RDWR\_B, CS\_B, and DIN/D0-D7. Each of these pins, according to its bank placement, uses the  $V_{CCO}$  lines for either Bank 4 (VCCO\_4 on most packages, VCCO\_BOTTOM on TQ144 and CP132 packages) or Bank 5 (VCCO\_5). All the signals used in the serial configuration modes rely on VCCO\_4 power. Signals used in the parallel configuration modes and Readback require from VCCO\_5 as well as from VCCO\_4.

Both the Dedicated signals described above and the Dual-Purpose signals constitute the configuration interface. The Dedicated pins, powered by the 2.5V  $V_{CCAUX}$  supply, always use the LVCMOS25 I/O standard. The Dual-Purpose signals, however, are powered by the VCCO\_4 supply and also by the VCCO\_5 supply in the Parallel configuration modes. The simplest configuration interface uses 2.5V for VCCO\_4 and VCCO\_5, if required. However, VCCO\_4 and, if needed, VCCO\_5 can be voltages other than 2.5V but then the configuration interface will have two voltage levels: 2.5V for V<sub>CCAUX</sub> and a separate  $V_{CCO}$  supply. The Dual-Purpose signals default to the LVCMOS input and output levels for the associated  $V_{CCO}$  voltage supply.

## **3.3V-Tolerant Configuration Interface**

A 3.3V-tolerant configuration interface simply requires adding a few external resistors as described in detail in <u>XAPP453</u>: *The 3.3V Configuration of Spartan-3 FPGAs.*

The 3.3V-tolerance is implemented as follows (a similar approach can be used for other supply voltage levels):

Apply 3.3V to VCCO\_4 and, in some configuration modes, to VCCO\_5 to power the Dual-Purpose configuration pins. This scales the output voltages and input thresholds associated with these pins so that they become 3.3V-compatible.

Apply 2.5V to  $V_{CCAUX}$  to power the Dedicated configuration pins. For 3.3V-tolerance, the Dedicated inputs require series resistors to limit the incoming current to 10 mA or less. The Dedicated outputs have reduced noise margin when the FPGA drives a High logic level into another device's 3.3V receiver. Choose a power regulator or supply that can tolerate reverse current on the V<sub>CCAUX</sub> lines.

## **Configuration Modes**

Spartan-3 FPGAs support the following five configuration modes:

- Slave Serial mode

- Master Serial mode

- Slave Parallel (SelectMAP) mode

- Master Parallel (SelectMAP) mode

- Boundary-Scan (JTAG) mode (IEEE 1532/IEEE 1149.1)

#### Slave Serial Mode

In Slave Serial mode, the FPGA receives configuration data in bit-serial form from a serial PROM or other serial source of configuration data. The FPGA on the far right of Figure 26 is set for the Slave Serial mode. The CCLK pin on the FPGA is an input in this mode. The serial bitstream must be set up at the DIN input pin a short time before each rising edge of the externally generated CCLK.

Multiple FPGAs can be daisy-chained for configuration from a single source. After a particular FPGA has been configured, the data for the next device is routed internally to the DOUT pin. The data on the DOUT pin changes on the falling edge of CCLK.

# **EXILINX**.

# Additional Configuration Details

Additional details about the Spartan-3 FPGA configuration architecture and command set are available in <u>UG332</u>: *Spartan-3 Generation Configuration User Guide* and in application note <u>XAPP452</u>: *Spartan-3 Advanced Configuration Architecture*.

# **Powering Spartan-3 FPGAs**

# Voltage Regulators

Various power supply manufacturers offer complete power solutions for Xilinx FPGAs, including some with integrated multi-rail regulators specifically designed for Spartan-3 FPGAs. The Xilinx Power Corner web page provides links to vendor solution guides as well as Xilinx power estimation and analysis tools.

# Power Distribution System (PDS) Design and Bypass/Decoupling Capacitors

Good power distribution system (PDS) design is important for all FPGA designs, especially for high-performance applications. Proper design results in better overall performance, lower clock and DCM jitter, and a generally more robust system. Before designing the printed circuit board (PCB) for the FPGA design, review application note <u>XAPP623</u>: *Power Distribution System (PDS) Design: Using Bypass/Decoupling Capacitors*.

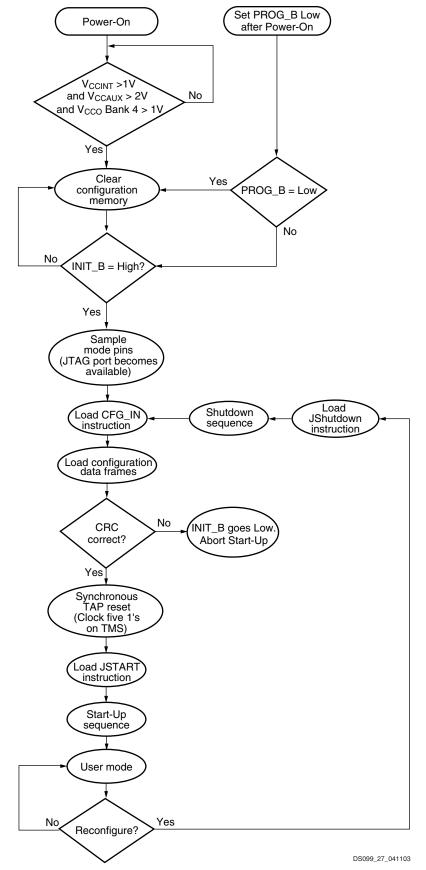

# **Power-On Behavior**

Spartan-3 FPGAs have a built-in Power-On Reset (POR) circuit that monitors the three power rails required to successfully configure the FPGA. At power-up, the POR circuit holds the FPGA in a reset state until the  $V_{CCINT}$ ,  $V_{CCAUX}$ , and  $V_{CCO}$  Bank 4 supplies reach their respective input threshold levels (see Table 29, page 59). After all three supplies reach their respective threshold, the POR reset is released and the FPGA begins its configuration process.

Because the three supply inputs must be valid to release the POR reset and can be supplied in any order, there are no specific voltage sequencing requirements. However, applying the FPGA's  $V_{CCAUX}$  supply before the  $V_{CCINT}$  supply uses the least I<sub>CCINT</sub> current.

Once all three supplies are valid, the minimum current required to power-on the FPGA is equal to the worst-case quiescent current, as specified in Table 34, page 62. Spartan-3 FPGAs do not require Power-On Surge (POS) current to successfully configure.

# Surplus I<sub>CCINT</sub> if V<sub>CCINT</sub> Applied before V<sub>CCAUX</sub>

If the  $V_{CCINT}$  supply is applied before the  $V_{CCAUX}$  supply, the FPGA may draw a surplus  $I_{CCINT}$  current in addition to the  $I_{CCINT}$  quiescent current levels specified in Table 34. The momentary additional  $I_{CCINT}$  surplus current might be a few hundred milliamperes under nominal conditions, significantly less than the instantaneous current consumed by the bypass capacitors at power-on. However, the surplus current immediately disappears when the  $V_{CCAUX}$  supply is applied, and, in response, the FPGA's  $I_{CCINT}$  quiescent current demand drops to the levels specified in Table 34. The FPGA does not use nor does it require the surplus current to successfully power-on and configure. If applying  $V_{CCINT}$  before  $V_{CCAUX}$ , ensure that the regulator does not have a foldback feature that could inadvertently shut down in the presence of the surplus current.

# Maximum Allowed $V_{\text{CCINT}}$ Ramp Rate on Early Devices, if $V_{\text{VCCINT}} \text{Supply is Last in Sequence}$

All devices with a mask revision code 'E' or later do not have a V<sub>CCINT</sub> ramp rate requirement. See Mask and Fab Revisions, page 58.

Early Spartan-3 FPGAs were produced at a 200 mm wafer production facility and are identified by a fabrication/process code of "FQ" on the device top marking, as shown in Package Marking, page 5. These "FQ" devices have a maximum  $V_{CCINT}$  ramp rate requirement if and only if  $V_{CCINT}$  is the last supply to ramp, after the  $V_{CCAUX}$  and  $V_{CCO}$  Bank 4 supplies. This maximum ramp rate appears as  $T_{CCINT}$  in Table 30, page 60.

# Minimum Allowed V<sub>CCO</sub> Ramp Rate on Early Devices

Devices shipped since 2006 essentially have no  $V_{CCO}$  ramp rate limits, shown in Table 30, page 60. Similarly, all devices with a mask revision code 'E' or later do not have a  $V_{CCO}$  ramp rate limit. See Mask and Fab Revisions, page 58.

## Notice of Disclaimer

THE XILINX HARDWARE FPGA AND CPLD DEVICES REFERRED TO HEREIN ("PRODUCTS") ARE SUBJECT TO THE TERMS AND CONDITIONS OF THE XILINX LIMITED WARRANTY WHICH CAN BE VIEWED AT <a href="http://www.xilinx.com/warranty.htm">http://www.xilinx.com/warranty.htm</a>. THIS LIMITED WARRANTY DOES NOT EXTEND TO ANY USE OF PRODUCTS IN AN APPLICATION OR ENVIRONMENT THAT IS NOT WITHIN THE SPECIFICATIONS STATED IN THE XILINX DATA SHEET. ALL SPECIFICATIONS ARE SUBJECT TO CHANGE WITHOUT NOTICE. PRODUCTS ARE NOT DESIGNED OR INTENDED TO BE FAIL-SAFE OR FOR USE IN ANY APPLICATION REQUIRING FAIL-SAFE PERFORMANCE, SUCH AS LIFE-SUPPORT OR SAFETY DEVICES OR SYSTEMS, OR ANY OTHER APPLICATION THAT INVOKES THE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). USE OF PRODUCTS IN CRITICAL APPLICATIONS IS AT THE SOLE RISK OF CUSTOMER, SUBJECT TO APPLICABLE LAWS AND REGULATIONS.

#### **CRITICAL APPLICATIONS DISCLAIMER**

XILINX PRODUCTS (INCLUDING HARDWARE, SOFTWARE AND/OR IP CORES) ARE NOT DESIGNED OR INTENDED TO BE FAIL-SAFE, OR FOR USE IN ANY APPLICATION REQUIRING FAIL-SAFE PERFORMANCE, SUCH AS IN LIFE-SUPPORT OR SAFETY DEVICES OR SYSTEMS, CLASS III MEDICAL DEVICES, NUCLEAR FACILITIES, APPLICATIONS RELATED TO THE DEPLOYMENT OF AIRBAGS, OR ANY OTHER APPLICATIONS THAT COULD LEAD TO DEATH, PERSONAL INJURY OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE (INDIVIDUALLY AND COLLECTIVELY, "CRITICAL APPLICATIONS"). FURTHERMORE, XILINX PRODUCTS ARE NOT DESIGNED OR INTENDED FOR USE IN ANY APPLICATIONS THAT AFFECT CONTROL OF A VEHICLE OR AIRCRAFT, UNLESS THERE IS A FAIL-SAFE OR REDUNDANCY FEATURE (WHICH DOES NOT INCLUDE USE OF SOFTWARE IN THE XILINX DEVICE TO IMPLEMENT THE REDUNDANCY) AND A WARNING SIGNAL UPON FAILURE TO THE OPERATOR. CUSTOMER AGREES, PRIOR TO USING OR DISTRIBUTING ANY SYSTEMS THAT INCORPORATE XILINX PRODUCTS, TO THOROUGHLY TEST THE SAME FOR SAFETY PURPOSES. TO THE MAXIMUM EXTENT PERMITTED BY APPLICABLE LAW, CUSTOMER ASSUMES THE SOLE RISK AND LIABILITY OF ANY USE OF XILINX PRODUCTS IN CRITICAL APPLICATIONS.

#### AUTOMOTIVE APPLICATIONS DISCLAIMER

XILINX PRODUCTS ARE NOT DESIGNED OR INTENDED TO BE FAIL-SAFE, OR FOR USE IN ANY APPLICATION REQUIRING FAIL-SAFE PERFORMANCE, SUCH AS APPLICATIONS RELATED TO: (I) THE DEPLOYMENT OF AIRBAGS, (II) CONTROL OF A VEHICLE, UNLESS THERE IS A FAIL-SAFE OR REDUNDANCY FEATURE (WHICH DOES NOT INCLUDE USE OF SOFTWARE IN THE XILINX DEVICE TO IMPLEMENT THE REDUNDANCY) AND A WARNING SIGNAL UPON FAILURE TO THE OPERATOR, OR (III) USES THAT COULD LEAD TO DEATH OR PERSONAL INJURY. CUSTOMER ASSUMES THE SOLE RISK AND LIABILITY OF ANY USE OF XILINX PRODUCTS IN SUCH APPLICATIONS.

# Spartan-3 FPGA Family: DC and Switching Characteristics

DS099 (v3.0) October 29, 2012

#### **Product Specification**

# **DC Electrical Characteristics**

In this section, specifications may be designated as Advance, Preliminary, or Production. These terms are defined as follows:

- <u>Advance</u>: Initial estimates are based on simulation, early characterization, and/or extrapolation from the characteristics of other families. Values are subject to change. Although speed grades with this designation are considered relatively stable and conservative, some under-reporting might still occur. Use as estimates, not for production.

- **Preliminary:** Based on complete early silicon characterization. Devices and speed grades with this designation are intended to give a better indication of the expected performance of production silicon. The probability of under-reported delays is greatly reduced compared to Advance data. Use as estimates, not for production.

- <u>Production</u>: These specifications are approved only after silicon has been characterized over numerous production lots. There is no under-reporting of delays, and customers receive formal notification of any subsequent changes. Parameter values are considered stable with no future changes expected.

Production-quality systems must only use FPGA designs compiled with a Production status speed file. FPGA designs using a less mature speed file designation should only be used during system prototyping or preproduction qualification. FPGA designs with speed files designated as Advance or Preliminary should not be used in a production-quality system.

Whenever a speed file designation changes, as a device matures toward Production status, rerun the <u>latest Xilinx ISE®</u> software on the FPGA design to ensure that the FPGA design incorporates the latest timing information and software updates.

All parameter limits are representative of worst-case supply voltage and junction temperature conditions. The following applies unless otherwise noted: The parameter values published in this module apply to all Spartan®-3 devices. AC and DC characteristics are specified using the same numbers for both commercial and industrial grades. All parameters representing voltages are measured with respect to GND.

#### Mask and Fab Revisions

Some specifications list different values for one or more mask or fab revisions, indicated by the device top marking (see Package Marking, page 5). The revision differences involve the power ramp rates, differential DC specifications, and DCM characteristics. The most recent revision (mask rev E and GQ fab/geometry code) is errata-free with improved specifications than earlier revisions.

Mask rev E with fab rev GQ has been shipping since 2005 (see <u>XCN05009</u>) and has been 100% of Xilinx Spartan-3 device shipments since 2006. SCD 0974 was provided to ensure the receipt of the rev E silicon, but it is no longer needed. Parts ordered under the SCD appended "0974" to the standard part number. For example, "XC3S50-4VQ100C" became "XC3S50-4VQ100C0974".

| Symbol             | Description                                                                                 | Conditions                     |                  | Min   | Мах                      | Units |

|--------------------|---------------------------------------------------------------------------------------------|--------------------------------|------------------|-------|--------------------------|-------|

| V <sub>CCINT</sub> | Internal supply voltage relative to GND                                                     |                                |                  | -0.5  | 1.32                     | V     |

| V <sub>CCAUX</sub> | Auxiliary supply voltage relative to GND                                                    | supply voltage relative to GND |                  | -0.5  | 3.00                     | V     |

| V <sub>CCO</sub>   | Output driver supply voltage relative to GND                                                |                                |                  | -0.5  | 3.75                     | V     |

| $V_{REF}$          | Input reference voltage relative to GND                                                     |                                |                  | -0.5  | V <sub>CCO</sub> +0.5    | V     |

| V <sub>IN</sub>    | Voltage applied to all User I/O pins and Dual-Purpose pins relative to GND <sup>(2,4)</sup> | Driver in a                    | Commercial       | -0.95 | 4.4                      | V     |

|                    | Dual-Purpose pins relative to GND <sup>(2,4)</sup>                                          | high-impedance<br>state        | Industrial       | -0.85 | 4.3                      |       |

|                    | Voltage applied to all Dedicated pins relative to GND <sup>(3)</sup>                        |                                | All temp. ranges | -0.5  | V <sub>CCAUX</sub> + 0.5 | V     |

#### Table 28: Absolute Maximum Ratings

© Copyright 2003–2012 Xilinx, Inc. XILINX, the Xilinx logo, Virtex, Spartan, ISE, Artix, Kintex, Zynq, Vivado and other designated brands included herein are trademarks of Xilinx in the United States and other countries. PCI and PCI-X are trademarks of PCI-SIG and used under license. All other trademarks are the property of their respective owners.

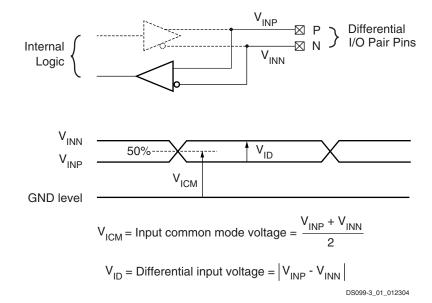

Figure 32: Differential Input Voltages

| Signal Standard                         |         | V <sub>CCO</sub> <sup>(1)</sup> V <sub>ID</sub> <sup>(3)</sup> V <sub>IC</sub> |         | V <sub>ID</sub> <sup>(3)</sup> |          | V <sub>ICM</sub> | V <sub>ICM</sub> |         |         |

|-----------------------------------------|---------|--------------------------------------------------------------------------------|---------|--------------------------------|----------|------------------|------------------|---------|---------|

| (IOSTANDARD)                            | Min (V) | Nom (V)                                                                        | Max (V) | Min (mV)                       | Nom (mV) | Max (mV)         | Min (V)          | Nom (V) | Max (V) |

| LDT_25 (ULVDS_25)                       | 2.375   | 2.50                                                                           | 2.625   | 200                            | 600      | 1000             | 0.44             | 0.60    | 0.78    |

| LVDS_25, LVDS_25_DCI                    | 2.375   | 2.50                                                                           | 2.625   | 100                            | 350      | 600              | 0.30             | 1.25    | 2.20    |

| BLVDS_25                                | 2.375   | 2.50                                                                           | 2.625   | -                              | 350      | -                | -                | 1.25    | -       |

| LVDSEXT_25,<br>LVDSEXT_25_DCI           | 2.375   | 2.50                                                                           | 2.625   | 100                            | 540      | 1000             | 0.30             | 1.20    | 2.20    |

| LVPECL_25                               | 2.375   | 2.50                                                                           | 2.625   | 100                            | -        | -                | 0.30             | 1.20    | 2.00    |

| RSDS_25                                 | 2.375   | 2.50                                                                           | 2.625   | 100                            | 200      | -                | -                | 1.20    | -       |

| DIFF_HSTL_II_18,<br>DIFF_HSTL_II_18_DCI | 1.70    | 1.80                                                                           | 1.90    | 200                            | -        | -                | 0.80             | -       | 1.00    |

| DIFF_SSTL2_II,<br>DIFF_SSTL2_II_DCI     | 2.375   | 2.50                                                                           | 2.625   | 300                            | -        | -                | 1.05             | -       | 1.45    |

#### Notes:

1. V<sub>CCO</sub> only supplies differential output drivers, not input circuits.

2. V<sub>REF</sub> inputs are not used for any of the differential I/O standards.

3.  $V_{ID}$  is a differential measurement.

## Table 47: Output Timing Adjustments for IOB (Cont'd)

|                                                                                                                       |            |       | Add the Adju | stment Below |       |

|-----------------------------------------------------------------------------------------------------------------------|------------|-------|--------------|--------------|-------|

| Convert Output Time from LVCMOS25 with 12mA Drive and Fast Slew Rate to the<br>Following Signal Standard (IOSTANDARD) |            |       | Speed        | Grade        | Units |

|                                                                                                                       | -5         | -4    |              |              |       |

| HSLVDCI_25                                                                                                            |            |       | 0.27         | 0.31         | ns    |

| HSLVDCI_33                                                                                                            | HSLVDCI_33 |       |              |              | ns    |

| HSTL_I                                                                                                                |            |       | 0.60         | 0.69         | ns    |

| HSTL_I_DCI                                                                                                            |            |       | 0.59         | 0.68         | ns    |

| HSTL_III                                                                                                              |            |       | 0.19         | 0.22         | ns    |

| HSTL_III_DCI                                                                                                          |            |       | 0.20         | 0.23         | ns    |

| HSTL_I_18                                                                                                             |            |       | 0.18         | 0.21         | ns    |

| HSTL_I_DCI_18                                                                                                         |            |       | 0.17         | 0.19         | ns    |

| HSTL_II_18                                                                                                            |            |       | -0.02        | -0.01        | ns    |

| HSTL_II_DCI_18                                                                                                        |            |       | 0.75         | 0.86         | ns    |

| HSTL_III_18                                                                                                           |            |       | 0.28         | 0.32         | ns    |

| HSTL_III_DCI_18                                                                                                       |            |       | 0.28         | 0.32         | ns    |

| LVCMOS12                                                                                                              | Slow       | 2 mA  | 7.60         | 8.73         | ns    |

|                                                                                                                       |            | 4 mA  | 7.42         | 8.53         | ns    |

|                                                                                                                       |            | 6 mA  | 6.67         | 7.67         | ns    |

|                                                                                                                       | Fast       | 2 mA  | 3.16         | 3.63         | ns    |

|                                                                                                                       |            | 4 mA  | 2.70         | 3.10         | ns    |

|                                                                                                                       |            | 6 mA  | 2.41         | 2.77         | ns    |

| LVCMOS15                                                                                                              | Slow       | 2 mA  | 4.55         | 5.23         | ns    |

|                                                                                                                       |            | 4 mA  | 3.76         | 4.32         | ns    |

|                                                                                                                       |            | 6 mA  | 3.57         | 4.11         | ns    |

|                                                                                                                       |            | 8 mA  | 3.55         | 4.09         | ns    |

|                                                                                                                       |            | 12 mA | 3.00         | 3.45         | ns    |

|                                                                                                                       | Fast       | 2 mA  | 3.11         | 3.57         | ns    |

|                                                                                                                       |            | 4 mA  | 1.71         | 1.96         | ns    |

|                                                                                                                       |            | 6 mA  | 1.44         | 1.66         | ns    |

|                                                                                                                       |            | 8 mA  | 1.26         | 1.44         | ns    |

|                                                                                                                       |            | 12 mA | 1.11         | 1.27         | ns    |

| LVDCI_15                                                                                                              |            |       | 1.51         | 1.74         | ns    |

| LVDCI_DV2_15                                                                                                          |            |       | 1.32         | 1.52         | ns    |

## Table 47: Output Timing Adjustments for IOB (Cont'd)

|              |                                                                                                                       |       | Add the Adjustment Below |       |       |

|--------------|-----------------------------------------------------------------------------------------------------------------------|-------|--------------------------|-------|-------|

|              | Convert Output Time from LVCMOS25 with 12mA Drive and Fast Slew Rate to the<br>Following Signal Standard (IOSTANDARD) |       | Speed Grade              |       | Units |

| . enerni,    |                                                                                                                       |       |                          | -4    |       |

| LVCMOS18     | Slow                                                                                                                  | 2 mA  | 5.49                     | 6.31  | ns    |

|              |                                                                                                                       | 4 mA  | 3.45                     | 3.97  | ns    |

|              |                                                                                                                       | 6 mA  | 2.84                     | 3.26  | ns    |

|              |                                                                                                                       | 8 mA  | 2.62                     | 3.01  | ns    |

|              |                                                                                                                       | 12 mA | 2.11                     | 2.43  | ns    |

|              |                                                                                                                       | 16 mA | 2.07                     | 2.38  | ns    |

|              | Fast                                                                                                                  | 2 mA  | 2.50                     | 2.88  | ns    |

|              |                                                                                                                       | 4 mA  | 1.15                     | 1.32  | ns    |

|              |                                                                                                                       | 6 mA  | 0.96                     | 1.10  | ns    |

|              |                                                                                                                       | 8 mA  | 0.87                     | 1.01  | ns    |

|              |                                                                                                                       | 12 mA | 0.79                     | 0.91  | ns    |

|              |                                                                                                                       | 16 mA | 0.76                     | 0.87  | ns    |

| LVDCI_18     |                                                                                                                       |       | 0.81                     | 0.94  | ns    |

| LVDCI_DV2_18 |                                                                                                                       |       | 0.67                     | 0.77  | ns    |

| LVCMOS25     | Slow                                                                                                                  | 2 mA  | 6.43                     | 7.39  | ns    |

|              |                                                                                                                       | 4 mA  | 4.15                     | 4.77  | ns    |

|              |                                                                                                                       | 6 mA  | 3.38                     | 3.89  | ns    |

|              |                                                                                                                       | 8 mA  | 2.99                     | 3.44  | ns    |

|              |                                                                                                                       | 12 mA | 2.53                     | 2.91  | ns    |

|              |                                                                                                                       | 16 mA | 2.50                     | 2.87  | ns    |

|              |                                                                                                                       | 24 mA | 2.22                     | 2.55  | ns    |

|              | Fast                                                                                                                  | 2 mA  | 3.27                     | 3.76  | ns    |

|              |                                                                                                                       | 4 mA  | 1.87                     | 2.15  | ns    |

|              |                                                                                                                       | 6 mA  | 0.32                     | 0.37  | ns    |

|              |                                                                                                                       | 8 mA  | 0.19                     | 0.22  | ns    |

|              |                                                                                                                       | 12 mA | 0                        | 0     | ns    |

|              |                                                                                                                       | 16 mA | -0.02                    | -0.01 | ns    |

|              |                                                                                                                       | 24 mA | -0.04                    | -0.02 | ns    |

| LVDCI_25     |                                                                                                                       |       | 0.27                     | 0.31  | ns    |

| LVDCI_DV2_25 |                                                                                                                       |       | 0.16                     | 0.19  | ns    |

# **Revision History**

| Date     | Version | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 04/11/03 | 1.0     | Initial Xilinx release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 07/11/03 | 1.1     | Extended Absolute Maximum Rating for junction temperature in Table 28. Added numbers for typical quiescent supply current (Table 34) and DLL timing.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 02/06/04 | 1.2     | Revised V <sub>IN</sub> maximum rating (Table 28). Added power-on requirements (Table 30), leakage current number (Table 33), and differential output voltage levels (Table 38) for Rev. 0. Published new quiescent current numbers (Table 34). Updated pull-up and pull-down resistor strengths (Table 33). Added LVDCI_DV2 and LVPECL standards (Table 37 and Table 38). Changed CCLK setup time (Table 66 and Table 67).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 03/04/04 | 1.3     | Added timing numbers from v1.29 speed files as well as DCM timing (Table 58 through Table 63).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 08/24/04 | 1.4     | Added reference to errata documents on page 49. Clarified Absolute Maximum Ratings and added ESD information (Table 28). Explained $V_{CCO}$ ramp time measurement (Table 30). Clarified I <sub>L</sub> specification (Table 33). Updated quiescent current numbers and added information on power-on and surplus current (Table 34). Adjusted V <sub>REF</sub> range for HSTL_III and HSTL_I_18 and changed V <sub>IH</sub> min for LVCMOS12 (Table 35). Added note limiting V <sub>TT</sub> range for SSTL2_II signal standards (Table 36). Calculated V <sub>OH</sub> and V <sub>OL</sub> levels for differential standards (Table 38). Updated Switching Characteristics with speed file v1.32 (Table 40 through Table 48 and Table 51 through Table 56). Corrected IOB test conditions (Table 41). Updated DCM timing with latest characterization data (Table 58 through Table 62). Improved DCM CLKIN pulse width specification (Table 58). Recommended use of Virtex-II FPGA Jitter calculator (Table 61). Improved DCM PSCLK pulse width specification (Table 62). Changed Phase Shifter lock time parameter (Table 63). Because the BitGen option Centered_x#_y# is not necessary for Variable Phase Shift mode, removed BitGen command table and referring text. Adjusted maximum CCLK frequency for the slave serial and parallel configuration modes (Table 66). Inverted CCLK waveform (Figure 37). Adjusted JTAG setup times (Table 68). |

| 12/17/04 | 1.5     | Updated timing parameters to match v1.35 speed file. Improved $V_{CCO}$ ramp time specification (Table 30).<br>Added a note limiting the rate of change of $V_{CCAUX}$ (Table 32). Added typical quiescent current values for the XC3S2000, XC3S4000, and XC3S5000 (Table 34). Increased $I_{OH}$ and $I_{OL}$ for SSTL2-I and SSTL2-II standards (Table 36). Added SSO guidelines for the VQ, TQ, and PQ packages as well as edited SSO guidelines for the FT and FG packages (Table 50). Added maximum CCLK frequencies for configuration using compressed bitstreams (Table 66 and Table 67). Added specifications for the HSLVDCI standards (Table 35, Table 36, Table 44, Table 47, Table 48, and Table 50).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 08/19/05 | 1.6     | Updated timing parameters to match v1.37 speed file. All Spartan-3 FPGA part types, except XC3S5000, promoted to Production status. Removed V <sub>CCO</sub> ramp rate restriction from all mask revision 'E' and later devices (Table 30). Added equivalent resistance values for internal pull-up and pull-down resistors (Table 33). Added worst-case quiescent current values for XC3S2000, XC3S4000, XC3S5000 (Table 34). Added industrial temperature range specification and improved typical quiescent current values (Table 34). Improved the DLL minimum clock input frequency specification from 24 MHz down to 18 MHz (Table 58). Improved the DFS minimum and maximum clock output frequency specifications (Table 60, Table 61). Added new miscellaneous DCM specifications (Table 64), primarily affecting Industrial temperature range applications. Updated Simultaneously Switching Output Guidelines and Table 50 for QFP packages. Added information on SSTL18_II I/O standard and timing to support DDR2 SDRAM interfaces. Added differential (or complementary single-ended) DIFF_HSTL_II_18 and DIFF_SSTL2_II I/O standards, including DCI terminated versions. Added electro-static discharge (ESD) data for the XC3S2000 and larger FPGAs (Table 28). Added link to Spartan-3 FPGA errata notices and how to receive automatic notifications of data sheet or errata changes.                                                  |

| 04/03/06 | 2.0     | Upgraded Module 3, removing Preliminary status. Moved XC3S5000 to Production status in Table 39.<br>Finalized I/O timing on XC3S5000 for v1.38 speed files. Added minimum timing values for various logic<br>and I/O paths. Corrected labels for $R_{PU}$ and $R_{PD}$ and updated $R_{PD}$ conditions for in Table 33. Added final<br>mask revision 'E' specifications for LVDS_25, RSDS_25, LVDSEXT_25 differential outputs to Table 38.<br>Added BLVDS termination requirements to Figure 34. Improved recommended Simultaneous Switching<br>Outputs (SSOs) limits in Table 50 for quad-flat packaged based on silicon testing using devices soldered<br>on a printed circuit board. Updated Note 2 in Table 63. Updated Note 6 in Table 30. Added INIT_B<br>minimum pulse width specification, $T_{INIT}$ , to Table 65.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 04/26/06 | 2.1     | Updated document links.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

# TQ144: 144-lead Thin Quad Flat Package

The XC3S50, the XC3S200, and the XC3S400 are available in the 144-lead thin quad flat package, TQ144. All devices share a common footprint for this package as shown in Table 91 and Figure 46.

The TQ144 package only has four separate VCCO inputs, unlike the BGA packages, which have eight separate VCCO inputs. The TQ144 package has a separate VCCO input for the top, bottom, left, and right. However, there are still eight separate I/O banks, as shown in Table 91 and Figure 46. Banks 0 and 1 share the VCCO\_TOP input, Banks 2 and 3 share the VCCO\_RIGHT input, Banks 4 and 5 share the VCCO\_BOTTOM input, and Banks 6 and 7 share the VCCO\_LEFT input.

All the package pins appear in Table 91 and are sorted by bank number, then by pin name. Pairs of pins that form a differential I/O pair appear together in the table. The table also shows the pin number for each pin and the pin type, as defined earlier.

An electronic version of this package pinout table and footprint diagram is available for download from the Xilinx website at <a href="http://www.xilinx.com/support/documentation/data\_sheets/s3\_pin.zip">http://www.xilinx.com/support/documentation/data\_sheets/s3\_pin.zip</a>.

## **Pinout Table**

| Bank | XC3S50, XC3S200,<br>XC3S400 Pin Name | TQ144 Pin<br>Number | Туре |

|------|--------------------------------------|---------------------|------|

| 0    | IO_L01N_0/VRP_0                      | P141                | DCI  |

| 0    | IO_L01P_0/VRN_0                      | P140                | DCI  |

| 0    | IO_L27N_0                            | P137                | I/O  |

| 0    | IO_L27P_0                            | P135                | I/O  |

| 0    | IO_L30N_0                            | P132                | I/O  |

| 0    | IO_L30P_0                            | P131                | I/O  |

| 0    | IO_L31N_0                            | P130                | I/O  |

| 0    | IO_L31P_0/VREF_0                     | P129                | VREF |

| 0    | IO_L32N_0/GCLK7                      | P128                | GCLK |

| 0    | IO_L32P_0/GCLK6                      | P127                | GCLK |

| 1    | Ю                                    | P116                | I/O  |

| 1    | IO_L01N_1/VRP_1                      | P113                | DCI  |

| 1    | IO_L01P_1/VRN_1                      | P112                | DCI  |

| 1    | IO_L28N_1                            | P119                | I/O  |

| 1    | IO_L28P_1                            | P118                | I/O  |

| 1    | IO_L31N_1/VREF_1                     | P123                | VREF |

| 1    | IO_L31P_1                            | P122                | I/O  |

| 1    | IO_L32N_1/GCLK5                      | P125                | GCLK |

| 1    | IO_L32P_1/GCLK4                      | P124                | GCLK |

| 2    | IO_L01N_2/VRP_2                      | P108                | DCI  |

| 2    | IO_L01P_2/VRN_2                      | P107                | DCI  |

| 2    | IO_L20N_2                            | P105                | I/O  |

| 2    | IO_L20P_2                            | P104                | I/O  |

| 2    | IO_L21N_2                            | P103                | I/O  |

| 2    | IO_L21P_2                            | P102                | I/O  |

| 2    | IO_L22N_2                            | P100                | I/O  |

| 2    | IO_L22P_2                            | P99                 | I/O  |

Table 91: TQ144 Package Pinout

# FG320: 320-lead Fine-pitch Ball Grid Array

The 320-lead fine-pitch ball grid array package, FG320, supports three different Spartan-3 devices, including the XC3S400, the XC3S1000, and the XC3S1500. The footprint for all three devices is identical, as shown in Table 98 and Figure 50.

The FG320 package is an 18 x 18 array of solder balls minus the four center balls.

All the package pins appear in Table 98 and are sorted by bank number, then by pin name. Pairs of pins that form a differential I/O pair appear together in the table. The table also shows the pin number for each pin and the pin type, as defined earlier.

An electronic version of this package pinout table and footprint diagram is available for download from the Xilinx website at <a href="http://www.xilinx.com/support/documentation/data\_sheets/s3\_pin.zip">http://www.xilinx.com/support/documentation/data\_sheets/s3\_pin.zip</a>.

## **Pinout Table**

Table 98: FG320 Package Pinout

| Bank | XC3S400, XC3S1000, XC3S1500<br>Pin Name | FG320<br>Pin Number | Туре |

|------|-----------------------------------------|---------------------|------|

| 0    | IO                                      | D9                  | I/O  |

| 0    | IO                                      | E7                  | I/O  |

| 0    | IO/VREF_0                               | B3                  | VREF |

| 0    | IO/VREF_0                               | D6                  | VREF |

| 0    | IO_L01N_0/VRP_0                         | A2                  | DCI  |

| 0    | IO_L01P_0/VRN_0                         | A3                  | DCI  |

| 0    | IO_L09N_0                               | B4                  | I/O  |

| 0    | IO_L09P_0                               | C4                  | I/O  |

| 0    | IO_L10N_0                               | C5                  | I/O  |

| 0    | IO_L10P_0                               | D5                  | I/O  |

| 0    | IO_L15N_0                               | A4                  | I/O  |

| 0    | IO_L15P_0                               | A5                  | I/O  |

| 0    | IO_L25N_0                               | B5                  | I/O  |

| 0    | IO_L25P_0                               | B6                  | I/O  |

| 0    | IO_L27N_0                               | C7                  | I/O  |

| 0    | IO_L27P_0                               | D7                  | I/O  |

| 0    | IO_L28N_0                               | C8                  | I/O  |

| 0    | IO_L28P_0                               | D8                  | I/O  |

| 0    | IO_L29N_0                               | E8                  | I/O  |

| 0    | IO_L29P_0                               | F8                  | I/O  |

| 0    | IO_L30N_0                               | A7                  | I/O  |

| 0    | IO_L30P_0                               | A8                  | I/O  |

| 0    | IO_L31N_0                               | B9                  | I/O  |

| 0    | IO_L31P_0/VREF_0                        | A9                  | VREF |

| 0    | IO_L32N_0/GCLK7                         | E9                  | GCLK |

| 0    | IO_L32P_0/GCLK6                         | F9                  | GCLK |

| 0    | VCCO_0                                  | B8                  | VCCO |

| 0    | VCCO_0                                  | C6                  | VCCO |

| 0    | VCCO_0                                  | G8                  | VCCO |

| Bank | XC3S1000<br>Pin Name | XC3S1500<br>Pin Name | XC3S2000<br>Pin Name | XC3S4000<br>Pin Name | XC3S5000<br>Pin Name | FG676 Pin<br>Number | Туре |

|------|----------------------|----------------------|----------------------|----------------------|----------------------|---------------------|------|

| N/A  | GND                  | GND                  | GND                  | GND                  | GND                  | D15                 | GND  |

| N/A  | GND                  | GND                  | GND                  | GND                  | GND                  | D23                 | GND  |

| N/A  | GND                  | GND                  | GND                  | GND                  | GND                  | K11                 | GND  |

| N/A  | GND                  | GND                  | GND                  | GND                  | GND                  | K12                 | GND  |

| N/A  | GND                  | GND                  | GND                  | GND                  | GND                  | K15                 | GND  |

| N/A  | GND                  | GND                  | GND                  | GND                  | GND                  | K16                 | GND  |

| N/A  | GND                  | GND                  | GND                  | GND                  | GND                  | L10                 | GND  |

| N/A  | GND                  | GND                  | GND                  | GND                  | GND                  | L11                 | GND  |

| N/A  | GND                  | GND                  | GND                  | GND                  | GND                  | L12                 | GND  |

| N/A  | GND                  | GND                  | GND                  | GND                  | GND                  | L13                 | GND  |

| N/A  | GND                  | GND                  | GND                  | GND                  | GND                  | L14                 | GND  |

| N/A  | GND                  | GND                  | GND                  | GND                  | GND                  | L15                 | GND  |

| N/A  | GND                  | GND                  | GND                  | GND                  | GND                  | L16                 | GND  |

| N/A  | GND                  | GND                  | GND                  | GND                  | GND                  | L17                 | GND  |

| N/A  | GND                  | GND                  | GND                  | GND                  | GND                  | M4                  | GND  |

| N/A  | GND                  | GND                  | GND                  | GND                  | GND                  | M10                 | GND  |

| N/A  | GND                  | GND                  | GND                  | GND                  | GND                  | M11                 | GND  |

| N/A  | GND                  | GND                  | GND                  | GND                  | GND                  | M12                 | GND  |

| N/A  | GND                  | GND                  | GND                  | GND                  | GND                  | M13                 | GND  |

| N/A  | GND                  | GND                  | GND                  | GND                  | GND                  | M14                 | GND  |

| N/A  | GND                  | GND                  | GND                  | GND                  | GND                  | M15                 | GND  |

| N/A  | GND                  | GND                  | GND                  | GND                  | GND                  | M16                 | GND  |

| N/A  | GND                  | GND                  | GND                  | GND                  | GND                  | M17                 | GND  |

| N/A  | GND                  | GND                  | GND                  | GND                  | GND                  | M23                 | GND  |

| N/A  | GND                  | GND                  | GND                  | GND                  | GND                  | N11                 | GND  |

| N/A  | GND                  | GND                  | GND                  | GND                  | GND                  | N12                 | GND  |

| N/A  | GND                  | GND                  | GND                  | GND                  | GND                  | N13                 | GND  |

| N/A  | GND                  | GND                  | GND                  | GND                  | GND                  | N14                 | GND  |

| N/A  | GND                  | GND                  | GND                  | GND                  | GND                  | N15                 | GND  |

| N/A  | GND                  | GND                  | GND                  | GND                  | GND                  | N16                 | GND  |

| N/A  | GND                  | GND                  | GND                  | GND                  | GND                  | P11                 | GND  |

| N/A  | GND                  | GND                  | GND                  | GND                  | GND                  | P12                 | GND  |

| N/A  | GND                  | GND                  | GND                  | GND                  | GND                  | P13                 | GND  |

| N/A  | GND                  | GND                  | GND                  | GND                  | GND                  | P14                 | GND  |

| N/A  | GND                  | GND                  | GND                  | GND                  | GND                  | P15                 | GND  |

| N/A  | GND                  | GND                  | GND                  | GND                  | GND                  | P16                 | GND  |

| N/A  | GND                  | GND                  | GND                  | GND                  | GND                  | R4                  | GND  |

| N/A  | GND                  | GND                  | GND                  | GND                  | GND                  | R10                 | GND  |

| N/A  | GND                  | GND                  | GND                  | GND                  | GND                  | R11                 | GND  |

| N/A  | GND                  | GND                  | GND                  | GND                  | GND                  | R12                 | GND  |

| N/A  | GND                  | GND                  | GND                  | GND                  | GND                  | R13                 | GND  |

| N/A  | GND                  | GND                  | GND                  | GND                  | GND                  | R14                 | GND  |

| N/A  | GND                  | GND                  | GND                  | GND                  | GND                  | R15                 | GND  |

## Table 107: FG900 Package Pinout (Cont'd)

| Bank | XC3S2000<br>Pin Name | XC3S4000, XC3S5000<br>Pin Name | FG900 Pin<br>Number | Туре |

|------|----------------------|--------------------------------|---------------------|------|

| 4    | IO_L11P_4            | IO_L11P_4                      | AE21                | I/O  |

| 4    | IO_L12N_4            | IO_L12N_4                      | AH21                | I/O  |

| 4    | IO_L12P_4            | IO_L12P_4                      | AJ21                | I/O  |

| 4    | IO_L13N_4            | IO_L13N_4                      | AB21                | I/O  |

| 4    | IO_L13P_4            | IO_L13P_4                      | AA20                | I/O  |

| 4    | IO_L14N_4            | IO_L14N_4                      | AC20                | I/O  |

| 4    | IO_L14P_4            | IO_L14P_4                      | AD20                | I/O  |

| 4    | IO_L15N_4            | IO_L15N_4                      | AE20                | I/O  |

| 4    | IO_L15P_4            | IO_L15P_4                      | AF20                | I/O  |

| 4    | IO_L16N_4            | IO_L16N_4                      | AG20                | I/O  |

| 4    | IO_L16P_4            | IO_L16P_4                      | AH20                | I/O  |

| 4    | IO_L17N_4            | IO_L17N_4                      | AJ20                | I/O  |

| 4    | IO_L17P_4            | IO_L17P_4                      | AK20                | I/O  |

| 4    | IO_L18N_4            | IO_L18N_4                      | AA19                | I/O  |

| 4    | IO_L18P_4            | IO_L18P_4                      | AB19                | I/O  |

| 4    | IO_L19N_4            | IO_L19N_4                      | AC19                | I/O  |

| 4    | IO_L19P_4            | IO_L19P_4                      | AD19                | I/O  |

| 4    | IO_L20N_4            | IO_L20N_4                      | AE19                | I/O  |

| 4    | IO_L20P_4            | IO_L20P_4                      | AF19                | I/O  |

| 4    | IO_L21N_4            | IO_L21N_4                      | AG19                | I/O  |

| 4    | IO_L21P_4            | IO_L21P_4                      | AH19                | I/O  |

| 4    | IO_L22N_4/VREF_4     | IO_L22N_4/VREF_4               | AJ19                | VREF |

| 4    | IO_L22P_4            | IO_L22P_4                      | AK19                | I/O  |

| 4    | IO_L23N_4            | IO_L23N_4                      | AB18                | I/O  |

| 4    | IO_L23P_4            | IO_L23P_4                      | AC18                | I/O  |

| 4    | IO_L24N_4            | IO_L24N_4                      | AE18                | I/O  |

| 4    | IO_L24P_4            | IO_L24P_4                      | AF18                | I/O  |

| 4    | IO_L25N_4            | IO_L25N_4                      | AJ18                | I/O  |

| 4    | IO_L25P_4            | IO_L25P_4                      | AK18                | I/O  |

| 4    | IO_L26N_4            | IO_L26N_4                      | AA17                | I/O  |

| 4    | IO_L26P_4/VREF_4     | IO_L26P_4/VREF_4               | AB17                | VREF |

| 4    | IO_L27N_4/DIN/D0     | IO_L27N_4/DIN/D0               | AD17                | DUAL |

| 4    | IO_L27P_4/D1         | IO_L27P_4/D1                   | AE17                | DUAL |

| 4    | IO_L28N_4            | IO_L28N_4                      | AH17                | I/O  |

| 4    | IO_L28P_4            | IO_L28P_4                      | AJ17                | I/O  |

| 4    | IO_L29N_4            | IO_L29N_4                      | AB16                | I/O  |

| 4    | IO_L29P_4            | IO_L29P_4                      | AC16                | I/O  |

| 4    | IO_L30N_4/D2         | IO_L30N_4/D2                   | AD16                | DUAL |

| 4    | IO_L30P_4/D3         | IO_L30P_4/D3                   | AE16                | DUAL |

| 4    | IO_L31N_4/INIT_B     | IO_L31N_4/INIT_B               | AG16                | DUAL |

| Bank | XC3S4000<br>Pin Name | XC3S5000<br>Pin Name | FG1156<br>Pin Number | Туре |

|------|----------------------|----------------------|----------------------|------|

| 1    | VCCO_1               | VCCO_1               | M22                  | VCCO |

| 2    | IO                   | IO                   | G33                  | I/O  |

| 2    | IO                   | IO                   | G34                  | I/O  |

| 2    | IO                   | IO                   | U25                  | I/O  |

| 2    | IO                   | IO                   | U26                  | I/O  |

| 2    | IO_L01N_2/VRP_2      | IO_L01N_2/VRP_2      | C33                  | DCI  |

| 2    | IO_L01P_2/VRN_2      | IO_L01P_2/VRN_2      | C34                  | DCI  |

| 2    | IO_L02N_2            | IO_L02N_2            | D33                  | I/O  |

| 2    | IO_L02P_2            | IO_L02P_2            | D34                  | I/O  |

| 2    | IO_L03N_2/VREF_2     | IO_L03N_2/VREF_2     | E32                  | VREF |

| 2    | IO_L03P_2            | IO_L03P_2            | E33                  | I/O  |

| 2    | IO_L04N_2            | IO_L04N_2            | F31                  | I/O  |

| 2    | IO_L04P_2            | IO_L04P_2            | F32                  | I/O  |

| 2    | IO_L05N_2            | IO_L05N_2            | G29                  | I/O  |

| 2    | IO_L05P_2            | IO_L05P_2            | G30                  | I/O  |

| 2    | IO_L06N_2            | IO_L06N_2            | H29                  | I/O  |

| 2    | IO_L06P_2            | IO_L06P_2            | H30                  | I/O  |

| 2    | IO_L07N_2            | IO_L07N_2            | H33                  | I/O  |

| 2    | IO_L07P_2            | IO_L07P_2            | H34                  | I/O  |

| 2    | IO_L08N_2            | IO_L08N_2            | J28                  | I/O  |

| 2    | IO_L08P_2            | IO_L08P_2            | J29                  | I/O  |

| 2    | IO_L09N_2/VREF_2     | IO_L09N_2/VREF_2     | H31                  | VREF |

| 2    | IO_L09P_2            | IO_L09P_2            | J31                  | I/O  |

| 2    | IO_L10N_2            | IO_L10N_2            | J32                  | I/O  |

| 2    | IO_L10P_2            | IO_L10P_2            | J33                  | I/O  |

| 2    | IO_L11N_2            | IO_L11N_2            | J27                  | I/O  |

| 2    | IO_L11P_2            | IO_L11P_2            | K26                  | I/O  |

| 2    | IO_L12N_2            | IO_L12N_2            | K27                  | I/O  |