#### AMD Xilinx - XC3S400-4PQG208I Datasheet

Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                              |

|--------------------------------|--------------------------------------------------------------|

| Product Status                 | Obsolete                                                     |

| Number of LABs/CLBs            | 896                                                          |

| Number of Logic Elements/Cells | 8064                                                         |

| Total RAM Bits                 | 294912                                                       |

| Number of I/O                  | 141                                                          |

| Number of Gates                | 400000                                                       |

| Voltage - Supply               | 1.14V ~ 1.26V                                                |

| Mounting Type                  | Surface Mount                                                |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                           |

| Package / Case                 | 208-BFQFP                                                    |

| Supplier Device Package        | 208-PQFP (28x28)                                             |

| Purchase URL                   | https://www.e-xfl.com/product-detail/xilinx/xc3s400-4pqg208i |

|                                |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

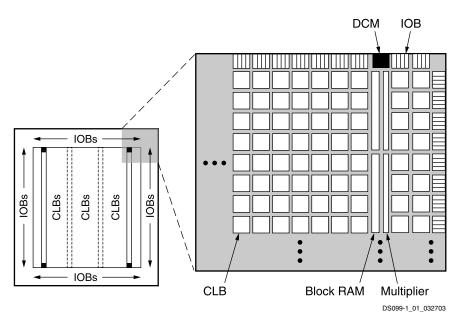

# Architectural Overview

The Spartan-3 family architecture consists of five fundamental programmable functional elements:

- Configurable Logic Blocks (CLBs) contain RAM-based Look-Up Tables (LUTs) to implement logic and storage elements that can be used as flip-flops or latches. CLBs can be programmed to perform a wide variety of logical functions as well as to store data.

- Input/Output Blocks (IOBs) control the flow of data between the I/O pins and the internal logic of the device. Each IOB supports bidirectional data flow plus 3-state operation. Twenty-six different signal standards, including eight high-performance differential standards, are available as shown in Table 2. Double Data-Rate (DDR) registers are included. The Digitally Controlled Impedance (DCI) feature provides automatic on-chip terminations, simplifying board designs.

- Block RAM provides data storage in the form of 18-Kbit dual-port blocks.

- Multiplier blocks accept two 18-bit binary numbers as inputs and calculate the product.

- Digital Clock Manager (DCM) blocks provide self-calibrating, fully digital solutions for distributing, delaying, multiplying, dividing, and phase shifting clock signals.

These elements are organized as shown in Figure 1. A ring of IOBs surrounds a regular array of CLBs. The XC3S50 has a single column of block RAM embedded in the array. Those devices ranging from the XC3S200 to the XC3S2000 have two columns of block RAM. The XC3S4000 and XC3S5000 devices have four RAM columns. Each column is made up of several 18-Kbit RAM blocks; each block is associated with a dedicated multiplier. The DCMs are positioned at the ends of the outer block RAM columns.

The Spartan-3 family features a rich network of traces and switches that interconnect all five functional elements, transmitting signals among them. Each functional element has an associated switch matrix that permits multiple connections to the routing.

#### Notes:

1. The two additional block RAM columns of the XC3S4000 and XC3S5000 devices are shown with dashed lines. The XC3S50 has only the block RAM column on the far left.

Figure 1: Spartan-3 Family Architecture

# Configuration

Spartan-3 FPGAs are programmed by loading configuration data into robust reprogrammable static CMOS configuration latches (CCLs) that collectively control all functional elements and routing resources. Before powering on the FPGA, configuration data is stored externally in a PROM or some other nonvolatile medium either on or off the board. After applying

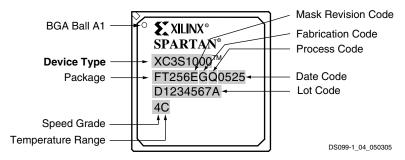

Figure 3: Spartan-3 FPGA BGA Package Marking Example for Part Number XC3S1000-4FT256C

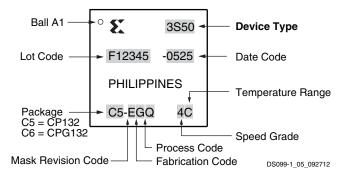

Figure 4: Spartan-3 FPGA CP132 and CPG132 Package Marking Example for XC3S50-4CP132C

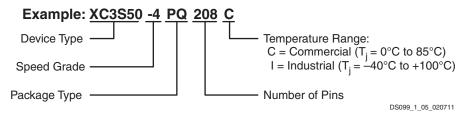

### **Ordering Information**

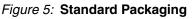

Spartan-3 FPGAs are available in both standard (Figure 5) and Pb-free (Figure 6) packaging options for all device/package combinations. The Pb-free packages include a special 'G' character in the ordering code.

For additional information on Pb-free packaging, see <u>XAPP427</u>: Implementation and Solder Reflow Guidelines for Pb-Free Packages.

DS099\_1\_06\_020711

Figure 6: Pb-Free Packaging

# Notice of Disclaimer

THE XILINX HARDWARE FPGA AND CPLD DEVICES REFERRED TO HEREIN ("PRODUCTS") ARE SUBJECT TO THE TERMS AND CONDITIONS OF THE XILINX LIMITED WARRANTY WHICH CAN BE VIEWED AT <a href="http://www.xilinx.com/warranty.htm">http://www.xilinx.com/warranty.htm</a>. THIS LIMITED WARRANTY DOES NOT EXTEND TO ANY USE OF PRODUCTS IN AN APPLICATION OR ENVIRONMENT THAT IS NOT WITHIN THE SPECIFICATIONS STATED IN THE XILINX DATA SHEET. ALL SPECIFICATIONS ARE SUBJECT TO CHANGE WITHOUT NOTICE. PRODUCTS ARE NOT DESIGNED OR INTENDED TO BE FAIL-SAFE OR FOR USE IN ANY APPLICATION REQUIRING FAIL-SAFE PERFORMANCE, SUCH AS LIFE-SUPPORT OR SAFETY DEVICES OR SYSTEMS, OR ANY OTHER APPLICATION THAT INVOKES THE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). USE OF PRODUCTS IN CRITICAL APPLICATIONS IS AT THE SOLE RISK OF CUSTOMER, SUBJECT TO APPLICABLE LAWS AND REGULATIONS.

#### CRITICAL APPLICATIONS DISCLAIMER

XILINX PRODUCTS (INCLUDING HARDWARE, SOFTWARE AND/OR IP CORES) ARE NOT DESIGNED OR INTENDED TO BE FAIL-SAFE, OR FOR USE IN ANY APPLICATION REQUIRING FAIL-SAFE PERFORMANCE, SUCH AS IN LIFE-SUPPORT OR SAFETY DEVICES OR SYSTEMS, CLASS III MEDICAL DEVICES, NUCLEAR FACILITIES, APPLICATIONS RELATED TO THE DEPLOYMENT OF AIRBAGS, OR ANY OTHER APPLICATIONS THAT COULD LEAD TO DEATH, PERSONAL INJURY OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE (INDIVIDUALLY AND COLLECTIVELY, "CRITICAL APPLICATIONS"). FURTHERMORE, XILINX PRODUCTS ARE NOT DESIGNED OR INTENDED FOR USE IN ANY APPLICATIONS THAT AFFECT CONTROL OF A VEHICLE OR AIRCRAFT, UNLESS THERE IS A FAIL-SAFE OR REDUNDANCY FEATURE (WHICH DOES NOT INCLUDE USE OF SOFTWARE IN THE XILINX DEVICE TO IMPLEMENT THE REDUNDANCY) AND A WARNING SIGNAL UPON FAILURE TO THE OPERATOR. CUSTOMER AGREES, PRIOR TO USING OR DISTRIBUTING ANY SYSTEMS THAT INCORPORATE XILINX PRODUCTS, TO THOROUGHLY TEST THE SAME FOR SAFETY PURPOSES. TO THE MAXIMUM EXTENT PERMITTED BY APPLICABLE LAW, CUSTOMER ASSUMES THE SOLE RISK AND LIABILITY OF ANY USE OF XILINX PRODUCTS IN CRITICAL APPLICATIONS.

#### AUTOMOTIVE APPLICATIONS DISCLAIMER

XILINX PRODUCTS ARE NOT DESIGNED OR INTENDED TO BE FAIL-SAFE, OR FOR USE IN ANY APPLICATION REQUIRING FAIL-SAFE PERFORMANCE, SUCH AS APPLICATIONS RELATED TO: (I) THE DEPLOYMENT OF AIRBAGS, (II) CONTROL OF A VEHICLE, UNLESS THERE IS A FAIL-SAFE OR REDUNDANCY FEATURE (WHICH DOES NOT INCLUDE USE OF SOFTWARE IN THE XILINX DEVICE TO IMPLEMENT THE REDUNDANCY) AND A WARNING SIGNAL UPON FAILURE TO THE OPERATOR, OR (III) USES THAT COULD LEAD TO DEATH OR PERSONAL INJURY. CUSTOMER ASSUMES THE SOLE RISK AND LIABILITY OF ANY USE OF XILINX PRODUCTS IN SUCH APPLICATIONS.

#### Table 10: DCI I/O Standards

| Category of Signal              | Signal Standard                       | V <sub>CCC</sub> | <sub>0</sub> (V) | V <sub>REF</sub> for | Termination Type             |               |  |

|---------------------------------|---------------------------------------|------------------|------------------|----------------------|------------------------------|---------------|--|

| Standard                        | (IOSTANDARD)                          | For Outputs      | For Inputs       | Inputs (V)           | At Output                    | At Input      |  |

| Single-Ended                    |                                       |                  | ·                | ·                    |                              |               |  |

| Gunning                         | GTL_DCI                               | 1.2              | 1.2              | 0.8                  | Cincle                       | Circele       |  |

| Transceiver Logic               | GTLP_DCI                              | 1.5              | 1.5              | 1.0                  | Single                       | Single        |  |

| High-Speed                      | HSTL_I_DCI                            | 1.5              | 1.5              | 0.75                 | None                         | Split         |  |

| Transceiver Logic               | HSTL_III_DCI                          | 1.5              | 1.5              | 0.9                  | None                         | Single        |  |

|                                 | HSTL_I_DCI_18                         | 1.8              | 1.8              | 0.9                  | None                         |               |  |

|                                 | HSTL_II_DCI_18<br>DIFF_HSTL_II_18_DCI | 1.8              | 1.8              | 0.9                  | Split                        | Split         |  |

|                                 | HSTL_III_DCI_18                       | 1.8              | 1.8              | 1.1                  | None                         | Single        |  |

| Low-Voltage CMOS                | LVDCI_15                              | 1.5              | 1.5              | -                    |                              |               |  |

|                                 | LVDCI_18                              | 1.8              | 1.8              | -                    | Controlled                   |               |  |

|                                 | LVDCI_25                              | 2.5              | 2.5              | _                    | impedance driver             | None          |  |

|                                 | LVDCI_33 <sup>(2)</sup>               | 3.3              | 3.3              | -                    | 1                            |               |  |

|                                 | LVDCI_DV2_15                          | 1.5              | 1.5              | -                    |                              |               |  |

|                                 | LVDCI_DV2_18                          | 1.8              | 1.8              | -                    | Controlled driver<br>with    |               |  |

|                                 | LVDCI_DV2_25                          | 2.5              | 2.5              | -                    | half-impedance               |               |  |

|                                 | LVDCI_DV2_33                          | 3.3              | 3.3              | _                    | 1                            |               |  |

| Hybrid HSTL Input               | HSLVDCI_15                            | 1.5              | 1.5              | 0.75                 |                              |               |  |

| and LVCMOS Output               | HSLVDCI_18                            | 1.8              | 1.8              | 0.9                  | Controlled                   | Nama          |  |

|                                 | HSLVDCI_25                            | 2.5              | 2.5              | 1.25                 | impedance driver             | None          |  |

|                                 | HSLVDCI_33                            | 3.3              | 3.3              | 1.65                 |                              |               |  |

| Stub Series                     | SSTL18_I_DCI                          | 1.8              | 1.8              | 0.9                  | $25\Omega$ driver            |               |  |

| Terminated Logic <sup>(3)</sup> | SSTL2_I_DCI                           | 2.5              | 2.5              | 1.25                 | $25\Omega$ driver            | Split         |  |

|                                 | SSTL2_II_DCI<br>DIFF_SSTL2_II_DCI     | 2.5              | 2.5              | 1.25                 | Split with $25\Omega$ driver | -p            |  |

| Differential                    |                                       |                  |                  |                      |                              |               |  |

| Low-Voltage                     | LVDS_25_DCI                           | N/A              | 2.5              | -                    | None                         | Split on each |  |

| Differential Signaling          | LVDSEXT_25_DCI                        | N/A              | 2.5              | -                    | None                         | line of pair  |  |

#### Notes:

1. DCI signal standards are not supported in Bank 5 of any Spartan-3 FPGA packaged in a VQ100, CP132, or TQ144 package.

2. Equivalent to LVTTL DCI.

3. The SSTL18\_II signal standard does not have a DCI equivalent.

### Supply Voltages for the IOBs

Three different supplies power the IOBs:

- The V<sub>CCO</sub> supplies, one for each of the FPGA's I/O banks, power the output drivers, except when using the GTL and GTLP signal standards. The voltage on the V<sub>CCO</sub> pins determines the voltage swing of the output signal.

- V<sub>CCINT</sub> is the main power supply for the FPGA's internal logic.

- The V<sub>CCAUX</sub> is an auxiliary source of power, primarily to optimize the performance of various FPGA functions such as I/O switching.

# The I/Os During Power-On, Configuration, and User Mode

With no power applied to the FPGA, all I/Os are in a high-impedance state. The  $V_{CCINT}$  (1.2V),  $V_{CCAUX}$  (2.5V), and  $V_{CCO}$  supplies may be applied in any order. Before power-on can finish,  $V_{CCINT}$ ,  $V_{CCO}$  Bank 4, and  $V_{CCAUX}$  must have reached their respective minimum recommended operating levels (see Table 29, page 59). At this time, all I/O drivers also will be in a high-impedance state.  $V_{CCO}$  Bank 4,  $V_{CCINT}$ , and  $V_{CCAUX}$  serve as inputs to the internal Power-On Reset circuit (POR).

A Low level applied to the HSWAP\_EN input enables pull-up resistors on User I/Os from power-on throughout configuration. A High level on HSWAP\_EN disables the pull-up resistors, allowing the I/Os to float. If the HSWAP\_EN pin is floating, then an internal pull-up resistor pulls HSWAP\_EN High. As soon as power is applied, the FPGA begins initializing its configuration memory. At the same time, the FPGA internally asserts the Global Set-Reset (GSR), which asynchronously resets all IOB storage elements to a Low state.

Upon the completion of initialization, INIT\_B goes High, sampling the M0, M1, and M2 inputs to determine the configuration mode. At this point, the configuration data is loaded into the FPGA. The I/O drivers remain in a high-impedance state (with or without pull-up resistors, as determined by the HSWAP\_EN input) throughout configuration.

The Global Three State (GTS) net is released during Start-Up, marking the end of configuration and the beginning of design operation in the User mode. At this point, those I/Os to which signals have been assigned go active while all unused I/Os remain in a high-impedance state. The release of the GSR net, also part of Start-up, leaves the IOB registers in a Low state by default, unless the loaded design reverses the polarity of their respective RS inputs.

In User mode, all internal pull-up resistors on the I/Os are disabled and HSWAP\_EN becomes a "don't care" input. If it is desirable to have pull-up or pull-down resistors on I/Os carrying signals, the appropriate symbol—e.g., PULLUP, PULLDOWN—must be placed at the appropriate pads in the design. The Bitstream Generator (Bitgen) option UnusedPin available in the Xilinx development software determines whether unused I/Os collectively have pull-up resistors, pull-down resistors, or no resistors in User mode.

# **CLB** Overview

For more details on the CLBs, refer to the chapter entitled "Using Configurable Logic Blocks" in UG331.

The Configurable Logic Blocks (CLBs) constitute the main logic resource for implementing synchronous as well as combinatorial circuits. Each CLB comprises four interconnected slices, as shown in Figure 11. These slices are grouped in pairs. Each pair is organized as a column with an independent carry chain.

The nomenclature that the FPGA Editor—part of the Xilinx development software—uses to designate slices is as follows: The letter 'X' followed by a number identifies columns of slices. The 'X' number counts up in sequence from the left side of the die to the right. The letter 'Y' followed by a number identifies the position of each slice in a pair as well as indicating the CLB row. The 'Y' number counts slices starting from the bottom of the die according to the sequence: 0, 1, 0, 1 (the first CLB row); 2, 3, 2, 3 (the second CLB row); etc. Figure 11 shows the CLB located in the lower left-hand corner of the die. Slices X0Y0 and X0Y1 make up the column-pair on the left where as slices X1Y0 and X1Y1 make up the column-pair on the right. For each CLB, the term "left-hand" (or SLICEM) indicates the pair of slices labeled with an even 'X' number, such as X0, and the term "right-hand" (or SLICEL) designates the pair of slices with an odd 'X' number, e.g., X1.

#### Table 34: Quiescent Supply Current Characteristics

| Symbol              | Description                                 | Device   | Typical <sup>(1)</sup> | Commercial<br>Maximum <sup>(1)</sup> | Industrial<br>Maximum <sup>(1)</sup> | Units |

|---------------------|---------------------------------------------|----------|------------------------|--------------------------------------|--------------------------------------|-------|

| I <sub>CCINTQ</sub> | Quiescent $V_{CCINT}$ supply current        | XC3S50   | 5                      | 24                                   | 31                                   | mA    |

|                     |                                             | XC3S200  | 10                     | 54                                   | 80                                   | mA    |

|                     |                                             | XC3S400  | 15                     | 110                                  | 157                                  | mA    |

|                     |                                             | XC3S1000 | 35                     | 160                                  | 262                                  | mA    |

|                     |                                             | XC3S1500 | 45                     | 260                                  | 332                                  | mA    |

|                     |                                             | XC3S2000 | 60                     | 360                                  | 470                                  | mA    |

|                     |                                             | XC3S4000 | 100                    | 450                                  | 810                                  | mA    |

|                     |                                             | XC3S5000 | 120                    | 600                                  | 870                                  | mA    |

| Iccoq               | Quiescent V <sub>CCO</sub> supply current   | XC3S50   | 1.5                    | 2.0                                  | 2.5                                  | mA    |

|                     |                                             | XC3S200  | 1.5                    | 3.0                                  | 3.5                                  | mA    |

|                     |                                             | XC3S400  | 1.5                    | 3.0                                  | 3.5                                  | mA    |

|                     |                                             | XC3S1000 | 2.0                    | 4.0                                  | 5.0                                  | mA    |

|                     |                                             | XC3S1500 | 2.5                    | 4.0                                  | 5.0                                  | mA    |

|                     |                                             | XC3S2000 | 3.0                    | 5.0                                  | 6.0                                  | mA    |

|                     |                                             | XC3S4000 | 3.5                    | 5.0                                  | 6.0                                  | mA    |

|                     |                                             | XC3S5000 | 3.5                    | 5.0                                  | 6.0                                  | mA    |

| I <sub>CCAUXQ</sub> | Quiescent V <sub>CCAUX</sub> supply current | XC3S50   | 7                      | 20                                   | 22                                   | mA    |

|                     |                                             | XC3S200  | 10                     | 30                                   | 33                                   | mA    |

|                     |                                             | XC3S400  | 15                     | 40                                   | 44                                   | mA    |

|                     |                                             | XC3S1000 | 20                     | 50                                   | 55                                   | mA    |

|                     |                                             | XC3S1500 | 35                     | 75                                   | 85                                   | mA    |

|                     |                                             | XC3S2000 | 45                     | 90                                   | 100                                  | mA    |

|                     |                                             | XC3S4000 | 55                     | 110                                  | 125                                  | mA    |

|                     |                                             | XC3S5000 | 70                     | 130                                  | 145                                  | mA    |

#### Notes:

- 1. The numbers in this table are based on the conditions set forth in Table 32. Quiescent supply current is measured with all I/O drivers in a high-impedance state and with all pull-up/pull-down resistors at the I/O pads disabled. Typical values are characterized using devices with typical processing at room temperature (T<sub>J</sub> of 25°C at V<sub>CCINT</sub> = 1.2V, V<sub>CCO</sub> = 3.3V, and V<sub>CCAUX</sub> = 2.5V). Maximum values are the production test limits measured for each device at the maximum specified junction temperature and at maximum voltage limits with V<sub>CCINT</sub> = 1.26V, V<sub>CCO</sub> = 3.465V, and V<sub>CCAUX</sub> = 2.625V. The FPGA is programmed with a "blank" configuration data file (i.e., a design with no functional elements instantiated). For conditions other than those described above, (e.g., a design including functional elements, the use of DCI standards, etc.), measured quiescent current levels may be different than the values in the table. Use the XPower Estimator or XPower Analyzer for more accurate estimates. See Note 2.

- 2. There are two recommended ways to estimate the total power consumption (quiescent plus dynamic) for a specific design: a) The <u>Spartan-3</u> <u>XPower Estimator</u> provides quick, approximate, typical estimates, and does not require a netlist of the design. b) XPower Analyzer, part of the Xilinx ISE development software, uses the FPGA netlist as input to provide more accurate maximum and typical estimates.

- The maximum numbers in this table also indicate the minimum current each power rail requires in order for the FPGA to power-on successfully, once all three rails are supplied. If V<sub>CCINT</sub> is applied before V<sub>CCAUX</sub>, there may be temporary additional I<sub>CCINT</sub> current until V<sub>CCAUX</sub> is applied. See Surplus I<sub>CCINT</sub> if V<sub>CCINT</sub> Applied before V<sub>CCAUX</sub>, page 54

### Table 36: DC Characteristics of User I/Os Using Single-Ended Standards

| Signal Star                                      | ndard | Test Co                 | nditions                | Logic Level Characteristics |                            |  |

|--------------------------------------------------|-------|-------------------------|-------------------------|-----------------------------|----------------------------|--|

| (IOSTANDARD) and Current<br>Drive Attribute (mA) |       | l <sub>OL</sub><br>(mA) | I <sub>ОН</sub><br>(mA) | V <sub>OL</sub><br>Max (V)  | V <sub>OH</sub><br>Min (V) |  |

| GTL                                              |       | 32                      | -                       | 0.4                         | -                          |  |

| GTL_DCI                                          |       | Note 3                  | Note 3                  |                             |                            |  |

| GTLP                                             |       | 36                      | -                       | 0.6                         | -                          |  |

| GTLP_DCI                                         |       | Note 3                  | Note 3                  |                             |                            |  |

| HSLVDCI_15                                       |       | Note 3                  | Note 3                  | 0.4                         | V <sub>CCO</sub> – 0.4     |  |

| HSLVDCI_18                                       |       |                         |                         |                             |                            |  |

| HSLVDCI_25                                       |       |                         |                         |                             |                            |  |

| HSLVDCI_33                                       |       |                         |                         |                             |                            |  |

| HSTL_I                                           |       | 8                       | -8                      | 0.4                         | V <sub>CCO</sub> – 0.4     |  |

| HSTL_I_DCI                                       |       | Note 3                  | Note 3                  |                             |                            |  |

| HSTL_III                                         |       | 24                      | -8                      | 0.4                         | V <sub>CCO</sub> - 0.4     |  |

| HSTL_III_DCI                                     |       | Note 3                  | Note 3                  | 1                           |                            |  |

| HSTL_I_18                                        |       | 8                       | -8                      | 0.4                         | V <sub>CCO</sub> - 0.4     |  |

| HSTL_I_DCI_18                                    |       | Note 3                  | Note 3                  |                             |                            |  |

| HSTL_II_18                                       |       | 16                      | -16                     | 0.4                         | V <sub>CCO</sub> - 0.4     |  |

| HSTL_II_DCI_18                                   |       | Note 3                  | Note 3                  | -                           |                            |  |

| HSTL_III_18                                      |       | 24                      | -8                      | 0.4                         | V <sub>CCO</sub> - 0.4     |  |

| HSTL_III_DCI_18                                  |       | Note 3                  | Note 3                  | -                           |                            |  |

| LVCMOS12 <sup>(4)</sup>                          | 2     | 2                       | -2                      | 0.4                         | V <sub>CCO</sub> - 0.4     |  |

|                                                  | 4     | 4                       | -4                      | -                           |                            |  |

|                                                  | 6     | 6                       | -6                      | -                           |                            |  |

| LVCMOS15 <sup>(4)</sup>                          | 2     | 2                       | -2                      | 0.4                         | V <sub>CCO</sub> – 0.4     |  |

|                                                  | 4     | 4                       | -4                      | -                           | 000                        |  |

|                                                  | 6     | 6                       | -6                      | -                           |                            |  |

|                                                  | 8     | 8                       | -8                      | -                           |                            |  |

|                                                  | 12    | 12                      | -12                     | -                           |                            |  |

| LVDCI_15,<br>LVDCI_DV2_15                        |       | Note 3                  | Note 3                  | -                           |                            |  |

| LVCMOS18 <sup>(4)</sup>                          | 2     | 2                       | -2                      | 0.4                         | V <sub>CCO</sub> – 0.4     |  |

|                                                  | 4     | 4                       | -4                      | -                           |                            |  |

|                                                  | 6     | 6                       | -6                      | -                           |                            |  |

|                                                  | 8     | 8                       | -8                      | -                           |                            |  |

|                                                  | 12    | 12                      | -12                     | -                           |                            |  |

|                                                  | 16    | 16                      | -16                     | -                           |                            |  |

| LVDCI_18,<br>LVDCI_DV2_18                        |       | Note 3                  | Note 3                  | -                           |                            |  |

| LVCMOS25 <sup>(4,5)</sup>                        | 2     | 2                       | -2                      | 0.4                         | V <sub>CCO</sub> – 0.4     |  |

|                                                  | 4     | 4                       | -4                      | 1                           |                            |  |

|                                                  | 6     | 6                       | -6                      | 1                           |                            |  |

|                                                  | 8     | 8                       | -8                      | -                           |                            |  |

|                                                  | 12    | 12                      | -12                     | -                           |                            |  |

|                                                  | 16    | 16                      | -16                     | =                           |                            |  |

|                                                  | 24    | 24                      | -24                     | -                           |                            |  |

| LVDCI_25,<br>LVDCI_DV2_25                        |       | Note 3                  | Note 3                  | -                           |                            |  |

#### Table 48: Test Methods for Timing Measurement at I/Os (Cont'd)

| Signal Standard<br>(IOSTANDARD) |         |                      | Inputs                   |                          | Out                       | Inputs and<br>Outputs |                    |

|---------------------------------|---------|----------------------|--------------------------|--------------------------|---------------------------|-----------------------|--------------------|

|                                 |         | V <sub>REF</sub> (V) | V <sub>L</sub> (V)       | V <sub>H</sub> (V)       | <b>R</b> <sub>T</sub> (Ω) | V <sub>T</sub> (V)    | V <sub>M</sub> (V) |

| HSTL_III_18                     |         | 1.1                  | V <sub>REF</sub> – 0.5   | V <sub>REF</sub> + 0.5   | 50                        | 1.8                   | V <sub>REF</sub>   |

| HSTL_III_DC                     | CI_18   |                      |                          |                          |                           |                       |                    |

| LVCMOS12                        |         | -                    | 0                        | 1.2                      | 1M                        | 0                     | 0.6                |

| VCMOS15                         |         | -                    | 0                        | 1.5                      | 1M                        | 0                     | 0.75               |

| VDCI_15                         |         |                      |                          |                          |                           |                       |                    |

| VDCI_DV2_                       | 15      |                      |                          |                          |                           |                       |                    |

| HSLVDCI_15                      | 5       |                      |                          |                          |                           |                       |                    |

| VCMOS18                         |         | -                    | 0                        | 1.8                      | 1M                        | 0                     | 0.9                |

| VDCI_18                         |         |                      |                          |                          |                           |                       |                    |

| VDCI_DV2_                       | 18      |                      |                          |                          |                           |                       |                    |

| ISLVDCI_18                      | }       | -                    |                          |                          |                           |                       |                    |

| VCMOS25                         |         | -                    | 0                        | 2.5                      | 1M                        | 0                     | 1.25               |

| VDCI_25                         |         |                      |                          |                          |                           |                       |                    |

| VDCI_DV2_                       | _25     |                      |                          |                          |                           |                       |                    |

| HSLVDCI_25                      | 5       |                      |                          |                          |                           |                       |                    |

| VCMOS33                         |         | -                    | 0                        | 3.3                      | 1M                        | 0                     | 1.65               |

| VDCI_33                         |         |                      |                          |                          |                           |                       |                    |

| VDCI_DV2_                       | 33      |                      |                          |                          |                           |                       |                    |

| HSLVDCI_33                      |         |                      |                          |                          |                           |                       |                    |

| VTTL                            |         | -                    | 0                        | 3.3                      | 1M                        | 0                     | 1.4                |

| PCI33_3                         | Rising  | -                    | Note 3                   | Note 3                   | 25                        | 0                     | 0.94               |

|                                 | Falling |                      |                          | =                        | 25                        | 3.3                   | 2.03               |

| STL18_I                         | •       | 0.9                  | V <sub>REF</sub> – 0.5   | V <sub>REF</sub> + 0.5   | 50                        | 0.9                   | V <sub>REF</sub>   |

| STL18_I_D                       | CI      |                      |                          |                          |                           |                       |                    |

| STL18_II                        |         | 0.9                  | V <sub>REF</sub> – 0.5   | V <sub>REF</sub> + 0.5   | 50                        | 0.9                   | V <sub>REF</sub>   |

| STL2_I                          |         | 1.25                 | V <sub>REF</sub> – 0.75  | V <sub>REF</sub> + 0.75  | 50                        | 1.25                  | V <sub>REF</sub>   |

| SSTL2_I_DC                      |         |                      |                          |                          |                           |                       |                    |

| SSTL2_II                        |         | 1.25                 | V <sub>REF</sub> – 0.75  | V <sub>REF</sub> + 0.75  | 25                        | 1.25                  | V <sub>REF</sub>   |

| SSTL2_II_D                      | CI      |                      |                          |                          | 50                        | 1.25                  |                    |

| Differential                    |         |                      |                          |                          |                           |                       |                    |

| DT_25 (UL\                      | /DS_25) | -                    | V <sub>ICM</sub> – 0.125 | V <sub>ICM</sub> + 0.125 | 60                        | 0.6                   | V <sub>ICM</sub>   |

|                                 | *       | -                    | V <sub>ICM</sub> – 0.125 | V <sub>ICM</sub> + 0.125 | 50                        | 1.2                   | V <sub>ICM</sub>   |

| LVDS_25_DCI                     |         | -                    |                          |                          | N/A                       | N/A                   |                    |

| BLVDS_25                        |         | -                    | V <sub>ICM</sub> – 0.125 | V <sub>ICM</sub> + 0.125 | 1M                        | 0                     | V <sub>ICM</sub>   |

| VDSEXT_2                        | 5       | -                    | V <sub>ICM</sub> – 0.125 | V <sub>ICM</sub> + 0.125 | 50                        | 1.2                   | V <sub>ICM</sub>   |

| LVDSEXT_25_DCI                  |         | —                    |                          |                          | N/A                       | N/A                   |                    |

| VPECL_25                        |         | -                    | V <sub>ICM</sub> – 0.3   | V <sub>ICM</sub> + 0.3   | 1M                        | 0                     | V <sub>ICM</sub>   |

| RSDS_25                         |         | -                    | V <sub>ICM</sub> – 0.1   | V <sub>ICM</sub> + 0.1   | 50                        | 1.2                   | V <sub>ICM</sub>   |

| DIFF_HSTL                       | II 18   | -                    | V <sub>ICM</sub> – 0.5   | V <sub>ICM</sub> + 0.5   | 50                        | 1.8                   | V <sub>ICM</sub>   |

| DIFF_HSTL                       |         | -                    |                          |                          |                           |                       |                    |

### Table 50: Recommended Number of Simultaneously Switching Outputs per V<sub>CCO</sub>/GND Pair (Cont'd)

| Cime                            | al Chandard |    | Package |       |       |       |                                              |

|---------------------------------|-------------|----|---------|-------|-------|-------|----------------------------------------------|

| Signal Standard<br>(IOSTANDARD) |             |    | VQ100   | TQ144 | PQ208 | CP132 | FT256, FG320, FG456,<br>FG676, FG900, FG1156 |

| LVCMOS33                        | Slow        | 2  | 34      | 24    | 24    | 52    | 76                                           |

|                                 |             | 4  | 17      | 14    | 14    | 26    | 46                                           |

|                                 |             | 6  | 17      | 11    | 11    | 26    | 27                                           |

|                                 |             | 8  | 10      | 10    | 10    | 13    | 20                                           |

|                                 |             | 12 | 9       | 9     | 9     | 13    | 13                                           |

|                                 |             | 16 | 8       | 8     | 8     | 8     | 10                                           |

|                                 |             | 24 | 8       | 8     | 8     | 8     | 9                                            |

|                                 | Fast        | 2  | 20      | 20    | 20    | 26    | 44                                           |

|                                 |             | 4  | 15      | 15    | 15    | 15    | 26                                           |

|                                 |             | 6  | 11      | 11    | 11    | 13    | 16                                           |

|                                 |             | 8  | 10      | 10    | 10    | 10    | 12                                           |

|                                 |             | 12 | 8       | 8     | 8     | 8     | 10                                           |

|                                 |             | 16 | 8       | 8     | 8     | 8     | 8                                            |

|                                 |             | 24 | 7       | 7     | 7     | 7     | 7                                            |

| LVDCI_33                        |             | -+ | 10      | 10    | 10    | 10    | 10                                           |

| LVDCI_DV2_33                    |             |    | 10      | 10    | 10    | 10    | 10                                           |

| HSLVDCI_33                      |             |    | 10      | 10    | 10    | 10    | 10                                           |

| LVTTL                           | Slow        | 2  | 34      | 25    | 25    | 52    | 60                                           |

|                                 |             | 4  | 17      | 16    | 16    | 26    | 41                                           |

|                                 |             | 6  | 17      | 15    | 15    | 26    | 29                                           |

|                                 |             | 8  | 12      | 12    | 12    | 13    | 22                                           |

|                                 |             | 12 | 10      | 10    | 10    | 13    | 13                                           |

|                                 |             | 16 | 10      | 10    | 10    | 10    | 11                                           |

|                                 |             | 24 | 8       | 8     | 8     | 8     | 9                                            |

|                                 | Fast        | 2  | 20      | 20    | 20    | 26    | 34                                           |

|                                 |             | 4  | 13      | 13    | 13    | 13    | 20                                           |

|                                 |             | 6  | 11      | 11    | 11    | 13    | 15                                           |

|                                 |             | 8  | 10      | 10    | 10    | 10    | 12                                           |

|                                 |             | 12 | 9       | 9     | 9     | 9     | 10                                           |

|                                 |             | 16 | 8       | 8     | 8     | 8     | 9                                            |

|                                 |             | 24 | 7       | 7     | 7     | 7     | 7                                            |

www.xilinx.com

#### Table 50: Recommended Number of Simultaneously Switching Outputs per V<sub>CCO</sub>/GND Pair (Cont'd)

| Cinnel Chenderd                            |                 | Package  |          |       |                                              |  |  |  |

|--------------------------------------------|-----------------|----------|----------|-------|----------------------------------------------|--|--|--|

| Signal Standard<br>(IOSTANDARD)            | VQ100           | TQ144    | PQ208    | CP132 | FT256, FG320, FG456,<br>FG676, FG900, FG1156 |  |  |  |

| PCl33_3                                    | 9               | 9        | 9        | 9     | 9                                            |  |  |  |

| SSTL18_I                                   | 13              | 13       | 13       | 13    | 17                                           |  |  |  |

| SSTL18_I_DCI                               | 13              | 13       | 13       | 13    | 17                                           |  |  |  |

| SSTL18_II                                  | 8               | 8        | 8        | 8     | 9                                            |  |  |  |

| SSTL2_I                                    | 10              | 10       | 10       | 10    | 13                                           |  |  |  |

| SSTL2_I_DCI                                | 10              | 10       | 10       | 10    | 13                                           |  |  |  |

| SSTL2_II                                   | 6               | 6        | 6        | 6     | 9                                            |  |  |  |

| SSTL2_II_DCI                               | 6               | 6        | 6        | 6     | 9                                            |  |  |  |

| Differential Standards (Number of I/O Pair | rs or Channels) | <u>.</u> | <u>+</u> |       |                                              |  |  |  |

| LDT_25 (ULVDS_25)                          | 5               | 5        | 5        | 5     | 5                                            |  |  |  |

| LVDS_25                                    | 7               | 5        | 5        | 12    | 20                                           |  |  |  |

| BLVDS_25                                   | 2               | 1        | 1        |       | 4                                            |  |  |  |

| LVDSEXT_25                                 | 5               | 5        | 5        | 5     | 5                                            |  |  |  |

| LVPECL_25                                  | 2               | 1        | 1        |       | 4                                            |  |  |  |

| RSDS_25                                    | 7               | 5        | 5        | 12    | 20                                           |  |  |  |

| DIFF_HSTL_II_18                            | 4               | 4        | 4        | 4     | 4                                            |  |  |  |

| DIFF_HSTL_II_18_DCI                        | 4               | 4        | 4        | 4     | 4                                            |  |  |  |

| DIFF_SSTL2_II                              | 3               | 3        | 3        | 3     | 4                                            |  |  |  |

| DIFF_SSTL2_II_DCI                          | 3               | 3        | 3        | 3     | 4                                            |  |  |  |

Notes:

The numbers in this table are recommendations that assume the FPGA is soldered on a printed circuit board using sound practices. This table assumes the following parasitic factors: combined PCB trace and land inductance per V<sub>CCO</sub> and GND pin of 1.0 nH, receiver capacitive load of 15 pF. Test limits are the V<sub>IL</sub>/V<sub>IH</sub> voltage limits for the respective I/O standard.

2. Regarding the SSO numbers for all DCI standards, the R<sub>REF</sub> resistors connected to the VRN and VRP pins of the FPGA are 50W.

3. If more than one signal standard is assigned to the I/Os of a given bank, refer to XAPP689: Managing Ground Bounce in Large FPGAs for information on how to perform weighted average SSO calculations.

4. Results are based on actual silicon testing using an FPGA soldered on a typical printed-circuit board.

#### Phase Shifter (PS)

Phase shifter operation is only supported if the DLL is in low-frequency mode, see Table 58. Fixed phase shift requires ISE software version 10.1.03 (or later).

#### Table 62: Recommended Operating Conditions for the PS in Variable Phase Mode

| Symbol                              | Description                         |       | quency Mode/<br><sub>CLKIN</sub> Range | -5  |     | -   | 4   | Units |  |

|-------------------------------------|-------------------------------------|-------|----------------------------------------|-----|-----|-----|-----|-------|--|

|                                     |                                     | CLKIN |                                        | Min | Max | Min | Max |       |  |

| Operating Freque                    | Operating Frequency Ranges          |       |                                        |     |     |     |     |       |  |

| PSCLK_FREQ<br>(F <sub>PSCLK</sub> ) | Frequency for the<br>PSCLK input    | Low   |                                        | 1   | 167 | 1   | 167 | MHz   |  |

| Input Pulse Requ                    | irements                            |       |                                        |     |     |     |     |       |  |

| PSCLK_PULSE                         | PSCLK pulse width                   | Low   | $F_{CLKIN} \le 100 \text{ MHz}$        | 40% | 60% | 40% | 60% | -     |  |

|                                     | as a percentage of the PSCLK period |       | F <sub>CLKIN</sub> > 100 MHz           | 45% | 55% | 45% | 55% | -     |  |

#### Table 63: Switching Characteristics for the PS in Variable or Fixed Phase Shift Mode

| Symbol               | Description                                                                                                                                                                                                                                  | Frequency Mode/<br>F <sub>CLKIN</sub> Range                     | -5  |       | -4  |       | Units |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|-----|-------|-----|-------|-------|

|                      |                                                                                                                                                                                                                                              |                                                                 | Min | Мах   | Min | Max   | _     |

| Phase Shifting Range |                                                                                                                                                                                                                                              |                                                                 |     |       |     |       |       |

| FINE_SHIFT_RANGE     | Phase shift range                                                                                                                                                                                                                            | Low                                                             | _   | 10.0  | -   | 10.0  | ns    |

| Lock Time            |                                                                                                                                                                                                                                              |                                                                 | 1   |       |     |       |       |

| LOCK_DLL_PS          | When using the PS in conjunction                                                                                                                                                                                                             | $18 \text{ MHz} \le \text{F}_{\text{CLKIN}} \le 30 \text{ MHz}$ | _   | 3.28  | -   | 3.28  | ms    |

|                      | with the DLL: The time from<br>deassertion at the DCM's Reset<br>input to the rising transition at its<br>LOCKED output. When the DCM<br>is locked, the CLKIN and CLKFB                                                                      | $30 \text{ MHz} < \text{F}_{\text{CLKIN}} \le 40 \text{ MHz}$   | _   | 2.56  | -   | 2.56  | ms    |

|                      |                                                                                                                                                                                                                                              | 40 MHz < $F_{CLKIN} \le 50$ MHz                                 | _   | 1.60  | -   | 1.60  | ms    |

|                      |                                                                                                                                                                                                                                              | 50 MHz < $F_{CLKIN} \le 60$ MHz                                 | _   | 1.00  | -   | 1.00  | ms    |

|                      | signals are in phase.                                                                                                                                                                                                                        | $60 \text{ MHz} < \text{F}_{\text{CLKIN}} \le 165 \text{ MHz}$  | _   | 0.88  | -   | 0.88  | ms    |

| LOCK_DLL_PS_FX       | When using the PS in conjunction<br>with the DLL and DFS: The time<br>from deassertion at the DCM's<br>Reset input to the rising transition<br>at its LOCKED output. When the<br>DCM is locked, the CLKIN and<br>CLKFB signals are in phase. | Low                                                             | -   | 10.40 | -   | 10.40 | ms    |

Notes:

1. The numbers in this table are based on the operating conditions set forth in Table 32 and Table 62.

2. The PS specifications in this table apply when the PS attribute CLKOUT\_PHASE\_SHIFT= VARIABLE or FIXED.

#### CCLK: Configuration Clock

The configuration clock signal on this pin synchronizes the reading or writing of configuration data. The CCLK pin is an input-only pin for the Slave Serial and Slave Parallel configuration modes. In the Master Serial and Master Parallel configuration modes, the FPGA drives the CCLK pin and CCLK should be treated as a full bidirectional I/O pin for signal integrity analysis.

Although the CCLK frequency is relatively low, Spartan-3 FPGA output edge rates are fast. Any potential signal integrity problems on the CCLK board trace can cause FPGA configuration to fail. Therefore, pay careful attention to the CCLK signal integrity on the printed circuit board. Signal integrity simulation with IBIS is recommended. For all configuration modes except JTAG, consider the signal integrity at every CCLK trace destination, including the FPGA's CCLK pin. For more details on CCLK design considerations, see Chapter 2 of UG332, Spartan-3 Generation Configuration User Guide.

During configuration, the CCLK pin has a pull-up resistor to VCCAUX, regardless of the HSWAP\_EN pin. After configuration, the CCLK pin is pulled High to VCCAUX by default as defined by the *CclkPin* bitstream selection, although this behavior is programmable. Any clocks applied to CCLK after configuration are ignored unless the bitstream option *Persist* is set to *Yes*, which retains the configuration interface. *Persist* is set to *No* by default. However, if *Persist* is set to *Yes*, then all clock edges are potentially active events, depending on the other configuration control signals.

The bitstream generator option *ConfigRate* determines the frequency of the internally-generated CCLK oscillator required for the Master configuration modes. The actual frequency is approximate due to the characteristics of the silicon oscillator and varies by up to 50% over the temperature and voltage range. By default, CCLK operates at approximately 6 MHz. Via the *ConfigRate* option, the oscillator frequency is set at approximately 3, 6, 12, 25, or 50 MHz. At power-on, CCLK always starts operation at its lowest frequency. The device does not start operating at the higher frequency until the ConfigRate control bits are loaded during the configuration process.

#### PROG\_B: Program/Configure Device

This asynchronous pin initiates the configuration or re-configuration processes. A Low-going pulse resets the configuration logic, initializing the configuration memory. This initialization process cannot finish until PROG\_B returns High. Asserting PROG\_B Low for an extended period delays the configuration process. At power-up, there is always a pull-up resistor to VCCAUX on this pin, regardless of the HSWAP\_EN input. After configuration, the bitstream generator option *ProgPin* determines whether or not the pull-up resistor is present. By default, the *ProgPin* option retains the pull-up resistor.

After configuration, hold the PROG\_B input High. Any Low-going pulse on PROG\_B lasting 300 ns or longer restarts the configuration process.

| PROG_B Input    | Response                                                                                                                                           |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| Power-up        | Automatically initiates configuration process.                                                                                                     |

| Low-going pulse | Initiate (re-)configuration process and continue to completion.                                                                                    |

| Extended Low    | Initiate (re-)configuration process and stall process at step where configuration memory is cleared. Process is stalled until PROG_B returns High. |

| 1               | If the configuration process is started, continue to completion. If configuration process is complete, stay in User mode.                          |

#### Table 73: PROG\_B Operation

#### DONE: Configuration Done, Delay Start-Up Sequence

The FPGA produces a Low-to-High transition on this pin indicating that the configuration process is complete. The bitstream generator option *DriveDone* determines whether this pin functions as a totem-pole output that can drive High or as an open-drain output. If configured as an open-drain output—which is the default behavior—then a pull-up resistor is required to produce a High logic level. There is a bitstream option that provides an internal pull-up resistor, otherwise an external pull-up resistor is required.

The open-drain option permits the DONE lines of multiple FPGAs to be tied together, so that the common node transitions High only after all of the FPGAs have completed configuration. Externally holding the open-drain DONE pin Low delays the start-up sequence, which marks the transition to user mode.

# TQ144: 144-lead Thin Quad Flat Package

The XC3S50, the XC3S200, and the XC3S400 are available in the 144-lead thin quad flat package, TQ144. All devices share a common footprint for this package as shown in Table 91 and Figure 46.

The TQ144 package only has four separate VCCO inputs, unlike the BGA packages, which have eight separate VCCO inputs. The TQ144 package has a separate VCCO input for the top, bottom, left, and right. However, there are still eight separate I/O banks, as shown in Table 91 and Figure 46. Banks 0 and 1 share the VCCO\_TOP input, Banks 2 and 3 share the VCCO\_RIGHT input, Banks 4 and 5 share the VCCO\_BOTTOM input, and Banks 6 and 7 share the VCCO\_LEFT input.

All the package pins appear in Table 91 and are sorted by bank number, then by pin name. Pairs of pins that form a differential I/O pair appear together in the table. The table also shows the pin number for each pin and the pin type, as defined earlier.

An electronic version of this package pinout table and footprint diagram is available for download from the Xilinx website at <a href="http://www.xilinx.com/support/documentation/data\_sheets/s3\_pin.zip">http://www.xilinx.com/support/documentation/data\_sheets/s3\_pin.zip</a>.

### **Pinout Table**

| Bank | XC3S50, XC3S200,<br>XC3S400 Pin Name | TQ144 Pin<br>Number | Туре |

|------|--------------------------------------|---------------------|------|

| 0    | IO_L01N_0/VRP_0                      | P141                | DCI  |

| 0    | IO_L01P_0/VRN_0                      | P140                | DCI  |

| 0    | IO_L27N_0                            | P137                | I/O  |

| 0    | IO_L27P_0                            | P135                | I/O  |

| 0    | IO_L30N_0                            | P132                | I/O  |

| 0    | IO_L30P_0                            | P131                | I/O  |

| 0    | IO_L31N_0                            | P130                | I/O  |

| 0    | IO_L31P_0/VREF_0                     | P129                | VREF |

| 0    | IO_L32N_0/GCLK7                      | P128                | GCLK |

| 0    | IO_L32P_0/GCLK6                      | P127                | GCLK |

| 1    | Ю                                    | P116                | I/O  |

| 1    | IO_L01N_1/VRP_1                      | P113                | DCI  |

| 1    | IO_L01P_1/VRN_1                      | P112                | DCI  |

| 1    | IO_L28N_1                            | P119                | I/O  |

| 1    | IO_L28P_1                            | P118                | I/O  |

| 1    | IO_L31N_1/VREF_1                     | P123                | VREF |

| 1    | IO_L31P_1                            | P122                | I/O  |

| 1    | IO_L32N_1/GCLK5                      | P125                | GCLK |

| 1    | IO_L32P_1/GCLK4                      | P124                | GCLK |

| 2    | IO_L01N_2/VRP_2                      | P108                | DCI  |

| 2    | IO_L01P_2/VRN_2                      | P107                | DCI  |

| 2    | IO_L20N_2                            | P105                | I/O  |

| 2    | IO_L20P_2                            | P104                | I/O  |

| 2    | IO_L21N_2                            | P103                | I/O  |

| 2    | IO_L21P_2                            | P102                | I/O  |

| 2    | IO_L22N_2                            | P100                | I/O  |

| 2    | IO_L22P_2                            | P99                 | I/O  |

Table 91: TQ144 Package Pinout

www.xilinx.com

#### Table 93: PQ208 Package Pinout (Cont'd)

| Bank   | XC3S50<br>Pin Name | XC3S200, XC3S400<br>Pin Names | PQ208 Pin<br>Number | Туре   |

|--------|--------------------|-------------------------------|---------------------|--------|

| N/A    | GND                | GND                           | P14                 | GND    |

| N/A    | GND                | GND                           | P25                 | GND    |

| N/A    | VCCAUX             | VCCAUX                        | P193                | VCCAUX |

| N/A    | VCCAUX             | VCCAUX                        | P173                | VCCAUX |

| N/A    | VCCAUX             | VCCAUX                        | P142                | VCCAUX |

| N/A    | VCCAUX             | VCCAUX                        | P121                | VCCAUX |

| N/A    | VCCAUX             | VCCAUX                        | P89                 | VCCAUX |

| N/A    | VCCAUX             | VCCAUX                        | P69                 | VCCAUX |

| N/A    | VCCAUX             | VCCAUX                        | P38                 | VCCAUX |

| N/A    | VCCAUX             | VCCAUX                        | P17                 | VCCAUX |

| N/A    | VCCINT             | VCCINT                        | P192                | VCCINT |

| N/A    | VCCINT             | VCCINT                        | P174                | VCCINT |

| N/A    | VCCINT             | VCCINT                        | P88                 | VCCINT |

| N/A    | VCCINT             | VCCINT                        | P70                 | VCCINT |

| VCCAUX | CCLK               | CCLK                          | P104                | CONFIG |

| VCCAUX | DONE               | DONE                          | P103                | CONFIG |

| VCCAUX | HSWAP_EN           | HSWAP_EN                      | P206                | CONFIG |

| VCCAUX | MO                 | MO                            | P55                 | CONFIG |

| VCCAUX | M1                 | M1                            | P54                 | CONFIG |

| VCCAUX | M2                 | M2                            | P56                 | CONFIG |

| VCCAUX | PROG_B             | PROG_B                        | P207                | CONFIG |

| VCCAUX | тск                | ТСК                           | P159                | JTAG   |

| VCCAUX | TDI                | TDI                           | P208                | JTAG   |

| VCCAUX | TDO                | TDO                           | P158                | JTAG   |

| VCCAUX | TMS                | TMS                           | P160                | JTAG   |

# User I/Os by Bank

Table 94 indicates how the available user-I/O pins are distributed between the eight I/O banks for the XC3S50 in the PQ208 package. Similarly, Table 95 shows how the available user-I/O pins are distributed between the eight I/O banks for the XC3S200 and XC3S400 in the PQ208 package.

| Table 94: User I/Os Per Bank for XC3S50 in PQ208 Package |

|----------------------------------------------------------|

|----------------------------------------------------------|

| Dookogo Edgo | I/O Bank | Maximum I/O | All Possible I/O Pins by Type |      |     |      |      |  |  |  |

|--------------|----------|-------------|-------------------------------|------|-----|------|------|--|--|--|

| Package Edge |          |             | I/O                           | DUAL | DCI | VREF | GCLK |  |  |  |

| Тор          | 0        | 15          | 9                             | 0    | 2   | 2    | 2    |  |  |  |

| юр           | 1        | 15          | 9                             | 0    | 2   | 2    | 2    |  |  |  |

| Right        | 2        | 16          | 13                            | 0    | 2   | 2    | 0    |  |  |  |

| nigin        | 3        | 16          | 12                            | 0    | 2   | 2    | 0    |  |  |  |

| Bottom       | 4        | 15          | 3                             | 6    | 2   | 2    | 2    |  |  |  |

| Bollom       | 5        | 15          | 3                             | 6    | 2   | 2    | 2    |  |  |  |

| Left         | 6        | 16          | 12                            | 0    | 2   | 2    | 0    |  |  |  |

| Leit         | 7        | 16          | 12                            | 0    | 2   | 2    | 0    |  |  |  |

#### Table 95: User I/Os Per Bank for XC3S200 and XC3S400 in PQ208 Package

| Dooleano Edno | I/O Bank | Maximum I/O | All Possible I/O Pins by Type |      |     |      |      |  |  |  |

|---------------|----------|-------------|-------------------------------|------|-----|------|------|--|--|--|

| Package Edge  |          |             | I/O                           | DUAL | DCI | VREF | GCLK |  |  |  |

| Тор           | 0        | 16          | 9                             | 0    | 2   | 3    | 2    |  |  |  |

| юр            | 1        | 15          | 9                             | 0    | 2   | 2    | 2    |  |  |  |

| Diabt         | 2        | 19          | 14                            | 0    | 2   | 3    | 0    |  |  |  |

| Right         | 3        | 20          | 15                            | 0    | 2   | 3    | 0    |  |  |  |

| Pottom        | 4        | 17          | 4                             | 6    | 2   | 3    | 2    |  |  |  |

| Bottom        | 5        | 15          | 3                             | 6    | 2   | 2    | 2    |  |  |  |

| 1.54          | 6        | 19          | 14                            | 0    | 2   | 3    | 0    |  |  |  |

| Left          | 7        | 20          | 15                            | 0    | 2   | 3    | 0    |  |  |  |

# FG320: 320-lead Fine-pitch Ball Grid Array

The 320-lead fine-pitch ball grid array package, FG320, supports three different Spartan-3 devices, including the XC3S400, the XC3S1000, and the XC3S1500. The footprint for all three devices is identical, as shown in Table 98 and Figure 50.

The FG320 package is an 18 x 18 array of solder balls minus the four center balls.

All the package pins appear in Table 98 and are sorted by bank number, then by pin name. Pairs of pins that form a differential I/O pair appear together in the table. The table also shows the pin number for each pin and the pin type, as defined earlier.

An electronic version of this package pinout table and footprint diagram is available for download from the Xilinx website at <a href="http://www.xilinx.com/support/documentation/data\_sheets/s3\_pin.zip">http://www.xilinx.com/support/documentation/data\_sheets/s3\_pin.zip</a>.

### **Pinout Table**

Table 98: FG320 Package Pinout

| Bank | XC3S400, XC3S1000, XC3S1500<br>Pin Name | FG320<br>Pin Number | Туре |

|------|-----------------------------------------|---------------------|------|

| 0    | IO                                      | D9                  | I/O  |

| 0    | IO                                      | E7                  | I/O  |

| 0    | IO/VREF_0                               | B3                  | VREF |

| 0    | IO/VREF_0                               | D6                  | VREF |

| 0    | IO_L01N_0/VRP_0                         | A2                  | DCI  |

| 0    | IO_L01P_0/VRN_0                         | A3                  | DCI  |

| 0    | IO_L09N_0                               | B4                  | I/O  |

| 0    | IO_L09P_0                               | C4                  | I/O  |

| 0    | IO_L10N_0                               | C5                  | I/O  |

| 0    | IO_L10P_0                               | D5                  | I/O  |

| 0    | IO_L15N_0                               | A4                  | I/O  |

| 0    | IO_L15P_0                               | A5                  | I/O  |

| 0    | IO_L25N_0                               | B5                  | I/O  |

| 0    | IO_L25P_0                               | B6                  | I/O  |

| 0    | IO_L27N_0                               | C7                  | I/O  |

| 0    | IO_L27P_0                               | D7                  | I/O  |

| 0    | IO_L28N_0                               | C8                  | I/O  |

| 0    | IO_L28P_0                               | D8                  | I/O  |

| 0    | IO_L29N_0                               | E8                  | I/O  |

| 0    | IO_L29P_0                               | F8                  | I/O  |

| 0    | IO_L30N_0                               | A7                  | I/O  |

| 0    | IO_L30P_0                               | A8                  | I/O  |

| 0    | IO_L31N_0                               | B9                  | I/O  |

| 0    | IO_L31P_0/VREF_0                        | A9                  | VREF |

| 0    | IO_L32N_0/GCLK7                         | E9                  | GCLK |

| 0    | IO_L32P_0/GCLK6                         | F9                  | GCLK |

| 0    | VCCO_0                                  | B8                  | VCCO |

| 0    | VCCO_0                                  | C6                  | VCCO |

| 0    | VCCO_0                                  | G8                  | VCCO |

www.xilinx.com

#### Table 107: FG900 Package Pinout (Cont'd)

| Bank | XC3S2000<br>Pin Name | XC3S4000, XC3S5000<br>Pin Name | FG900 Pin<br>Number | Туре |

|------|----------------------|--------------------------------|---------------------|------|

| 1    | IO_L25P_1            | IO_L25P_1                      | D19                 | I/O  |

| 1    | IO_L26N_1            | IO_L26N_1                      | A19                 | I/O  |

| 1    | IO_L26P_1            | IO_L26P_1                      | B19                 | I/O  |

| 1    | IO_L27N_1            | IO_L27N_1                      | F17                 | I/O  |

| 1    | IO_L27P_1            | IO_L27P_1                      | G17                 | I/O  |

| 1    | IO_L28N_1            | IO_L28N_1                      | B17                 | I/O  |

| 1    | IO_L28P_1            | IO_L28P_1                      | C17                 | I/O  |

| 1    | IO_L29N_1            | IO_L29N_1                      | J16                 | I/O  |

| 1    | IO_L29P_1            | IO_L29P_1                      | K16                 | I/O  |

| 1    | IO_L30N_1            | IO_L30N_1                      | G16                 | I/O  |

| 1    | IO_L30P_1            | IO_L30P_1                      | H16                 | I/O  |

| 1    | IO_L31N_1/VREF_1     | IO_L31N_1/VREF_1               | D16                 | VREF |

| 1    | IO_L31P_1            | IO_L31P_1                      | E16                 | I/O  |

| 1    | IO_L32N_1/GCLK5      | IO_L32N_1/GCLK5                | B16                 | GCLK |

| 1    | IO_L32P_1/GCLK4      | IO_L32P_1/GCLK4                | C16                 | GCLK |

| 1    | N.C. (♦)             | IO_L37N_1                      | H18                 | I/O  |

| 1    | N.C. (♦)             | IO_L37P_1                      | J18                 | I/O  |

| 1    | N.C. (♦)             | IO_L38N_1                      | D18                 | I/O  |

| 1    | N.C. (♦)             | IO_L38P_1                      | E18                 | I/O  |

| 1    | N.C. (♦)             | IO_L39N_1                      | A18                 | I/O  |

| 1    | N.C. (♦)             | IO_L39P_1                      | B18                 | I/O  |

| 1    | N.C. (�)             | IO_L40N_1                      | K17                 | I/O  |

| 1    | N.C. (♦)             | IO_L40P_1                      | K18                 | I/O  |

| 1    | VCCO_1               | VCCO_1                         | L17                 | VCCO |

| 1    | VCCO_1               | VCCO_1                         | C18                 | VCCO |