# E·XFL

#### AMD Xilinx - XC3S400-4TQG144I Datasheet

Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                              |

|--------------------------------|--------------------------------------------------------------|

| Product Status                 | Active                                                       |

| Number of LABs/CLBs            | 896                                                          |

| Number of Logic Elements/Cells | 8064                                                         |

| Total RAM Bits                 | 294912                                                       |

| Number of I/O                  | 97                                                           |

| Number of Gates                | 400000                                                       |

| Voltage - Supply               | 1.14V ~ 1.26V                                                |

| Mounting Type                  | Surface Mount                                                |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                           |

| Package / Case                 | 144-LQFP                                                     |

| Supplier Device Package        | 144-TQFP (20x20)                                             |

| Purchase URL                   | https://www.e-xfl.com/product-detail/xilinx/xc3s400-4tqg144i |

|                                |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

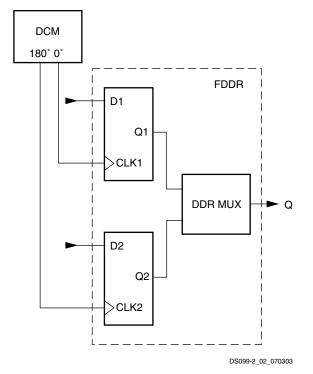

Figure 8: Clocking the DDR Register

Aside from high bandwidth data transfers, DDR can also be used to reproduce, or "mirror", a clock signal on the output. This approach is used to transmit clock and data signals together. A similar approach is used to reproduce a clock signal at multiple outputs. The advantage for both approaches is that skew across the outputs will be minimal.

Some adjacent I/O blocks (IOBs) share common routing connecting the ICLK1, ICLK2, OTCLK1, and OTCLK2 clock inputs of both IOBs. These IOB pairs are identified by their differential pair names IO\_LxxN\_# and IO\_LxxP\_#, where "xx" is an I/O pair number and '#' is an I/O bank number. Two adjacent IOBs containing DDR registers must share common clock inputs, otherwise one or more of the clock signals will be unroutable.

## **Pull-Up and Pull-Down Resistors**

The optional pull-up and pull-down resistors are intended to establish High and Low levels, respectively, at unused I/Os. The pull-up resistor optionally connects each IOB pad to  $V_{CCO}$ . A pull-down resistor optionally connects each pad to GND. These resistors are placed in a design using the PULLUP and PULLDOWN symbols in a schematic, respectively. They can also be instantiated as components, set as constraints or passed as attributes in HDL code. These resistors can also be selected for all unused I/O using the Bitstream Generator (BitGen) option UnusedPin. A Low logic level on HSWAP\_EN activates the pull-up resistors on all I/Os during configuration (see The I/Os During Power-On, Configuration, and User Mode, page 21).

The Spartan-3 FPGAs I/O pull-up and pull-down resistors are significantly stronger than the "weak" pull-up/pull-down resistors used in previous Xilinx FPGA families. See Table 33, page 61 for equivalent resistor strengths.

## **Keeper Circuit**

Each I/O has an optional keeper circuit that retains the last logic level on a line after all drivers have been turned off. This is useful to keep bus lines from floating when all connected drivers are in a high-impedance state. This function is placed in a design using the KEEPER symbol. Pull-up and pull-down resistors override the keeper circuit.

## Coarse Phase Shift Outputs of the DLL Component

In addition to CLK0 for zero-phase alignment to the CLKIN signal, the DLL also provides the CLK90, CLK180 and CLK270 outputs for 90°, 180° and 270° phase-shifted signals, respectively. These signals are described in Table 16, page 33. Their relative timing in the Low Frequency Mode is shown in Figure 22, page 37. The CLK90, CLK180 and CLK270 outputs are not available when operating in the High Frequency mode. (See the description of the DLL\_FREQUENCY\_MODE attribute in Table 17, page 33.) For control in finer increments than 90°, see Phase Shifter (PS), page 39.

## **Basic Frequency Synthesis Outputs of the DLL Component**

The DLL component provides basic options for frequency multiplication and division in addition to the more flexible synthesis capability of the DFS component, described in a later section. These operations result in output clock signals with frequencies that are either a fraction (for division) or a multiple (for multiplication) of the incoming clock frequency. The CLK2X output produces an in-phase signal that is twice the frequency of CLKIN. The CLK2X180 output also doubles the frequency, but is 180° out-of-phase with respect to CLKIN. The CLKDIV output generates a clock frequency that is a predetermined fraction of the CLKIN frequency. The CLKDV\_DIVIDE attribute determines the factor used to divide the CLKIN frequency. The attribute can be set to various values as described in Table 17. The basic frequency synthesis outputs are described in Table 16. Their relative timing in the Low Frequency Mode is shown in Figure 22.

The CLK2X and CLK2X180 outputs are not available when operating in the High Frequency mode. See the description of the DLL\_FREQUENCY\_MODE attribute in Table 18.

## **Duty Cycle Correction of DLL Clock Outputs**

The CLK2X<sup>(1)</sup>, CLK2X180, and CLKDV<sup>(2)</sup> output signals ordinarily exhibit a 50% duty cycle—even if the incoming CLKIN signal has a different duty cycle. A 50% duty cycle means that the High and Low times of each clock cycle are equal. The DUTY\_CYCLE\_CORRECTION attribute determines whether or not duty cycle correction is applied to the CLK0, CLK90, CLK180 and CLK270 outputs. If DUTY\_CYCLE\_CORRECTION is set to TRUE, then the duty cycle of these four outputs is corrected to 50%. If DUTY\_CYCLE\_CORRECTION is set to FALSE, then these outputs exhibit the same duty cycle as the CLKIN signal. Figure 22 compares the characteristics of the DLL's output signals to those of the CLKIN signal.

<sup>1.</sup> The CLK2X output generates a 25% duty cycle clock at the same frequency as the CLKIN signal until the DLL has achieved lock.

<sup>2.</sup> The duty cycle of the CLKDV outputs may differ somewhat from 50% (i.e., the signal will be High for less than 50% of the period) when the CLKDV\_DIVIDE attribute is set to a non-integer value *and* the DLL is operating in the High Frequency mode.

# **XILINX**.

# Interconnect

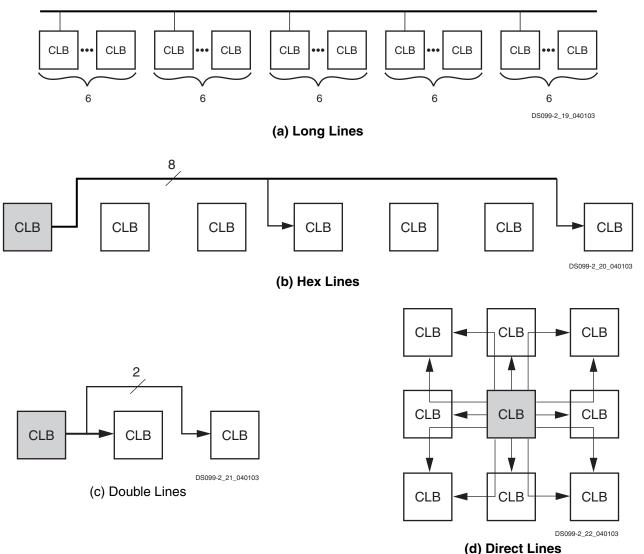

Interconnect (or routing) passes signals among the various functional elements of Spartan-3 devices. There are four kinds of interconnect: Long lines, Hex lines, Double lines, and Direct lines.

Long lines connect to one out of every six CLBs (see section [a] of Figure 25). Because of their low capacitance, these lines are well-suited for carrying high-frequency signals with minimal loading effects (e.g. skew). If all eight Global Clock Inputs are already committed and there remain additional clock signals to be assigned, Long lines serve as a good alternative.

Hex lines connect one out of every three CLBs (see section [b] of Figure 25). These lines fall between Long lines and Double lines in terms of capability: Hex lines approach the high-frequency characteristics of Long lines at the same time, offering greater connectivity.

Double lines connect to every other CLB (see section [c] of Figure 25). Compared to the types of lines already discussed, Double lines provide a higher degree of flexibility when making connections.

Direct lines afford any CLB direct access to neighboring CLBs (see section [d] of Figure 25). These lines are most often used to conduct a signal from a "source" CLB to a Double, Hex, or Long line and then from the longer interconnect back to a Direct line accessing a "destination" CLB.

For more details, refer to the "Using Interconnect" chapter in UG331.

(d) Direct L

Figure 25: Types of Interconnect

www.xilinx.com

# **E** XILINX.

Initial Spartan-3 FPGA mask revisions have a limit on how fast the V<sub>CCO</sub> supply can ramp. The minimum allowed V<sub>CCO</sub> ramp rate appears as  $T_{CCO}$  in Table 30, page 60. The minimum rate is affected by the package inductance. Consequently, the ball grid array and chip-scale packages (CP132, FT256, FG456, FG676, and FG900) allow a faster ramp rate than the quad-flat packages (VQ100, TQ144, and PQ208).

# **Configuration Data Retention, Brown-Out**

The FPGA's configuration data is stored in robust CMOS configuration latches. The data in these latches is retained even when the voltages drop to the minimum levels necessary to preserve RAM contents. This is specified in Table 31, page 60.

If, after configuration, the  $V_{CCAUX}$  or  $V_{CCINT}$  supply drops below its data retention voltage, clear the current device configuration using one of the following methods:

- Force the V<sub>CCAUX</sub> or V<sub>CCINT</sub> supply voltage below the minimum Power On Reset (POR) voltage threshold Table 29, page 59).

- Assert PROG\_B Low.

The POR circuit does not monitor the VCCO\_4 supply after configuration. Consequently, dropping the VCCO\_4 voltage does not reset the device by triggering a Power-On Reset (POR) event.

# No Internal Charge Pumps or Free-Running Oscillators

Some system applications are sensitive to sources of analog noise. Spartan-3 FPGA circuitry is fully static and does not employ internal charge pumps.

The CCLK configuration clock is active during the FPGA configuration process. After configuration completes, the CCLK oscillator is automatically disabled unless the Bitstream Generator (BitGen) option *Persist=Yes*. See Module 4: Table 80, page 125.

Spartan-3 FPGAs optionally support a featured called Digitally Controlled Impedance (DCI). When used in an application, the DCI logic uses an internal oscillator. The DCI logic is only enabled if the FPGA application specifies an I/O standard that requires DCI (LVDCI\_33, LVDCI\_25, etc.). If DCI is not used, the associated internal oscillator is also disabled.

In summary, unless an application uses the *Persist=Yes* option or specifies a DCI I/O standard, an FPGA with no external switching remains fully static.

## Table 34: Quiescent Supply Current Characteristics

| Symbol              | Description                                 | Device   | Typical <sup>(1)</sup> | Commercial<br>Maximum <sup>(1)</sup> | Industrial<br>Maximum <sup>(1)</sup> | Units |

|---------------------|---------------------------------------------|----------|------------------------|--------------------------------------|--------------------------------------|-------|

| I <sub>CCINTQ</sub> | Quiescent $V_{CCINT}$ supply current        | XC3S50   | 5                      | 24                                   | 31                                   | mA    |

|                     |                                             | XC3S200  | 10                     | 54                                   | 80                                   | mA    |

|                     |                                             | XC3S400  | 15                     | 110                                  | 157                                  | mA    |

|                     |                                             | XC3S1000 | 35                     | 160                                  | 262                                  | mA    |

|                     |                                             | XC3S1500 | 45                     | 260                                  | 332                                  | mA    |

|                     |                                             | XC3S2000 | 60                     | 360                                  | 470                                  | mA    |

|                     |                                             | XC3S4000 | 100                    | 450                                  | 810                                  | mA    |

|                     |                                             | XC3S5000 | 120                    | 600                                  | 870                                  | mA    |

| Iccoq               | Quiescent V <sub>CCO</sub> supply current   | XC3S50   | 1.5                    | 2.0                                  | 2.5                                  | mA    |

|                     |                                             | XC3S200  | 1.5                    | 3.0                                  | 3.5                                  | mA    |

|                     |                                             | XC3S400  | 1.5                    | 3.0                                  | 3.5                                  | mA    |

|                     |                                             | XC3S1000 | 2.0                    | 4.0                                  | 5.0                                  | mA    |

|                     |                                             | XC3S1500 | 2.5                    | 4.0                                  | 5.0                                  | mA    |

|                     |                                             | XC3S2000 | 3.0                    | 5.0                                  | 6.0                                  | mA    |

|                     |                                             | XC3S4000 | 3.5                    | 5.0                                  | 6.0                                  | mA    |

|                     |                                             | XC3S5000 | 3.5                    | 5.0                                  | 6.0                                  | mA    |

| I <sub>CCAUXQ</sub> | Quiescent V <sub>CCAUX</sub> supply current | XC3S50   | 7                      | 20                                   | 22                                   | mA    |

|                     |                                             | XC3S200  | 10                     | 30                                   | 33                                   | mA    |

|                     |                                             | XC3S400  | 15                     | 40                                   | 44                                   | mA    |

|                     |                                             | XC3S1000 | 20                     | 50                                   | 55                                   | mA    |

|                     |                                             | XC3S1500 | 35                     | 75                                   | 85                                   | mA    |

|                     |                                             | XC3S2000 | 45                     | 90                                   | 100                                  | mA    |

|                     |                                             | XC3S4000 | 55                     | 110                                  | 125                                  | mA    |

|                     |                                             | XC3S5000 | 70                     | 130                                  | 145                                  | mA    |

#### Notes:

- 1. The numbers in this table are based on the conditions set forth in Table 32. Quiescent supply current is measured with all I/O drivers in a high-impedance state and with all pull-up/pull-down resistors at the I/O pads disabled. Typical values are characterized using devices with typical processing at room temperature (T<sub>J</sub> of 25°C at V<sub>CCINT</sub> = 1.2V, V<sub>CCO</sub> = 3.3V, and V<sub>CCAUX</sub> = 2.5V). Maximum values are the production test limits measured for each device at the maximum specified junction temperature and at maximum voltage limits with V<sub>CCINT</sub> = 1.26V, V<sub>CCO</sub> = 3.465V, and V<sub>CCAUX</sub> = 2.625V. The FPGA is programmed with a "blank" configuration data file (i.e., a design with no functional elements instantiated). For conditions other than those described above, (e.g., a design including functional elements, the use of DCI standards, etc.), measured quiescent current levels may be different than the values in the table. Use the XPower Estimator or XPower Analyzer for more accurate estimates. See Note 2.

- 2. There are two recommended ways to estimate the total power consumption (quiescent plus dynamic) for a specific design: a) The <u>Spartan-3</u> <u>XPower Estimator</u> provides quick, approximate, typical estimates, and does not require a netlist of the design. b) XPower Analyzer, part of the Xilinx ISE development software, uses the FPGA netlist as input to provide more accurate maximum and typical estimates.

- The maximum numbers in this table also indicate the minimum current each power rail requires in order for the FPGA to power-on successfully, once all three rails are supplied. If V<sub>CCINT</sub> is applied before V<sub>CCAUX</sub>, there may be temporary additional I<sub>CCINT</sub> current until V<sub>CCAUX</sub> is applied. See Surplus I<sub>CCINT</sub> if V<sub>CCINT</sub> Applied before V<sub>CCAUX</sub>, page 54

#### Table 41: System-Synchronous Pin-to-Pin Setup and Hold Times for the IOB Input Path (Cont'd)

|                   |                                                                         |                                                      |          | Speed | Grade |       |

|-------------------|-------------------------------------------------------------------------|------------------------------------------------------|----------|-------|-------|-------|

| Symbol            | Description                                                             | Conditions                                           | Device   | -5    | -4    | Units |

|                   |                                                                         |                                                      |          | Min   | Min   |       |

| T <sub>PHFD</sub> | When writing to IFF, the time from                                      | LVCMOS25 <sup>(3)</sup> ,                            | XC3S50   | -0.98 | -0.93 | ns    |

|                   | the active transition at the Global<br>Clock pin to the point when data | IOBDELAY = IFD,<br>without DCM                       | XC3S200  | -0.40 | -0.35 | ns    |

|                   | must be held at the Input pin. The DCM is not in use. The Input         |                                                      | XC3S400  | -0.27 | -0.22 | ns    |

|                   |                                                                         | DCM is not in use. The Input<br>Delay is programmed. | XC3S1000 | -1.19 | -1.14 | ns    |

|                   |                                                                         |                                                      | XC3S1500 | -1.43 | -1.38 | ns    |

|                   |                                                                         |                                                      | XC3S2000 | -2.33 | -2.28 | ns    |

|                   |                                                                         | XC3S4000                                             | -2.47    | -2.42 | ns    |       |

|                   |                                                                         |                                                      | XC3S5000 | -2.66 | -2.61 | ns    |

#### Notes:

- 1. The numbers in this table are tested using the methodology presented in Table 48 and are based on the operating conditions set forth in Table 32 and Table 35.

- 2. This setup time requires adjustment whenever a signal standard other than LVCMOS25 is assigned to the Global Clock Input or the data Input. If this is true of the Global Clock Input, *subtract* the appropriate adjustment from Table 44. If this is true of the data Input, *add* the appropriate Input adjustment from the same table.

- 3. This hold time requires adjustment whenever a signal standard other than LVCMOS25 is assigned to the Global Clock Input or the data Input. If this is true of the Global Clock Input, *add* the appropriate Input adjustment from Table 44. If this is true of the data Input, *subtract* the appropriate Input adjustment from the same table. When the hold time is negative, it is possible to change the data before the clock's active edge.

- 4. DCM output jitter is included in all measurements.

#### Table 42: Setup and Hold Times for the IOB Input Path

|                      |                                                                                               | Conditions                |          | Speed Grade |      |       |

|----------------------|-----------------------------------------------------------------------------------------------|---------------------------|----------|-------------|------|-------|

| Symbol               | Description                                                                                   |                           | Device   | -5          | -4   | Units |

|                      |                                                                                               |                           |          | Min         | Min  |       |

| Setup Times          |                                                                                               | -                         | U        |             |      |       |

| T <sub>IOPICK</sub>  | Time from the setup of data at the Input pin                                                  | LVCMOS25 <sup>(2)</sup> , | XC3S50   | 1.65        | 1.89 | ns    |

|                      | to the active transition at the ICLK input of<br>the Input Flip-Flop (IFF). No Input Delay is | IOBDELAY = NONE           | XC3S200  | 1.37        | 1.57 | ns    |

|                      | programmed.                                                                                   |                           | XC3S400  | 1.37        | 1.57 | ns    |

|                      |                                                                                               |                           | XC3S1000 | 1.65        | 1.89 | ns    |

|                      |                                                                                               |                           | XC3S1500 | 1.65        | 1.89 | ns    |

|                      |                                                                                               |                           | XC3S2000 | 1.65        | 1.89 | ns    |

|                      |                                                                                               |                           | XC3S4000 | 1.73        | 1.99 | ns    |

|                      |                                                                                               |                           | XC3S5000 | 1.82        | 2.09 | ns    |

| T <sub>IOPICKD</sub> | Time from the setup of data at the Input pin                                                  | LVCMOS25 <sup>(2)</sup> , | XC3S50   | 4.39        | 5.04 | ns    |

|                      | to the active transition at the IFF's ICLK input. The Input Delay is programmed.              | IOBDELAY = IFD            | XC3S200  | 4.76        | 5.47 | ns    |

|                      |                                                                                               |                           | XC3S400  | 4.63        | 5.32 | ns    |

|                      |                                                                                               |                           | XC3S1000 | 5.02        | 5.76 | ns    |

|                      |                                                                                               |                           | XC3S1500 | 5.40        | 6.20 | ns    |

|                      |                                                                                               |                           | XC3S2000 | 6.68        | 7.68 | ns    |

|                      |                                                                                               |                           | XC3S4000 | 7.16        | 8.24 | ns    |

|                      |                                                                                               |                           | XC3S5000 | 7.33        | 8.42 | ns    |

www.xilinx.com

#### Table 69: Types of Pins on Spartan-3 FPGAs (Cont'd)

| Pin Type/<br>Color Code | Description                                                                                                                                                                                                                                                       | Pin Name                                                                                                                                                    |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VREF                    | Dual-purpose pin that is either a user-I/O pin or, along with all other VREF pins in the same bank, provides a reference voltage input for certain I/O standards. If used for a reference voltage within a bank, all VREF pins within the bank must be connected. | IO/VREF_#<br>IO_Lxxy_#/VREF_#                                                                                                                               |

| GND                     | Dedicated ground pin. The number of GND pins depends on the package used. All must be connected.                                                                                                                                                                  | GND                                                                                                                                                         |

| VCCAUX                  | Dedicated auxiliary power supply pin. The number of VCCAUX pins depends on the package used. All must be connected to +2.5V.                                                                                                                                      | VCCAUX                                                                                                                                                      |

| VCCINT                  | Dedicated internal core logic power supply pin. The number of VCCINT pins depends on the package used. All must be connected to +1.2V.                                                                                                                            | VCCINT                                                                                                                                                      |

| VCCO                    | Dedicated I/O bank, output buffer power supply pin. Along with other VCCO pins in the same bank, this pin supplies power to the output buffers within the I/O bank and sets the input threshold voltage for some I/O standards.                                   | VCCO_#<br>CP132 and TQ144 Packages Only:<br>VCCO_LEFT, VCCO_TOP,<br>VCCO_RIGHT, VCCO_BOTTOM                                                                 |

| GCLK                    | Dual-purpose pin that is either a user-I/O pin or an input to a specific global buffer input. Every package has eight dedicated GCLK pins.                                                                                                                        | IO_Lxxy_#/GCLK0,<br>IO_Lxxy_#/GCLK1,<br>IO_Lxxy_#/GCLK2,<br>IO_Lxxy_#/GCLK3,<br>IO_Lxxy_#/GCLK4,<br>IO_Lxxy_#/GCLK5,<br>IO_Lxxy_#/GCLK6,<br>IO_Lxxy_#/GCLK7 |

| N.C.                    | This package pin is not connected in this specific device/package combination but may be connected in larger devices in the same package.                                                                                                                         | N.C.                                                                                                                                                        |

#### Notes:

1. # = I/O bank number, an integer between 0 and 7.

I/Os with Lxxy\_# are part of a differential output pair. 'L' indicates differential output capability. The "xx" field is a two-digit integer, unique to each bank that identifies a differential pin-pair. The 'y' field is either 'P' for the true signal or 'N' for the inverted signal in the differential pair. The '#' field is the I/O bank number.

## **Pin Definitions**

Table 70 provides a brief description of each pin listed in the Spartan-3 FPGA pinout tables and package footprint diagrams. Pins are categorized by their pin type, as listed in Table 69. See Detailed, Functional Pin Descriptions for more information.

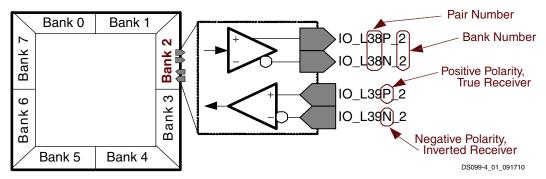

#### **Differential Pair Labeling**

A pin supports differential standards if the pin is labeled in the format "Lxxy\_#". The pin name suffix has the following significance. Figure 40 provides a specific example showing a differential input to and a differential output from Bank 2.

- 'L' indicates differential capability.

- "xx" is a two-digit integer, unique for each bank, that identifies a differential pin-pair.

- 'y' is replaced by 'P' for the true signal or 'N' for the inverted. These two pins form one differential pin-pair.

- '#' is an integer, 0 through 7, indicating the associated I/O bank.

If unused, these pins are in a high impedance state. The Bitstream generator option UnusedPin enables a pull-up or pull-down resistor on all unused I/O pins.

#### Behavior from Power-On through End of Configuration

During the configuration process, all pins that are not actively involved in the configuration process are in a high-impedance state. The CONFIG- and JTAG-type pins have an internal pull-up resistor to VCCAUX during configuration. For all other I/O pins, the HSWAP\_EN input determines whether or not pull-up resistors are activated during configuration. HSWAP\_EN = 0 enables the pull-up resistors. HSWAP\_EN = 1 disables the pull-up resistors allowing the pins to float, which is the desired state for hot-swap applications.

Figure 40: Differential Pair Labelling

## **DUAL Type: Dual-Purpose Configuration and I/O Pins**

These pins serve dual purposes. The user-I/O pins are temporarily borrowed during the configuration process to load configuration data into the FPGA. After configuration, these pins are then usually available as a user I/O in the application. If a pin is not applicable to the specific configuration mode—controlled by the mode select pins M2, M1, and M0—then the pin behaves as an I/O-type pin.

There are 12 dual-purpose configuration pins on every package, six of which are part of I/O Bank 4, the other six part of I/O Bank 5. Only a few of the pins in Bank 4 are used in the Serial configuration modes.

See Pin Behavior During Configuration, page 122.

#### **Serial Configuration Modes**

This section describes the dual-purpose pins used during either Master or Slave Serial mode. See Table 75 for Mode Select pin settings required for Serial modes. All such pins are in Bank 4 and powered by VCCO\_4.

In both the Master and Slave Serial modes, DIN is the serial configuration data input. The D1-D7 inputs are unused in serial mode and behave like general-purpose I/O pins.

In all the cases, the configuration data is synchronized to the rising edge of the CCLK clock signal.

The DIN, DOUT, and INIT\_B pins can be retained in the application to support reconfiguration by setting the Persist bitstream generation option. However, the serial modes do not support device readback.

#### HSWAP\_EN: Disable Pull-up Resistors During Configuration

As shown in Table 76, a Low on this asynchronous pin enables pull-up resistors on all user I/Os not actively involved in the configuration process, although only until device configuration completes. A High disables the pull-up resistors during configuration, which is the desired state for some applications.

The dedicated configuration CONFIG pins (CCLK, DONE, PROG\_B, HSWAP\_EN, M2, M1, M0), the JTAG pins (TDI, TMS, TCK, TDO) and the INIT\_B always have active pull-up resistors during configuration, regardless of the value on HSWAP\_EN.

After configuration, HSWAP\_EN becomes a "don't care" input and any pull-up resistors previously enabled by HSWAP\_EN are disabled. If a user I/O in the application requires a pull-up resistor after configuration, place a PULLUP primitive on the associated I/O pin or, for some pins, set the associated bitstream generator option.

#### Table 76: HSWAP\_EN Encoding

| HSWAP_EN                                                                                                                                                       | Function                                                     |  |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|--|--|--|--|--|

| During Config                                                                                                                                                  | During Configuration                                         |  |  |  |  |  |

| 0 Enable pull-up resistors on all pins not actively involved in the configuration process. Pull-ups are only active unticonfiguration completes. See Table 79. |                                                              |  |  |  |  |  |

| 1                                                                                                                                                              | No pull-up resistors during configuration.                   |  |  |  |  |  |

| After Configuration, User Mode                                                                                                                                 |                                                              |  |  |  |  |  |

| Х                                                                                                                                                              | This pin has no function except during device configuration. |  |  |  |  |  |

#### Notes:

1. X = don't care, either 0 or 1.

The Bitstream generator option HswapenPin determines whether a pull-up resistor to VCCAUX, a pull-down resistor, or no resistor is present on HSWAP\_EN after configuration.

## **JTAG: Dedicated JTAG Port Pins**

#### Table 77: JTAG Pin Descriptions

| Pin Name | Direction | Description                                                                                                                                                                                                                                                                              | Bitstream Generation Option                                                                                                |

|----------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| ТСК      | Input     | <b>Test Clock:</b> The TCK clock signal synchronizes all boundary scan operations on its rising edge.                                                                                                                                                                                    | The BitGen option <b>TckPin</b> determines whether a pull-up resistor, pull-down resistor or no resistor is present.       |

| TDI      | Input     | <b>Test Data Input:</b> TDI is the serial data input for all JTAG instruction and data registers. This input is sampled on the rising edge of TCK.                                                                                                                                       | The BitGen option <b>TdiPin</b> determines<br>whether a pull-up resistor, pull-down<br>resistor or no resistor is present. |

| TMS      | Input     | <b>Test Mode Select:</b> The TMS input controls the sequence of states through which the JTAG TAP state machine passes. This input is sampled on the rising edge of TCK.                                                                                                                 | The BitGen option <b>TmsPin</b> determines whether a pull-up resistor, pull-down resistor or no resistor is present.       |

| TDO      | Output    | <b>Test Data Output:</b> The TDO pin is the data output for all JTAG instruction and data registers. This output is sampled on the rising edge of TCK. The TDO output is an active totem-pole driver and is not like the open-collector TDO output on Virtex <sup>®</sup> -II Pro FPGAs. | The BitGen option <b>TdoPin</b> determines<br>whether a pull-up resistor, pull-down<br>resistor or no resistor is present. |

These pins are dedicated connections to the four-wire IEEE 1532/IEEE 1149.1 JTAG port, shown in Figure 43 and described in Table 77. The JTAG port is used for boundary-scan testing, device configuration, application debugging, and possibly an additional serial port for the application. These pins are dedicated and are not available as user-I/O pins. Every package has four dedicated JTAG pins and these pins are powered by the +2.5V VCCAUX supply.

For additional information on JTAG configuration, see Boundary-Scan (JTAG) Mode, page 50.

# TQ144: 144-lead Thin Quad Flat Package

The XC3S50, the XC3S200, and the XC3S400 are available in the 144-lead thin quad flat package, TQ144. All devices share a common footprint for this package as shown in Table 91 and Figure 46.

The TQ144 package only has four separate VCCO inputs, unlike the BGA packages, which have eight separate VCCO inputs. The TQ144 package has a separate VCCO input for the top, bottom, left, and right. However, there are still eight separate I/O banks, as shown in Table 91 and Figure 46. Banks 0 and 1 share the VCCO\_TOP input, Banks 2 and 3 share the VCCO\_RIGHT input, Banks 4 and 5 share the VCCO\_BOTTOM input, and Banks 6 and 7 share the VCCO\_LEFT input.

All the package pins appear in Table 91 and are sorted by bank number, then by pin name. Pairs of pins that form a differential I/O pair appear together in the table. The table also shows the pin number for each pin and the pin type, as defined earlier.

An electronic version of this package pinout table and footprint diagram is available for download from the Xilinx website at http://www.xilinx.com/support/documentation/data\_sheets/s3\_pin.zip.

## **Pinout Table**

| Bank | XC3S50, XC3S200,<br>XC3S400 Pin Name | TQ144 Pin<br>Number | Туре |

|------|--------------------------------------|---------------------|------|

| 0    | IO_L01N_0/VRP_0                      | P141                | DCI  |

| 0    | IO_L01P_0/VRN_0                      | P140                | DCI  |

| 0    | IO_L27N_0                            | P137                | I/O  |

| 0    | IO_L27P_0                            | P135                | I/O  |

| 0    | IO_L30N_0                            | P132                | I/O  |

| 0    | IO_L30P_0                            | P131                | I/O  |

| 0    | IO_L31N_0                            | P130                | I/O  |

| 0    | IO_L31P_0/VREF_0                     | P129                | VREF |

| 0    | IO_L32N_0/GCLK7                      | P128                | GCLK |

| 0    | IO_L32P_0/GCLK6                      | P127                | GCLK |

| 1    | Ю                                    | P116                | I/O  |

| 1    | IO_L01N_1/VRP_1                      | P113                | DCI  |

| 1    | IO_L01P_1/VRN_1                      | P112                | DCI  |

| 1    | IO_L28N_1                            | P119                | I/O  |

| 1    | IO_L28P_1                            | P118                | I/O  |

| 1    | IO_L31N_1/VREF_1                     | P123                | VREF |

| 1    | IO_L31P_1                            | P122                | I/O  |

| 1    | IO_L32N_1/GCLK5                      | P125                | GCLK |

| 1    | IO_L32P_1/GCLK4                      | P124                | GCLK |

| 2    | IO_L01N_2/VRP_2                      | P108                | DCI  |

| 2    | IO_L01P_2/VRN_2                      | P107                | DCI  |

| 2    | IO_L20N_2                            | P105                | I/O  |

| 2    | IO_L20P_2                            | P104                | I/O  |

| 2    | IO_L21N_2                            | P103                | I/O  |

| 2    | IO_L21P_2                            | P102                | I/O  |

| 2    | IO_L22N_2                            | P100                | I/O  |

| 2    | IO_L22P_2                            | P99                 | I/O  |

Table 91: TQ144 Package Pinout

#### Table 93: PQ208 Package Pinout (Cont'd)

| Bank | XC3S50<br>Pin Name | XC3S200, XC3S400<br>Pin Names | PQ208 Pin<br>Number | Туре |

|------|--------------------|-------------------------------|---------------------|------|

| 1    | IO_L10N_1/VREF_1   | IO_L10N_1/VREF_1              | P166                | VREF |

| 1    | IO_L10P_1          | IO_L10P_1                     | P165                | I/O  |

| 1    | IO_L27N_1          | IO_L27N_1                     | P169                | I/O  |

| 1    | IO_L27P_1          | IO_L27P_1                     | P168                | I/O  |

| 1    | IO_L28N_1          | IO_L28N_1                     | P172                | I/O  |

| 1    | IO_L28P_1          | IO_L28P_1                     | P171                | I/O  |

| 1    | IO_L31N_1/VREF_1   | IO_L31N_1/VREF_1              | P178                | VREF |

| 1    | IO_L31P_1          | IO_L31P_1                     | P176                | I/O  |

| 1    | IO_L32N_1/GCLK5    | IO_L32N_1/GCLK5               | P181                | GCLK |

| 1    | IO_L32P_1/GCLK4    | IO_L32P_1/GCLK4               | P180                | GCLK |

| 1    | VCCO_1             | VCCO_1                        | P164                | VCCO |

| 1    | VCCO_1             | VCCO_1                        | P177                | VCCO |

| 2    | N.C. (�)           | IO/VREF_2                     | P154                | VREF |

| 2    | IO_L01N_2/VRP_2    | IO_L01N_2/VRP_2               | P156                | DCI  |

| 2    | IO_L01P_2/VRN_2    | IO_L01P_2/VRN_2               | P155                | DCI  |

| 2    | IO_L19N_2          | IO_L19N_2                     | P152                | I/O  |

| 2    | IO_L19P_2          | IO_L19P_2                     | P150                | I/O  |

| 2    | IO_L20N_2          | IO_L20N_2                     | P149                | I/O  |

| 2    | IO_L20P_2          | IO_L20P_2                     | P148                | I/O  |

| 2    | IO_L21N_2          | IO_L21N_2                     | P147                | I/O  |

| 2    | IO_L21P_2          | IO_L21P_2                     | P146                | I/O  |

| 2    | IO_L22N_2          | IO_L22N_2                     | P144                | I/O  |

| 2    | IO_L22P_2          | IO_L22P_2                     | P143                | I/O  |

| 2    | IO_L23N_2/VREF_2   | IO_L23N_2/VREF_2              | P141                | VREF |

| 2    | IO_L23P_2          | IO_L23P_2                     | P140                | I/O  |

| 2    | IO_L24N_2          | IO_L24N_2                     | P139                | I/O  |

| 2    | IO_L24P_2          | IO_L24P_2                     | P138                | I/O  |

| 2    | N.C. (�)           | IO_L39N_2                     | P137                | I/O  |

| 2    | N.C. (�)           | IO_L39P_2                     | P135                | I/O  |

| 2    | IO_L40N_2          | IO_L40N_2                     | P133                | I/O  |

| 2    | IO_L40P_2/VREF_2   | IO_L40P_2/VREF_2              | P132                | VREF |

| 2    | VCCO_2             | VCCO_2                        | P136                | VCCO |

| 2    | VCCO_2             | VCCO_2                        | P153                | VCCO |

| 3    | IO_L01N_3/VRP_3    | IO_L01N_3/VRP_3               | P107                | DCI  |

| 3    | IO_L01P_3/VRN_3    | IO_L01P_3/VRN_3               | P106                | DCI  |

| 3    | N.C. (�)           | IO_L17N_3                     | P109                | I/O  |

| 3    | N.C. (�)           | IO_L17P_3/VREF_3              | P108                | VREF |

| 3    | IO_L19N_3          | IO_L19N_3                     | P113                | I/O  |

| 3    | IO_L19P_3          | IO_L19P_3                     | P111                | I/O  |

| 3    | IO_L20N_3          | IO_L20N_3                     | P115                | I/O  |

## Table 98: FG320 Package Pinout (Cont'd)

| Bank | XC3S400, XC3S1000, XC3S1500<br>Pin Name | FG320<br>Pin Number | Туре |

|------|-----------------------------------------|---------------------|------|

| 6    | IO_L01P_6/VRN_6                         | T2                  | DCI  |

| 6    | IO_L16N_6                               | U1                  | I/O  |

| 6    | IO_L16P_6                               | T1                  | I/O  |

| 6    | IO_L17N_6                               | R2                  | I/O  |

| 6    | IO_L17P_6/VREF_6                        | R1                  | VREF |

| 6    | IO_L19N_6                               | R3                  | I/O  |

| 6    | IO_L19P_6                               | P3                  | I/O  |

| 6    | IO_L20N_6                               | P2                  | I/O  |

| 6    | IO_L20P_6                               | P1                  | I/O  |

| 6    | IO_L21N_6                               | N4                  | I/O  |

| 6    | IO_L21P_6                               | P4                  | I/O  |

| 6    | IO_L22N_6                               | N5                  | I/O  |

| 6    | IO_L22P_6                               | M5                  | I/O  |

| 6    | IO_L23N_6                               | M3                  | I/O  |

| 6    | IO_L23P_6                               | M4                  | I/O  |

| 6    | IO_L24N_6/VREF_6                        | N2                  | VREF |

| 6    | IO_L24P_6                               | M1                  | I/O  |

| 6    | IO_L27N_6                               | L6                  | I/O  |

| 6    | IO_L27P_6                               | L5                  | I/O  |

| 6    | IO_L34N_6/VREF_6                        | L3                  | VREF |

| 6    | IO_L34P_6                               | L4                  | I/O  |

| 6    | IO_L35N_6                               | L2                  | I/O  |

| 6    | IO_L35P_6                               | L1                  | I/O  |

| 6    | IO_L39N_6                               | K5                  | I/O  |

| 6    | IO_L39P_6                               | K4                  | I/O  |

| 6    | IO_L40N_6                               | K1                  | I/O  |

| 6    | IO_L40P_6/VREF_6                        | K2                  | VREF |

| 6    | VCCO_6                                  | K7                  | VCCO |

| 6    | VCCO_6                                  | L7                  | VCCO |

| 6    | VCCO_6                                  | N3                  | VCCO |

| 7    | Ю                                       | J6                  | I/O  |

| 7    | IO_L01N_7/VRP_7                         | C3                  | DCI  |

| 7    | IO_L01P_7/VRN_7                         | C2                  | DCI  |

| 7    | IO_L16N_7                               | C1                  | I/O  |

| 7    | IO_L16P_7/VREF_7                        | B1                  | VREF |

| 7    | IO_L17N_7                               | D1                  | I/O  |

| 7    | IO_L17P_7                               | D2                  | I/O  |

| 7    | IO_L19N_7/VREF_7                        | E3                  | VREF |

| 7    | IO_L19P_7                               | D3                  | I/O  |

| 7    | IO_L20N_7                               | E2                  | I/O  |

#### Table 100: FG456 Package Pinout (Cont'd)

| Bank | 3S400<br>Pin Name | 3S1000, 3S1500, 3S2000<br>Pin Name | FG456<br>Pin Number | Туре |

|------|-------------------|------------------------------------|---------------------|------|

| 0    | N.C. (�)          | IO_L22N_0                          | E8                  | I/O  |

| 0    | N.C. (�)          | IO_L22P_0                          | D8                  | I/O  |

| 0    | IO_L24N_0         | IO_L24N_0                          | B8                  | I/O  |

| 0    | IO_L24P_0         | IO_L24P_0                          | A8                  | I/O  |

| 0    | IO_L25N_0         | IO_L25N_0                          | F9                  | I/O  |

| 0    | IO_L25P_0         | IO_L25P_0                          | E9                  | I/O  |

| 0    | IO_L27N_0         | IO_L27N_0                          | B9                  | I/O  |

| 0    | IO_L27P_0         | IO_L27P_0                          | A9                  | I/O  |

| 0    | IO_L28N_0         | IO_L28N_0                          | F10                 | I/O  |

| 0    | IO_L28P_0         | IO_L28P_0                          | E10                 | I/O  |

| 0    | IO_L29N_0         | IO_L29N_0                          | C10                 | I/O  |

| 0    | IO_L29P_0         | IO_L29P_0                          | B10                 | I/O  |

| 0    | IO_L30N_0         | IO_L30N_0                          | F11                 | I/O  |

| 0    | IO_L30P_0         | IO_L30P_0                          | E11                 | I/O  |

| 0    | IO_L31N_0         | IO_L31N_0                          | D11                 | I/O  |

| 0    | IO_L31P_0/VREF_0  | IO_L31P_0/VREF_0                   | C11                 | VREF |

| 0    | IO_L32N_0/GCLK7   | IO_L32N_0/GCLK7                    | B11                 | GCLK |

| 0    | IO_L32P_0/GCLK6   | IO_L32P_0/GCLK6                    | A11                 | GCLK |

| 0    | VCCO_0            | VCCO_0                             | C8                  | VCCO |

| 0    | VCCO_0            | VCCO_0                             | F8                  | VCCO |

| 0    | VCCO_0            | VCCO_0                             | G9                  | VCCO |

| 0    | VCCO_0            | VCCO_0                             | G10                 | VCCO |

| 0    | VCCO_0            | VCCO_0                             | G11                 | VCCO |

| 1    | 10                | Ю                                  | A12                 | I/O  |

| 1    | 10                | Ю                                  | E16                 | I/O  |

| 1    | IO                | Ю                                  | F12                 | I/O  |

| 1    | 10                | Ю                                  | F13                 | I/O  |

| 1    | 10                | Ю                                  | F16                 | I/O  |

| 1    | 10                | Ю                                  | F17                 | I/O  |

| 1    | IO/VREF_1         | IO/VREF_1                          | E13                 | VREF |

| 1    | N.C. (�)          | IO/VREF_1                          | F14                 | VREF |

| 1    | IO_L01N_1/VRP_1   | IO_L01N_1/VRP_1                    | C19                 | DCI  |

| 1    | IO_L01P_1/VRN_1   | IO_L01P_1/VRN_1                    | B20                 | DCI  |

| 1    | IO_L06N_1/VREF_1  | IO_L06N_1/VREF_1                   | A19                 | VREF |

| 1    | IO_L06P_1         | IO_L06P_1                          | B19                 | I/O  |

| 1    | IO_L09N_1         | IO_L09N_1                          | C18                 | I/O  |

| 1    | IO_L09P_1         | IO_L09P_1                          | D18                 | I/O  |

| 1    | IO_L10N_1/VREF_1  | IO_L10N_1/VREF_1                   | A18                 | VREF |

| 1    | IO_L10P_1         | IO_L10P_1                          | B18                 | I/O  |

| 1    | IO_L15N_1         | IO_L15N_1                          | D17                 | I/O  |

## Table 100: FG456 Package Pinout (Cont'd)

| Bank | 3S400<br>Pin Name | 3S1000, 3S1500, 3S2000<br>Pin Name | FG456<br>Pin Number | Туре |

|------|-------------------|------------------------------------|---------------------|------|

| 7    | IO_L23N_7         | IO_L23N_7                          | F2                  | I/O  |

| 7    | IO_L23P_7         | IO_L23P_7                          | F3                  | I/O  |

| 7    | IO_L24N_7         | IO_L24N_7                          | H5                  | I/O  |

| 7    | IO_L24P_7         | IO_L24P_7                          | G5                  | I/O  |

| 7    | N.C. (�)          | IO_L26N_7                          | G3                  | I/O  |

| 7    | N.C. (�)          | IO_L26P_7                          | G4                  | I/O  |

| 7    | IO_L27N_7         | IO_L27N_7                          | G1                  | I/O  |

| 7    | IO_L27P_7/VREF_7  | IO_L27P_7/VREF_7                   | G2                  | VREF |

| 7    | N.C. (�)          | IO_L28N_7                          | H1                  | I/O  |

| 7    | N.C. (�)          | IO_L28P_7                          | H2                  | I/O  |

| 7    | N.C. (�)          | IO_L29N_7                          | J4                  | I/O  |

| 7    | N.C. (�)          | IO_L29P_7                          | H4                  | I/O  |

| 7    | N.C. (�)          | IO_L31N_7                          | J5                  | I/O  |

| 7    | N.C. (�)          | IO_L31P_7                          | J6                  | I/O  |

| 7    | N.C. (�)          | IO_L32N_7                          | J1                  | I/O  |

| 7    | N.C. (�)          | IO_L32P_7                          | J2                  | I/O  |

| 7    | N.C. (�)          | IO_L33N_7                          | K5                  | I/O  |

| 7    | N.C. (�)          | IO_L33P_7                          | K6                  | I/O  |

| 7    | IO_L34N_7         | IO_L34N_7                          | K3                  | I/O  |

| 7    | IO_L34P_7         | IO_L34P_7                          | K4                  | I/O  |

| 7    | IO_L35N_7         | IO_L35N_7                          | K1                  | I/O  |

| 7    | IO_L35P_7         | IO_L35P_7                          | K2                  | I/O  |

| 7    | IO_L38N_7         | IO_L38N_7                          | L5                  | I/O  |

| 7    | IO_L38P_7         | IO_L38P_7                          | L6                  | I/O  |

| 7    | IO_L39N_7         | IO_L39N_7                          | L3                  | I/O  |

| 7    | IO_L39P_7         | IO_L39P_7                          | L4                  | I/O  |

| 7    | IO_L40N_7/VREF_7  | IO_L40N_7/VREF_7                   | L1                  | VREF |

| 7    | IO_L40P_7         | IO_L40P_7                          | L2                  | I/O  |

| 7    | VCCO_7            | VCCO_7                             | H3                  | VCCO |

| 7    | VCCO_7            | VCCO_7                             | H6                  | VCCO |

| 7    | VCCO_7            | VCCO_7                             | J7                  | VCCO |

| 7    | VCCO_7            | VCCO_7                             | K7                  | VCCO |

| 7    | VCCO_7            | VCCO_7                             | L7                  | VCCO |

| N/A  | GND               | GND                                | A1                  | GND  |

| N/A  | GND               | GND                                | A22                 | GND  |

| N/A  | GND               | GND                                | AA2                 | GND  |

| N/A  | GND               | GND                                | AA21                | GND  |

| N/A  | GND               | GND                                | AB1                 | GND  |

| N/A  | GND               | GND                                | AB22                | GND  |

| N/A  | GND               | GND                                | B2                  | GND  |

#### Table 103: FG676 Package Pinout (Cont'd)

| Bank | XC3S1000<br>Pin Name | XC3S1500<br>Pin Name | XC3S2000<br>Pin Name | XC3S4000<br>Pin Name | XC3S5000<br>Pin Name | FG676 Pin<br>Number | Туре |

|------|----------------------|----------------------|----------------------|----------------------|----------------------|---------------------|------|

| 6    | IO_L20N_6            | IO_L20N_6            | IO_L20N_6            | IO_L20N_6            | IO_L20N_6            | V7                  | I/O  |

| 6    | IO_L20P_6            | IO_L20P_6            | IO_L20P_6            | IO_L20P_6            | IO_L20P_6            | U7                  | I/O  |

| 6    | IO_L21N_6            | IO_L21N_6            | IO_L21N_6            | IO_L21N_6            | IO_L21N_6            | V5                  | I/O  |

| 6    | IO_L21P_6            | IO_L21P_6            | IO_L21P_6            | IO_L21P_6            | IO_L21P_6            | V4                  | I/O  |

| 6    | IO_L22N_6            | IO_L22N_6            | IO_L22N_6            | IO_L22N_6            | IO_L22N_6            | V3                  | I/O  |

| 6    | IO_L22P_6            | IO_L22P_6            | IO_L22P_6            | IO_L22P_6            | IO_L22P_6            | V2                  | I/O  |

| 6    | IO_L23N_6            | IO_L23N_6            | IO_L23N_6            | IO_L23N_6            | IO_L23N_6            | U6                  | I/O  |

| 6    | IO_L23P_6            | IO_L23P_6            | IO_L23P_6            | IO_L23P_6            | IO_L23P_6            | U5                  | I/O  |

| 6    | IO_L24N_6/VREF_6     | IO_L24N_6/VREF_6     | IO_L24N_6/VREF_6     | IO_L24N_6/VREF_6     | IO_L24N_6/VREF_6     | U4                  | VREF |

| 6    | IO_L24P_6            | IO_L24P_6            | IO_L24P_6            | IO_L24P_6            | IO_L24P_6            | U3                  | I/O  |

| 6    | IO_L26N_6            | IO_L26N_6            | IO_L26N_6            | IO_L26N_6            | IO_L26N_6            | U2                  | I/O  |

| 6    | IO_L26P_6            | IO_L26P_6            | IO_L26P_6            | IO_L26P_6            | IO_L26P_6            | U1                  | I/O  |

| 6    | IO_L27N_6            | IO_L27N_6            | IO_L27N_6            | IO_L27N_6            | IO_L27N_6            | Т8                  | I/O  |

| 6    | IO_L27P_6            | IO_L27P_6            | IO_L27P_6            | IO_L27P_6            | IO_L27P_6            | T7                  | I/O  |

| 6    | IO_L28N_6            | IO_L28N_6            | IO_L28N_6            | IO_L28N_6            | IO_L28N_6            | Т6                  | I/O  |

| 6    | IO_L28P_6            | IO_L28P_6            | IO_L28P_6            | IO_L28P_6            | IO_L28P_6            | T5                  | I/O  |

| 6    | IO_L29N_6            | IO_L29N_6            | IO_L29N_6            | IO_L29N_6            | IO_L29N_6            | T2                  | I/O  |

| 6    | IO_L29P_6            | IO_L29P_6            | IO_L29P_6            | IO_L29P_6            | IO_L29P_6            | T1                  | I/O  |

| 6    | IO_L31N_6            | IO_L31N_6            | IO_L31N_6            | IO_L31N_6            | IO_L31N_6            | R8                  | I/O  |

| 6    | IO_L31P_6            | IO_L31P_6            | IO_L31P_6            | IO_L31P_6            | IO_L31P_6            | R7                  | I/O  |

| 6    | IO_L32N_6            | IO_L32N_6            | IO_L32N_6            | IO_L32N_6            | IO_L32N_6            | R6                  | I/O  |

| 6    | IO_L32P_6            | IO_L32P_6            | IO_L32P_6            | IO_L32P_6            | IO_L32P_6            | R5                  | I/O  |

| 6    | IO_L33N_6            | IO_L33N_6            | IO_L33N_6            | IO_L33N_6            | IO_L33N_6            | T4                  | I/O  |

| 6    | IO_L33P_6            | IO_L33P_6            | IO_L33P_6            | IO_L33P_6            | IO_L33P_6            | R3                  | I/O  |

| 6    | IO_L34N_6/VREF_6     | IO_L34N_6/VREF_6     | IO_L34N_6/VREF_6     | IO_L34N_6/VREF_6     | IO_L34N_6/VREF_6     | R2                  | VREF |

| 6    | IO_L34P_6            | IO_L34P_6            | IO_L34P_6            | IO_L34P_6            | IO_L34P_6            | R1                  | I/O  |

| 6    | IO_L35N_6            | IO_L35N_6            | IO_L35N_6            | IO_L35N_6            | IO_L35N_6            | P8                  | I/O  |

| 6    | IO_L35P_6            | IO_L35P_6            | IO_L35P_6            | IO_L35P_6            | IO_L35P_6            | P7                  | I/O  |

| 6    | IO_L38N_6            | IO_L38N_6            | IO_L38N_6            | IO_L38N_6            | IO_L38N_6            | P6                  | I/O  |

| 6    | IO_L38P_6            | IO_L38P_6            | IO_L38P_6            | IO_L38P_6            | IO_L38P_6            | P5                  | I/O  |

| 6    | IO_L39N_6            | IO_L39N_6            | IO_L39N_6            | IO_L39N_6            | IO_L39N_6            | P4                  | I/O  |

| 6    | IO_L39P_6            | IO_L39P_6            | IO_L39P_6            | IO_L39P_6            | IO_L39P_6            | P3                  | I/O  |

| 6    | IO_L40N_6            | IO_L40N_6            | IO_L40N_6            | IO_L40N_6            | IO_L40N_6            | P2                  | I/O  |

| 6    | IO_L40P_6/VREF_6     | IO_L40P_6/VREF_6     | IO_L40P_6/VREF_6     | IO_L40P_6/VREF_6     | IO_L40P_6/VREF_6     | P1                  | VREF |

| 6    | VCCO_6               | VCCO_6               | VCCO_6               | VCCO_6               | VCCO_6               | P9                  | VCCO |

| 6    | VCCO_6               | VCCO_6               | VCCO_6               | VCCO_6               | VCCO_6               | P10                 | VCCO |

| 6    | VCCO_6               | VCCO_6               | VCCO_6               | VCCO_6               | VCCO_6               | R9                  | VCCO |

| 6    | VCCO_6               | VCCO_6               | VCCO_6               | VCCO_6               | VCCO_6               | Т3                  | VCCO |

| 6    | VCCO_6               | VCCO_6               | VCCO_6               | VCCO_6               | VCCO_6               | Т9                  | VCCO |

| 6    | VCCO_6               | VCCO_6               | VCCO_6               | VCCO_6               | VCCO_6               | U8                  | VCCO |

| 6    | VCCO_6               | VCCO_6               | VCCO_6               | VCCO_6               | VCCO_6               | V8                  | VCCO |

| 6    | VCCO_6               | VCCO_6               | VCCO_6               | VCCO_6               | VCCO_6               | Y3                  | VCCO |

| 7    | IO_L01N_7/VRP_7      | IO_L01N_7/VRP_7      | IO_L01N_7/VRP_7      | IO_L01N_7/VRP_7      | IO_L01N_7/VRP_7      | F5                  | DCI  |

#### Table 107: FG900 Package Pinout (Cont'd)

| Bank | XC3S2000<br>Pin Name | XC3S4000, XC3S5000<br>Pin Name | FG900 Pin<br>Number | Туре |

|------|----------------------|--------------------------------|---------------------|------|

| 1    | IO_L25P_1            | IO_L25P_1                      | D19                 | I/O  |

| 1    | IO_L26N_1            | IO_L26N_1                      | A19                 | I/O  |

| 1    | IO_L26P_1            | IO_L26P_1                      | B19                 | I/O  |

| 1    | IO_L27N_1            | IO_L27N_1                      | F17                 | I/O  |

| 1    | IO_L27P_1            | IO_L27P_1                      | G17                 | I/O  |

| 1    | IO_L28N_1            | IO_L28N_1                      | B17                 | I/O  |

| 1    | IO_L28P_1            | IO_L28P_1                      | C17                 | I/O  |

| 1    | IO_L29N_1            | IO_L29N_1                      | J16                 | I/O  |

| 1    | IO_L29P_1            | IO_L29P_1                      | K16                 | I/O  |

| 1    | IO_L30N_1            | IO_L30N_1                      | G16                 | I/O  |

| 1    | IO_L30P_1            | IO_L30P_1                      | H16                 | I/O  |

| 1    | IO_L31N_1/VREF_1     | IO_L31N_1/VREF_1               | D16                 | VREF |

| 1    | IO_L31P_1            | IO_L31P_1                      | E16                 | I/O  |

| 1    | IO_L32N_1/GCLK5      | IO_L32N_1/GCLK5                | B16                 | GCLK |

| 1    | IO_L32P_1/GCLK4      | IO_L32P_1/GCLK4                | C16                 | GCLK |

| 1    | N.C. (♦)             | IO_L37N_1                      | H18                 | I/O  |

| 1    | N.C. (♦)             | IO_L37P_1                      | J18                 | I/O  |

| 1    | N.C. (♦)             | IO_L38N_1                      | D18                 | I/O  |

| 1    | N.C. (♦)             | IO_L38P_1                      | E18                 | I/O  |

| 1    | N.C. (♦)             | IO_L39N_1                      | A18                 | I/O  |

| 1    | N.C. (♦)             | IO_L39P_1                      | B18                 | I/O  |

| 1    | N.C. (�)             | IO_L40N_1                      | K17                 | I/O  |

| 1    | N.C. (♦)             | IO_L40P_1                      | K18                 | I/O  |

| 1    | VCCO_1               | VCCO_1                         | L17                 | VCCO |

| 1    | VCCO_1               | VCCO_1                         | C18                 | VCCO |

| 1    | VCCO_1               | VCCO_1                         | G18                 | VCCO |

| 1    | VCCO_1               | VCCO_1                         | L18                 | VCCO |

| 1    | VCCO_1               | VCCO_1                         | L19                 | VCCO |

| 1    | VCCO_1               | VCCO_1                         | J20                 | VCCO |

| 1    | VCCO_1               | VCCO_1                         | C22                 | VCCO |

| 1    | VCCO_1               | VCCO_1                         | G22                 | VCCO |

| 1    | VCCO_1               | VCCO_1                         | E24                 | VCCO |

| 1    | VCCO_1               | VCCO_1                         | C26                 | VCCO |

| 2    | IO                   | IO                             | J25                 | I/O  |

| 2    | IO_L01N_2/VRP_2      | IO_L01N_2/VRP_2                | C29                 | DCI  |

| 2    | IO_L01P_2/VRN_2      | IO_L01P_2/VRN_2                | C30                 | DCI  |

| 2    | IO_L02N_2            | IO_L02N_2                      | D27                 | I/O  |

| 2    | IO_L02P_2            | IO_L02P_2                      | D28                 | I/O  |

| 2    | IO_L03N_2/VREF_2     | IO_L03N_2/VREF_2               | D29                 | VREF |

| 2    | IO_L03P_2            | IO_L03P_2                      | D30                 | I/O  |

#### Table 107: FG900 Package Pinout (Cont'd)

| Bank XC3S2000<br>Pin Name |        | XC3S4000, XC3S5000<br>Pin Name | FG900 Pin<br>Number | Туре |  |

|---------------------------|--------|--------------------------------|---------------------|------|--|

| 7                         | VCCO_7 | VCCO_7                         | N3                  | VCCO |  |

| 7                         | VCCO_7 | VCCO_7                         | G5                  | VCCO |  |

| 7                         | VCCO_7 | VCCO_7                         | J7                  | VCCO |  |

| 7                         | VCCO_7 | VCCO_7                         | N7                  | VCCO |  |

| 7                         | VCCO_7 | VCCO_7                         | L9                  | VCCO |  |

| 7                         | VCCO_7 | VCCO_7                         | M11                 | VCCO |  |

| 7                         | VCCO_7 | VCCO_7                         | N11                 | VCCO |  |

| 7                         | VCCO_7 | VCCO_7                         | P11                 | VCCO |  |

| N/A                       | GND    | GND                            | A1                  | GND  |  |

| N/A                       | GND    | GND                            | B1                  | GND  |  |

| N/A                       | GND    | GND                            | F1                  | GND  |  |

| N/A                       | GND    | GND                            | K1                  | GND  |  |

| N/A                       | GND    | GND                            | P1                  | GND  |  |

| N/A                       | GND    | GND                            | U1                  | GND  |  |

| N/A                       | GND    | GND                            | AA1                 | GND  |  |

| N/A                       | GND    | GND                            | AE1                 | GND  |  |

| N/A                       | GND    | GND                            | AJ1                 | GND  |  |

| N/A                       | GND    | GND                            | AK1                 | GND  |  |

| N/A                       | GND    | GND                            | A2                  | GND  |  |

| N/A                       | GND    | GND                            | B2                  | GND  |  |

| N/A                       | GND    | GND                            | AJ2                 | GND  |  |

| N/A                       | GND    | GND                            | E5                  | GND  |  |

| N/A                       | GND    | GND                            | K5                  | GND  |  |

| N/A                       | GND    | GND                            | P5                  | GND  |  |

| N/A                       | GND    | GND                            | U5                  | GND  |  |

| N/A                       | GND    | GND                            | AA5                 | GND  |  |

| N/A                       | GND    | GND                            | AF5                 | GND  |  |

| N/A                       | GND    | GND                            | A6                  | GND  |  |

| N/A                       | GND    | GND                            | AK6                 | GND  |  |

| N/A                       | GND    | GND                            | K8                  | GND  |  |

| N/A                       | GND    | GND                            | P8                  | GND  |  |

| N/A                       | GND    | GND                            | U8                  | GND  |  |

| N/A                       | GND    | GND                            | AA8                 | GND  |  |

| N/A                       | GND    | GND                            | A10                 | GND  |  |

| N/A                       | GND    | GND                            | E10                 | GND  |  |

| N/A                       | GND    | GND                            | H10                 | GND  |  |

| N/A                       | GND    | GND                            | AC10                | GND  |  |

| N/A                       | GND    | GND                            | AF10                | GND  |  |

| N/A                       | GND    | GND                            | AK10                | GND  |  |

| N/A                       | GND    | GND                            | R12                 | GND  |  |

## Table 107: FG900 Package Pinout (Cont'd)

| Bank | XC3S2000<br>Pin Name | XC3S4000, XC3S5000<br>Pin Name | FG900 Pin<br>Number | Туре |

|------|----------------------|--------------------------------|---------------------|------|

| N/A  | GND                  | GND                            | R17                 | GND  |

| N/A  | GND                  | GND                            | T17                 | GND  |

| N/A  | GND                  | GND                            | U17                 | GND  |

| N/A  | GND                  | GND                            | V17                 | GND  |

| N/A  | GND                  | GND                            | AC17                | GND  |

| N/A  | GND                  | GND                            | AF17                | GND  |

| N/A  | GND                  | GND                            | AK17                | GND  |

| N/A  | GND                  | GND                            | N18                 | GND  |

| N/A  | GND                  | GND                            | P18                 | GND  |

| N/A  | GND                  | GND                            | R18                 | GND  |

| N/A  | GND                  | GND                            | T18                 | GND  |

| N/A  | GND                  | GND                            | U18                 | GND  |

| N/A  | GND                  | GND                            | V18                 | GND  |

| N/A  | GND                  | GND                            | R19                 | GND  |

| N/A  | GND                  | GND                            | T19                 | GND  |

| N/A  | GND                  | GND                            | A21                 | GND  |

| N/A  | GND                  | GND                            | E21                 | GND  |

| N/A  | GND                  | GND                            | H21                 | GND  |

| N/A  | GND                  | GND                            | AC21                | GND  |

| N/A  | GND                  | GND                            | AF21                | GND  |

| N/A  | GND                  | GND                            | AK21                | GND  |

| N/A  | GND                  | GND                            | K23                 | GND  |

| N/A  | GND                  | GND                            | P23                 | GND  |

| N/A  | GND                  | GND                            | U23                 | GND  |

| N/A  | GND                  | GND                            | AA23                | GND  |

| N/A  | GND                  | GND                            | A25                 | GND  |

| N/A  | GND                  | GND                            | AK25                | GND  |

| N/A  | GND                  | GND                            | E26                 | GND  |

| N/A  | GND                  | GND                            | K26                 | GND  |

| N/A  | GND                  | GND                            | P26                 | GND  |

| N/A  | GND                  | GND                            | U26                 | GND  |

| N/A  | GND                  | GND                            | AA26                | GND  |