Welcome to <u>E-XFL.COM</u>

### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| D | eta | ails |  |

|---|-----|------|--|

|   |     |      |  |

| Details                        |                                                              |

|--------------------------------|--------------------------------------------------------------|

| Product Status                 | Obsolete                                                     |

| Number of LABs/CLBs            | 896                                                          |

| Number of Logic Elements/Cells | 8064                                                         |

| Total RAM Bits                 | 294912                                                       |

| Number of I/O                  | 141                                                          |

| Number of Gates                | 400000                                                       |

| Voltage - Supply               | 1.14V ~ 1.26V                                                |

| Mounting Type                  | Surface Mount                                                |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                              |

| Package / Case                 | 208-BFQFP                                                    |

| Supplier Device Package        | 208-PQFP (28x28)                                             |

| Purchase URL                   | https://www.e-xfl.com/product-detail/xilinx/xc3s400-5pqg208c |

|                                |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### Table 8: Single-Ended I/O Standards

| Signal Standard | V <sub>cco</sub> | (Volts)    | V <sub>REF</sub> for Inputs                           | <b>Board Termination</b>            |  |

|-----------------|------------------|------------|-------------------------------------------------------|-------------------------------------|--|

| (IOSTANDARD)    | For Outputs      | For Inputs | V <sub>REF</sub> for Inputs<br>(Volts) <sup>(1)</sup> | Voltage (V <sub>TT</sub> ) in Volts |  |

| GTL             | Note 2           | Note 2     | 0.8                                                   | 1.2                                 |  |

| GTLP            | Note 2           | Note 2     | 1                                                     | 1.5                                 |  |

| HSTL_I          | 1.5              | -          | 0.75                                                  | 0.75                                |  |

| HSTL_III        | 1.5              | _          | 0.9                                                   | 1.5                                 |  |

| HSTL_I_18       | 1.8              | -          | 0.9                                                   | 0.9                                 |  |

| HSTL_II_18      | 1.8              | -          | 0.9                                                   | 0.9                                 |  |

| HSTL_III_18     | 1.8              | -          | 1.1                                                   | 1.8                                 |  |

| LVCMOS12        | 1.2              | 1.2        | -                                                     | -                                   |  |

| LVCMOS15        | 1.5              | 1.5        | -                                                     | -                                   |  |

| LVCMOS18        | 1.8              | 1.8        | -                                                     | -                                   |  |

| LVCMOS25        | 2.5              | 2.5        | -                                                     | -                                   |  |

| LVCMOS33        | 3.3              | 3.3        | -                                                     | -                                   |  |

| LVTTL           | 3.3              | 3.3        | -                                                     | -                                   |  |

| PCI33_3         | 3.0              | 3.0        | -                                                     | -                                   |  |

| SSTL18_I        | 1.8              | -          | 0.9                                                   | 0.9                                 |  |

| SSTL18_II       | 1.8              | -          | 0.9                                                   | 0.9                                 |  |

| SSTL2_I         | 2.5              | -          | 1.25                                                  | 1.25                                |  |

| SSTL2_II        | 2.5              | -          | 1.25                                                  | 1.25                                |  |

### Notes:

1. Banks 4 and 5 of any Spartan-3 device in a VQ100 package do not support signal standards using V<sub>REF</sub>

2. The V<sub>CCO</sub> level used for the GTL and GTLP standards must be no lower than the termination voltage (V<sub>TT</sub>), nor can it be lower than the voltage at the I/O pad.

3. See Table 10 for a listing of the single-ended DCI standards.

Differential standards employ a pair of signals, one the opposite polarity of the other. The noise canceling (e.g., Common-Mode Rejection) properties of these standards permit exceptionally high data transfer rates. This section introduces the differential signaling capabilities of Spartan-3 devices.

Each device-package combination designates specific I/O pairs that are specially optimized to support differential standards. A unique "L-number", part of the pin name, identifies the line-pairs associated with each bank (see Figure 40, page 112). For each pair, the letters 'P' and 'N' designate the true and inverted lines, respectively. For example, the pin names IO\_L43P\_7 and IO\_L43N\_7 indicate the true and inverted lines comprising the line pair L43 on Bank 7. The V<sub>CCO</sub> lines provide current to the outputs. The V<sub>CCAUX</sub> lines supply power to the differential inputs, making them independent of the V<sub>CCO</sub> voltage for an I/O bank. The V<sub>REF</sub> lines are not used. Select the V<sub>CCO</sub> level to suit the desired differential standard according to Table 9.

### Table 9: Differential I/O Standards

| Signal Standard   | V <sub>cco</sub> ( | V for Inputs (Volts) |                                     |

|-------------------|--------------------|----------------------|-------------------------------------|

| (IOSTANDARD)      | For Outputs        | For Inputs           | V <sub>REF</sub> for Inputs (Volts) |

| LDT_25 (ULVDS_25) | 2.5                | -                    | -                                   |

| LVDS_25           | 2.5                | -                    | -                                   |

| BLVDS_25          | 2.5                | -                    | -                                   |

| LVDSEXT_25        | 2.5                | -                    | -                                   |

| LVPECL_25         | 2.5                | -                    | -                                   |

| RSDS_25           | 2.5                | -                    | -                                   |

| DIFF_HSTL_II_18   | 1.8                | -                    | -                                   |

| DIFF_SSTL2_II     | 2.5                | -                    | -                                   |

#### Notes:

1. See Table 10 for a listing of the differential DCI standards.

The need to supply  $V_{REF}$  and  $V_{CCO}$  imposes constraints on which standards can be used in the same bank. See The Organization of IOBs into Banks section for additional guidelines concerning the use of the  $V_{CCO}$  and  $V_{BFF}$  lines.

## **Digitally Controlled Impedance (DCI)**

When the round-trip delay of an output signal—i.e., from output to input and back again—exceeds rise and fall times, it is common practice to add termination resistors to the line carrying the signal. These resistors effectively match the impedance of a device's I/O to the characteristic impedance of the transmission line, thereby preventing reflections that adversely affect signal integrity. However, with the high I/O counts supported by modern devices, adding resistors requires significantly more components and board area. Furthermore, for some packages—e.g., ball grid arrays—it may not always be possible to place resistors close to pins.

DCI answers these concerns by providing two kinds of on-chip terminations: Parallel terminations make use of an integrated resistor network. Series terminations result from controlling the impedance of output drivers. DCI actively adjusts both parallel and series terminations to accurately match the characteristic impedance of the transmission line. This adjustment process compensates for differences in I/O impedance that can result from normal variation in the ambient temperature, the supply voltage and the manufacturing process. When the output driver turns off, the series termination, by definition, approaches a very high impedance; in contrast, parallel termination resistors remain at the targeted values.

DCI is available only for certain I/O standards, as listed in Table 10. DCI is selected by applying the appropriate I/O standard extensions to symbols or components. There are five basic ways to configure terminations, as shown in Table 11. The DCI I/O standard determines which of these terminations is put into effect.

HSTL\_I\_DCI-, HSTL\_III\_DCI-, and SSTL2\_I\_DCI-type outputs do not require the VRN and VRP reference resistors. Likewise, LVDCI-type inputs do not require the VRN and VRP reference resistors. In a bank without any DCI I/O or a bank containing non-DCI I/O and purely HSTL\_I\_DCI- or HSTL\_III\_DCI-type outputs, or SSTL2\_I\_DCI-type outputs or LVDCI-type inputs, the associated VRN and VRP pins can be used as general-purpose I/O pins.

The HSLVDCI (High-Speed LVDCI) standard is intended for bidirectional use. The driver is identical to LVDCI, while the input is identical to HSTL. By using a V<sub>REF</sub>-referenced input, HSLVDCI allows greater input sensitivity at the receiver than when using a single-ended LVCMOS-type receiver.

## Table 10: DCI I/O Standards

| Category of Signal              | Signal Standard                       | V <sub>CCC</sub> | <sub>0</sub> (V) | V <sub>REF</sub> for | Termination Type             |               |  |

|---------------------------------|---------------------------------------|------------------|------------------|----------------------|------------------------------|---------------|--|

| Standard                        | (IOSTANDARD)                          | For Outputs      | For Inputs       | Inputs (V)           | At Output                    | At Input      |  |

| Single-Ended                    |                                       |                  | ·                | ·                    |                              |               |  |

| Gunning                         | GTL_DCI                               | 1.2              | 1.2              | 0.8                  | Cincle                       | Circele       |  |

| Transceiver Logic               | GTLP_DCI                              | 1.5              | 1.5              | 1.0                  | Single                       | Single        |  |

| High-Speed                      | HSTL_I_DCI                            | 1.5              | 1.5              | 0.75                 | None                         | Split         |  |

| Transceiver Logic               | HSTL_III_DCI                          | 1.5              | 1.5              | 0.9                  | None                         | Single        |  |

|                                 | HSTL_I_DCI_18                         | 1.8              | 1.8              | 0.9                  | None                         |               |  |

|                                 | HSTL_II_DCI_18<br>DIFF_HSTL_II_18_DCI | 1.8              | 1.8              | 0.9                  | Split                        | Split         |  |

|                                 | HSTL_III_DCI_18                       | 1.8              | 1.8              | 1.1                  | None                         | Single        |  |

| Low-Voltage CMOS                | LVDCI_15                              | 1.5              | 1.5              | -                    |                              | None          |  |

|                                 | LVDCI_18                              | 1.8              | 1.8              | -                    | Controlled                   |               |  |

|                                 | LVDCI_25                              | 2.5              | 2.5              | _                    | impedance driver             |               |  |

|                                 | LVDCI_33 <sup>(2)</sup>               | 3.3              | 3.3              | -                    | 1                            |               |  |

|                                 | LVDCI_DV2_15                          | 1.5              | 1.5              | -                    | Controlled driver            |               |  |

|                                 | LVDCI_DV2_18                          | 1.8              | 1.8              | -                    |                              |               |  |

|                                 | LVDCI_DV2_25                          | 2.5              | 2.5              | -                    | with half-impedance          |               |  |

|                                 | LVDCI_DV2_33                          | 3.3              | 3.3              | _                    | 1                            |               |  |

| Hybrid HSTL Input               | HSLVDCI_15                            | 1.5              | 1.5              | 0.75                 |                              |               |  |

| and LVCMOS Output               | HSLVDCI_18                            | 1.8              | 1.8              | 0.9                  | Controlled                   | Nama          |  |

|                                 | HSLVDCI_25                            | 2.5              | 2.5              | 1.25                 | impedance driver             | None          |  |

|                                 | HSLVDCI_33                            | 3.3              | 3.3              | 1.65                 |                              |               |  |

| Stub Series                     | SSTL18_I_DCI                          | 1.8              | 1.8              | 0.9                  | $25\Omega$ driver            |               |  |

| Terminated Logic <sup>(3)</sup> | SSTL2_I_DCI                           | 2.5              | 2.5              | 1.25                 | $25\Omega$ driver            | Split         |  |

|                                 | SSTL2_II_DCI<br>DIFF_SSTL2_II_DCI     | 2.5              | 2.5              | 1.25                 | Split with $25\Omega$ driver | op            |  |

| Differential                    |                                       |                  |                  |                      |                              |               |  |

| Low-Voltage                     | LVDS_25_DCI                           | N/A              | 2.5              | -                    | None                         | Split on each |  |

| Differential Signaling          | LVDSEXT_25_DCI                        | N/A              | 2.5              | -                    | None                         | line of pair  |  |

### Notes:

1. DCI signal standards are not supported in Bank 5 of any Spartan-3 FPGA packaged in a VQ100, CP132, or TQ144 package.

2. Equivalent to LVTTL DCI.

3. The SSTL18\_II signal standard does not have a DCI equivalent.

## **Function Generator**

Each of the two LUTs (F and G) in a slice have four logic inputs (A1-A4) and a single output (D). This permits any four-variable Boolean logic operation to be programmed into them. Furthermore, wide function multiplexers can be used to effectively combine LUTs within the same CLB or across different CLBs, making logic functions with still more input variables possible.

The LUTs in both the right-hand and left-hand slice-pairs not only support the logic functions described above, but also can function as ROM that is initialized with data at the time of configuration.

The LUTs in the left-hand slice-pair (even-numbered columns such as X0 in Figure 11) of each CLB support two additional functions that the right-hand slice-pair (odd-numbered columns such as X1) do not.

First, it is possible to program the "left-hand LUTs" as distributed RAM. This type of memory affords moderate amounts of data buffering anywhere along a data path. One left-hand LUT stores 16 bits. Multiple left-hand LUTs can be combined in various ways to store larger amounts of data. A dual port option combines two LUTs so that memory access is possible from two independent data lines. A Distributed ROM option permits pre-loading the memory with data during FPGA configuration.

Second, it is possible to program each left-hand LUT as a 16-bit shift register. Used in this way, each LUT can delay serial data anywhere from one to 16 clock cycles. The four left-hand LUTs of a single CLB can be combined to produce delays up to 64 clock cycles. The SHIFTIN and SHIFTOUT lines cascade LUTs to form larger shift registers. It is also possible to combine shift registers across more than one CLB. The resulting programmable delays can be used to balance the timing of data pipelines.

# **Block RAM Overview**

All Spartan-3 devices support block RAM, which is organized as configurable, synchronous 18Kbit blocks. Block RAM stores relatively large amounts of data more efficiently than the distributed RAM feature described earlier. (The latter is better suited for buffering small amounts of data anywhere along signal paths.) This section describes basic Block RAM functions. For more information, refer to the chapter entitled "Using Block RAM" in <u>UG331</u>.

The aspect ratio—i.e., width vs. depth—of each block RAM is configurable. Furthermore, multiple blocks can be cascaded to create still wider and/or deeper memories.

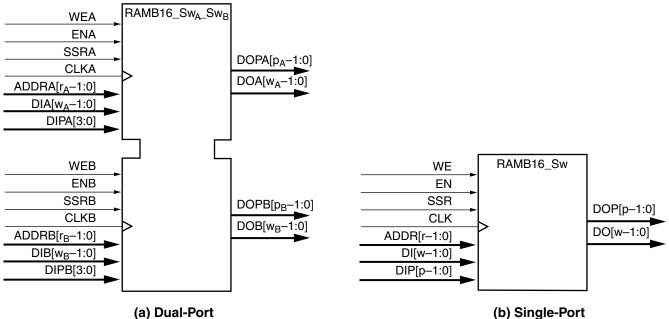

A choice among primitives determines whether the block RAM functions as dual- or single-port memory. A name of the form RAMB16\_S[w<sub>A</sub>]\_S[w<sub>B</sub>] calls out the dual-port primitive, where the integers w<sub>A</sub> and w<sub>B</sub> specify the total data path width at ports w<sub>A</sub> and w<sub>B</sub>, respectively. Thus, a RAMB16\_S9\_S18 is a dual-port RAM with a 9-bit-wide Port A and an 18-bit-wide Port B. A name of the form RAMB16\_S[w] identifies the single-port primitive, where the integer w specifies the total data path width of the lone port. A RAMB16\_S18 is a single-port RAM with an 18-bit-wide port. Other memory functions—e.g., FIFOs, data path width conversion, ROM, etc.—are readily available using the CORE Generator<sup>TM</sup> software, part of the Xilinx development software.

(a) Dual-Port

DS099-2\_13\_112905

### Notes:

- 1. w<sub>A</sub> and w<sub>B</sub> are integers representing the total data path width (i.e., data bits plus parity bits) at ports A and B, respectively.

- p<sub>A</sub> and p<sub>B</sub> are integers that indicate the number of data path lines serving as parity bits. 2.

- r<sub>A</sub> and r<sub>B</sub> are integers representing the address bus width at ports A and B, respectively. З.

- The control signals CLK, WE, EN, and SSR on both ports have the option of inverted polarity. 4.

### Figure 14: Block RAM Primitives

| Signal<br>Description   | Port A<br>Signal Name | Port B<br>Signal Name | Direction | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------------------|-----------------------|-----------------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Address Bus             | ADDRA                 | ADDRB                 | Input     | The Address Bus selects a memory location for read or write operations. The width (w) of the port's associated data path determines the number of available address lines (r).                                                                                                                                                                                                                                                                                                |

|                         |                       |                       |           | Whenever a port is enabled (ENA or ENB = High), address transitions must meet the data sheet setup and hold times with respect to the port clock (CLKA or CLKB). This requirement must be met, even if the RAM read output is of no interest.                                                                                                                                                                                                                                 |

| Data Input Bus          | DIA                   | DIB                   | Input     | Data at the DI input bus is written to the addressed memory location addressed on an enabled active CLK edge.                                                                                                                                                                                                                                                                                                                                                                 |

|                         |                       |                       |           | It is possible to configure a port's total data path width (w) to be 1, 2, 4,<br>9, 18, or 36 bits. This selection applies to both the DI and DO paths of<br>a given port. Each port is independent. For a port assigned a width (w),<br>the number of addressable locations is 16,384/(w-p) where "p" is the<br>number of parity bits. Each memory location has a width of "w"<br>(including parity bits). See the DIP signal description for more<br>information of parity. |

| Parity Data<br>Input(s) | DIPA                  | DIPB                  | Input     | Parity inputs represent additional bits included in the data input path to support error detection. The number of parity bits "p" included in the DI (same as for the DO bus) depends on a port's total data path width (w). See Table 14.                                                                                                                                                                                                                                    |

### Table 13: Block RAM Port Signals

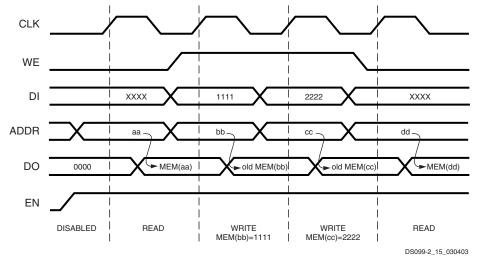

Figure 16: Waveforms of Block RAM Data Operations with READ\_FIRST Selected

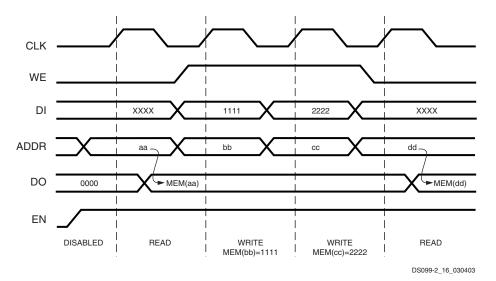

Choosing a third attribute called NO\_CHANGE puts the DO outputs in a latched state when asserting WE. Under this condition, the DO outputs will retain the data driven just before WE was asserted. NO\_CHANGE timing is shown in the portion of Figure 17 during which WE is High.

Figure 17: Waveforms of Block RAM Data Operations with NO\_CHANGE Selected

## **Dedicated Multipliers**

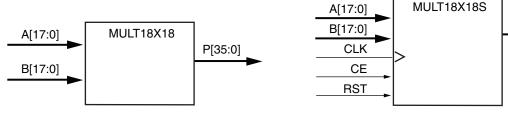

All Spartan-3 devices provide embedded multipliers that accept two 18-bit words as inputs to produce a 36-bit product. This section provides an introduction to multipliers. For further details, refer to the chapter entitled "Using Embedded Multipliers" in UG331.

The input buses to the multiplier accept data in two's-complement form (either 18-bit signed or 17-bit unsigned). One such multiplier is matched to each block RAM on the die. The close physical proximity of the two ensures efficient data handling. Cascading multipliers permits multiplicands more than three in number as well as wider than 18-bits. The multiplier is placed in a design using one of two primitives: an asynchronous version called MULT18X18 and a version with a register called MULT18X18S, as shown in Figure 18. The signals for these primitives are defined in Table 15.

The CORE Generator system produces multipliers based on these primitives that can be configured to suit a wide range of requirements.

(a) Asynchronous 18-bit Multiplier

(b) 18-bit Multiplier with Register

DS099-2\_17\_091510

P[35:0]

### Figure 18: Embedded Multiplier Primitives

### Table 15: Embedded Multiplier Primitives Descriptions

| Signal<br>Name | Direction            | Function                                                                                                                                                           |

|----------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A[17:0]        | Input                | Apply one 18-bit multiplicand to these inputs. The MULT18X18S primitive requires a setup time before the enabled rising edge of CLK.                               |

| B[17:0]        | Input                | Apply the other 18-bit multiplicand to these inputs. The MULT18X18S primitive requires a setup time before the enabled rising edge of CLK.                         |

| P[35:0]        | Output               | The output on the P bus is a 36-bit product of the multiplicands A and B. In the case of the MULT18X18S primitive, an enabled rising CLK edge updates the P bus.   |

| CLK            | Input <sup>(1)</sup> | CLK is only an input to the MULT18X18S primitive. The clock signal applied to this input, when enabled by CE, updates the output register that drives the P bus.   |

| CE             | Input <sup>(1)</sup> | CE is only an input to the MULT18X18S primitive. Enable for the CLK signal. Asserting this input enables the CLK signal to update the P bus.                       |

| RST            | Input <sup>(1)</sup> | RST is only an input to the MULT18X18S primitive. Asserting this input resets the output register on an enabled, rising CLK edge, forcing the P bus to all zeroes. |

### Notes:

1. The control signals CLK, CE and RST have the option of inverted polarity.

# **Digital Clock Manager (DCM)**

Spartan-3 devices provide flexible, complete control over clock frequency, phase shift and skew through the use of the DCM feature. To accomplish this, the DCM employs a Delay-Locked Loop (DLL), a fully digital control system that uses feedback to maintain clock signal characteristics with a high degree of precision despite normal variations in operating temperature and voltage. This section provides a fundamental description of the DCM. For further information, refer to the chapter entitled "Using Digital Clock Managers" in UG331.

Each member of the Spartan-3 family has four DCMs, except the smallest, the XC3S50, which has two DCMs. The DCMs are located at the ends of the outermost Block RAM column(s). See Figure 1, page 3. The Digital Clock Manager is placed in a design as the "DCM" primitive.

The DCM supports three major functions:

- Clock-skew Elimination: Clock skew describes the extent to which clock signals may, under normal circumstances, deviate from zero-phase alignment. It occurs when slight differences in path delays cause the clock signal to arrive at different points on the die at different times. This clock skew can increase set-up and hold time requirements as well as clock-to-out time, which may be undesirable in applications operating at a high frequency, when timing is critical. The DCM eliminates clock skew by aligning the output clock signal it generates with another version of the clock signal that is fed back. As a result, the two clock signals establish a zero-phase relationship. This effectively cancels out clock distribution delays that may lie in the signal path leading from the clock output of the DCM to its feedback input.

- Frequency Synthesis: Provided with an input clock signal, the DCM can generate a wide range of different output clock frequencies. This is accomplished by either multiplying and/or dividing the frequency of the input clock signal by any of several different factors.

## Table 36: DC Characteristics of User I/Os Using Single-Ended Standards (Cont'd)

| Signal Standard<br>(IOSTANDARD) and Current<br>Drive Attribute (mA) |    | Test Co                                      | nditions | Logic Level C              | haracteristics             |

|---------------------------------------------------------------------|----|----------------------------------------------|----------|----------------------------|----------------------------|

|                                                                     |    | I <sub>OL</sub> I <sub>OH</sub><br>(mA) (mA) |          | V <sub>OL</sub><br>Max (V) | V <sub>ОН</sub><br>Min (V) |

| LVCMOS33 <sup>(4)</sup>                                             | 2  | 2                                            | -2       | 0.4                        | V <sub>CCO</sub> – 0.4     |

|                                                                     | 4  | 4                                            | -4       | _                          |                            |

|                                                                     | 6  | 6                                            | 6        | _                          |                            |

|                                                                     | 8  | 8                                            | -8       |                            |                            |

|                                                                     | 12 | 12                                           | -12      |                            |                            |

|                                                                     | 16 | 16                                           | -16      | _                          |                            |

|                                                                     | 24 | 24                                           | -24      | _                          |                            |

| LVDCI_33,<br>LVDCI_DV2_33                                           |    | Note 3                                       | Note 3   | _                          |                            |

| LVTTL <sup>(4)</sup>                                                | 2  | 2                                            | -2       | 0.4                        | 2.4                        |

|                                                                     | 4  | 4                                            | -4       |                            |                            |

|                                                                     | 6  | 6                                            | 6        |                            |                            |

|                                                                     | 8  | 8                                            | 8        |                            |                            |

|                                                                     | 12 | 12                                           | -12      |                            |                            |

|                                                                     | 16 | 16                                           | -16      |                            |                            |

|                                                                     | 24 | 24                                           | -24      |                            |                            |

| PCI33_3                                                             |    | Note 6                                       | Note 6   | 0.10V <sub>CCO</sub>       | 0.90V <sub>CCO</sub>       |

| SSTL18_I                                                            |    | 6.7                                          | -6.7     | V <sub>TT</sub> – 0.475    | V <sub>TT</sub> + 0.475    |

| SSTL18_I_DCI<br>SSTL18_II<br>SSTL2_I<br>SSTL2_I_DCI                 |    | Note 3                                       | Note 3   |                            |                            |

|                                                                     |    | 13.4                                         | -13.4    | V <sub>TT</sub> – 0.475    | V <sub>TT</sub> + 0.475    |

|                                                                     |    | 8.1                                          | -8.1     | V <sub>TT</sub> – 0.61     | V <sub>TT</sub> + 0.61     |

|                                                                     |    | Note 3                                       | Note 3   |                            |                            |

| SSTL2_II <sup>(7)</sup>                                             |    | 16.2                                         | -16.2    | V <sub>TT</sub> – 0.81     | V <sub>TT</sub> + 0.81     |

| SSTL2_II_DCI <sup>(7)</sup>                                         |    | Note 3                                       | Note 3   |                            |                            |

#### Notes:

2.

The numbers in this table are based on the conditions set forth in Table 32 and Table 35. 1.

The numbers in this table are based on the conditions set for Descriptions of the symbols used in this table are as follows:  $I_{OL}$  – the output current condition under which VOL is tested  $V_{OL}$  – the output current condition under which VOH is tested  $V_{OL}$  – the output voltage that indicates a Low logic level  $V_{H}$  – the input voltage that indicates a High logic level  $V_{H}$  – the input voltage that indicates a High logic level  $V_{H}$  – the input voltage that indicates a High logic level  $V_{H}$  – the supply voltage for output drivers as well as LVCM

$V_{CCO}$  – the supply voltage for output drivers as well as LVCMOS, LVTTL, and PCI inputs  $V_{REF}$  – the reference voltage for setting the input switching threshold  $V_{TT}$  – the voltage applied to a resistor termination

Tested according to the standard's relevant specifications. When using the DCI version of a standard on a given I/O bank, that bank will consume more power than if the non-DCI version had been used instead. The additional power is drawn for the purpose of impedance-matching at the I/O pins. A portion of this power is dissipated in the two RREF resistors. 3.

For the LVCMOS and LVTTL standards: the same V<sub>OL</sub> and V<sub>OH</sub> limits apply for both the Fast and Slow slew attributes. 4.

All dedicated output pins (CCLK, DONE, and TDO) and dual-purpose totem-pole output pins (D0-D7 and BUSY/DOUT) exhibit the characteristics of 5. LVCMOS25 with 12 mA drive and slow slew rate. For information concerning the use of 3.3V signals, see 3.3V-Tolerant Configuration Interface, page 47.

Tested according to the relevant PCI specifications. For more information, see XAPP457. 6.

7. The minimum usable V<sub>TT</sub> voltage is 1.25V.

### Table 70: Spartan-3 FPGA Pin Definitions (Cont'd)

| Pin Name            | Direction               | Description                                                                                                                                                                                                                                    |

|---------------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TDI                 | Input                   | <b>JTAG Test Data Input:</b><br>TDI is the serial data input for all JTAG instruction and data registers. This<br>pin has an internal pull-up resistor to VCCAUX during configuration.                                                         |

| TMS                 | Input                   | <b>JTAG Test Mode Select:</b><br>The serial TMS input controls the operation of the JTAG port. This pin has an internal pull-up resistor to VCCAUX during configuration.                                                                       |

| TDO                 | Output                  | <b>JTAG Test Data Output:</b><br>TDO is the serial data output for all JTAG instruction and data registers.<br>This pin has an internal pull-up resistor to VCCAUX during configuration.                                                       |

| VCCO: I/O bank out  | out voltage supply pins |                                                                                                                                                                                                                                                |

| VCCO_#              | Supply                  | <b>Power Supply for Output Buffer Drivers (per bank):</b><br>These pins power the output drivers within a specific I/O bank.                                                                                                                   |

| VCCAUX: Auxiliary   | voltage supply pins     |                                                                                                                                                                                                                                                |

| VCCAUX              | Supply                  | Power Supply for Auxiliary Circuits:<br>+2.5V power pins for auxiliary circuits, including the Digital Clock<br>Managers (DCMs), the dedicated configuration pins (CONFIG), and the<br>dedicated JTAG pins. All VCCAUX pins must be connected. |

| VCCINT: Internal co | re voltage supply pins  |                                                                                                                                                                                                                                                |

| VCCINT              | Supply                  | <b>Power Supply for Internal Core Logic:</b><br>+1.2V power pins for the internal logic. All pins must be connected.                                                                                                                           |

| GND: Ground supply  | y pins                  |                                                                                                                                                                                                                                                |

| GND                 | Supply                  | <b>Ground:</b><br>Ground pins, which are connected to the power supply's return path. All pins must be connected.                                                                                                                              |

| N.C.: Unconnected   | backage pins            |                                                                                                                                                                                                                                                |

| N.C.                |                         | Unconnected Package Pin:<br>These package pins are unconnected.                                                                                                                                                                                |

### Notes:

1. All unused inputs and bidirectional pins must be tied either High or Low. For unused enable inputs, apply the level that disables the associated function. One common approach is to activate internal pull-up or pull-down resistors. An alternative approach is to externally connect the pin to either VCCO or GND.

2. All outputs are of the totem-pole type — i.e., they can drive High as well as Low logic levels — except for the cases where "Open Drain" is indicated. The latter can only drive a Low logic level and require a pull-up resistor to produce a High logic level.

## **Detailed, Functional Pin Descriptions**

### I/O Type: Unrestricted, General-purpose I/O Pins

After configuration, I/O-type pins are inputs, outputs, bidirectional I/O, three-state outputs, open-drain outputs, or open-source outputs, as defined in the application

Pins labeled "IO" support all SelectIO<sup>™</sup> interface signal standards except differential standards. A given device at most only has a few of these pins.

A majority of the general-purpose I/O pins are labeled in the format "IO\_Lxxy\_#". These pins support all SelectIO signal standards, including the differential standards such as LVDS, ULVDS, BLVDS, RSDS, or LDT.

For additional information, see IOBs, page 10

### HSWAP\_EN: Disable Pull-up Resistors During Configuration

As shown in Table 76, a Low on this asynchronous pin enables pull-up resistors on all user I/Os not actively involved in the configuration process, although only until device configuration completes. A High disables the pull-up resistors during configuration, which is the desired state for some applications.

The dedicated configuration CONFIG pins (CCLK, DONE, PROG\_B, HSWAP\_EN, M2, M1, M0), the JTAG pins (TDI, TMS, TCK, TDO) and the INIT\_B always have active pull-up resistors during configuration, regardless of the value on HSWAP\_EN.

After configuration, HSWAP\_EN becomes a "don't care" input and any pull-up resistors previously enabled by HSWAP\_EN are disabled. If a user I/O in the application requires a pull-up resistor after configuration, place a PULLUP primitive on the associated I/O pin or, for some pins, set the associated bitstream generator option.

### Table 76: HSWAP\_EN Encoding

| HSWAP_EN                       | Function                                                                                                                                                       |  |  |  |  |  |  |

|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| During Config                  | During Configuration                                                                                                                                           |  |  |  |  |  |  |

| 0                              | Enable pull-up resistors on all pins not actively involved in the configuration process. Pull-ups are only active until configuration completes. See Table 79. |  |  |  |  |  |  |

| 1                              | No pull-up resistors during configuration.                                                                                                                     |  |  |  |  |  |  |

| After Configuration, User Mode |                                                                                                                                                                |  |  |  |  |  |  |

| Х                              | This pin has no function except during device configuration.                                                                                                   |  |  |  |  |  |  |

### Notes:

1. X = don't care, either 0 or 1.

The Bitstream generator option HswapenPin determines whether a pull-up resistor to VCCAUX, a pull-down resistor, or no resistor is present on HSWAP\_EN after configuration.

## **JTAG: Dedicated JTAG Port Pins**

### Table 77: JTAG Pin Descriptions

| Pin Name | Direction | Description                                                                                                                                                                                                                                                                              | Bitstream Generation Option                                                                                                |

|----------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| ТСК      | Input     | <b>Test Clock:</b> The TCK clock signal synchronizes all boundary scan operations on its rising edge.                                                                                                                                                                                    | The BitGen option <b>TckPin</b> determines whether a pull-up resistor, pull-down resistor or no resistor is present.       |

| TDI      | Input     | <b>Test Data Input:</b> TDI is the serial data input for all JTAG instruction and data registers. This input is sampled on the rising edge of TCK.                                                                                                                                       | The BitGen option <b>TdiPin</b> determines<br>whether a pull-up resistor, pull-down<br>resistor or no resistor is present. |

| TMS      | Input     | <b>Test Mode Select:</b> The TMS input controls the sequence of states through which the JTAG TAP state machine passes. This input is sampled on the rising edge of TCK.                                                                                                                 | The BitGen option <b>TmsPin</b> determines whether a pull-up resistor, pull-down resistor or no resistor is present.       |

| TDO      | Output    | <b>Test Data Output:</b> The TDO pin is the data output for all JTAG instruction and data registers. This output is sampled on the rising edge of TCK. The TDO output is an active totem-pole driver and is not like the open-collector TDO output on Virtex <sup>®</sup> -II Pro FPGAs. | The BitGen option <b>TdoPin</b> determines<br>whether a pull-up resistor, pull-down<br>resistor or no resistor is present. |

These pins are dedicated connections to the four-wire IEEE 1532/IEEE 1149.1 JTAG port, shown in Figure 43 and described in Table 77. The JTAG port is used for boundary-scan testing, device configuration, application debugging, and possibly an additional serial port for the application. These pins are dedicated and are not available as user-I/O pins. Every package has four dedicated JTAG pins and these pins are powered by the +2.5V VCCAUX supply.

For additional information on JTAG configuration, see Boundary-Scan (JTAG) Mode, page 50.

All VCCAUX inputs must be connected together and to the +2.5V voltage supply. Furthermore, there must be sufficient supply decoupling to guarantee problem-free operation, as described in XAPP623.

Because VCCAUX connects to the DCMs and the DCMs are sensitive to voltage changes, be sure that the VCCAUX supply and the ground return paths are designed for low noise and low voltage drop, especially that caused by a large number of simultaneous switching I/Os.

## **GND Type: Ground**

All GND pins must be connected and have a low resistance path back to the various VCCO, VCCINT, and VCCAUX supplies.

# **Pin Behavior During Configuration**

Table 79 shows how various pins behave during the FPGA configuration process. The actual behavior depends on the values applied to the M2, M1, and M0 mode select pins and the HSWAP\_EN pin. The mode select pins determine which of the DUAL type pins are active during configuration. In JTAG configuration mode, none of the DUAL-type pins are used for configuration and all behave as user-I/O pins.

All DUAL-type pins not actively used during configuration and all I/O-type, DCI-type, VREF-type, GCLK-type pins are high impedance (floating, three-stated, Hi-Z) during the configuration process. These pins are indicated in Table 79 as shaded table entries or cells. These pins have a pull-up resistor to their associated VCCO if the HSWAP\_EN pin is Low. When HSWAP\_EN is High, these pull-up resistors are disabled during configuration.

Some pins always have an active pull-up resistor during configuration, regardless of the value applied to the HSWAP\_EN pin. After configuration, these pull-up resistors are controlled by Bitstream Options.

- All the dedicated CONFIG-type configuration pins (CCLK, PROG\_B, DONE, M2, M1, M0, and HSWAP\_EN) have a

pull-up resistor to VCCAUX.

- All JTAG-type pins (TCK, TDI, TMS, TDO) have a pull-up resistor to VCCAUX.

- The INIT\_B DUAL-purpose pin has a pull-up resistor to VCCO\_4 or VCCO\_BOTTOM, depending on package style.

After configuration completes, some pins have optional behavior controlled by the configuration bitstream loaded into the part. For example, via the bitstream, all unused I/O pins can be collectively configured as input pins with either a pull-up resistor, a pull-down resistor, or be left in a high-impedance state.

|                      |                               | Configuration Mode Settings <m2:m1:m0></m2:m1:m0> |                          |               |           |                            |  |  |  |  |

|----------------------|-------------------------------|---------------------------------------------------|--------------------------|---------------|-----------|----------------------------|--|--|--|--|

| Pin Name             | Serial Modes                  |                                                   | SelectMap Parallel Modes |               | JTAG Mode | Bitstream<br>Configuration |  |  |  |  |

|                      | Master <0:0:0>                | Slave <1:1:1>                                     | Master <0:1:1>           | Slave <1:1:0> | <1:0:1>   | Option                     |  |  |  |  |

| I/O: General-pur     | I/O: General-purpose I/O pins |                                                   |                          |               |           |                            |  |  |  |  |

| IO                   |                               |                                                   |                          |               |           | UnusedPin                  |  |  |  |  |

| IO_Lxxy_#            |                               |                                                   |                          |               |           | UnusedPin                  |  |  |  |  |

| DUAL: Dual-pur       | pose configuration            | pins                                              |                          |               |           |                            |  |  |  |  |

| IO_Lxxy_#/<br>DIN/D0 | DIN (I)                       | DIN (I)                                           | D0 (I/O)                 | D0 (I/O)      |           | Persist UnusedPin          |  |  |  |  |

| IO_Lxxy_#/<br>D1     |                               |                                                   | D1 (I/O)                 | D1 (I/O)      |           | Persist UnusedPin          |  |  |  |  |

| IO_Lxxy_#/<br>D2     |                               |                                                   | D2 (I/O)                 | D2 (I/O)      |           | Persist UnusedPin          |  |  |  |  |

| IO_Lxxy_#/<br>D3     |                               |                                                   | D3 (I/O)                 | D3 (I/O)      |           | Persist UnusedPin          |  |  |  |  |

| IO_Lxxy_#/<br>D4     |                               |                                                   | D4 (I/O)                 | D4 (I/O)      |           | Persist UnusedPin          |  |  |  |  |

### Table 79: Pin Behavior After Power-Up, During Configuration

## CP132: 132-Ball Chip-Scale Package

**Note:** The CP132 and CPG132 packages are discontinued. See www.xilinx.com/support/documentation/spartan-3.htm#19600.

The pinout and footprint for the XC3S50 in the 132-ball chip-scale package, CP132, appear in Table 89 and Figure 45.

All the package pins appear in Table 89 and are sorted by bank number, then by pin name. Pins that form a differential I/O pair appear together in the table. The table also shows the pin number for each pin and the pin type, as defined earlier.

The CP132 footprint has eight I/O banks. However, the voltage supplies for the two I/O banks along an edge are connected together internally. Consequently, there are four output voltage supplies, labeled VCCO\_TOP, VCCO\_RIGHT, VCCO\_BOTTOM, and VCCO\_LEFT.

## **Pinout Table**

Table 89: CP132 Package Pinout

| Bank | XC3S50 Pin Name  | CP132<br>Ball | Туре |

|------|------------------|---------------|------|

| 0    | IO_L01N_0/VRP_0  | A3            | DCI  |

| 0    | IO_L01P_0/VRN_0  | C4            | DCI  |

| 0    | IO_L27N_0        | C5            | I/O  |

| 0    | IO_L27P_0        | B5            | I/O  |

| 0    | IO_L30N_0        | B6            | I/O  |

| 0    | IO_L30P_0        | A6            | I/O  |

| 0    | IO_L31N_0        | C7            | I/O  |

| 0    | IO_L31P_0/VREF_0 | B7            | VREF |

| 0    | IO_L32N_0/GCLK7  | A7            | GCLK |

| 0    | IO_L32P_0/GCLK6  | C8            | GCLK |

| 1    | IO_L01N_1/VRP_1  | A13           | DCI  |

| 1    | IO_L01P_1/VRN_1  | B13           | DCI  |

| 1    | IO_L27N_1        | C11           | I/O  |

| 1    | IO_L27P_1        | A12           | I/O  |

| 1    | IO_L28N_1        | A11           | I/O  |

| 1    | IO_L28P_1        | B11           | I/O  |

| 1    | IO_L31N_1/VREF_1 | C9            | VREF |

| 1    | IO_L31P_1        | A10           | I/O  |

| 1    | IO_L32N_1/GCLK5  | A8            | GCLK |

| 1    | IO_L32P_1/GCLK4  | A9            | GCLK |

| 2    | IO_L01N_2/VRP_2  | D12           | DCI  |

| 2    | IO_L01P_2/VRN_2  | C14           | DCI  |

| 2    | IO_L20N_2        | E12           | I/O  |

| 2    | IO_L20P_2        | E13           | I/O  |

| 2    | IO_L21N_2        | E14           | I/O  |

| 2    | IO_L21P_2        | F12           | I/O  |

| 2    | IO_L23N_2/VREF_2 | F13           | VREF |

| 2    | IO_L23P_2        | F14           | I/O  |

| 2    | IO_L24N_2        | G12           | I/O  |

www.xilinx.com

## Table 98: FG320 Package Pinout (Cont'd)

| Bank | XC3S400, XC3S1000, XC3S1500<br>Pin Name | FG320<br>Pin Number | Туре |

|------|-----------------------------------------|---------------------|------|

| 3    | IO_L24N_3                               | M18                 | I/O  |

| 3    | IO_L24P_3                               | N17                 | I/O  |

| 3    | IO_L27N_3                               | L14                 | I/O  |

| 3    | IO_L27P_3                               | L13                 | I/O  |

| 3    | IO_L34N_3                               | L15                 | I/O  |

| 3    | IO_L34P_3/VREF_3                        | L16                 | VREF |

| 3    | IO_L35N_3                               | L18                 | I/O  |

| 3    | IO_L35P_3                               | L17                 | I/O  |

| 3    | IO_L39N_3                               | K13                 | I/O  |

| 3    | IO_L39P_3                               | K14                 | I/O  |

| 3    | IO_L40N_3/VREF_3                        | K17                 | VREF |

| 3    | IO_L40P_3                               | K18                 | I/O  |

| 3    | VCCO_3                                  | K12                 | VCCO |

| 3    | VCCO_3                                  | L12                 | VCCO |

| 3    | VCCO_3                                  | N16                 | VCCO |

| 4    | IO                                      | P12                 | I/O  |

| 4    | IO                                      | V14                 | I/O  |

| 4    | IO/VREF_4                               | R10                 | VREF |

| 4    | IO/VREF_4                               | U13                 | VREF |

| 4    | IO/VREF_4                               | V17                 | VREF |

| 4    | IO_L01N_4/VRP_4                         | U16                 | DCI  |

| 4    | IO_L01P_4/VRN_4                         | V16                 | DCI  |

| 4    | IO_L06N_4/VREF_4                        | P14                 | VREF |

| 4    | IO_L06P_4                               | R14                 | I/O  |

| 4    | IO_L09N_4                               | U15                 | I/O  |

| 4    | IO_L09P_4                               | V15                 | I/O  |

| 4    | IO_L10N_4                               | T14                 | I/O  |

| 4    | IO_L10P_4                               | U14                 | I/O  |

| 4    | IO_L25N_4                               | R13                 | I/O  |

| 4    | IO_L25P_4                               | P13                 | I/O  |

| 4    | IO_L27N_4/DIN/D0                        | T12                 | DUAL |

| 4    | IO_L27P_4/D1                            | R12                 | DUAL |

| 4    | IO_L28N_4                               | V12                 | I/O  |

| 4    | IO_L28P_4                               | V11                 | I/O  |

| 4    | IO_L29N_4                               | R11                 | I/O  |

| 4    | IO_L29P_4                               | T11                 | I/O  |

| 4    | IO_L30N_4/D2                            | N11                 | DUAL |

| 4    | IO_L30P_4/D3                            | P11                 | DUAL |

| 4    | IO_L31N_4/INIT_B                        | U10                 | DUAL |

## Table 100: FG456 Package Pinout (Cont'd)

| Bank | 3S400         3S1000, 3S1500, 3S2000           Pin Name         Pin Name |                     | FG456<br>Pin Number | Туре |

|------|--------------------------------------------------------------------------|---------------------|---------------------|------|

| 4    | IO_L30N_4/D2                                                             | IO_L30N_4/D2        | U12                 | DUAL |

| 4    | IO_L30P_4/D3                                                             | IO_L30P_4/D3        | V12                 | DUAL |

| 4    | IO_L31N_4/INIT_B                                                         | IO_L31N_4/INIT_B    | W12                 | DUAL |

| 4    | IO_L31P_4/DOUT/BUSY                                                      | IO_L31P_4/DOUT/BUSY | Y12                 | DUAL |

| 4    | IO_L32N_4/GCLK1                                                          | IO_L32N_4/GCLK1     | AA12                | GCLK |

| 4    | IO_L32P_4/GCLK0                                                          | IO_L32P_4/GCLK0     | AB12                | GCLK |

| 4    | VCCO_4                                                                   | VCCO_4              | T12                 | VCCO |

| 4    | VCCO_4                                                                   | VCCO_4              | T13                 | VCCO |

| 4    | VCCO_4                                                                   | VCCO_4              | T14                 | VCCO |

| 4    | VCCO_4                                                                   | VCCO_4              | U15                 | VCCO |

| 4    | VCCO_4                                                                   | VCCO_4              | Y15                 | VCCO |

| 5    | IO                                                                       | IO                  | U7                  | I/O  |

| 5    | N.C. (♦)                                                                 | IO                  | U9                  | I/O  |

| 5    | 10                                                                       | Ю                   | U10                 | I/O  |

| 5    | 10                                                                       | 10                  | U11                 | I/O  |

| 5    | 10                                                                       | IO                  | V7                  | I/O  |

| 5    | IO                                                                       | IO                  | V10                 | I/O  |

| 5    | IO/VREF_5                                                                | IO/VREF_5           | AB11 VRE            |      |

| 5    | IO/VREF_5                                                                | IO/VREF_5           | U6                  | VREF |

| 5    | IO_L01N_5/RDWR_B                                                         | IO_L01N_5/RDWR_B    | Y4                  | DUAL |

| 5    | IO_L01P_5/CS_B                                                           | IO_L01P_5/CS_B      | AA3 DUA             |      |

| 5    | IO_L06N_5                                                                | IO_L06N_5           | AB4                 | I/O  |

| 5    | IO_L06P_5                                                                | IO_L06P_5           | AA4 I/O             |      |

| 5    | IO_L09N_5                                                                | IO_L09N_5           | Y5 I/O              |      |

| 5    | IO_L09P_5                                                                | IO_L09P_5           | W5 I/O              |      |

| 5    | IO_L10N_5/VRP_5                                                          | IO_L10N_5/VRP_5     | AB5                 | DCI  |

| 5    | IO_L10P_5/VRN_5                                                          | IO_L10P_5/VRN_5     | AA5                 | DCI  |

| 5    | IO_L15N_5                                                                | IO_L15N_5           | W6                  | I/O  |

| 5    | IO_L15P_5                                                                | IO_L15P_5           | V6                  | I/O  |

| 5    | IO_L16N_5                                                                | IO_L16N_5           | AA6                 | I/O  |

| 5    | IO_L16P_5                                                                | IO_L16P_5           | Y6 I/O              |      |

| 5    | N.C. (�)                                                                 | IO_L19N_5           | Y7                  | I/O  |

| 5    | N.C. (♦)         IO_L19P_5/<br>VREF_5         W7                         |                     | W7                  | VREF |

| 5    | N.C. (�)                                                                 | IO_L22N_5           | AB7                 | I/O  |

| 5    | N.C. (�)                                                                 | IO_L22P_5           | AA7 I/O             |      |

| 5    | IO_L24N_5                                                                | IO_L24N_5           | W8 I/C              |      |

| 5    | IO_L24P_5                                                                | IO_L24P_5           | V8                  | I/O  |

| 5    | IO_L25N_5                                                                | IO_L25N_5           |                     |      |

| 5    | IO_L25P_5                                                                | IO_L25P_5           | AA8 I/C             |      |

### Table 107: FG900 Package Pinout (Cont'd)

| Bank | BankXC3S2000<br>Pin NameXC3S4000, XC3S5<br>Pin Name |                  | FG900 Pin<br>Number | Туре |  |

|------|-----------------------------------------------------|------------------|---------------------|------|--|

| 2    | IO_L04N_2                                           | IO_L04N_2        | E29 I/C             |      |  |

| 2    | IO_L04P_2                                           | IO_L04P_2        | E30 I/0             |      |  |

| 2    | IO_L05N_2                                           | IO_L05N_2        | F28                 | I/O  |  |

| 2    | IO_L05P_2                                           | IO_L05P_2        | F29                 | I/O  |  |

| 2    | IO_L06N_2                                           | IO_L06N_2        | G27                 | I/O  |  |

| 2    | IO_L06P_2                                           | IO_L06P_2        | G28                 | I/O  |  |

| 2    | IO_L07N_2                                           | IO_L07N_2        | G29                 | I/O  |  |

| 2    | IO_L07P_2                                           | IO_L07P_2        | G30                 | I/O  |  |

| 2    | IO_L08N_2                                           | IO_L08N_2        | G25                 | I/O  |  |

| 2    | IO_L08P_2                                           | IO_L08P_2        | H24                 | I/O  |  |

| 2    | IO_L09N_2/VREF_2                                    | IO_L09N_2/VREF_2 | H25                 | VREF |  |

| 2    | IO_L09P_2                                           | IO_L09P_2        | H26                 | I/O  |  |

| 2    | IO_L10N_2                                           | IO_L10N_2        | H27                 | I/O  |  |

| 2    | IO_L10P_2                                           | IO_L10P_2        | H28                 | I/O  |  |

| 2    | IO_L12N_2                                           | IO_L12N_2        | H29                 | I/O  |  |

| 2    | IO_L12P_2                                           | IO_L12P_2        | H30                 | I/O  |  |

| 2    | IO_L13N_2                                           | IO_L13N_2        | J26                 | I/O  |  |

| 2    | IO_L13P_2/VREF_2                                    | IO_L13P_2/VREF_2 | J27 VR              |      |  |

| 2    | IO_L14N_2                                           | IO_L14N_2        | J29                 | I/O  |  |

| 2    | IO_L14P_2                                           | IO_L14P_2        | J30                 | I/O  |  |

| 2    | IO_L15N_2                                           | IO_L15N_2        | J23                 | I/O  |  |

| 2    | IO_L15P_2                                           | IO_L15P_2        | K22 I/0             |      |  |

| 2    | IO_L16N_2                                           | IO_L16N_2        | K24                 | I/O  |  |

| 2    | IO_L16P_2                                           | IO_L16P_2        | K25                 | I/O  |  |

| 2    | IO_L19N_2                                           | IO_L19N_2        | L25                 | I/O  |  |

| 2    | IO_L19P_2                                           | IO_L19P_2        | L26                 | I/O  |  |

| 2    | IO_L20N_2                                           | IO_L20N_2        | L27                 | I/O  |  |

| 2    | IO_L20P_2                                           | IO_L20P_2        | L28                 | I/O  |  |

| 2    | IO_L21N_2                                           | IO_L21N_2        | L29                 | I/O  |  |

| 2    | IO_L21P_2                                           | IO_L21P_2        | L30                 | I/O  |  |

| 2    | IO_L22N_2                                           | IO_L22N_2        | M22                 | I/O  |  |

| 2    | IO_L22P_2                                           | IO_L22P_2        | M23                 | I/O  |  |

| 2    | IO_L23N_2/VREF_2                                    | IO_L23N_2/VREF_2 | M24 VRE             |      |  |

| 2    | IO_L23P_2                                           | IO_L23P_2        | M25                 | I/O  |  |

| 2    | IO_L24N_2                                           | IO_L24N_2        | M27                 | I/O  |  |

| 2    | IO_L24P_2                                           | IO_L24P_2        | M28 I/O             |      |  |

| 2    | IO_L26N_2                                           | IO_L26N_2        | M21 I/O             |      |  |

| 2    | IO_L26P_2                                           | IO_L26P_2        | N21                 | I/O  |  |

| 2    | IO_L27N_2                                           | IO_L27N_2        | N22                 | I/O  |  |

| 2    | IO_L27P_2                                           | IO_L27P_2        | N23                 | I/O  |  |

### Table 107: FG900 Package Pinout (Cont'd)

| Bank | XC3S2000<br>Pin Name | XC3S4000, XC3S5000<br>Pin Name | FG900 Pin<br>Number | Туре |  |

|------|----------------------|--------------------------------|---------------------|------|--|

| 7    | IO_L23N_7            | IO_L23N_7                      | L3                  | I/O  |  |

| 7    | IO_L23P_7            | IO_L23P_7                      | L4                  | I/O  |  |

| 7    | IO_L24N_7            | IO_L24N_7                      | L1                  | I/O  |  |

| 7    | IO_L24P_7            | IO_L24P_7                      | L2                  | I/O  |  |

| 7    | N.C. (�)             | IO_L25N_7                      | M6                  | I/O  |  |

| 7    | N.C. (�)             | IO_L25P_7                      | M7                  | I/O  |  |

| 7    | IO_L26N_7            | IO_L26N_7                      | M3                  | I/O  |  |

| 7    | IO_L26P_7            | IO_L26P_7                      | M4                  | I/O  |  |

| 7    | IO_L27N_7            | IO_L27N_7                      | M1                  | I/O  |  |

| 7    | IO_L27P_7/VREF_7     | IO_L27P_7/VREF_7               | M2                  | VREF |  |

| 7    | IO_L28N_7            | IO_L28N_7                      | N10                 | I/O  |  |

| 7    | IO_L28P_7            | IO_L28P_7                      | M10                 | I/O  |  |

| 7    | IO_L29N_7            | IO_L29N_7                      | N8                  | I/O  |  |

| 7    | IO_L29P_7            | IO_L29P_7                      | N9                  | I/O  |  |

| 7    | IO_L31N_7            | IO_L31N_7                      | N1                  | I/O  |  |

| 7    | IO_L31P_7            | IO_L31P_7                      | N2                  | I/O  |  |

| 7    | IO_L32N_7            | IO_L32N_7                      | P9                  | I/O  |  |

| 7    | IO_L32P_7            | IO_L32P_7                      | P10                 | I/O  |  |

| 7    | IO_L33N_7            | IO_L33N_7                      | P6                  | I/O  |  |

| 7    | IO_L33P_7            | IO_L33P_7                      | P7                  | I/O  |  |

| 7    | IO_L34N_7            | IO_L34N_7                      | P2                  | I/O  |  |

| 7    | IO_L34P_7            | IO_L34P_7                      | P3                  | I/O  |  |

| 7    | IO_L35N_7            | IO_L35N_7                      | R9                  | I/O  |  |

| 7    | IO_L35P_7            | IO_L35P_7                      | R10                 | I/O  |  |

| 7    | IO_L37N_7            | IO_L37N_7                      | R7                  | I/O  |  |

| 7    | IO_L37P_7/VREF_7     | IO_L37P_7/VREF_7               | R8                  | VREF |  |

| 7    | IO_L38N_7            | IO_L38N_7                      | R5                  | I/O  |  |

| 7    | IO_L38P_7            | IO_L38P_7                      | R6                  | I/O  |  |

| 7    | IO_L39N_7            | IO_L39N_7                      | R3                  | I/O  |  |

| 7    | IO_L39P_7            | IO_L39P_7                      | R4                  | I/O  |  |

| 7    | IO_L40N_7/VREF_7     | IO_L40N_7/VREF_7               | R1                  | VREF |  |

| 7    | IO_L40P_7            | IO_L40P_7                      | R2                  | I/O  |  |

| 7    | N.C. (�)             | IO_L46N_7                      | M8 I/0              |      |  |

| 7    | N.C. (�)             | IO_L46P_7                      | M9                  | I/O  |  |

| 7    | N.C. (�)             | IO_L49N_7                      | N6                  | I/O  |  |

| 7    | N.C. (�)             | IO_L49P_7                      | M5 I/0              |      |  |

| 7    | N.C. (�)             | IO_L50N_7                      | N4                  | I/O  |  |

| 7    | N.C. (�)             | IO_L50P_7                      | N5                  | I/O  |  |

| 7    | VCCO_7               | VCCO_7                         | E3                  | VCCO |  |

| 7    | VCCO_7               | VCCO_7                         | J3                  | VCCO |  |

### Table 107: FG900 Package Pinout (Cont'd)

| Bank   | XC3S2000<br>Pin Name | XC3S4000, XC3S5000<br>Pin Name | FG900 Pin<br>Number | Туре   |  |

|--------|----------------------|--------------------------------|---------------------|--------|--|

| N/A    | VCCINT               | VCCINT                         | V12                 | VCCINT |  |

| N/A    | VCCINT               | VCCINT                         | W12                 | VCCINT |  |

| N/A    | VCCINT               | VCCINT                         | M13                 | VCCINT |  |

| N/A    | VCCINT               | VCCINT                         | W13                 | VCCINT |  |

| N/A    | VCCINT               | VCCINT                         | M14                 | VCCINT |  |

| N/A    | VCCINT               | VCCINT                         | W14                 | VCCINT |  |

| N/A    | VCCINT               | VCCINT                         | L15                 | VCCINT |  |

| N/A    | VCCINT               | VCCINT                         | Y15                 | VCCINT |  |

| N/A    | VCCINT               | VCCINT                         | L16                 | VCCINT |  |

| N/A    | VCCINT               | VCCINT                         | Y16                 | VCCINT |  |

| N/A    | VCCINT               | VCCINT                         | M17                 | VCCINT |  |

| N/A    | VCCINT               | VCCINT                         | W17                 | VCCINT |  |

| N/A    | VCCINT               | VCCINT                         | M18                 | VCCINT |  |

| N/A    | VCCINT               | VCCINT                         | W18                 | VCCINT |  |

| N/A    | VCCINT               | VCCINT                         | M19                 | VCCINT |  |

| N/A    | VCCINT               | VCCINT                         | N19                 | VCCINT |  |

| N/A    | VCCINT               | VCCINT                         | P19                 | VCCINT |  |

| N/A    | VCCINT               | VCCINT                         | U19                 | VCCINT |  |

| N/A    | VCCINT               | VCCINT                         | V19                 | VCCINT |  |

| N/A    | VCCINT               | VCCINT                         | W19                 | VCCINT |  |

| N/A    | VCCINT               | VCCINT                         | L20                 | VCCINT |  |

| N/A    | VCCINT               | VCCINT                         | R20                 | VCCINT |  |

| N/A    | VCCINT               | VCCINT                         | T20                 | VCCINT |  |

| N/A    | VCCINT               | VCCINT                         | Y20                 | VCCINT |  |

| VCCAUX | CCLK                 | CCLK                           | AH28                | CONFIG |  |

| VCCAUX | DONE                 | DONE                           | AJ28                | CONFIG |  |

| VCCAUX | HSWAP_EN             | HSWAP_EN                       | A3                  | CONFIG |  |

| VCCAUX | M0                   | MO                             | AJ3                 | CONFIG |  |

| VCCAUX | M1                   | M1                             | AH3                 | CONFIG |  |

| VCCAUX | M2                   | M2                             | AK3                 | CONFIG |  |